# Grid-Following DVI-Based Converter Operating in Weak Grids for Enhancing Frequency Stability

Meysam Saeedian, Reza Sangrody, Mahdi Shahparasti, *Member, IEEE*, Shamsodin Taheri, *Senior Member, IEEE*, and Edris Pouresmaeil, *Senior Member, IEEE*

Abstract-Inertia requirement is the paramount challenge in future power systems with a significant share of renewable energy generators. A promising solution to this issue is applying Distributed Virtual Inertia (DVI) concept, i.e. releasing energy preserved in the DC-link capacitors of employed power converters in the grid following a frequency disturbance. Nonetheless, small-signal stability analyses affirm that a local mode associated with the control system is prone to become unstable when the grid-interactive converter augmented with the DVI operates in weak grids. To overcome this problem, an efficient compensator is proposed in this paper. This compensator introduces one degreeof-freedom to the direct-axis current controller in synchronous reference frame, which eliminates the adverse impact of DVI function on converter stability. Finally, the efficacy of the proposed control framework is depicted by simulations in MATLAB. The results illustrate that the grid frequency rate of change following a step-up load change is improved by 30% compared to the case in which the DVI loop is nullified.

Index Terms—Distributed virtual inertia, grid frequency regulation, modern power system, phase –locked loop (PLL) dynamics, weak grid.

# Nomenclature

#### Abbreviations

$egin{array}{lll} DVI & {

m Distributed virtual inertia} \ PoI & {

m Point of interconnection} \ RES & {

m Renewable energy source} \ RoCoF & {

m Rate of change of frequency} \ SG & {

m Synchronous generator} \ SRF & {

m Synchronous reference frame} \ \end{array}$

Manuscript received May 7, 2020; revised August 31, 2020 and January 7, 2021; accepted January 27, 2021. Date of publication February 17, 2021; date of current version January 24, 2022. Paper no. TPWRD-00673-2020. (Corresponding author: Edris Pouresmaeil.)

Meysam Saeedian is with the Department of Electrical Engineering and Automation, Aalto-yliopisto, 02150 Espoo, Finland (e-mail: meysam.saeedian@aalto.fi).

Reza Sangrody is with the Department of Electrical and Computer Engineering, Islamic Azad University Foroozkooh Branch, Firoozkooh, Iran (e-mail: reza.sangrody@gmail.com).

Mahdi Shahparasti is with the School of Technology and Innovations, University of Vaasa, 65200 Vaasa, Finland (e-mail: mahdi.shahparasti@uwasa.fi).

Shamsodin Taheri is with the Computer Science and Engineering, Universite du Quebec en Outaouais, Gatineau, Quebec J8X 3X7, Canada (e-mail: shamsodin.taheri@uqo.ca).

Edris Pouresmaeil is with the Department of Electrical Engineering and Automation (EEA), Aalto University, 02150 Espoo, Finland (e-mail: edris.pouresmaeil@gmail.com).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TPWRD.2021.3059898.

Digital Object Identifier 10.1109/TPWRD.2021.3059898

| SCR | Short–circuit ratio      |  |

|-----|--------------------------|--|

| VSC | Voltage source converter |  |

#### Variables

| Grid current space vector      |

|--------------------------------|

| Converter current space vector |

| Converter input power          |

| Converter output power         |

| Grid voltage space vector      |

| PoI voltage space vector       |

| Converter voltage space vector |

| DC-link voltage                |

| Grid angular frequency         |

| Synchronization angle          |

|                                |

#### **Parameters**

| $C_{dc}, C_f$        | DC-link capacitor, filter capacitor      |

|----------------------|------------------------------------------|

| $k, k_d$             | DVI gain, compensator gain               |

| $k_{ppll}, k_{ipll}$ | PLL controller gains                     |

| $k_{pi}, k_{ii}$     | Current controller gains                 |

| $k_{pu}, k_{iu}$     | DC-voltage controller gains              |

| $k_{pq}, k_{iq}$     | AC-voltage controller gains              |

| $i_w^*$              | Converter current reference space vector |

| $\tilde{R_f}, R_g$   | Filter resistance, grid resistance       |

| $L_f, L_g$           | Filter inductance, grid inductance       |

|                      | DC-link voltage reference                |

| $u_{dc}^*$ $u_p^*$   | PoI voltage reference                    |

| $\omega_0^r$         | Grid nominal angular frequency           |

| $\omega_d$           | Compensator cut-off frequency            |

| $\zeta_d$            | Compensator damping ratio                |

|                      |                                          |

## Indices

| dq-    | Grid synchronous reference frame    |

|--------|-------------------------------------|

| $dq^c$ | Control synchronous reference frame |

#### I. INTRODUCTION

ONTINUOUS decrease in system inertia is the paramount issue in energy transition, from conventional thermal generation based on synchronous machines to converter–interfaced renewable generation. Loss of inertia changes the nature of power system, making low–inertia grids more sensitive to frequency perturbations (i.e. power mismatch between generation and demand) and jeopardizes system stability [1]–[3].

The frequency regulation adequacy is assessed with two most cited metrics: 1) rate of change of frequency (RoCoF), and 2)

frequency nadir -the maximum frequency deviation with regard to nominal value following a disturbance. Overall system inertia, effective droop coefficient, and governor/turbine delays are three significant parameters affecting the aforesaid indices [4]. In other words, diminution in system inertia is one of the parameters that impose a limit on further integration of RESs into power systems. This is because power electronic—based generators have neither rotational inertia nor damping characteristics of SGs inherently. The solution to this problem can be found in control scheme of interfaced converters, i.e. readjusting converter power reference in response to the contingencies, which is analogous to the released kinetic energy of real SGs [5], [6].

## A. Literature Survey

A plethora of mechanisms have been proposed for inertia emulation (also known as virtual or synthetic inertia) through a variety of devices [7]-[17], ranging from synchronous condensers to VSCs control. Reference [7] suggests employing synchronous condensers at the PoI of VSC-based sources, resulting in slower frequency dynamics. Synchronverter, an inverter that mimics SGs, has been proposed in [8]. The dynamic equations governing a synchronverter is the same as the SG equations; only the mechanical power exchanged with the prime mover is replaced with the power swapped with the inverter DC-link. Superior to an SG, we can select the parameters such as inertia in a synchronverter. Inspired by the operating principles of induction machines, [9] introduced a PLL-less VSC control called inducverter, which can participate in grid frequency regulation. In this method, the grid angle information required for the basic swing equation is generated by the power damping unit. The authors in [10] proposed a fast frequency support from wind farm doubly-fed induction generators (DFIGs) with auxiliary dynamic demand control. This method coordinates the DFIG and controllable loads to jointly provide inertial response following frequency disturbances. Research work conducted in [11] applies a super–capacitor to enhance the frequency stability, in which droop characteristic is paralleled with an integral controller and a distribution function. In [12], the authors enhanced a control method for battery energy storage systems (BESS) in autonomous microgrids with high penetration of RESs. In developed technique, a frequency controller composed of a droop control and inertia emulation function governs the BESS active power. A new control framework based on a stochastic equivalent model of the power system has been developed in [13], which provides flexible inertia constant to accommodate higher levels of distributed generation. This method employs an adaptive ESS dispatch strategy in a microgrid to provide frequency support for the host grid. The work presented in [14] focuses on frequency regulation of a stand-alone microgrid by means of external energy reserve. Therein, an ESS-fed inverter is governed using a current controller equipped with a new frequency estimation technique. A promising method called distributed virtual inertia (DVI) for mimicking inertial response of real SGs has been proposed in [15]–[17]. The DVI approach employs the DC-link capacitors inhered in the DC-side of

grid—interfaced converters (applied to solar/wind farms, variable speed drives, switched—mode power supplies, active power filters etc.) as the energy buffer aimed at primary frequency stability improvement. In other words, the emulated inertia by the DVI approach is essentially generated through a large number of capacitors employed in many grid—tied converters distributed in modern power systems. This concept can be implemented without increasing system cost and complexity [15].

# B. Problem Statement and Paper Contribution

This study concerns the impact of DVI method on stability of grid—following converters operating in weak grids. To this end, we first present a precise small—signal state—space realization of a grid—interactive converter, composed of inner—loop current controller, outer—loop voltage controller, DVI function, and SRF transformation introduced by synchronization unit dynamics. The problem statement and contribution of the paper to the research field are thus summarized as:

- The small-signal stability analyses reveal that a local mode corresponding to the control system subjects to instability when the converter augmented with the DVI function operates in weak grids. Higher DVI gain yields better grid primary frequency regulation as the DVI method can provide more inertia power; but, it exacerbates the converter instability.

- To overcome this instability problem and gain the most benefit from acceptable DC-link voltage oscillations (aimed at primary frequency stability enhancement following a disturbance), a new compensator is proposed and designed. Consequently, the proposed control scheme provides the maximum DVI support while the system remains stable in weak grids, which is the main contribution of this work.

The remainder of this paper is organized as follows: Section II includes the converter control scheme. Followed by deriving state—space realization of the system in Section III, the instability problem of the converter equipped with the DVI functionality in weak grids is further elaborated in Section IV. The proposed compensator and its design procedure is provided in Section V. The efficacy of the proposed control framework is then depicted in Section VI by simulations in MATLAB. Finally, Section VII concludes the paper.

## II. CONVERTER CONTROL SCHEME

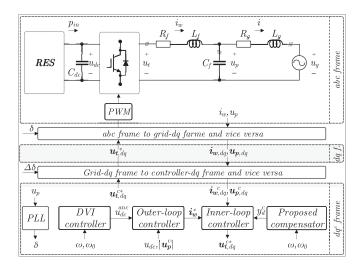

Throughout this study, the entire modeling and control of the converter is implemented in the SRF. Quantities in the synchronous coordinates are written in complex space vectors—denoted with boldface letters — e.g.  $\boldsymbol{u_g} = u_{gd} + ju_{gq}$  for the grid voltage. Consider Fig. 1, where the quantities on the three–phase AC–side are expressed in the abc–frame. An LC converter output filter is assumed to mitigate the high–order harmonics introduced by the switching process. The grid is modeled as a equivalent Thevenin circuit with the grid strength defined by

Fig. 1. Grid-interactive converter model understudy.

short-circuit ratio:

$$SCR = \frac{u_{p,rated}^2 / \sqrt{R_g^2 + \omega^2 L_g^2}}{p_{out,rated}}.$$

(1)

The network with SCR  $\geq 3.0$  is known as a strong grid while SCR < 3.0 represents a weak grid condition [18]. Herein, we consider two SCRs, 2.5 and 1.0. On the DC-side,  $C_{dc}$  denotes the DC-link capacitance which acts as the energy buffer in DVI concept for power system inertia augmentation. The mechanism of emulating inertia in the DVI approach is as follow: the grid frequency oscillation ( $\Delta\omega$ ) following a disturbance (power mismatch between the generation and demand) is proportionally linked to the DC-bus voltage controller through the DVI gain 'k', as later depicted in Fig. 4. Remarkably,  $k \times \Delta\omega$  must be limited to the maximum acceptable DC-link voltage variation. Hence, any  $\Delta\omega$  yields discharging  $C_{dc}$  which is analogous to the released kinetic energy of real SGs during the frequency disturbance. The inertia coefficient generated by this method can be expressed as [15], [16]:

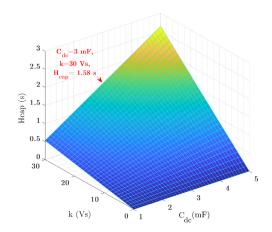

$$H_{cap} = k \frac{C_{dc} u_{dc}^{*2}}{2V A_{rated}}. (2)$$

As per (2), the virtual inertia  $H_{cap}$  under a certain VSC power rating ( $VA_{rated}$ ) is restricted by the following factors:  $C_{dc}$ ,  $u_{dc}^*$ , and k. Fig. 2 illustrates the virtual inertia coefficient  $H_{cap}$  in terms of  $C_{dc}$ , and k for a 16 kVA power converter with  $u_{dc}^* = 750$  V. As observed from this figure,  $H_{cap}$  increases as the DC-link capacitance and the DVI gain take larger values. Therefore, better grid primary frequency regulation is attained.

# III. SYSTEM MODEL

This section includes the detailed state-space representation for each control block and system element in Fig. 1. Consequently, the model is linearized around operating points for small-signal stability analyses.

Fig. 2. Synthetic inertia coefficient in terms of  $C_{dc}$  and k (reference: [15]).

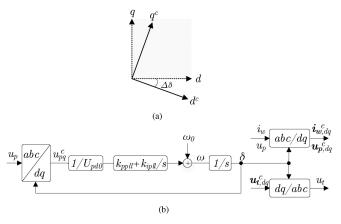

Fig. 3. (a) Reference frames associated with the grid and the controller, (b) PLL structure.

## A. Synchronization Unit (PLL)

The PLL acts as a closed–loop control to synchronize the VSC with the grid. Due to the operation of the PLL, the system depicted in Fig. 1 comprises two synchronous reference frames: one is the grid frame (dq) and the other one is the control frame  $(dq^c)$  [19], [20]. The former frame is defined by the PoI voltage while the latter one is introduced by the PLL dynamics following a perturbation. In steady state, the  $dq^c$  frame coincides with the dq frame. When a small disturbance occurs (e.g. stochastic demand fluctuation), the synchronization angle  $(\delta)$  oscillates to re–synchronize the converter with the grid. Thus, the frames are no longer aligned and  $dq^c$  lags the grid frame as depicted in Fig. 3(a). The PLL drives the q-component of PoI voltage in the  $dq^c$  frame to zero. Assuming that a second–order PLL [21] is applied [Fig. 3(b)], the state-space realization of the PLL is expressed as:

$$\dot{\delta} = \omega = \omega_0 + \frac{k_{ppll}}{U_{pd0}} u_{pq}^c + \underbrace{\frac{k_{ippl}}{U_{pd0}} \int u_{pq}^c dt}_{(3)}$$

To accurately model the impact of PLL on the system dynamics, the measured quantities  $i_w$  and  $u_p$  in the grid coordinates must be rotated to the  $dq^c$  frame for feedback control process (cf. Fig. 1). Then, the command voltage signal  $u_t^{c*}$  generated

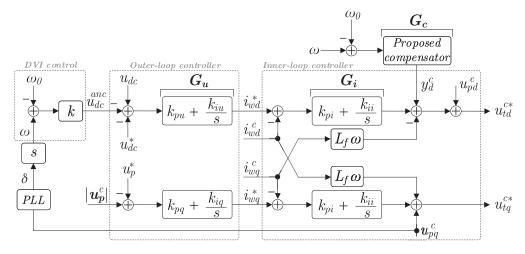

Fig. 4. Block diagram of the proposed controller in dq-coordinate.

by the control loops is re–transformed to the grid coordinate (i.e.  $u_t^{c*} \to u_t^*$ ). Assuming that the error angle between the two frames  $(\Delta \delta)$  is small, the aforesaid process is mathematically characterized as:

$$i_{\mathbf{w}}^{c} = (1 - j\Delta\delta)i_{\mathbf{w}}, \ \mathbf{u}_{\mathbf{p}}^{c}$$

$$= (1 - j\Delta\delta)\mathbf{u}_{\mathbf{p}}, \ \mathbf{u}_{\mathbf{t}}^{*} = (1 + j\Delta\delta)\mathbf{u}_{\mathbf{t}}^{c*}. \tag{4}$$

# B. DC-Side Dynamics

Suppose that the power losses in the converter and interfaced filter is negligible. As per the power balance between two sides of the VSC, the state–space model of the DC–link dynamics is represented by:

$$\dot{u}_{dc} = \frac{p_{in} - \frac{3}{2}(u_{pd}i_{wd} + u_{pq}i_{wq})}{C_{dc}u_{dc}}.$$

(5)

### C. AC-Side Dynamics

The electric system includes an LC filter and a transmission line modeled as Thevenin equivalent. This simple structure is selected to obtain a basic model focusing on the dynamics of the VSC rather than AC grid topology. Without major inaccuracy, we can assume that the command voltage  $u_t^*$  appears at the input side of the filter (i.e.  $u_t^* = u_t$ ). This approach only neglects the energy losses across power switches [22]. Using complex–valued space vectors presentation, the SRF state–space equations governing the AC–side dynamics are established as:

$$\dot{\boldsymbol{i}}_{\boldsymbol{w}} = \frac{1}{L_f} \boldsymbol{u}_{\boldsymbol{t}} - \frac{1}{L_f} \boldsymbol{u}_{\boldsymbol{p}} - \left(\frac{R_f}{L_f} + j\omega\right) \boldsymbol{i}_{\boldsymbol{w}} \tag{6}$$

$$\dot{\boldsymbol{u}}_{\boldsymbol{p}} = \frac{1}{C_f} \boldsymbol{i}_{\boldsymbol{w}} - \frac{1}{C_f} \boldsymbol{i} - j\omega \boldsymbol{u}_{\boldsymbol{p}} \tag{7}$$

$$\dot{i} = \frac{1}{L_g} u_p - \frac{1}{L_g} u_g - \left(\frac{R_g}{L_g} + j\omega\right) i.$$

(8)

#### D. AC-Current Control

The converter output current  $i_w$  is set to its reference  $i_w^* = i_{wd}^* + j i_{wq}^*$  via two proportional-integral (PI) controllers with PoI voltage feedforward and cancellation of the dq-cross coupling [23]. Hence, the modulation voltage reference  $u_t^{c*}$  in the control dq-coordinate is defined by:

$$\boldsymbol{u_{t}^{c*}} = \boldsymbol{u_{p}^{c}} + j\omega L_{f} \boldsymbol{i_{w}^{c}} + k_{pi} (\boldsymbol{i_{w}^{*}} - \boldsymbol{i_{w}^{c}}) + \underbrace{k_{ii} \int (\boldsymbol{i_{w}^{*}} - \boldsymbol{i_{w}^{c}}) dt}_{\varphi_{i_{w}, dq}}.$$

(9)

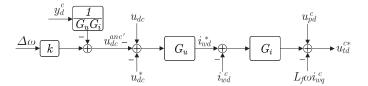

As  $i_w^*$  is always expressed in the control dq frame, it is not denoted by the superscript c'. Moreover, the d-axis current reference is obtained by regulating the DC-link voltage to its nominal value whereas the AC-voltage control loop defines the q-axis current reference (cf. Fig. 4).

## E. DC-Voltage Control

The DC-link voltage regulation to its nominal value is attained by a PI-controller. Furthermore, the ancillary voltage signal  $u^{anc}_{dc}$  generated through the DVI approach is added to the DC-voltage controller aimed at enhancing grid primary frequency regulation (cf. Fig. 4). Thus:

$$i_{wd}^* = k_{pu}[u_{dc} - u_{dc}^* - u_{dc}^{anc}] + \underbrace{k_{iu} \int [u_{dc} - u_{dc}^* - u_{dc}^{anc}] dt}_{\varphi_u}$$

(10)

in which  $u_{dc}^{anc}$  is:

$$u_{dc}^{anc} = k(\omega - \omega_0) = k\Delta\omega. \tag{11}$$

It is worth pointing out that the DC-link voltage must be restricted to  $u_{dc}^{\min} \leq u_{dc} \leq u_{dc}^{\max}$ , in which  $u_{dc}^{\min}$  ensures linear modulation of the VSC. While,  $u_{dc}^{\max}$  is defined by the voltage rating of converter switches [24]. As a consequence, the amplitude of ancillary signal  $u_{dc}^{anc}$  must be limited such that the DC-link voltage oscillation holds the aforesaid range.

## F. AC-Voltage Control

The AC-voltage controller is required in weak grid connections. This is because the PoI voltage in weak grids is not constant and needs to be regulated to its reference  $u_p^*$  (herein  $400\sqrt{2/3}$  V). Accordingly, a PI-controller is used for the AC-voltage control loop (cf. Fig. 4), and its output produces the q-axis current reference as:

$$i_{wq}^* = k_{pq}(|\boldsymbol{u_p^c}| - u_p^*) + \underbrace{k_{iq} \int (|\boldsymbol{u_p^c}| - u_p^*) dt}_{\varphi_q}$$

(12)

where  $|u_p^c| = \sqrt{u_{pd}^{c2} + u_{pq}^{c2}}$ . In the linearization process,  $|\Delta u_p^c| = \Delta u_{pd}^c$  [23], [25].

#### IV. SMALL-SIGNAL STATE-SPACE STABILITY ANALYSIS

This section affirms that the ancillary DVI technique yields instability of a local mode associated with the control system when the converter operates in weak grids. The VSC scheme shown in Fig. 1 exclusive of proposed compensator is called uncompensated system.

#### A. Linearized Model

The stability assessments are based on eigenvalues. Therefore, the state equations (3)–(12) are linearized around equilibrium points (denoted by 0 in subscripts) to obtain the small–signal state–space realization as [26]:

$$[\Delta \dot{x}_{uncomp}] = [A_{uncomp}][\Delta x_{uncomp}] + [B_{uncomp}][\Delta u]$$

(13)

where the prefix  $\Delta$  stands for the small deviation of the corresponding state variable around the equilibrium point. The state matrix  $\Delta x_{uncomp}$  and input matrix  $\Delta u$  are defined, respectively as:

$$\Delta x_{uncomp} = [\Delta \delta \ \Delta \varphi_{\delta} \ \Delta i_{wd} \ \Delta i_{wq} \ \Delta u_{pd} \ \Delta u_{pq} \ \Delta u_{dc}$$

$$\Delta \varphi_{u} \ \Delta \varphi_{i_{wd}} \ \Delta \varphi_{i_{wq}} \ \Delta i_{d} \ \Delta i_{q} \ \Delta \varphi_{q}]_{1 \times 13}^{T} \quad (14)$$

$$\Delta u = [\Delta p_{in}]. \tag{15}$$

It is worth mentioning that the state variables  $\Delta\varphi_{\delta}$ ,  $\Delta\varphi_{u}$ ,  $\Delta\varphi_{i_{wd}}$ ,  $\Delta\varphi_{i_{wq}}$ , and  $\Delta\varphi_{q}$  are associated with integral parts of the PLL, DC-voltage control, d-axis current control, q-axis current control, and AC-voltage control, respectively. The state and input matrices of the uncompensated system are provided in Appendix. Furthermore, the specifications of system understudy are tabulated in Table I.

#### B. Sensitivity Analysis

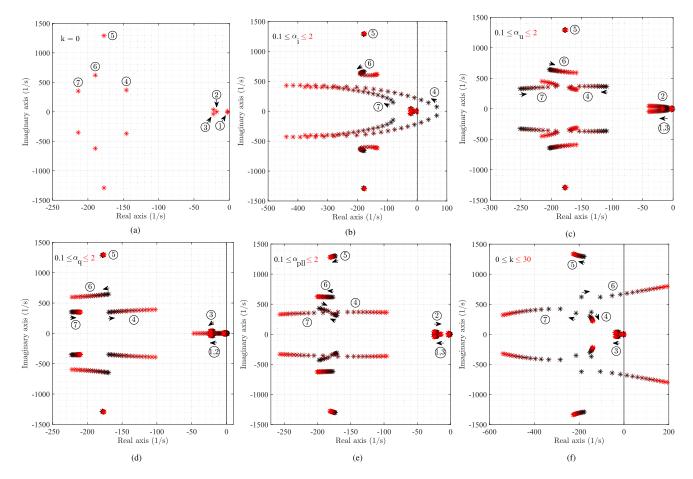

Below, we appraise the sensitivity of system stability in terms of control parameters variations. Fig. 5(a) depicts eigenvalue locus of the uncompensated VSC under very—weak grid condition (SCR = 1.0) whilst the DVI function stays nullified, i.e. k is set to zero. The eigenvalues define 7 different modes marked with numbers. According to the Lyapunov stability theory and Fig. 5(a), the system is asymptotically stable in the small–signal

TABLE I

THE PARAMETERS OF SYSTEM UNDERSTUDY

| Parameter  | Value           | Parameter            | Value                          |

|------------|-----------------|----------------------|--------------------------------|

| $R_f, L_f$ | 0.1 Ω, 2.94 mH  | $k_{ppll}, k_{ipll}$ | 10, 100                        |

| $C_f$      | 50 μF           | $k_{pi}, k_{ii}$     | 1.176, 470.4                   |

| $C_{dc}$   | 4 mF            | $k_{pu}, k_{iu}$     | 0.1, 5                         |

| SCR        | 1.0 & 2.5       | $k_{pq}, k_{iq}$     | 0.001, 5                       |

| k          | 30 Vs           | $\omega_0$           | $2\pi \times 50 \text{ rad/s}$ |

| $k_d$      | 4 & 3.3 Vs      | $u_{dc}^*$           | 750 V                          |

| $\zeta_d$  | 1.0             | $u_{p,rated}$        | 400 V                          |

| $\omega_d$ | 335 & 805 rad/s | $VA_{rated}$         | 16 kVA                         |

sense. Fig. 5(b)–(e) illustrate four case studies, modifying the parameters of 1) inner current controller, 2) DC–voltage controller, 3) AC–voltage controller, 4) and synchronization unit.

In case 1, the PI control parameters are scaled using the variable  $\alpha_i$ , which is increased from 0.1 to 2 with changes of 0.1. Fig. 5(b) shows the corresponding pole diagram. The modification of inner current control affects significantly modes 4, 6, and 7. Its impact on the remaining poles is negligible. As observed from Fig. 5(b), increasing  $\alpha_i$  yields movement of modes 4 and 7 towards the left-hand side of s-plane. Thus, the system becomes stable. In case 2, the DC-voltage control parameters are multiplied by the variable  $\alpha_u$ , varying between  $0.1 \le \alpha_u \le 2$ . As per Fig. 5(c), modes 1, 2, and 5 are hardly sensitive to DC-voltage control variations. Nonetheless, the VSC is stable as all the poles remain in the left–half s–plane. The impact of AC-voltage control is demonstrated in case 3 [cf. Fig. 5(d)]. Multiplying the associated PI control parameters by the variable  $0.1 \le \alpha_q \le 2$  affects all modes except 5. Mode 2 is unstable for  $\alpha_q \leq 0.4$ , however, increasing  $\alpha_q$  shifts this pole towards the stable region. Other poles are stable in the defined scenario. The modification of PLL parameters by scaling the variable  $0.1 \le \alpha_{pll} \le 2$  is depicted in Fig. 5(e). It is clear that the control system is stable if  $\alpha_{pll}$  holds the aforesaid range. Thus far, we can conclude that the VSC is robust against variations of control parameters. A compromise should be made between locations of different modes by selecting proper variables  $\alpha$ (herein, we set all  $\alpha$  to 1).

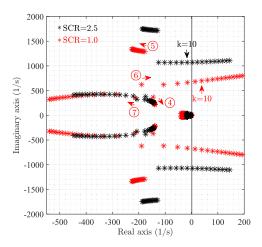

The provision of synthetic inertia support is fulfilled by increasing the gain k in the DVI technique. However, it results in migration of mode 6 towards the right–hand side of s–plane [cf. Fig. 5(f)], making the system completely unstable. The effect of DVI function on other modes is also pictured in Fig. 5(f). The higher DVI gain, the better grid primary frequency regulation; nonetheless, it exacerbates the system instability as observed from Fig. 5(f). Hence, we deduce that the DVI approach induces instability to the interfaced converter in weak grids. It is noteworthy that the control system remains stable even with high DVI gain when the grid is strong enough. Fig. 6 demonstrates the eigenvalue loci of the system for two different values of SCR (notice  $0 \le k \le 30$ ). For example, the system is stable with k = 10 if SCR = 2.5 while it subjects to instability in weaker grid conditions with the same k.

## V. PROPOSED COMPENSATION TECHNIQUE

## A. Model Description

Herein, we propose a new compensator to 1) overcome the instability problem raised by the ancillary DVI control, and 2) take

Fig. 5. Eigenvalue loci of the system (SCR = 1.0) (a) k = 0, (b)  $0.1 \le \alpha_i \le 2$ , (c)  $0.1 \le \alpha_u \le 2$ , (d)  $0.1 \le \alpha_q \le 2$ , (e)  $0.1 \le \alpha_{pll} \le 2$ , (f)  $0 \le k \le 30$  with variations of 2.

Fig. 6. Eigenvalue loci of the system for different values of SCR (0  $\leq k \leq$  30 with variations of 2).

the most advantage of acceptable DC-link voltage oscillation. As illustrated in Fig. 4, the compensation signal  $y_d^c(s)$  introduces one degree-of-freedom to the d-channel of the VSC controller. The mathematical model of this supplementary signal in Laplace domain is:

$$y_d^c(s) = \frac{2k_d \zeta_d \omega_d s}{s^2 + 2\zeta_d \omega_d s + \omega_d^2} (\omega - \omega_0) = G_c(s) \Delta \omega.$$

(16)

Fig. 7. Simplified model of the d-channel controller.

The compensator is designed based on the fact that the time–derivative of PLL output (i.e  $\omega$ ) entered to the d–channel through the DVI function is the detrimental factor of system stability in weak grids (cf. Figs. 4 & 5). Thus,  $\omega$  is selected as the signal to solve the aforesaid problem. The compensator output  $y_d^c(s)$  must not affect the tracking of controlled variables during steady state operation (i.e. when  $\omega=\omega_0$ ). Therefore, the grid nominal angular frequency  $\omega_0$  is subtracted from the signal  $\omega$ , and is then applied to a band–pass filter to obtain  $y_d^c(s)$ . The parameters  $k_d$ ,  $\zeta_d$  and  $\omega_d$  in (16) are the filter gain, damping ratio and cut–off frequency, respectively.

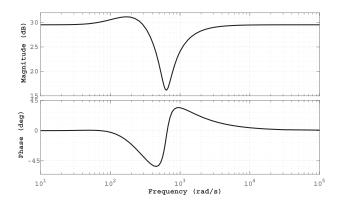

The proposed compensator can be explicated as modifying the DVI gain k into a transfer function named k'(s); which is derived as below. Consider the d-channel of controller in Fig. 4. Moving the signal  $y_d^c(s)$  ahead of the d-axis current and DC-voltage controllers yields Fig. 7. Hence, the new ancillary voltage signal

Fig. 8. Frequency response of k'(s).

$u_{dc}^{anc'}(s)$  is obtained as:

$$u_{dc}^{anc'}(s) = \underbrace{k\Delta\omega}_{u_{dc}^{anc}} - \frac{y_d^c(s)}{G_u(s)G_i(s)}.$$

(17)

Substituting (16) into (17) gives:

$$u_{dc}^{anc'}(s) = \underbrace{\left(k - \frac{G_c(s)}{G_u(s)G_i(s)}\right)}_{k'(s)} \Delta\omega. \tag{18}$$

Fig. 8 illustrates the frequency response of k'(s) when k and SCR are set to 30 Vs and 1.0, respectively (the parameters of  $G_c(s)$  are designed in Section V. B). As observed from this figure, k'(s) attenuates k at a certain range of frequency. The k'(s) amplitude is 29.55 dB (30 Vs) – just equal to k. However, it curtails to 16 dB (6.3 Vs) at 640 rad/s which yields a stable mode of 6 (cf. Fig. 6). Thus, we conclude that k'(s) manipulates k as a function of frequency so that it holds the VSC stable while providing maximum DVI support as it will be shown in Fig. 14 (the maximum DVI support is obtained if the DC–link capacitor is discharged until  $u_{dc}$  reaches  $u_{dc}^{\min}$ ). It is also noteworthy that  $u_{dc}^{anc'}(s)$  does not impact on the d-axis current controller (DC-voltage controller) bandwidth as it only changes the current reference  $i_{wd}^*$  (DC-link voltage reference  $u_{dc}^*$ ) – the input of controller – with grid frequency disturbance (cf. Fig. 7).

Two state variables  $\gamma_1$  and  $\gamma_2$  are defined by (16) with the small–signal state–space realization of:

$$\begin{bmatrix} \Delta \dot{\gamma}_1 \\ \Delta \dot{\gamma}_2 \end{bmatrix} = \begin{bmatrix} -2\zeta_d \omega_d & 1 \\ -\omega_d^2 & 0 \end{bmatrix} \begin{bmatrix} \Delta \gamma_1 \\ \Delta \gamma_2 \end{bmatrix} + \begin{bmatrix} -2\zeta_d \omega_d k_d k_{ppll} \\ 0 \end{bmatrix} \Delta \delta + \begin{bmatrix} 2\zeta_d \omega_d k_d \\ 0 \end{bmatrix} \Delta \varphi_\delta + \begin{bmatrix} 2\zeta_d \omega_d k_d k_{ppll} / U_{pd0} \\ 0 \end{bmatrix} \Delta u_{pq}$$

(19)

and  $\Delta y_d^c = \Delta \gamma_1$ , which are added to the uncompensated system presented by (13). Hence, the final small-signal state-space model of the compensated VSC system is derived as:

$$[\Delta \dot{x}_{comp}] = [A_{comp}][\Delta x_{comp}] + [B_{comp}][\Delta u]$$

(20)

where the corresponding matrices are presented in Appendix.

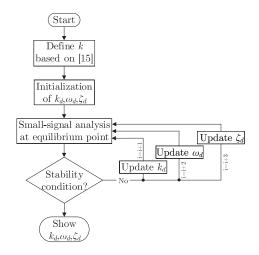

Fig. 9. Design flowchart of proposed compensator (i stands for iteration).

# B. Compensator Design

Three parameters  $k_d$ ,  $\omega_d$ , and  $\zeta_d$  are designed so that the adverse impact of the DVI function on system stability is eliminated. The design flowchart is depicted in Fig. 9, which can be summarized as follows: 1) the DVI gain is first defined by the algorithm presented in [15]. 2) The compensator parameters are then initialized in a practical manner. 3) The eigenvalues analysis is performed around the equilibrium points applying MATLAB to examine the system small–signal stability. 4) If all eigenvalues are in the left–half s–plane, the VSC is being stabilized and the stability condition is satisfied. Otherwise,  $k_d$ ,  $\omega_d$ , and  $\zeta_d$  must be updated in three separate iterations, respectively. In each iteration, the algorithm returns to stage 3. In this study, two worst–case scenarios are considered for the design process: 1) SCR = 1.0 and k = 30, and 2) SCR = 2.5 and k = 30 (cf. Fig. 6).

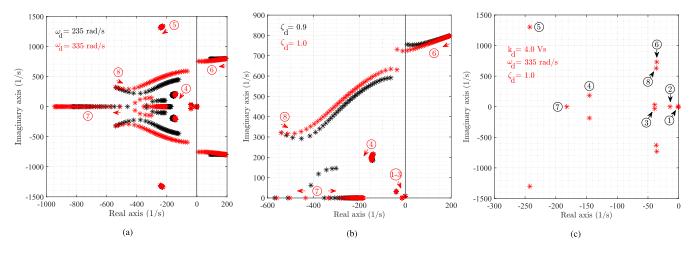

Fig. 10(a) shows the eigenvalue locus of the compensated system with SCR = 1.0 in terms of different  $k_d$  and  $\omega_d$  (we first assume that  $\zeta_d = 0.9$ ). It is noteworthy that the complex mode 8 is defined by the proposed compensator. The parameter  $k_d$  varies between  $0 \le k_d \le 4$  Vs and  $\omega_d$  takes two values, 235 and 335 rad/s. As observed from this figure, the unstable mode 6 moves towards the stable region of s-plane by increasing  $k_d$ . This trend occurs at a faster rate for higher values of the cut-off frequency  $\omega_d$ . Thus far, the parameters  $k_d$  and  $\omega_d$  are selected 4 Vs and 335 rad/s, respectively. Nonetheless, the system is still unstable. Hence, the third parameter, i.e.  $\zeta_d$ , must be updated. As illustrated in Fig. 10(b), increasing  $\zeta_d$  yields a more damped system (it positively affects modes 6 and 7 – the eigenvalues with positive imaginary parts are only displayed for high visibility). Thus,  $\zeta_d = 1.0$  stabilizes the VSC. It is noteworthy that the proposed compensator has no impact on the most dominant modes 1, 2, and 3 while it relocates the unstable mode 6 from  $193.4 \pm j798$  to the stable location  $-36 \pm j731$  [cf. Figs. 6 and 10(c)], i.e. the negative impact of DVI function on the system eigenvalues is compensated by the ancillary signal  $y_d^c(s)$ .

Fig. 11 also presents the compensator design for SCR = 2.5. The same algorithm is performed here. First, assume  $\zeta_d$  is set to 0.7. Fig. 11(a) depicts the VSC eigenvalue locus when  $k_d$  varies

Fig. 10. The impact of  $k_d$  and (a)  $\omega_d$  (b)  $\zeta_d$  on the system dynamics, (c) final eigenvalue locus of the compensated system (remark: the grid SCR = 1.0).

Fig. 11. The impact of  $k_d$  and (a)  $\omega_d$  (b)  $\zeta_d$  on the system dynamics, (c) final eigenvalue locus of the compensated system (remark: the grid SCR = 2.5).

between  $0 \le k_d \le 3.3$  Vs, and  $\omega_d$  takes the values 605 and 805 rad/s. As indicated, the mode of interest 6 shifts to the left–hand side of s–plane by increasing  $k_d$ . Again, this trend happens at a faster rate for bigger value of  $\omega_d$ . Thus far,  $k_d$  and  $\omega_d$  are selected 3.3 Vs and 805 rad/s, respectively. On the other hand, a more damped system can be obtained with increasing  $\zeta_d$  as shown in Fig. 11(b). Herein,  $\zeta_d = 1.0$  is considered. Akin to former scenario, the compensator does not impact on the most dominant modes whereas it conveys the unstable mode 6 from  $144.7 \pm j1107$  to the stable point  $-139 \pm j1003$  [cf. Fig. 11(c)]. Hence, in weak grids where the DVI functionality results in system instability, the proposed compensator successfully stabilizes the VSC control.

#### VI. SIMULATION RESULTS

To check the efficacy of proposed method, the time-domain model of the system shown in Fig. 1 has been built in MATLAB. The operating voltage  $u_p$  is  $400 \, \mathrm{V(rms)}$ , and the converter power rating is 16 kVA. It is assumed that the maximum acceptable DC-link voltage oscillation is 6.67% (i.e. 50 V). The weak grid is represented by two different SCRs, 2.5 and 1.0. Other specifications of the VSC system is summarized in Table I.

Simulations are split into two parts: 1) uncompensated system to support the stability analyses conducted in Section IV, and 2) compensated system to validate effectiveness of the proposed compensation technique.

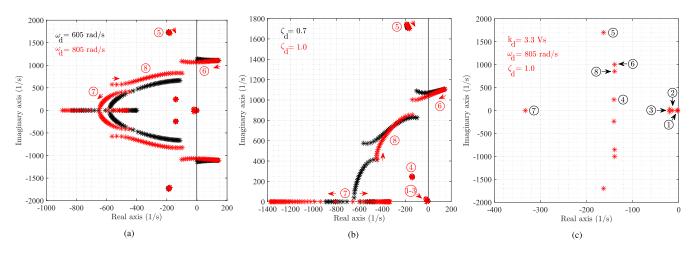

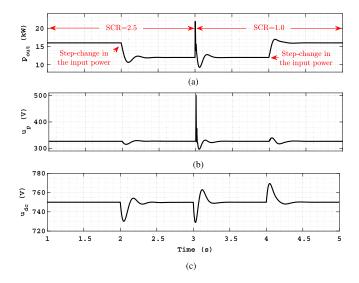

# A. Uncompensated VSC System

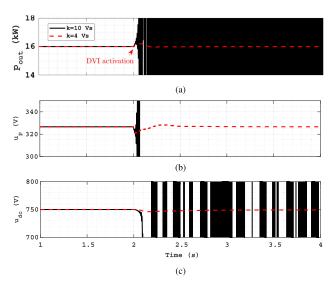

This subsection presents the converter outputs when the proposed compensator stays nullified. First, the grid operates normally. As indicated in Section III, the grid-following converter achieves two control functions: 1) injects  $p_{in}$  while regulating the dc-link capacitor voltage, and 2) regulates the point of interconnection voltage. Fig. 12 illustrates  $p_{out}$ ,  $u_p$ , and  $u_{dc}$  considering step-changes in the input power at t = 2 s and 4 s ( $p_{in}$ :  $16 \, \text{kVA} \rightarrow 12 \, \text{kVA} \rightarrow 16 \, \text{kVA}$ , respectively), and SCR-change at t = 3 s (SCR:  $2.5 \rightarrow 1.0$ ). This figure proves the proper operation of control block under grid-normal condition as the controlled variables track their references well. As stated earlier, however, the converter controller augmented with the DVI functionality subjects to instability if a frequency disturbance (e.g. demand fluctuation) occurs in the weak grid. It is worth noting that the DVI function aims at better primary frequency regulation via generating synthetic inertia. To indicate this issue, a 3% step-up

Fig. 12. VSC outputs (remark: the power grid is under normal operation).

Fig. 13. Uncompensated system outputs (remarks: SCR = 1.0, and the 3% step-up load change occurs at t=2 s).

load change is considered at t=2 s and the output waveforms for two different values of the DVI gain k are provided in Fig. 13 (grid SCR is 1.0). As observed in this figure, the controlled variables reach their nominal values perfectly. But, the control system becomes unstable followed by the defined disturbance when k increases. These results support the eigenvalue analyses conducted in Section IV (cf. Figs. 5 & 13).

# B. Compensated VSC System

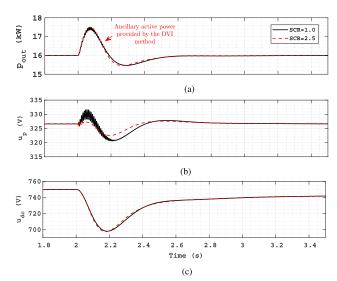

Here, the proposed compensator is activated to overcome the adverse impact of the DVI approach on system stability. The results are then measured. Fig. 14 depicts the outputs of interest when the grid SCR is 2.5 and 1.0, and the 3% step–up load change arises at t=2 s. As per Fig. 14(a), the converter output power  $p_{out}$  swiftly increases from 16 kW to 17.5 kW when the frequency perturbation occurs. This supplementary power is analogous with the released kinetic energy of real

Fig. 14. Compensated system outputs (remarks:  $k=30~{\rm Vs}$ , and the 3% stepup load change occurs at  $t=2~{\rm s}$ ).

Fig. 15. Frequency oscillations measured by the PLL at the PoI (remark: SCR = 1.0).

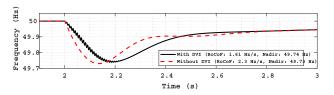

synchronous generators during disturbance to restore the power balance, i.e. mechanism of synthetic inertia provision. The PoI voltage oscillations following the disturbance is illustrated in Fig. 14(b), in which  $u_p$  reaches the nominal value after a short transient. Moreover, the DC-link capacitor voltage is brought in Fig. 14(c). As observed, the voltage drops to 700 V by the DVI function. It is worth noting that the voltage is still within the acceptable range. The decrease in capacitor voltage signifies that the discharged energy supports the grid frequency, resulting in better primary frequency regulation. The frequency oscillations measured by the PLL at the PoI is also shown in Fig. 15. When the VSC system is equipped with the DVI function, the grid frequency experiences lower frequency nadir and the frequency rate of change is improved by 30% compared with the case in which the DVI loop is canceled out. Thus, the frequency stability metrics are enhanced using the proposed control scheme.

From Figs. 13 and 14, we can conclude that the proposed compensator holds the system augmented with the DVI functionality totally stable in weak grids. It should be highlighted that the supplementary active power provided by the DVI technique is 9.38% of the VSC power rating which is a promising value for future power grids with high shares of RESs integrating through voltage source converters.

## VII. CONCLUSION

Herein, we first studied the stability of a grid-following voltage source converter equipped with distributed virtual inertia

(DVI) technique under weak grid conditions. The precise smallsignal state-space analyses have revealed that a local mode associated with the control system subjects to instability when the DVI-based converter operates in weak grids. To overcome this instability problem, an efficient compensator has been then proposed, which introduces one degree-of-freedom to the d-axis current controller. Thus, the developed control scheme provides maximum DVI support whilst the system remains stable. Finally, the simulations have depicted that the rate of frequency change following a power mismatch between generation and demand has improved by 30% compared to the case in which the DVI function is canceled out.

# APPENDIX A STATE AND INPUT MATRICES

The state matrices associated with the uncompensated and compensated VSC systems are provided at the end of this paper, in which:

$$a_{3,1} = \frac{kk_{pu}k_{pi}k_{ppll} - k_{pi}I_{wq0} + U_{pq0} - U_{tq0}}{L_f} + I_{wq0}k_{ppll} + \omega_0 I_{wd0} - k_{ppll}I_{wq0}$$

$$a_{4,1} = \frac{k_{pi}I_{wd0} + k_{pi}k_{pq}U_{pq0} - U_{pd0} + U_{td0}}{L_f} + \omega_0 I_{wq0}$$

$$-2k_{ppll}I_{wd0}$$

$$a_{7,3} = \frac{-3U_{pd0}}{2C_{dc}u_{dc}^*}$$

$$a_{7,4} = \frac{-3U_{pq0}}{2C_{dc}u_{dc}^*}$$

$$a_{7,5} = \frac{-3I_{wd0}}{2C_{dc}u_{dc}^*}$$

$$a_{7,6} = \frac{-3I_{wq0}}{2C_{dc}u_{dc}^*}$$

$$a_{9,1} = kk_{pu}k_{ii}k_{ppll} - k_{ii}I_{wq0}$$

$$a_{10,1} = k_{ii}I_{wd0} + k_{ii}k_{pq}U_{pq0}.$$

And the input matrices are:

$$B_{uncomp} = \begin{pmatrix} 0_{1\times6} & \frac{1}{C_{dc}u_{dc}^*} & 0_{1\times6} \end{pmatrix}_{1\times13}^T$$

$A_{uncomp}$

$$B_{comp} = \begin{pmatrix} B_{uncomp} & 0_{1\times 2} \end{pmatrix}_{1\times 15}^{T}.$$

Moreover, the state vector  $\Delta x_{comp}$  corresponding to the compensated VSC system is:

$$\Delta x_{comp} = [\Delta x_{uncomp} \ \Delta \gamma_1 \ \Delta \gamma_2]_{1 \times 15}^T.$$

#### REFERENCES

- N. Hatziargyriou et al., "Contribution to bulk system control and stability by distributed energy resources connected at distribution network," IEEE Power Energy Soc., Piscataway, NJ, USA, Tech. Rep. PES-TR22, Jan. 2017.

- [2] B. K. Poolla, S. Bolognani, and F. Dörfler, "Optimal placement of virtual inertia in power grids," *IEEE Trans. Autom. Control*, vol. 62, no. 12, pp. 6209–6220, Dec. 2017.

- [3] C. Collados-Rodriguez, M. Cheah-Mane, E. Prieto-Araujo, and O. Gomis-Bellmunt, "Stability analysis of systems with high VSC penetration: Where is the limit?," *IEEE Trans. Power Del.*, vol. 35, no. 4, pp. 2021–2031, Aug. 2020.

- [4] P. Vorobev et al., "Deadbands, droop, and inertia impact on power system frequency distribution," *IEEE Trans. Power Syst.*, vol. 34, no. 4, pp. 3098–3108, Jul. 2019.

- [5] J. Alipoor, Y. Miura, and T. Ise, "Power system stabilization using virtual synchronous generator with alternating moment of inertia," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 3, no. 2, pp. 451–458, Jun. 2015.

- [6] A. Tayyebi, D. Groß, A. Anta, F. Kupzog, and F. Dörfler, "Frequency stability of synchronous machines and grid-forming power converters," *IEEE J. Emerg. Sel. Top. Power Electron*, vol. 8, no. 2, pp. 1004–1018, Jun. 2020.

- [7] J. Jia, G. Yang, A. H. Nielsen, and V. Gevorgian, "Investigation on the combined effect of VSC-based sources and synchronous condensers under grid unbalanced faults," *IEEE Trans. Power Del.*, vol. 34, no. 5, pp. 1898–1908, Oct. 2019.

- [8] Q. Zhong and G. Weiss, "Synchronverters: Inverters that mimic synchronous generators," *IEEE Trans. Ind. Electron.*, vol. 58, no. 4, pp. 1259–1267, Apr. 2011.

- [9] M. Ashabani, F. D. Freijedo, S. Golestan, and J. M. Guerrero, "Inducverters: PLL—Less converters with auto—synchronization and emulated inertia capability," *IEEE Trans. Smart Grid*, vol. 7, no. 3, pp. 1660–1674, May 2016.

- [10] S. Wang and K. Tomsovic, "Fast frequency support from wind turbine generators with auxiliary dynamic demand control," *IEEE Trans. Power Syst.*, vol. 34, no. 5, pp. 3340–3348, Sep. 2019.

- [11] J. Kim et al., "Super-capacitor to provide ancillary services with control coordination," *IEEE Trans. Ind. Appl.*, vol. 55, no. 5, pp. 5119–5127, Sep. 2019.

- [12] I. Serban and C. Marinescu, "Control strategy of three-phase battery energy storage systems for frequency support in microgrids and with uninterrupted supply of local loads," *IEEE Trans. Power Electron.*, vol. 29, no. 9, pp. 5010–5020, Sep. 2014.

- [13] H. Golpîra, A. R. Messina, and H. Bevrani, "Emulation of virtual inertia to accommodate higher penetration levels of distributed generation in power grids," *IEEE Trans. Power Syst.*, vol. 34, no. 5, pp. 3384–3394, Sep. 2019.

- [14] U. Bose, S. K. Chattopadhyay, C. Chakraborty, and B. Pal, "A novel method of frequency regulation in microgrid," *IEEE Trans. Ind. Appl.*, vol. 55, no. 1, pp. 111–121, Feb. 2019.

- [15] J. Fang, H. Li, Y. Tang, and F. Blaabjerg, "Distributed power system virtual inertia implemented by grid–connected power converters," *IEEE Trans. Power Electron.*, vol. 33, no. 10, pp. 8488–8499, Oct. 2018.

- [16] J. Fang, H. Li, Y. Tang, and F. Blaabjerg, "On the inertia of future moreelectronics power systems," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 7, no. 4, pp. 2130–2146, Dec. 2019.

- [17] E. Waffenschmidt, and R. S. Y. Hui, "Virtual inertia with PV inverters using DC-link capacitors," in *IEEE 18th Eur. Conf. Power Electron. Appl.*, Sep. 2016, pp. 1–10.

- [18] A. J. Agbemuko, J. L. Dominguez-Garcia, O. Gomis-Bellmunt, and L. Harnefors, "Passivity-based analysis and performance enhancement of a vector controlled VSC connected to a weak AC grid," *IEEE Trans. Power Del.*, vol. 36, no. 1, pp. 156–167, Feb. 2021.

- [19] B. Wen, D. Boroyevich, R. Burgos, P. Mattavelli and Z. Shen, "Analysis of D-Q small-signal impedance of grid-tied inverters," *IEEE Trans. Power Electron.*, vol. 31, no. 1, pp. 675–687, Jan. 2016.

- [20] Y. Huang, X. Yuan, J. Hu, and P. Zhou, "Modeling of VSC connected to weak grid for stability analysis of DC-Link voltage control," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 3, no. 4, pp. 1193–1204, Dec. 2015.

- [21] G.-C. Hsieh and J. C. Hung, "Phase–locked loop techniques|A survey," IEEE Trans. Ind. Electron., vol. 43, no. 6, pp. 609–615, Dec. 1996.

- [22] M. Rasheduzzaman, J. A. Mueller, and J. W. Kimball, "An accurate Small–Signal model of Inverter–Dominated islanded microgrids using dq reference frame," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 2, no. 4, pp. 1070–1080, Dec. 2014.

- [23] L. Harnefors, M. Bongiorno, and S. Lundberg, "Input-Admittance calculation and shaping for controlled voltage-source converters," *IEEE Trans. Ind. Electron.*, vol. 54, no. 6, pp. 3323–3334, Dec. 2007.

- [24] D. G. Holmes and T. A. Lipo, Pulse Width Modulation for Power Converters: Principles and Practice. Hoboken, NJ, USA: Wiley, 2003.

- [25] L. Fan and Z. Miao, "Admittance-based stability analysis: Bode plots, nyquist diagrams or eigenvalue analysis?," *IEEE Trans. Power Syst.*, vol. 35, no. 4, pp. 3312–3315, Jul. 2020.

- [26] P. Kundur, Power System Stability and Control, 1st ed., New York, NY, USA: McGraw-Hill, 1994.