# In-Place Evaluation of Powering and Signaling Within Fan-Out Multiple IC Chip Packaging

Hiroki Sonoda<sup>©</sup>, *Graduate Student Member, IEEE*, Ryo Kasai, Daisuke Tanaka, Yoshihide Murakami, Kyoshi Mihara, Yuuki Araga<sup>©</sup>, *Member, IEEE*, Naoya Watanabe<sup>©</sup>, *Member, IEEE*, Haruo Shimamoto<sup>©</sup>, Katsuya Kikuchi<sup>©</sup>, *Member, IEEE*, Takuji Miki<sup>©</sup>, *Member, IEEE*, and Makoto Nagata<sup>©</sup>, *Senior Member, IEEE*

Abstract—This article confirms the advantage of fan-out (FO) packaging in the electrical performance of power delivery among integrated circuit (IC) chips with the best use of land side capacitors (LSCs). On-chip in-place waveform measurements quantitatively evaluate the integrity of powering and signaling within FO wafer level packaging (FOWLP) multiple chip module (MCM) demonstrators, where a pair of IC chips are assembled with LSCs with different sizes and structures. The IC chip incorporates an array of 12 digital cores and on-chip waveform monitor (OCM) circuits. Each digital core consists of a low-voltage differential signaling (LVDS) transceiver channel that is backed by a static random access memory (SRAM)-based builtin self test (BIST) module and supplied by an on-chip voltage regulator module (VRM). The LSCs are placed on the bottom side of an FO interposer and inserted between the output of VRM and the ground plane almost ideally with the shortest length of physical traces. A Si membrane capacitor of 10 nF sustains the lowest power line impedance over the frequency range of 2.0 GHz more constantly than a multilayer ceramic counterpart, and attenuates the high-order harmonic frequency components to the clocking frequency at 750 MHz. The leverage of LSCs in powering also improves signaling and helps achieve the wider eye openings in LVDS channels. The implications are elaborated for the capacitor selections with respect to the physical types of capacitors, the size of capacitances, and the level of shares in power delivery among digital cores, all toward the higher level of integrity in powering and signaling in FOWLP MCMs.

Index Terms—Fan-out (FO) packaging, low-voltage differential signaling (LVDS), multichip module, on chip monitoring, power delivery network (PDN), power integrity, power noise, signal integrity, Si capacitor (SiCap).

Manuscript received 20 April 2022; accepted 23 May 2022. Date of publication 30 May 2022; date of current version 26 July 2022. Recommended for publication by Associate Editor B. Vaisband upon evaluation of reviewers' comments. (Corresponding author: Hiroki Sonoda.)

Hiroki Sonoda, Takuji Miki, and Makoto Nagata are with the Graduate School of Science, Technology and Innovation, Kobe University, Kobe 657-8501, Japan (e-mail: sonoda@cs26.scitec.kobe-u.ac.jp; miki@cs26.scitec.kobe-u.ac.jp; nagata@cs.kobe-u.ac.jp).

Ryo Kasai, Daisuke Tanaka, Yoshihide Murakami, and Kyoshi Mihara are with Murata Manufacturing Company Ltd., Kyoto 617-8555, Japan (e-mail: ryo.kasai@murata.com; d\_tanaka@murata.com; murakami@murata.com; mh@murata.com).

Yuuki Araga, Naoya Watanabe, Haruo Shimamoto, and Katsuya Kikuchi are with the National Institute of Advanced Industrial Science and Technology (AIST), AIST Tsukuba Headquarters, Tsukuba, Ibaraki 305-8560, Japan (e-mail: yuuki.araga@aist.go.jp; naoya-watanabe@aist.go.jp; haruo.shimamoto@aist.go.jp; k-kikuchi@aist.go.jp).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TCPMT.2022.3179149.

Digital Object Identifier 10.1109/TCPMT.2022.3179149

#### I. Introduction

DVANCED packaging has evolved to accommodate mul-A tiple integrated circuit (IC) chips for unifying various functionality into a system in the form of multiple chips in a module (MCM). The demand is further extended for heterogeneously integrating multiple chiplets that are individually developed using suitable device technologies and supplied by associated semiconductor fabs. 3-D IC chip (3DIC) stacking [1]–[6] and fan-out (FO) wafer level packaging (FOWLP) [7]–[10] technologies have been extensively explored. Both of them fulfill the advanced packaging toward the higher performance and a smaller footprint as well as a lower profile. Stakeholders can share the cost of manufacturing and disperse the risk of investments, even tracking the level of integration under Moore's law that is continuously required by applications. Photonics and electronics integration [11] deploying FOWLP MCM achieves the high data bandwidth in a system where multiple chips of processors, memories, and opto-electronic interfaces are tightly connected. A machine learning device [12] uses FOWLP to unite IC chips for neural-network processing and memory and further exploits 3DIC for a high-density imaging chip to be placed on the top surface [13]. Those applications demand the design of MCM systems to strive for high data bandwidths, stable power supplies, and the maximized power efficiency all around IC chips.

To achieve the goal of system-level performance, the integrity in signaling and powering appears to be a challenge in practically implementing MCM devices with advanced packaging [14]-[18]. Once IC chips are assembled in a package, their power and signal lines are unified horizontally within membranes of an interposer or vertically through the Si substrate of IC chips, and fundamentally inaccessible by external measurement equipment. Chip-package-system board integrated simulation can provide analytical insights of internal states once models are properly prepared for electronic components including IC chips [19]–[21]. Packaging materials are electrically characterized for modeling passive impedance [22], [23]. The simulation concatenates the passive models and active circuits to solve dynamic behaviors of powering and signaling. Here, the accuracy of simulation remains being concerned by designers and needs to be confirmed or even

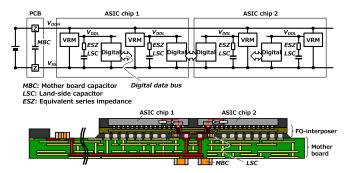

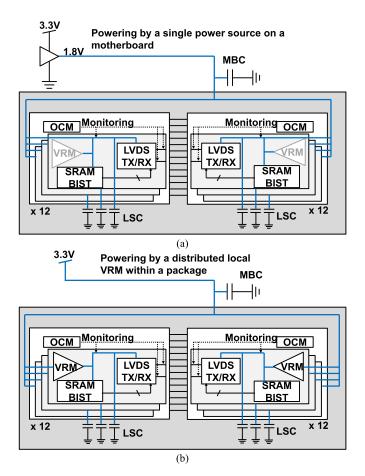

Fig. 1. MCM architecture in schematic (top) and in FO physical structure (bottom).

calibrated by the measurements on test devices with reference structures.

The 3DIC demonstrators have been developed and characterized [14], [24] and referred to the superiority of power noise mitigation and signaling performance. Those are attributed naturally to the construction of 3DIC stacks with vertically distributed capacitors among power delivery networks (PDNs) [25], [26]. The benefits of embedded capacitors in FOWLP devices were also exhibited by monitoring power and signal waveforms [27], [28]. The implications with the different property of interposers have been relevantly discussed with the same device architecture but integrated on a Si passive interposer differently from the fan-out one, which should be referred to [29]. Here, our demonstration was self-explanatory but limited only to qualitative observations in the previous reports, which were insufficient to discuss the selection of capacitors in the design of a PDN.

In this article, the electronic performance of PDN is precisely and quantitatively evaluated in FOWLP devices through on-chip measurements and equivalent circuit simulation. It is shown that the electrical impedance of power delivery can be strategically planned in a fan-out (FO) structure with the best use of land side capacitors (LSCs) with smaller series impedance that benefits from the very short connecting paths in nature to the stacked membranes in an FO structure. The implications of capacitor selections in the design of FOWLP MCM devices are elaborated through the in-place evaluation of power and signal integrity (PI and SI), for the first time.

The rest of this article is organized as follows. Section II describes FOWLP MCM demonstrators and associated experimental setups for in-place power noise and signal waveform measurements. Section III evaluates the electrical performance of powering and signaling and then discusses the design strategy of FOWLP MCMs with LSC selections. Section IV concisely provides conclusions.

## II. FOWLP MCM DEMONSTRATOR

# A. MCM Architecture

The MCM architecture of Fig. 1 is exemplified with two application-specific IC (ASIC) chips having multiple digital cores and being encapsulated in FO assembly. This architecture is intended for the PI and SI evaluation of a typical digital IC chip. An external high supply voltage,  $V_{\rm DDH}$ , is converted by a voltage regulator module (VRM) into the local supply

voltage  $V_{\rm DDL}$  for digital circuits in each power domain. Digital signals are communicated over a chip-to-chip digital data bus using physical layer signaling schemes such as low-voltage differential signaling (LVDS). The electrical performance of PDNs fundamentally influences PI and SI, where a designer needs to carefully choose and locate capacitors throughout the physical structure of system-level FO assembly.

The chips are faced down on the FO interposer and their bumps on pads are connected to the wires patterned over metal layers in the interposer. The entire MCM in a ball-grid array (BGA) is then mounted on a mother printed circuit board (PCB). The LSCs are mounted in the backside of the MCM with the shortest length of physical traces to the associated pads of an IC chip. In addition, mother board capacitors (MBCs) are mounted on the PCB at multiple locations of the system-level PDN for decoupling.

# B. MCM Demonstrator With Test IC Chip

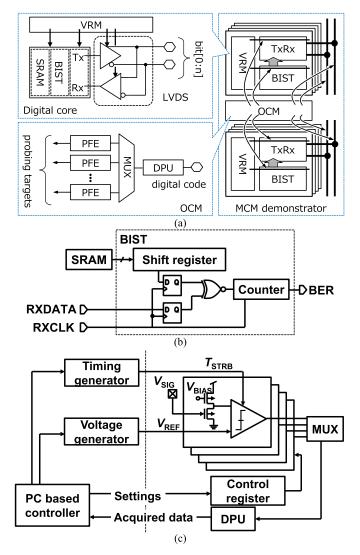

We have prepared FO MCM demonstrators for the present study. The block diagram is given in Fig. 2(a). The demonstrator consists of the tile of digital cores involving LVDS channels with transmitter (Tx) and receiver (Rx) circuits, and static random access memory (SRAM)-based built-in self test (BIST) logic core circuits, all supplied by a dedicated VRM. In addition, the on-chip waveform monitoring (OCM) circuits are equipped for in-place PI and SI evaluation among the digital cores.

The VRM down converts the external voltage of 3.3 V into the internal digital core voltage of 1.8 V, which is locally stabilized by the dedicated capacitor, LSC.

The Tx drives the outgoing differential signals. The Rx vice versa receives and converts the incoming differential ones to the rectangular signal of bit streaming. The BIST core circuits of Fig. 2(b) continuously check the consistency between incoming received data (RXDATA) and expected data prestored in SRAM at the rate of received data clock (RXCLK). The number of inconsistent bits is counted in a bitwise way and then read by an external checker as the data bit error rate (BER).

The OCM circuits includes probing front end (PFE) modules for sensing individual analog voltage signals at respective probe inputs and a data processing unit (DPU) for digitizing voltage waveforms after a multiplexer (MUX) [29], [30]. The PFE module of OCM system, Fig. 2(c), senses  $V_{SIG}$  by a source follower (SF), and immediately compares its output voltage to the reference one,  $V_{REF}$ , by a latched comparator (LC) at the strobe timing  $T_{STRB}$ . External voltage and timing generators provide  $V_{REF}$  and  $T_{STRB}$ , respectively. The SF internally provides an offset dc voltage to  $V_{SIG}$  in order to match the input voltage range of the LC. This allows the PFE to effectively capture the  $V_{SIG}$  of interest in a rail-to-rail voltage range, namely, from the ground voltage to the power supply voltage. The single bit stream from the comparator is given to MUX. The probe selection is set through on-chip registers. The waveform data acquisitions are fully controlled by the software running on an off-chip computer (PC).

Fig. 2. Block diagrams of (a) MCM demonstrator, (b) BIST core circuit, and (c) OCM system.

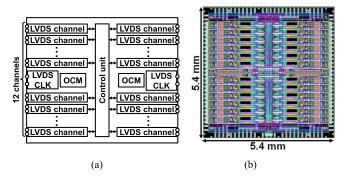

Fig. 3. Test chip overview. (a) Block diagram. (b) Chip layout.

The digital cores, represented by LVDS transceiver channels, are integrated on a silicon prototype chip shown in Fig. 3. Each left and right side of the chip holds 12 LVDS data channels that are managed by a central control unit. Another LVDS clock channel receives and drives the clock (CLK) signal that is shared by the data channels over multiple chips for synchronization. The chip has the area size of 5.4 mm  $\times$  5.4 mm and uses a 0.18-m standard CMOS technology.

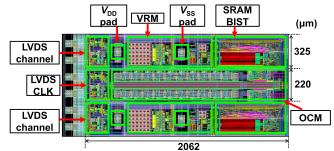

Fig. 4. Physical layout view of LVDS channels featured by in-place waveform capturing [27].

An in-place power and signal waveform capturing macro is realized with OCM circuits and aligned to adjacent LVDS channels in their physical layout, as shown in Fig. 4. The macro has the total of 20 PFE modules uniformly arrayed in two sides and associated probe wirings drawn to the nearest points of interest within respective LVDS channels. These points to capture waveforms include the plus and minus nodes of signaling, power supply, and ground nodes around SRAM and BIST digital cores as well as the output of VRM. There are pads for bumps to be connected to membrane metallic traces on the FO interposer for LVDS channels and CLK signals as well as  $V_{\rm DD}$  and ground ( $V_{\rm SS}$ ).

# C. MCM Demonstrator With Capacitors

The block diagrams of MCM demonstrators are given in Fig. 5. The identical chips are horizontally placed in a face-to-face way and the 12 data and one clock LVDS channels are one-to-one connected. We prepare two configurations in power delivery for exploring the effect of capacitors. The exploratory version of Fig. 5(a), where a single on-board power converter supplies every circuit in the MCM with the support of MBCs while on-chip VRMs are fully cut off and bypassed. In contrast, the main version of Fig. 5(b) utilizes on-chip VRMs locally powering circuits among the LVDS channels. The OCM circuits are powered by the dedicated PDNs and isolated from LVDS channels, in both versions.

We have manufactured the MCM demonstrators with nine different variations of electrical parameters, as listed in Table I, including the exploratory versions [see Fig. 5(a)] without and with LSC, and the main versions [see Fig. 5(b)] with different physical structures and sizes of LSCs. The main versions have some other variations where more than one LVDS channels are bundled and powered by a single VRM selected from the bundle, where the other VRMs are turned off. The LSCs are chosen from the structures of multilayer ceramic capacitor (MLCC) and Si capacitor (SiCap). The electrical parameters in Table II highlight the properties of MLCC and SiCap. The electrical series resistor (ESR) and inductor (ESL) are derived at the self-resonance frequency ( $F_{res}$ ) and represented at the frequency of 1 GHz, respectively. The dielectric constant (Dk) and dissipation factor (Df) are assumed to be 4.4 and 0.02, respectively, in our FO interposer. These numbers are used in the simulation of electrical impedance in Section III.

Fig. 5. Block diagram of demonstrators with different powering schemes. (a) Exploratory and (b) main versions.

TABLE I

MCM DEMONSTRATOR VARIATIONS. EXPLORATORY (EXP.) AND

MAIN VERSIONS FOLLOW PDN CONFIGURATION IN

FIG. 5(A) AND (B), RESPECTIVELY

| MCM<br>demonstrator | Number of channels / VRM | LSC type | LSC size<br>(nF) | PDN configuration |

|---------------------|--------------------------|----------|------------------|-------------------|

| demonstrator        | CHAIIIIEIS / VIXIVI      |          | (1111 )          | Configuration     |

| #1                  | -                        | No сар.  |                  | Exp. (Fig. 5a)    |

| #2                  | -                        | MLCC     | 1                | Exp. (Fig. 5a)    |

| #3                  | 6                        | MLCC     | 10               | Main (Fig. 5b)    |

| #4                  | 6                        | SiCap    | 10               | Main (Fig. 5b)    |

| #5                  | 1                        | No Cap   | -                | Main (Fig. 5b)    |

| #6                  | 1                        | MLCC     | 3.9              | Main (Fig. 5b)    |

| #7                  | 1                        | MLCC     | 10               | Main (Fig. 5b)    |

| #8                  | 3                        | MLCC     | 3.9              | Main (Fig. 5b)    |

| #9                  | 1                        | MLCC     | 1                | Main (Fig. 5b)    |

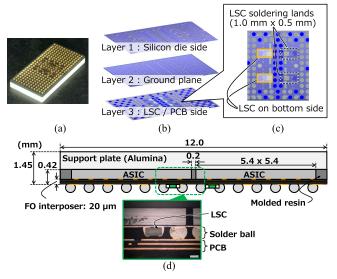

The top and cross section views of the manufactured FOWLP MCM are shown in Fig. 6. The ASIC chips are faced down on the FO interposer while being attached to an alumina plate on the die backside [see Fig. 6(a)]. The MCM module has the external area size of  $12.0~\text{mm} \times 6.0~\text{mm}$  and the height of 1.45~mm excluding the ball diameter of nominally  $50~\mu\text{m}$ . The space between ASIC chips is around 0.2~mm. Three membrane layers are, respectively, patterned for metal wirings and formed in the interposer [see Fig. 6(b)], with each thickness of  $4~\mu\text{m}$ , for the following purposes; Layer 1: the pads to be connected to the bumps of ASIC chips and associated power and signal

TABLE II LSC ELECTRICAL PARAMETERS.

| MCM<br>demonstrator | LSC type | LSC size<br>(nF) | ESR*1<br>(Ohm) | ESL*2<br>(nH) |

|---------------------|----------|------------------|----------------|---------------|

| #3                  | MLCC     | 10               | 0.12           | 0.37          |

| #4                  | SiCap    | 10               | 0.28           | 0.16          |

|                     |          |                  | *1at F         | *2at 1 GHz    |

Fig. 6. MCM demonstrator in FOWLP (a) top view, (b) FO membrane layers' image, (c) LSC soldering location on bottom side, and (d) cross section view.

lines, Layer 2: the whole areas dedicated to the ground plane, and Layer 3: the lands to mount LSCs and the pads for balls connecting to PCB, respectively. The total thickness of the interposer is approximately 20  $\mu$ m.

The LSCs are soldered on the bottom side of the FO interposer with the lands customized to fit the external size of the capacitors. The footprint of LSC shown in Fig. 6(c) is  $1.0 \text{ mm} \times 0.5 \text{ mm}$  for the MCM demonstrators #3 and #4. The LSC is mounted on the bottom side of the interposer and finely concealed within the ball diameter [see Fig. 6(d)]. This allows the die pad of VRM output to be located in the almost same place of the land to LSC and minimizes the physical length of power supply trace, which is 0.83 mm including metal routings and balls. The other land of LSC is connected to the ground plane of the interposer with the physical trace length of 0.95 mm. In comparison, the length from the power pad of IC chips to the land of MBC becomes as large as 3.39 mm that is mostly dominated by the metal routings on the mother PCB with the total height of 1.57 mm, in the MCM demonstrator #1 for direct powering without VRM [see Fig. 5(a)].

# D. Experimental Setup

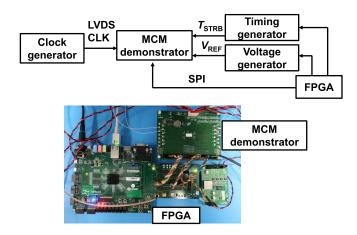

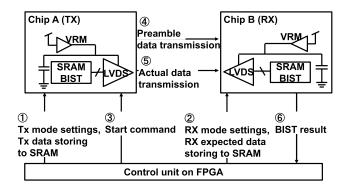

The whole experimental setup shown in Fig. 7 is fully automated, according to the measurement sequence of Fig. 8. A photo is also given and shows its compactness. The field-programmable gate array (FPGA) device intermediates the transactions between the software on PC and the MCM demonstrator as well as the generators of  $V_{\rm REF}$  and  $T_{\rm STRB}$ .

Fig. 7. Experimental setup.

Fig. 8. Experimental measurement sequence.

An external clock generator provides the system clock through LVDS CLK channel.

There are several registers for commanding measurements in the sequence (1, 2, 3, and 6 in Fig. 8), which are written and read between the demonstrator and FPGA through serial-parallel interface (SPI). The OCM probe selections are similarly led by additional registers in the analog power domain dedicated to the OCM system. Data bits are prestored to the SRAM core on one of the chips that is set in Tx mode. The same data are also stored to the other one in Rx mode for BIST operation. Once the sequence is triggered, the data transmission starts with preambles and then repeats with the prestored data. The BIST results are also collected. The waveform acquisition by the OCM proceeds in parallel, where  $T_{\text{STRB}}$  to sample the voltage waveform of interest moves incrementally forward with the time step of  $\Delta T$  in every iteration of the transmission. In contrast,  $V_{REF}$  in the voltage comparison also increases with the increment of  $\Delta V$  to search the nearest voltage. In the present setup,  $\Delta V$  and  $\Delta T$  are set to be 100  $\mu$ V and 100 ps, respectively, which determine the resolution of waveform capturing. The waveform acquisition algorithm associated with the OCM circuits has been explored [30], [31] and utilized for the in-place waveform-based evaluation of undesired noise coupling in automotive IC chips [32], [33]. Here, our MCM demonstrator adopts this technique in a customized way to evaluate the powering and signaling within the FO interposer featuring stacked membrane layers and proximate LSCs.

Fig. 9. On-chip power supply and signal waveforms during LVDS data transmission [27].

#### III. EXPERIMENTS

# A. On-Chip Captured Waveforms

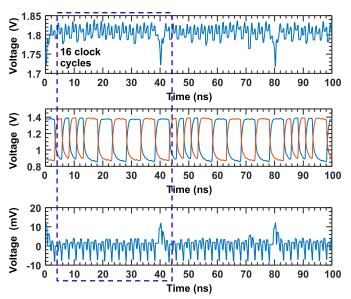

The waveforms in-place captured on the power supply  $(V_{\rm DD})$ , differential signaling  $(V_{\rm SIG+}, V_{\rm SIG-})$ , and ground  $(V_{SS})$  nodes are exemplified in Fig. 9. The all 12 LVDS channels are synchronously transmitting 16-bit (2-byte) data of "1010110011001100" with the LVDS CLK frequency at 400 MHz. One of the LVDS channels adjacent to the on-chip waveform acquisition macro is measured. The powering nodes exhibit the periodic voltage variations of roughly 40 mV and 10 mV for  $V_{\rm DD}$  and  $V_{\rm SS}$ , respectively, that are regularly seen with the interval of 1.25 ns due to the power current consumption of logic circuits at either rise or fall edge of clocking. There is an additional large drop in every 16 clock cycles, according to the access to SRAM cores for reading 2-byte data to send (in Tx side) or to compare (in Rx side). The simultaneous occurrence of drops among  $V_{\rm DD}$  and  $V_{\rm SS}$  is the natural consequence of power current flowing in the core PDN. The differential signaling also exhibits clear transitions associated with the bit sequence. The vertical axes are calibrated in advance with regard to the offset voltage and voltage gain.

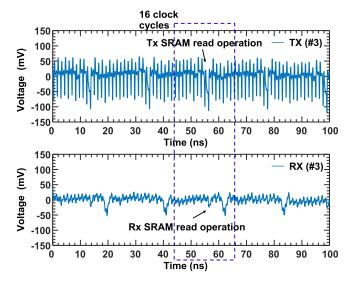

The power supply waveforms are compared in Fig. 10 on the individual  $V_{\rm DD}$  nodes of the two chips in Tx and Rx operation modes, respectively, within the MCM demonstrator (#3). The LVDS channels operate at 750 MHz, which is the highest operating frequency with no erroneous bit found in the BIST outputs over the time of OCM waveform measurements. The higher level of voltage peaks is seen in the Tx than in the Rx mode, since the Tx circuits drive signal lines between the chips over interposer laminates. The Rx circuits receives the incoming signals regenerate digital data under the presence of power noise. We focus on the Rx mode in the following measurements.

Fig. 10. Power noise waveforms in Tx and Rx operation.

Fig. 11. Power noise suppression by capacitors. (a) No capacitor, (b) with MBCs, and (c) with MBCs and LSCs.

# B. Power and Signal Integrity

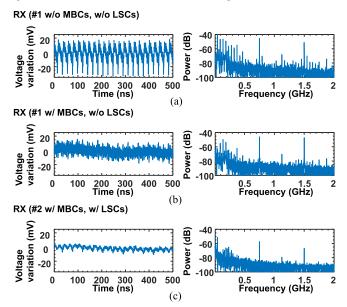

The power supply voltage variations are compared among the MCM demonstrators with different capacitor configurations, as shown in Fig. 11. The MCM demonstrator (#1, #2) in the exploratory version [see Fig. 5(a)] is tested in the different combinations of with and without MBCs and LSCs. The frequency-domain analysis results are also plotted, which are in general dominated mainly by the 1st and 2nd harmonic components of the clock frequency at 750 MHz. While the demonstrator without any PDN capacitors gives the largest voltage variations in the frequency below 750 MHz [see Fig. 11(a)], the variations become slightly attenuated if MBCs with the total capacitance of 1.2  $\mu$ F are provided on the PCB [see Fig. 11(b)]. The power supply voltage becomes very much stabilized with LSCs [see Fig. 11(c)], which is explained by the proximate position of LSCs to the source of power current consumption among LVDS channels.

Fig. 12. Power noise waveforms and signal eye diagrams.

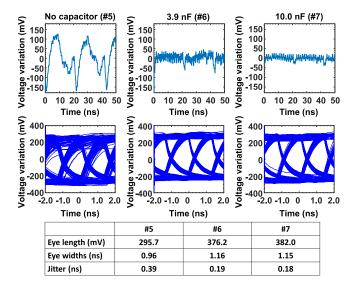

The effect of LSC is further examined in Fig. 12 for powering and signaling among the MCM demonstrators (#5, #6, and #7) in the main version [see Fig. 5(b)] using VRMs. The waveforms in the Rx mode are captured on the internal  $V_{\rm DD}$  pad as the output of VRM to be connected to LSC and also the signal pads of  $V_{\rm SIG+}$  and  $V_{\rm SIG-}$ . While the power supply voltage variation is more attenuated with the larger size of LSC capacitors, synchronously, the signaling eye diagram becomes clearer. The size of eye openings as well as the time width of jitters are summarized in the table.

The VRM makes the PDN of LVS channel isolated from the other PDNs and also decoupled from the on-board part of power delivery. The LSC becomes the necessary part for an on-chip VRM to suppress power noise spikes in its isolated power domain.

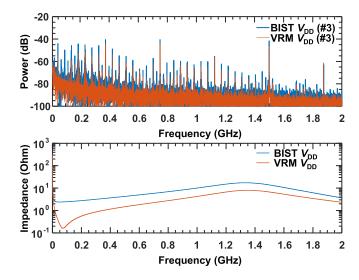

The voltage variations on the  $V_{\rm DD}$  pad as the output of VRM are compared with those on the other  $V_{\rm DD}$  node located nearby the BIST circuits, for the frequency–domain components of Fig. 13. Both nodes have the relative distance of approximately 900  $\mu$ m in the physical layout of LVDS channel (see Fig. 4). The magnitude of frequency components becomes large in the distant location from the output terminal of VRM, roughly from +3 to +6 dB over the frequency range of 2.0 GHz. We have also simulated the series impedance on the power line from the land of LSC to the pad in the LVDS channel for the same frequency range. There is a consistency between the larger series impedance and the higher magnitude of frequency components in the voltage variation. The proximate placement of LSCs is suggested for the superior noise attenuation and the better signal quality.

# C. Design Exploration

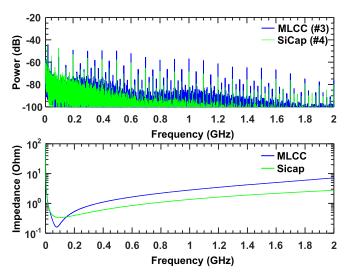

The selection of capacitor physical types is explored with the waveforms on the  $V_{\rm DD}$  pad as the output of VRM when the LVDS channels operate at 100 MHz. The frequency components are compared between the MCM demonstrators (#3 and #4) in the main version with MLCC and SiCap of equally 10 nF, as shown in Fig. 14 for the frequency range

Fig. 13. Comparison of power noise components at VRM (top). Power line impedance is also shown by simulation (bottom).

Fig. 14. Comparison of MLCC and SiCap for power noise suppression (top). The clocking frequency is fixed at 100 MHz. Power line impedance is also shown by simulation (bottom).

of 2.0 GHz. The power line impedance is also simulated with equivalent circuits. It is clearly observed that the power voltage variations follow the impedance trends of respective capacitor types. The smaller electronic series inductance (ESL) inherently to SiCap provides the continuous attenuation in a broad frequency range, while the smallest impedance gives the highest suppression by MLCC but only within the spot frequency of its resonance.

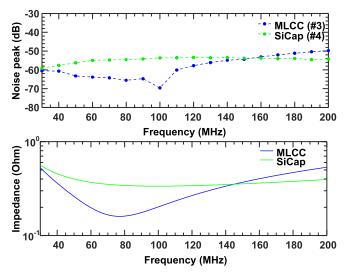

The follow-up measurements are executed in Fig. 15 where the LVDS channels operate at different frequencies from 15 to 100 MHz. The largest frequency components, which are often seen at the twice clocking frequency owing to rise and fall transitions, are compared among MLCC and SiCap types. The obvious trends again confirm the influence of the wide frequency impedance, ESZ, parasitic to capacitors.

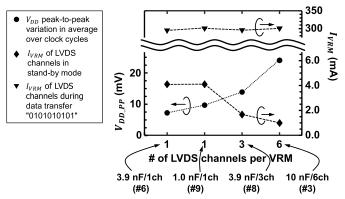

The impact of the number of LVDS channels powered by a single VRM is investigated in Fig. 16, where the in-place

Fig. 15. Comparison of MLCC and SiCap for power noise suppression at different operating frequencies (top). The largest frequency components at  $2\times$  of clocking frequency are plotted. Power line impedance is also shown by simulation (bottom).

Fig. 16. Comparison of power noise and power current for different number of LVDS channels per VRM.

waveforms on the  $V_{\rm DD}$  pad as the output of VRM are evaluated. The peak-to-peak voltage variation is averaged over clock cycles and denoted as  $V_{\rm DD\_PP}$ , during the data transmission among 12 LVDS channels at 750 MHz with the largest bit activities of "0101010101010101." The  $V_{\rm DD\ PP}$  is minimized if every LVDS channel is powered by its dedicated VRM, where a single LSC is also exclusively prepared. The smaller  $V_{\rm DD\_PP}$ is observed for the larger capacitance if we compare #6 and #9. The  $V_{\rm DD\ PP}$  enlarges with the number of LVDS channels that share a single VRM and an associated LSC, where the capacitance per an LVDS channel is chosen to be roughly equal to the order of 1 nF among the demonstrators (#3, #8, and #9). The  $V_{\rm DD\ PP}$  becomes roughly 2.5 times larger in #3 than in #9. Here, the tradeoff needs to be taken into account between the power integrity and power consumption. The total power supply current among VRMs,  $I_{VRM}$ , is also measured in Fig. 16 (on the right axis) and compared among the demonstrators. The quiescent  $I_{VRM}$  simply increases with the number of VRMs when LVDS channels are all in the stand-by mode (no data transmission). In contrast, the  $I_{VRM}$  becomes almost constant accordingly to bit activities, independently of the number of channels supplied by the single VRM (with sufficient power current capacity).

It is reasonable to share a single VRM by some LVDS channels in low-power applications often provided with intermittent operation modes. In contrast, a per-channel VRM with dedicated LSCs is preferable to prioritize the power and signal integrity in high-performance data storage and server applications, where data transmission is active almost all the time. We think that the demonstrator #3 represents the one best point of design explorations with the power noise reduction, power current consumption, the number of components, and associated footprints [see Fig. 6(c)].

## IV. CONCLUSION

Powering and signaling among digital cores were in-place evaluated by using OCM circuits within MCM integration in FOWLP assembly. The digital cores in a system-on-chip integration were represented by the array of multichannel LVDS transceivers with SRAM-based BIST functionality for chip-to-chip data communication.

Power and signal waveforms were not observable from the outside of IC chips in flip-chip assembly, which excluded the quantitative measurements of the electronic performance of PDN. This problem was solved by the construction of MCM demonstrators in this article.

The superiority of power noise suppression is proven in FOWLP thanks to the LSC proximately placed at the output of VRM and the immediate bottom side of FO interposer, providing the shortest length of physical power delivery traces. This benefits clearly from the selection of lower equivalent series impedance (ESZ) capacitors. These implications came only from the given in-place evaluation with the support of equivalent circuit simulation and were elaborated for the careful capacitor selections and placements in the design of FOWLP MCMs toward the higher level of PI and SI.

It is quantitatively shown that the leverage of LSCs in the FO PDN well suppresses power voltage variations in the wide frequency range of 2.0 GHz when LVDS channels operate at 750 MHz. This also improves signaling with the wider eye openings in LVDS. The SiCap of 10 nF sustains the effectiveness over the full frequency range, and better than MLCC overall, due to low ESR and ESL to the capacitor itself and also to the membrane wirings on an FO interposer. The attenuation was confirmed even for the high order harmonic components up to 20th to the clock frequency at 100 MHz, as well as that for the primary frequency components at various clock frequencies up to 100 MHz. The equivalent circuit simulation supports the results.

Further explorations beyond our experiments in this article will be pursued for the co-design flow of PDN on FOWLP MCM devices among the circuits on a chip, structures in the FO interposer, and the selection and placement of discrete electronic components. The equivalent circuit simulation needs to be more capable of handling all the components and to be desirably calibrated with physical test vehicles.

#### REFERENCES

J. U. Knickerbocker et al., "3-D silicon integration and silicon packaging technology using silicon through-vias," *IEEE J. Solid-State Circuits*, vol. 41, no. 8, pp. 1718–1725, Aug. 2006.

- [2] J. Van Olmen et al., "3D stacked IC demonstration using a through silicon via first approach," in IEDM Tech. Dig., Dec. 2008, pp. 303–306.

- [3] P. Garrou, C. Bower, and P. Ramm, Eds., Handbook of 3D Integration: Technology and Applications of 3D Integrated Circuits. Hoboken, NJ, USA: Wiley, 2008.

- [4] G. Van der Plas et al., "Design issues and considerations for low-cost 3-D TSV IC technology," *IEEE J. Solid-State Circuits*, vol. 46, no. 1, pp. 293–307, Jan. 2011.

- [5] P. Garrou, M. Koyanagi, and P. Ramm, Eds., Handbook of 3D Integration: 3D Process Technology. Hoboken, NJ, USA: Wiley, 2014.

- [6] P. D. Franzon, E. J. Marinissen, and M. S. Bakir, Eds., Handbook of 3D Integration: Design, Test, and Thermal Management. Hoboken, NJ, USA: Wiley, 2019.

- [7] S. W. Yoon, A. Bahr, X. Baraton, P. C. Marimuthu, and F. Carson, "3D eWLB (embedded wafer level BGA) technology for 3D-packaging/3D-SiP (systems-in-package) applications," in *Proc. 11th Electron. Packag. Technol. Conf.*, Dec. 2009, pp. 915–919.

- [8] C. C. Liu et al., "High-performance integrated fan-out wafer level packaging (InFO-WLP): Technology and system integration," in IEDM Tech. Dig., Dec. 2012, pp. 14.1.1–14.1.4.

- [9] J. H. Lau et al., "Fan-out wafer-level packaging for heterogeneous integration," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 8, no. 9, pp. 1544–1560, Sep. 2018.

- [10] B. Keser and S. Krohnert, Eds., Advances in Embedded and Fan-Out Wafer Level Packaging Technologies. Hoboken, NJ, USA: Wiley, 2019.

- [11] H. Uemura et al., "Backside optical i/o module for Si photonics integrated with electrical ICs using fan-out wafer level packaging technology," in Proc. IEEE 68th Electron. Compon. Technol. Conf. (ECTC), May 2018, pp. 822–827.

- [12] M. D. Rotaru, W. Tang, D. Rahul, and Z. Zhang, "Design and development of high density fan-out wafer level package (HD-FOWLP) for deep neural network (DNN) chiplet accelerators using advanced interface bus (AIB)," in *Proc. IEEE 71st Electron. Compon. Technol. Conf. (ECTC)*, Jun. 2021, pp. 1258–1263.

- [13] T. Yamazaki et al., "A 1ms high-speed vision chip with 3D-stacked 140GOPS column-parallel PEs for spatio-temporal image processing," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 82–83.

- [14] I. Savidis, S. Kose, and E. G. Friedman, "Power noise in TSV-based 3-D integrated circuits," *IEEE J. Solid-State Circuits*, vol. 48, no. 2, pp. 587–597, Feb. 2013.

- [15] J. Roullard *et al.*, "Evaluation of 3D interconnect routing and stacking strategy to optimize high speed signal transmission for memory on logic," in *Proc. IEEE 62nd Electron. Compon. Technol. Conf.*, May 2012, pp. 8–13.

- [16] S. Takaya et al., "A 100GB/s wide I/O with 4096b TSVs through an active silicon interposer with in-place waveform capturing," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2013, pp. 434–435.

- [17] C.-T. Wang and D. Yu, "Signal and power integrity analysis on integrated fan-out PoP (InFO\_PoP) technology for next generation mobile applications," in *Proc. IEEE 66th Electron. Compon. Technol. Conf. (ECTC)*, May 2016, pp. 380–385.

- [18] S.-H. You et al., "Advanced fan-out package Si/PI/thermal performance analysis of novel RDL packages," in Proc. IEEE 68th Electron. Compon. Technol. Conf. (ECTC), May 2018, pp. 1295–1301.

- [19] E. Kulali, E. Wasserman, and J. Zheng, "Chip power model—A new methodology for system power integrity analysis and design," in *Proc. IEEE Electr. Perform. Electron. Packag.*, Oct. 2007, pp. 259–262.

- [20] J. Xu et al., "A novel system-level power integrity transient analysis methodology using simplified CPM model, physics-based equivalent circuit PDN model and small signal VRM model," in Proc. IEEE Int. Symp. Electromagn. Compat., Signal Power Integrity (EMC+SIPI), Jul. 2019, pp. 205–210.

- [21] H. Suenaga, A. Tsukioka, K. Jike, and M. Nagata, "Compact simulation of chip-to-chip active noise coupling on a system PCB board," *IEEE Lett. Electromagn. Compat. Pract. Appl.*, vol. 2, no. 1, pp. 15–20, Mar. 2020.

- [22] Q. Wang et al., "Modeling optimization of test patterns used in deembedding method for through silicon via (TSV) measurement in silicon interposer," in Proc. IEEE Int. Symp. Electromagn. Compat. (EMC), Jul. 2016, pp. 412–417.

- [23] L. T. Guan, C. K. Fai, and D. H. S. Wee, "FOWLP electrical performances," in *Proc. IEEE 18th Electron. Packag. Technol. Conf. (EPTC)*, Nov. 2016, pp. 79–84.

- [24] Y. Araga et al., "Measurements and analysis of substrate noise coupling in TSV based 3D integrated circuits," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 4, no. 6, pp. 1026–1037, Jun. 2014.

- [25] M. Nagata, S. Takaya, and H. Ikeda, "In-place signal and power noise waveform capturing within 3-D chip stacking," *IEEE Design Test*, vol. 32, no. 6, pp. 87–98, Dec. 2015.

- [26] K. Monta et al., "3-D CMOS chip stacking for security ICs featuring backside buried metal power delivery networks with distributed capacitance," *IEEE Trans. Electron Devices*, vol. 68, no. 4, pp. 2077–2082, Apr. 2021

- [27] H. Sonoda et al., "In-place power noise and signal waveform measurements on LVDS channels in fan-out multiple IC chip packaging," in Proc. 12th Int. Workshop Electromagn. Compat. Integr. Circuits (EMC Compo), Oct. 2019, pp. 1–3.

- [28] H. Sonoda et al., "Power noise suppression by land-side capacitors within fan-out multiple IC chip packaging," in Proc. IEEE Int. Symp. Electromagn. Compat., Signal Power Integrity (EMC+SIPI), Aug. 2020, p. 1.

- [29] Y. Araga et al., "Landside capacitor efficacy among multi-chip-module using Si-interposer," *IEICE Electron. Exp.*, vol. 18, no. 9, May 2021, Art. no. 20210070.

- [30] K. Noguchi and M. Nagata, "An on-chip multichannel waveform monitor for diagnosis of systems-on-a-chip integration," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 15, no. 10, pp. 1101–1110, Oct. 2007.

- [31] T. Hashida and M. Nagata, "On-chip waveform capture and application to diagnosis of power delivery in SoC integration," *IEEE J. Solid-State Circuits*, vol. 46, no. 4, pp. 789–796, Apr. 2011.

- [32] A. Murata et al., "Noise analysis using on-chip waveform monitor in bandgap voltage references," in Proc. 9th Int. Workshop Electromagn. Compat. Integr. Circuits (EMC Compo), Dec. 2013, pp. 226–231.

- [33] K. Taniguchi et al., "Susceptibility evaluation of CAN transceiver circuits with in-place waveform capturing under RF DPI," in Proc. 11th Int. Workshop Electromagn. Compat. Integr. Circuits (EMCCompo), Jul. 2017, pp. 59–63.

**Hiroki Sonoda** (Graduate Student Member, IEEE) received the B.S. degree in engineering and the M.S. degree in science, technology, and innovation from Kobe University, Kobe, Japan, in 2018 and 2020, respectively, where he is currently pursuing the Ph.D. degree.

His research interests include low-impedance packaging techniques and hardware security.

**Ryo Kasai** received the B.S. and M.S. degrees from Aoyama Gakuin University, Tokyo, Japan, in 2000 and 2002, respectively.

He joined Ink Jet Printer Business Unit, Canon, Inc., Tokyo. He had been engaged over 17 years in the development of semiconductor circuit design for inkjet printheads. He is currently an Application Engineer with Murata Manufacturing Company Ltd., Yokohama, Japan. His research focuses on low-impedance package design using MLCC.

**Daisuke Tanaka** received the B.E. and M.E. degrees in electrical and electronic engineering from Okayama University, Okayama, Japan, in 2003 and 2005, respectively.

Since 2005, he has been with Murata Manufacturing Company Ltd., Kyoto, Japan, where he has been responsible for the research and development of EMI components, development of high-density capacitors for various applications, and power integrity design with using low-ESL capacitor.

Yoshihide Murakami received the B.E. degree in mechanical engineering from the Musashi Institute of Technology, Tokyo, Japan, in 1991.

Since 1991, he has been with Murata Manufacturing Company Ltd., Kyoto, Japan, where he has been responsible for the engaged in board design of RF and WiFi modules, and since 2008, power integrity design with using low-ESL capacitor.

**Kyoshi Mihara** received the B.E. degree in electrical engineering from Kanagawa University, Kanagawa, Japan, in 1983.

He joined FA Sensor Manufacturers, Aichi, Japan. Since 1991, he has been with Murata Manufacturing Company Ltd., Kyoto, Japan, where he has been responsible for the research and development of EMI components, development of high-density capacitors for various applications, and power integrity design with using low-ESL capacitor.

Yuuki Araga (Member, IEEE) received the B.E., M.E., and Ph.D. degrees from the Department of Computer and System Engineering, Kobe University, Kobe, Japan, in 2008, 2010, and 2014, respectively.

He is currently a Researcher with National Institute of Advanced Industrial Science and Technology (AIST), Tsukuba, Japan. His research focuses on measurement and modeling techniques for 3-D integrated circuits.

Naoya Watanabe (Member, IEEE) received the M.S. and Ph.D. degrees in computer science and electronics from the Kyushu Institute of Technology, Kitakyushu, Japan, in 2001 and 2004, respectively.

From 2004 to 2006, he was a Research Associate with the Kyushu Institute of Technology, and from 2006 to 2008, he worked as a Researcher with the Kumamoto Technology and Industry Foundation, Kumamoto, Japan. In 2008, he joined the Fukuoka Industry, Science and Technology Foundation, Japan, as a Researcher, and in 2011, he joined

National Institute of Advanced Industrial Science and Technology (AIST), Tsukuba, Japan. He has been engaged in study of 3-D stacking technology, 3-D stacked systems, and 3-D IC testing.

Dr. Watanabe is a member of the IEEE Components, Packaging, and Manufacturing Technology Society, the Japan Institute of Electronics Packaging (JIEP), the Japan Society of Applied Physics (JSAP), and the International Microelectronics Assembly & Packaging Society (IMAPS). He received the Best Paper Award from IEEE CPMT Symposium Japan (ICSJ) in 2013.

**Haruo Shimamoto** received the B.S. and M.S. degrees from Osaka University, in 1978 and 1980, respectively.

He joined the Semiconductor Business Unit, Mitsubishi Electric Corporation, Tokyo, Japan. The former business unit was merged to Renesas in 2003 with Hitachi, Tokyo, and in 2010 with NEC Corporation, Tokyo. He had been engaged over 28 years in the development of semiconductor packaging and mass production. In 2013, he joined National Institute of Advanced Industrial Science

and Technology (AIST), Tsukuba, Japan, and is studying 3-D packaging technology. He is currently an Invited Researcher with the 3D Integration System Group, Device Technology Research Institute, AIST.

Mr. Shimamoto is a member of the Japan Institute of Electronics Packaging (JIEP).

**Katsuya Kikuchi** (Member, IEEE) received the B.S., M.S., and Ph.D. degrees in electronic engineering from Saitama University, Saitama, Japan, in 1996, 1998, and 2001, respectively.

He joined National Institute of Advanced Industrial Science and Technology (AIST), Tsukuba, Japan, in 2001, where he has been engaged in the research on 3-D integration system technologies. He is currently a Group Leader with the 3D Integration System Group, Device Technology Research Institute, AIST. His current research interests include

design and fabrication techniques toward 3-D integration systems with a particular emphasis on power/signal integrity, testing, and diagnosis.

Dr. Kikuchi is a member of the Japan Institute of Electronics Packaging (JIEP), the Institute of Electronics Information and Communication Engineers (IEICE), the Japan Society of Applied Physics (JSAP), and the American Physical Society (APS).

**Takuji Miki** (Member, IEEE) received the B.S. and M.S. degrees from Ritsumeikan University, Kyoto, Japan, in 2004 and 2006, respectively, and the Ph.D. degree from Kobe University, Kobe, Japan, in 2017.

From 2006 to 2016, he was with Panasonic Corporation, Osaka, Japan, where he was involved in the development of high performance analog and mixed-signal integrated circuits for consumer and industrial applications. He is an Associate Professor with the Graduate School of Science, Technology

and Innovation, Kobe University. His current research interests include data converters, sensor interface, and hardware security.

Makoto Nagata (Senior Member, IEEE) received the B.S. and M.S. degrees in physics from Gakushuin University, Tokyo, Japan, in 1991 and 1993, respectively, and the Ph.D. degree in electronics engineering from Hiroshima University, Hiroshima, Japan, in 2001.

He was a Research Associate with Hiroshima University from 1994 to 2002 and an Associate Professor with Kobe University, Kobe, Japan, from 2002 to 2009, where he was promoted to a Full Professor in 2009. He is currently the Dean

and a Professor with the Graduate School of Science, Technology and Innovation, Kobe University. His research interests include design techniques targeting high-performance mixed analog, RF and digital VLSI systems with particular emphasis on power/signal/substrate integrity and electromagnetic compatibility, testing and diagnosis, 3-D system integration, as well as their applications for hardware security and safety, and cryogenic electronics for quantum computing.

Dr. Nagata is a Senior Member of IEICE. He has been a member of a variety of technical program committees of international conferences, such as the Symposium on VLSI Circuits (2002-2009), Custom Integrated Circuits Conference (2007–2009), Asian Solid-State Circuits Conference (2005–2009), International Solid-State Circuits Conference (2014-2022), European Solid-State Circuits Conference (since 2020), and many others. He chaired the Technology Directions subcommittee for International Solid-State Circuits Conference (2018-2022) and now serves as an Executive Committee Member. He was the Technical Program Chair (2010-2011), the Symposium Chair (2012-2013), and an Executive Committee Member (2014-2015) for the Symposium on VLSI circuits. He was the IEEE Solid-State Circuits Society (SSCS) Distinguished Lecturer (DL) (2020-2021) and also the IEEE SSCS Kansai Chapter Chair (2017-2018). He has been an AdCom Member of the IEEE SSCS (since 2020) and an Associate Editor for IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS (since 2015).