# Program/Erase Scheme for Suppressing Interface Trap Generation in HfO<sub>2</sub>-Based Ferroelectric Field Effect Transistor

Jinhong Min<sup>®</sup>, Nicolo Ronchi<sup>®</sup>, Sean R. C. McMitchell<sup>®</sup>, Barry O'Sullivan<sup>®</sup>, Kaustuv Banerjee, Geert Van den bosch<sup>®</sup>, *Member, IEEE*, Jan Van Houdt<sup>®</sup>, *Fellow, IEEE*, and Changhwan Shin<sup>®</sup>, *Senior Member, IEEE*

**Abstract**— The endurance of the HfO<sub>2</sub>-based ferroelectric FET (FeFET) is investigated using various program/erase (PG/ER) pulse schemes. The ramp time (Tramp), which is the time to reach the PG/ER voltage, and the hold time (Thold), which is the time duration to maintain the PG/ER voltage, are adjusted, and thereafter, their influence on endurance is observed through the memory window, subthreshold slope, and threshold voltage of the FeFET while the FeFET is cycled up to 10<sup>4</sup> by a sequence of PG/ER pulses. Both parameters are closely related to depassivating interface traps, and it turns out that a long Tramp but short Thold are desirable to suppress the interface trap generation in FeFET. The relation between  $T_{ramp}$ ,  $T_{hold}$  and the interface trap generation is explained by the transient built-in electric field (which is generated by the transiently trapped carrier in the gate oxide when the gate voltage is swept rapidly).

Index Terms—Ferroelectrics, FeFET, reliability, endurance.

## I. INTRODUCTION

THE discovery of ferroelectricity in doped hafnium oxide thin film resolved the long-standing retention and scalability problems of perovskite-based ferroelectric FET (FeFET) [1]–[4]. The HfO<sub>2</sub>-based FeFET gate stack structure

Manuscript received June 8, 2021; revised July 23, 2021; accepted August 2, 2021. Date of publication August 5, 2021; date of current version August 26, 2021. This work was supported in part by the Ministry of Trade, Industry, and Energy (MOTIE), South Korea, through the Fostering Global Talents for Innovative Growth Program under Grant P0008745, supervised by the Korea Institute for Advancement of Technology (KIAT), and in part by the Korean Government through the National Research Foundation of Korea (NRF) under Grant 2020R1A2C1009063. The review of this letter was arranged by Editor U. Ganguly. (Corresponding author: Changhwan Shin.)

Jinhong Min is with the Department of Electrical and Computer Engineering, Sungkyunkwan University, Suwon-si 16419, South Korea, also with imec, 3001 Leuven, Belgium, and also with KU Leuven, 3001 Leuven, Belgium.

Nicolo Ronchi, Sean R. C. McMitchell, Barry O'Sullivan, Kaustuv Banerjee, and Geert Van den bosch are with imec, 3001 Leuven, Belgium.

Jan Van Houdt is with imec, 3001 Leuven, Belgium, and also with KU Leuven, 3001 Leuven, Belgium.

Changhwan Shin is with the Department of Electrical and Computer Engineering, Sungkyunkwan University, Suwon-si 16419, South Korea (e-mail: cshin@skku.edu).

Color versions of one or more figures in this letter are available at https://doi.org/10.1109/LED.2021.3102592.

Digital Object Identifier 10.1109/LED.2021.3102592

can be similar in structure to the one of NAND flash memory, therefore, being CMOS-process-compatible and capable of operating at low voltage. These properties make the HfO<sub>2</sub>-based FeFET interesting as a next-generation memory device [4], [5]. A wide range of studies has been done on HfO<sub>2</sub>-based FeFET to figure out optimal memory performance, as the Hf-based ferroelectric thin film can exhibit various properties depending on doping materials and fabrication condition [6]–[10].

Since the size of the memory window (MW), which is the threshold voltage ( $V_T$ ) difference between program (PG) state and erase (ER) state, is one of the most important performance factors of the memory device, the evolution of the MW by PG/ER cycling has been extensively investigated [12]–[16]. At the initial stage of PG/ER cycling, the MW increases due to the wake-up effect of ferroelectric thin film. However, the MW widening by the wake-up is only observed at  $\sim 0.1~\%$  of the total number of PG/ER cycles. On the other hand, the MW closure is observed at  $\sim 99~\%$  of the number of P/E cycles because of the device degradation. Therefore, it is essential to minimize the influence of the degradation of the FeFET to stably store the data. For this purpose, the understanding of degradation mechanism of the FeFET according to PG/ER cycling has been studied [17], [18].

The FeFET has a thin interfacial oxide layer between the ferroelectric layer and the Si channel, which is closely related to the degradation of the FeFET. When PG/ER pulse is applied to the FeFET, electron tunneling occurs through the interfacial oxide, consequently the oxide trapping and/or interface trapping states are created. These oxide traps and interface traps cause MW closure and positive V<sub>T</sub> shift. These two types of trapping are mainly known to affect the degradation of the FeFET.

There are many studies on the effects of various cycle waveforms adjusted for frequency or amplitude on the endurance of the ferroelectric capacitors, which is key component of the FeFET [19]–[21]. However, limited studies have investigated the influence of the shape of PG/ER pulse on the endurance of FeFET. In this work, the impact of the parameters constituting PG/ER pulse on the MW and SS of FeFET is intensively investigated, and the influence is explained with bipolar biastemperature-instability (BTI) [22],[23]. As a result, PG/ER scheme for enhancing the endurance of the FeFET will be proposed.

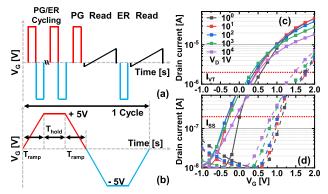

Fig. 1. (a) Test sequence used for measuring the endurance of FeFETs. (b) Timing definition of the PG/ER pulse. (c), (d) Current-vs.-gate voltage (I<sub>D</sub>-vs.-V<sub>G</sub>) of a FeFET after  $10^0 \sim 10^4$  cycles. The solid line and dashed line indicate the PG state and the ER state of a FeFET, respectively. Note that the V<sub>T</sub> and SS are extracted at their respective current level, i.e.,  $2 \,\mu$ A and  $0.2 \,\mu$ A (see the red-colored dotted line in the figure).

# II. EXPERIMENT

Using gate first process, ferroelectric field effect transistors (FeFETs) with TiN/Si/Si:HfO<sub>2</sub>/SiO<sub>2</sub>/Si gate stack were fabricated on 300 mm wafer. In the gate stack, 1nm-thick SiO<sub>2</sub> interfacial oxide layer was chemically grown on the Si surface. On top of it, 9.5nm-thick Si:HfO<sub>2</sub> and 5nm-thick TiN layer were deposited by atomic layer deposition (ALD). Between Si:HfO<sub>2</sub> and TiN layer, a 2nm-thick Si buffer layer was deposited by physical vapor deposition (PVD), to reduce the strain between the ferroelectric and the metal gate electrode. The FeFETs were annealed in N<sub>2</sub> ambient at 900°C to crystallize the Si:HfO<sub>2</sub> film. The channel length/width of FeFETs were 1  $\mu$ m/1  $\mu$ m.

The endurance of FeFETs was measured using the pulse train [which is shown in Fig. 1(a)]. The PG/ER pulses were applied to the FeFETs over  $10^0 \sim 10^4$  cycles. Afterwards, I<sub>D</sub>-vs.-V<sub>G</sub> of PG state and ER state of FeFETs were measured by the readout.

The evolution of  $I_D$ -vs.- $V_G$  of a FeFET over many cycles is represented in Fig. 1(c), (d). The subthreshold swing (SS) and threshold voltage ( $V_T$ ) at PG state or ER state were extracted at their respective constant current level, i.e.,  $0.2~\mu A$  and  $2~\mu A$  respectively, while the MW was calculated as the difference of  $V_T$  between the PG state and the ER state.

When measuring the current-vs.-voltage curve for extracting  $V_T$ , the characterization was completed within 20  $\mu$ s using a 1mA measurement range option to minimize interference by the read gate voltage [11]. In the case of the current-vs.voltage curve for SS, characterization was completed within  $\sim 1$  ms seconds using a  $1\mu A$  measurement range option to extract in the deeper current region to present a convincing SS. For the  $1\mu$ A-range measurement the interference during the readout was limited by a smaller Vg sweep (i.e., up to 1.4 V instead of 2 V). The lowest current level (i.e.,  $\sim$  10 nA) shown in fig. 1 (d) is not an actual leakage drain current but the minimum measurement resolution of the readout. 1 s of delay time was inserted between the PG/ER pulse and readout, to avoid the influence of bulk trapping in the HfO<sub>2</sub> [12]. To define the waveform of PG/ER pulse, the ramp time (T<sub>ramp</sub>) and hold time (T<sub>hold</sub>) was adjusted while the magnitude of PG/ER voltage was fixed as |5 V| through optimization.

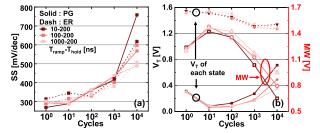

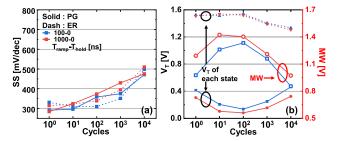

Fig. 2. Median value of (a) SS and (b) MW,  $V_T$  of FeFETs for various cycles up to  $10^4$  cycles. Note that  $T_{ramp}$  is varied from 10 ns to 1000 ns while  $T_{hold}$  was fixed as 200 ns. The solid line and dashed line indicate the PG state and the ER state, respectively. Note that PG/ER pulse with a longer  $T_{ramp}$  shows better MW and SS after  $10^4$  cycles.

# III. RESULTS AND DISCUSSION

It is well known that FeFETs processed on the same wafer are affected by device-to-device variation due to the grain distribution in the ferroelectric thin film [16], [24]–[26]. Each time different PG/ER pulse schemes were used to provide statistically reliable data, up to 20 devices were measured for each extraction of  $V_{\rm T}$  and SS. In this discussion, every figure represents the median value of measurement data.

To begin with,  $T_{ramp}$  was adjusted to see the impact of ramp time on the endurance of FeFETs. Using the fixed  $T_{hold}$  of 200 ns,  $T_{ramp}$  was varied from 10 ns to 1000 ns. The evolution of MW, SS and  $V_T$  at each PG/ER state were plotted to analyze the endurance of FeFETs (see Fig. 2).

The MW widening by wake-up effect occurs between  $10^0$  and  $10^1$  cycles [see Fig. 2(b)]. Then, at  $10^4$  cycles,  $V_T$  of each PG/ER state increases significantly. This is because of the rapid degradation of SS (which strongly depends on  $T_{ramp}$ ). With a shorter  $T_{ramp}$ , larger SS degradation and positive  $V_T$  shift were observed, especially at  $10^4$  cycles.

In addition, PG/ER pulse schemes with shorter  $T_{ramp}$  deteriorates the MW more than other schemes. This is because the degree of the degradation of SS depends on whether FeFETs' state was at the PG state or at the ER state. It was observed that the SS at the PG state is more deteriorated than the SS at the ER state at  $10^4$  cycles. As a result, a longer  $T_{ramp}$ , which prevents the SS deterioration in both states, not only prevents the positive  $V_T$  shift, but also was able to improve the MW of FeFETs. With the shortest  $T_{ramp}$ , the MW was median of 0.65 V. However, with the longest  $T_{ramp}$  case, the MW was median of 0.95 V at  $10^4$  cycles.

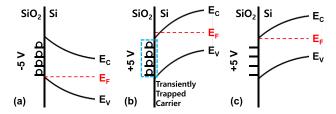

The rapid SS degradation with a short T<sub>ramp</sub> seems to agree with the interface trap depassivation by bipolar BTI [22], [23]. Some previous BTI studies showed that the amount of depassivated interface traps (which are depassivated by the bipolar BTI) is more than the sum of interface traps measured in each of the positive BTI and negative BTI measurements. In addition, the bipolar BTI exhibited frequency dependency: a higher frequency stress can generate more interface trap. This was mainly elucidated by the built-in electric field which is generated by transiently trapped carriers (see Fig. 3). If the gate voltage is quickly swept, the trapped carriers are still trapped in the oxide even if the gate voltage is switched. This is mainly because the emission rate of trap is finite [see Fig. 3(b)]. Therefore, the transiently trapped carrier can form the built-in electric field.

The additional built-in electric field could enhance the band bending between SiO<sub>2</sub> and Si than the energy band at

Fig. 3. Qualitative depiction of band diagram between  $SiO_2$  interfacial layer and Si channel when sweeping the gate voltage sweep from -5 V to +5 V. (a) and (c) represent the band diagram at steady-state under |5 VI, and (b) represents the band diagram at transient-state between (a) and (c). Note that the transiently-trapped carriers should cause more band bending [compare (b) against (c)].

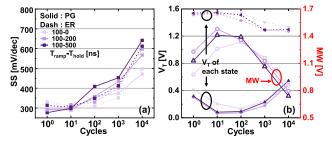

Fig. 4. (a) SS, (b) MW and  $V_T$  of FeFETs for various cycles up to  $10^4$  cycles. Note that  $T_{hold}$  is varied from 0 ns to 500 ns while  $T_{ramp}$  was fixed as 100 ns. The solid line and dashed line indicate the PG state and the ER state, respectively. Note that PG/ER pulse with a shorter  $T_{hold}$  shows better MW and SS after  $10^4$  cycles.

steady stress state, and it enhances BTI effects. Moreover, these trapped carriers could provide recombination energy that intensifies the BTI effect. In this respect, it can be estimated that the impact of  $T_{ramp}$  would be similar because the FeFETs were exposed to similar stress such as bipolar BTI. If the PG/ER pulse has a shorter  $T_{ramp}$ , it could confine more carriers transiently and generate a larger built-in electric field. As a result, severe BTI effects would happen, and thereby, more interface traps would be created.

There are many studies that have investigated the impact of  $T_{hold}$  to look for an appropriate PG/ER pulse width. It is well known that the properly long  $T_{hold}$  widens the MW [26], [27]. However, there are few studies on the impact of  $T_{hold}$  on endurance. Therefore, the impact of  $T_{hold}$  was investigated in this work

Using the fixed T<sub>ramp</sub> of 200 ns, T<sub>hold</sub> was varied from 0 ns to 500 ns. For T<sub>hold</sub> of 200 ns and 500 ns, they performed better initial MW due to the wake-up effect and practically long PG/ER pulses. However, the MW began to degrade earlier than T<sub>hold</sub> of 0 ns because of the trapping in the oxide induced by the long T<sub>hold</sub>[see Fig. 4(a)]. At 10<sup>3</sup> cycles, the SS in the case of long T<sub>hold</sub> is further increased. Thus, V<sub>T</sub> at each PG/ER state shifted/increased and MW decreased. This happened because more carriers were accumulated in the oxide by the influence of T<sub>hold</sub>, before sweeping the gate voltage, and the accumulated carriers were generated by a larger built-in electric field while sweeping the gate voltage.

Last but not least, the waveforms of triangle PG/ER pulse, which has  $T_{hold}$  of 0 ns, were compared to each other (see Fig. 5). In this comparison,  $T_{ramp}$  shorter than 100 ns was not used because it was too short to program or erase the ferroelectric layer of FeFETs. Thus, only the  $T_{ramp}$  of 100 ns and 1000 ns cases are displayed. Same as previous schemes,

Fig. 5. (a) SS, (b) MW and  $V_T$  of FeFETs for various cycles up to  $10^4$  cycles. Note that  $T_{ramp}$  is set to either 100 ns or 1000 ns while  $T_{ramp}$  was fixed as 0 ns. The solid line and dashed line indicate the PG state and the ER state, respectively.

$T_{ramp}$  of 1000 ns performed better MW thanks to 10 times longer pulse length.

In terms of SS,  $T_{ramp}$  of 100 and 1000 ns shows similar SS up to  $10^4$  cycles. However, in the case of  $T_{ramp}$  of 100ns, especially the  $V_T$  of the program state was not set better than 1000ns due to the short PG/ER pulse scheme. In addition, the device deterioration occurred faster than the case of  $T_{ramp}$  of 1000ns between  $10^3$  and  $10^4$  cycles, resulting in a sharp degradation in MW and SS. This implies that when using short  $T_{ramp}$ , the device may deteriorate faster. Among all the PG/ER pulse schemes, we can find that the waveform of triangle PG/ER pulse which has  $T_{ramp}$  of 1000 ns not only secured a wider MW, but also suppressed the SS degradation after  $10^4$  cycles of program and erase endurance test because it reduced the amount of transiently-trapped carriers.

### IV. CONCLUSION

The influence of various PG/ER pulse schemes on the endurance of FeFET was studied.  $T_{ramp}$  and  $T_{hold}$  was varied from 10 ns to 1000 ns and 0 ns to 500 ns, respectively, to modulate the PG/ER pulse. The MW, SS and  $V_T$  were measured to quantitatively evaluate the endurance of FeFETs. If  $T_{ramp}$  is short but  $T_{hold}$  is long, the amount of interface trap generated is surged up, and thereby, the MW and SS become worse. This is because the built-in electric field is generated by the transiently trapped carrier, and thereafter, the built-in electric field accelerates the interface trap generation.

In the worst case, when the PG/ER pulse has  $T_{ramp}$  of 10 ns and  $T_{hold}$  of 200 ns, the MW was deteriorated to median of 0.65 V after  $10^4$  cycles. On the other hand, when the PG/ER pulse has  $T_{ramp}$  of 1000 ns and  $T_{hold}$  of 0 ns, the MW was maintained at median of 0.97 V after  $10^4$  cycles, representing the best endurance.

In this study, when PG/ER pulse is applied, both rising time (which is the time that it takes to reach the PG/ER voltage) and falling time (which is the time that it takes to reach the ground voltage) were considered equally as the ramp time. However, it turned out that the generation of interface trap under the bipolar stress condition is controlled by either the rising or falling time, and the amount of interface traps generated varies depending on the doping type of devices [22]. Therefore, it is necessary to further investigate the effect of the PG/ER scheme on the endurance of FeFET in future, and it is expected to help improve and understand the endurance of FeFET.

### **ACKNOWLEDGMENT**

The authors would like to thank Yusuke Higashi for helpful discussions and help in performing some of the experiments.

### REFERENCES

- T. P. Ma and J.-P. Han, "Why is nonvolatile ferroelectric memory fieldeffect transistor still elusive?" *IEEE Electron Device Lett.*, vol. 23, no. 7, pp. 386–388, Jul. 2002, doi: 10.1109/LED.2002.1015207.

- [2] N. Gong and T.-P. Ma, "Why is FE-HfO<sub>2</sub> more suitable than PZT or SBT for scaled nonvolatile 1-T memory cell? A retention perspective," *IEEE Electron Device Lett.*, vol. 37, no. 9, pp. 1123–1126, Sep. 2016, doi: 10.1109/LED.2016.2593627.

- [3] T. S. Böescke, J. Müeller, D. Bräeuhaus, U. Schröeder, and U. Böettger, "Ferroelectricity in hafnium oxide thin films," *Appl. Phys. Lett.*, vol. 99, no. 10, 2011, Art. no. 102903, doi: 10.1063/1.3634052.

- [4] T. S. Böscke, S. Teichert, D. Bräuhaus, J. Müller, U. Schröder, U. Böttger, and T. Mikolajick, "Phase transitions in ferroelectric silicon doped hafnium oxide," *Appl. Phys. Lett.*, vol. 99, no. 11, 2011, Art. no. 112904, doi: 10.1063/1.3636434.

- [5] K. Florent, S. Lavizzari, L. Di Piazza, M. Popovici, J. Duan, G. Groeseneken, and J. Van Houdt, "Reliability study of ferroelectric Al:HfO<sub>2</sub> thin films for DRAM and NAND applications," *IEEE Trans. Electron Devices*, vol. 64, no. 10, pp. 4091–4098, Oct. 2017, doi: 10.1109/TED.2017.2742549.

- [6] J. Müller, T. S. Böscke, S. Müller, E. Yurchuk, P. Polakowski, J. Paul, D. Martin, T. Schenk, K. Khullar, and A. Kersch, "Ferroelectric hafnium oxide: A CMOS-compatible and highly scalable approach to future ferroelectric memories," *IEDM Tech. Dig.*, Washington, DC, USA, Oct. 2013, pp. 10.8.1–10.8.4, doi: 10.1109/IEDM.2013. 6724605.

- [7] J. Müller, T. S. Böscke, U. Schröder, S. Mueller, D. Bräuhaus, U. Böttger, L. Frey, and T. Mikolajick, "Ferroelectricity in simple binary ZrO<sub>2</sub> and HfO<sub>2</sub>," *Nano Lett.*, vol. 12, no. 8, pp. 4318–4323, Aug. 2012.

- [8] S. Mueller, J. Mueller, A. Singh, S. Riedel, J. Sundqvist, U. Schroeder, and T. Mikolajick, "Incipient ferroelectricity in al-doped HfO<sub>2</sub> thin films," *Adv. Funct. Mater.*, vol. 22, no. 11, pp. 2412–2417, Jun. 2012, doi: 10.1002/adfm.201103119.

- [9] S. Mueller, C. Adelmann, A. Singh, S. Van Elshocht, U. Schroeder, and T. Mikolajick, "Ferroelectricity in Gd-doped HfO<sub>2</sub> thin films," ECS J. Solid State Sci. Technol., vol. 1, no. 6, pp. N123–N126, 2012, doi: 10.1149/2.002301jss.

- [10] N. Ronchi, S. McMitchell, J. Min, K. Banerjee, G. Van den Bosch, C. Shin, and J. Van Houdt, "Endurance of ferroelectric La-doped HfO<sub>2</sub> for SFS gate-stack memory devices," in *Proc. IEEE Int. Memory Workshop (IMW)*, Dresden, Germany, May 2020, pp. 1–4, doi: 10.1109/IMW48823.2020.9108125.

- [11] H. Mulaosmanovic, E. T. Breyer, T. Mikolajick, and S. Slesazeck, "Ferroelectric FETs with 20-nm-thick HfO<sub>2</sub> layer for large memory window and high performance," *IEEE Trans. Electron Devices*, vol. 66, no. 9, pp. 3828–3833, Sep. 2019, doi: 10.1109/TED.2019. 2930749.

- [12] K. Ni, P. Sharma, J. Zhang, M. Jerry, J. A. Smith, K. Tapily, R. Clark, S. Mahapatra, and S. Datta, "Critical role of interlayer in Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> ferroelectric FET nonvolatile memory performance," *IEEE Trans. Electron Devices*, vol. 65, no. 6, pp. 2461–2469, Jun. 2018, doi: 10.1109/TED.2018.2829122.

- [13] S. Mueller, J. Müller, R. Hoffmann, E. Yurchuk, T. Schlösser, R. Boschke, and J. Paul, "From MFM capacitors toward ferroelectric transistors: Endurance and disturb characteristics of HfO<sub>2</sub>-based FeFET devices," in *IEEE Trans. Electron Devices*, vol. 60, no. 12, pp. 4199–4205, Dec. 2013, doi: 10.1109/TED.2013.2283465.

- [14] T. Ali, P. Polakowski, S. Riedel, T. Büttner, T. Kämpfe, M. Rudolph, B. Pätzold, K. Seidel, D. Löhr, R. Hoffmann, M. Czernohorsky, K. Kühnel, P. Steinke, J. Calvo, K. Zimmermann, and J. Müller, "High endurance ferroelectric hafnium oxide-based FeFET memory without retention penalty," *IEEE Trans. Electron Devices*, vol. 65, no. 9, pp. 3769–3774, Sep. 2018, doi: 10.1109/TED.2018.2856818.

- [15] J. Muller, E. Yurchuk, T. Schlosser, J. Paul, R. Hoffmann, S. Müller, D. Martin, S. Slesazeck, P. Polakowski, J. Sundqvist, M. Czernohorsky, K. Seidel, P. Kucher, R. Boschke, M. Trentzsch, K. Gebauer, U. Schroder, and T. Mikolajick, "Ferroelectricity in HfO<sub>2</sub> enables nonvolatile data storage in 28 nm HKMG," in *Proc. Symp. VLSI Technol. (VLSIT)*, Honolulu, HI, USA, Jun. 2012, pp. 25–26, doi: 10.1109/VLSIT.2012.6242443.

- [16] S. Beyer, S. Dünkel, M. Trentzsch, J. Müller, A. Hellmich, D. Utess, J. Paul, and D. Kleimaie, "FeFET: A versatile CMOS compatible device with game-changing potential," in *Proc. IEEE Int. Memory Workshop (IMW)*, Dresden, Germany, May 2020, pp. 1–4, doi: 10.1109/IMW48823.2020.9108150.

- [17] N. Gong and T.-P. Ma, "A study of endurance issues in HfO<sub>2</sub>-based ferroelectric field effect transistors: Charge trapping and trap generation," *IEEE Electron Device Lett.*, vol. 39, no. 1, pp. 15–18, Jan. 2018, doi: 10.1109/LED.2017.2776263.

- [18] B. Zeng, M. Liao, J. Liao, W. Xiao, Q. Peng, S. Zheng, and Y. Zhou, "Program/erase cycling degradation mechanism of HfO<sub>2</sub>-based FeFET memory devices," *IEEE Electron Device Lett.*, vol. 40, no. 5, pp. 710–713, May 2019, doi: 10.1109/LED.2019.2908084.

- [19] E. Yurchuk, S. Mueller, D. Martin, S. Slesazeck, U. Schroeder, T. Mikolajick, J. Müller, J. Paul, R. Hoffmann, J. Sundqvist, T. Schlosser, R. Boschke, R. van Bentum, and M. Trentzsch, "Origin of the endurance degradation in the novel HfO<sub>2</sub>-based 1T ferroelectric nonvolatile memories," in *Proc. IEEE Int. Rel. Phys. Symp.*, Waikoloa, HI, USA, Jun. 2014, pp. 2E.5.1–2E.5.5, doi: 10.1109/IRPS.2014.6860603.

- [20] E. Yurchuk, J. Muller, S. Muller, J. Paul, M. Pesic, R. van Bentum, U. Schroeder, and T. Mikolajick, "Charge-trapping phenomena in HfO<sub>2</sub>-based FeFET-type nonvolatile memories," *IEEE Trans. Electron Devices*, vol. 63, no. 9, pp. 3501–3507, Sep. 2016, doi: 10.1109/TED.2016.2588439.

- [21] M. Pesic, A. Padovani, S. Slcsazeck, T. Mikolajick, and L. Larcher, "Deconvoluting charge trapping and nucleation interplay in FeFETs: Kinetics and Reliability," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Mar. 2018, pp. 25.1.1–25.1.4, doi: 10.1109/IEDM.2018.8614492.

- [22] S. Zhu, A. Nakajima, T. Ohashi, and H. Miyake, "Mechanism of dynamic bias temperature instability in p- and nMOSFETs: The effect of pulse waveform," *IEEE Trans. Electron Devices*, vol. 53, no. 8, pp. 1805–1814, Aug. 2006, doi: 10.1109/TED.2006.877876.

- [23] T. P. Chen, S. Li, S. Fung, and K. F. Lo, "Interface trap generation by FN injection under dynamic oxide field stress," *IEEE Trans. Electron Devices*, vol. 45, no. 9, pp. 1920–1926, Sep. 1998, doi: 10.1109/16.711356.

- [24] T. Ali, P. Polakowski, T. Büttner, T. Kämpfe, M. Rudolph, B. Pätzold, R. Hoffmann, M. Czernohorsky, and K. Kühnel, "Principles and challenges for binary oxide based ferroelectric memory FeFET," in *Proc. IEEE 11th Int. Memory Workshop (IMW)*, Monterey, CA, USA, May 2019, pp. 1–4, doi: 10.1109/IMW.2019.8739651.

- [25] K. Ni, W. Chakraborty, J. Smith, B. Grisafe, and S. Datta, "Fundamental understanding and control of device-to-device variation in deeply scaled ferroelectric FETs," in *Proc. Symp. VLSI Technol.*, Kyoto, Japan, Jun. 2019, pp. T40–T41, doi: 10.23919/VLSIT.2019.8776497.

- [26] T. Ali, K. Kuhnel, M. Czernohorsky, M. Rudolph, B. Patzold, R. Olivo, D. Lehninger, K. Mertens, F. Muller, M. Lederer, R. Hoffmann, C. Mart, M. N. Kalkani, P. Steinke, T. Kampfe, J. Muller, J. V. Houdt, K. Seidel, and L. M. Eng, "Impact of ferroelectric wakeup on reliability of laminate based Si-doped hafnium oxide (HSO) FeFET memory cells," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Dallas, TX, USA, Apr. 2020, pp. 1–9, doi: 10.1109/IRPS45951.2020.9128337.

- [27] K.-T. Chen, H.-Y. Chen, C.-Y. Liao, G.-Y. Siang, C. Lo, M.-H. Liao, K.-S. Li, S. T. Chang, and M. H. Lee, "Non-volatile ferroelectric FETs using 5-nm Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> with high data retention and read endurance for 1T memory applications," *IEEE Electron Device Lett.*, vol. 40, no. 3, pp. 399–402, Mar. 2019, doi: 10.1109/LED.2019.2896231.