# Pulsed Power Performance of $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs at L-Band

Neil A. Moser<sup>®</sup>, *Member, IEEE*, Tadj Asel, Kyle J. Liddy<sup>®</sup>, Miles Lindquist, Nicholas C. Miller, Shin Mou, Adam Neal, *Member, IEEE*, Dennis E. Walker, Steve Tetlak, Kevin D. Leedy<sup>®</sup>, Gregg H. Jessen<sup>®</sup>, *Senior Member, IEEE*, Andrew J. Green, *Member, IEEE*, and Kelson D. Chabak<sup>®</sup>, *Member, IEEE*

Abstract— DC, small, and large signal results are shown under continuous wave and pulsed conditions for a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> metal-oxide-semiconductor field-effect transistor operating at 1 and 2 GHz. The device has a maximum transducer gain, maximum output power, and peak power added efficiency of 13 dB (15 dB), 715 mW/mm (487 mW/mm), and 23.4% (21.2%), respectively at 1 GHz (2 GHz). We observe the continuous wave output power is limited to 213 mW/mm by drain dispersion likely from surface or interface traps in the gatedrain region as indicated by pulsed IV measurements. High parasitic resistances, as indicated by high knee voltages, also limit the power performance under continuous and pulsed large signal conditions.

# *Index Terms*— $\beta$ -Ga2O3, MOSFET, small signal, large signal, radio frequency, pulsed radio frequency.

## I. INTRODUCTION

**B**ETA-PHASE gallium oxide (β-Ga<sub>2</sub>O<sub>3</sub>) metal-oxidesemiconductor field-effect transistors (MOSFETs) are promising power devices due to high projected critical field strength,  $E_{crit}$ , of ~8MV/cm [1], [2] and experimental  $E_{crit}$  of > 3.8 MV/cm [3]. Most β-Ga<sub>2</sub>O<sub>3</sub> devices have been reported so far with excellent power switch figures of merit (FoM) [4]–[6], but it has also been noted that high  $E_{crit}$  allows for aggressive scaling of devices which can lead to a high RF FoM for β-Ga<sub>2</sub>O<sub>3</sub> [7]. Early β-Ga<sub>2</sub>O<sub>3</sub> RF devices have been reported with RF power gain up to nearly 20 GHz using small signal measurements [8], [9] and with limited gain in large-signal results up to 1 GHz [10], [11]. Due to the low thermal conductivity of β-Ga<sub>2</sub>O<sub>3</sub>, pulsed-power measurements provide an important means to evaluate the RF

Manuscript received April 6, 2020; revised April 21, 2020 and April 29, 2020; accepted May 6, 2020. Date of publication May 11, 2020; date of current version June 29, 2020. The review of this letter was arranged by Editor G. Han. (*Corresponding author: Neil A. Moser.*)

Neil A. Moser, Nicholas C. Miller, Kevin D. Leedy, and Kelson D. Chabak are with the Air Force Research Laboratory, Wright-Patterson AFB, OH 45433 USA (e-mail: neil.moser@us.af.mil).

Tadj Asel is with UES, Inc., Dayton, OH 45432 USA.

Kyle J. Liddy is with KBR, Beavercreek, OH 45431 USA.

Miles Lindquist is with the Department of Electrical and Computer Engineering, The Ohio State University, Columbus, OH 43210 USA.

Shin Mou and Adam Neal are with the Air Force Research Laboratory Manufacturing and Materials Directorate, Wright-Patterson AFB, OH 45433 USA.

Dennis E. Walker, Steve Tetlak, and Andrew J. Green are with the Air Force Research Laboratory Sensors Directorate, Wright-Patterson AFB, OH 45433 USA.

Gregg H. Jessen is with the FAST Labs, BAE Systems, Inc., Nashua, NH 03060 USA.

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2020.2993555

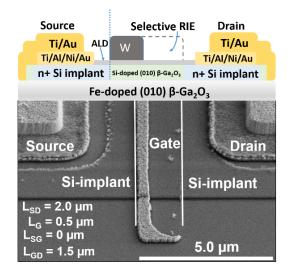

Fig. 1. Schematic of the fabricated device with corresponding scanning electron microscope image of the source-drain region. Device dimensions are included.

power performance potential of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices with high RF FoM can lead to new opportunities for integrating RF and power conversion on available  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> native, large-area substrates.

Here, we present small and large signal RF power performance at L-band for a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET. Higher gain and dc performance than previously measured RF power devices yield RF performance at 1 GHz with output power,  $P_{OUT}$ of 715 mW/mm and power added efficiency, *PAE*, of 23.4%. We further evaluate the small and large signal data under continuous wave (CW) and pulsed conditions up to 2 GHz demonstrating the validity and repeatability of the results for both our measurement technique and the device itself. We also provide insight into the limitations of our device, including drain dispersion, self-heating, and parasitic resistances, toward increasing performance.

#### II. METHODS

$\beta$ -Ga<sub>2</sub>O<sub>3</sub> lateral MOSFETs were fabricated on a 65-nmthick- $\beta$ -Ga<sub>2</sub>O<sub>3</sub> channel grown by molecular beam epitaxy with target Si doping of 2 × 10<sup>18</sup> cm<sup>-3</sup> on an Fe-doped (010)-oriented native substrate acquired commercially. Devices were fabricated based on a subtractive self-aligned gate (SAG) process. First, mesa isolation was performed by a BCl<sub>3</sub> dry etch followed by 30 nm of Al<sub>2</sub>O<sub>3</sub> deposited by plasma enhanced atomic layer deposition to serve as a gate oxide and implant ionization cap. Tungsten (W) was

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

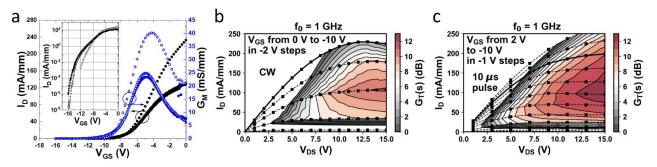

Fig. 2. DC transfer curve, ID vs. VGS, with inset log scale (a) and family of curves, ID vs. VDS, with contours showing the small signal gain, GT(s) for CW S parameters at 1 GHz (b) and 10  $\mu$ s pulsed S parameters at 1 GHz (c). In (a), forward (closed symbols) and reverse (open symbols) are shown for VD = 15 V (circles) and VD = 5 V (squares). In (b) and (c), the VG = 0 V curve has a solid line for comparison.

sputtered 200 nm thick and an implant mask was defined by a subtractive dry etch process to form a scaled 2  $\mu$ m channel which is an improvement over our previously reported SAG device [12]. The sample was implanted with Si targeting a box profile of  $2.5 \times 10^{20}$  cm<sup>-3</sup> and a depth of 85 nm. A second dry-etch of the W implant mask was implemented to remove W to form the drift region while the remaining W formed the SAG electrode. The Al<sub>2</sub>O<sub>3</sub> layer is designed to protect the Ga<sub>2</sub>O<sub>3</sub> channel layer since it has high etch selectively to the W dry etch process. The Si implant was activated with a 2 minute 900 °C rapid thermal anneal (RTA) in N<sub>2</sub> overpressure. Next, the Al<sub>2</sub>O<sub>3</sub> was selectively removed to deposit ohmic metal by electron beam evaporation and the sample was subject to RTA at 470 °C for 1 minute in N<sub>2</sub> overpressure. Interconnect metal (Ti/Au) was added to characterize the dc and RF performance. A final 3  $\mu$ m of additional pad metal was deposited which was found to be critical for thermal dissipation during high power testing. Fig. 1 shows a schematic cross section and scanning electron microscopy image of the device prior to additional pad metal.

The resulting devices have a 2 × 50  $\mu$ m gate periphery. The gate length,  $L_G$ , and gate-drain spacing,  $L_{GD}$ , were 0.5  $\mu$ m and 1.5  $\mu$ m, respectively, as measured with a scanning electron microscope. The free carrier concentration and mobility were measured to be  $5.5 \times 10^{17}$  cm<sup>-3</sup> and 74 cm<sup>2</sup>/(V·s), respectively, after fabrication using van Der Pauw structures on a sister sample. Transfer length method (TLM) was used to determine a contact resistance of ~16  $\Omega$ ·mm, although variation across the wafer was significant due to an unoptimized implant step and ranged from 5 to 25  $\Omega$ ·mm for sites with good TLM line fits.

Load-pull testing was performed at L-band using passive source and load tuners. All tuning was performed at 0 dBm available input power with a goal of maximizing transducer gain,  $G_T$ . Diode-based power sensors were used during load-pull to measure pulsed power where the gate bias, drain supply, and RF source were pulsed in order with a 2  $\mu$ s pulse delay between turn on and turn off of each. The quiescent values were  $V_{GQ} = 0$  V and  $V_{DQ} = 0$  V for all pulsed load pull measurements with a period of 10 ms for the various pulse widths. The measurement window was positioned in the third quarter of each different pulse width and the pulsed power output waveform was observed to verify power did not fluctuate significantly over the pulse width measurement window. Power calibration values were also verified to remain unchanged as the pulse width was changed. Similar

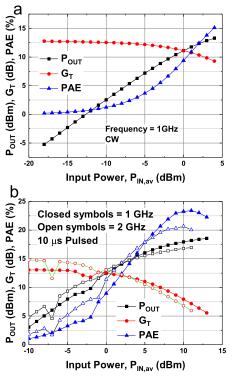

Fig. 3. Load-pull power sweeps for CW at 1 GHz (a) and for 10  $\mu$ s pulse at 1 GHz and 2 GHz (b).

pulse conditions were used for pulsed scattering parameter (S-parameter) measurements.

#### III. RESULTS

Fig. 2a shows a DC transfer curve demonstrating transconductance of 40 mS/mm and  $I_{ON}/I_{OFF}$  ratio greater than 10<sup>8</sup>. Fig. 2 also shows the family of curves ( $J_D$  vs.  $V_{DS}$ ) with overlapping contours of small signal gain,  $G_{T(s)}$ , for the CW (Fig. 2b) and 10  $\mu$ s pulse width (Fig. 2c) measurements. The small signal gain was calculated from S-parameters (CW and 10  $\mu$ s pulse width) at the tuning point for maximum gain found in the load-pull measurement. Fig. 3 shows power sweep data for CW (Fig. 3a) load-pull and 10  $\mu$ s pulse width (Fig. 3b) load-pull at 1 and 2 GHz. The load-pull results were obtained at a supply voltage,  $V_D = 20$  V, and bias,  $V_G = -4.5$  V which is near the peak transconductance and expected maximum gain (see Fig. 2a) from the  $V_D = 15$  V transfer curve.

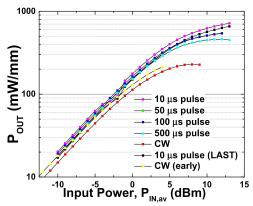

To analyze the effects of dispersion and self-heating, Fig. 4 depicts the normalized output power of several different pulse widths. The maximum output power is reduced as

Fig. 4. A comparison of output power for pulsed and CW load pull with varying pulse widths (pulse period remains 10 ms throughout). The measurements include an early CW measurement and a short pulse (10  $\mu$ s) measurement taken at the beginning and end (labeled "LAST") of testing for analysis of degradation.

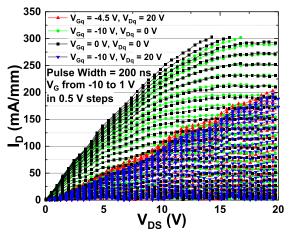

the pulse width (and therefore duty cycle) increases. Degradation also has an effect as the first and last short pulse (10  $\mu$ s) measurements do not match exactly; however, after many measurements deep into gain compression, the device generally maintained the behavior shown in Fig. 2. Fig. 5 shows a pulsed-IV measurement analyzing the drain dispersion characteristics including a quiescent voltage at the bias used in the load pull measurements of Figs. 3 and 4,  $V_D = 20$  V and  $V_G = -4.5$  V.

#### **IV. DISCUSSION**

The 2  $\times$  50  $\mu$ m device has a maximum  $G_T$ , maximum  $P_{OUT}$ , and PAE of 13 dB (15 dB), 715 mW/mm (487 mW/mm), and 23.4% (21.2%), respectively at 1 GHz (2 GHz) as seen in Fig. 3 for a 10  $\mu$ s pulsed input power. These values agree well with the small signal results of Fig. 2. The 2 GHz  $G_T$  is slightly higher because of a larger tuning range for the passive tuner at 2 GHz. For CW input, the device achieved  $G_T = 12.8$  dB,  $P_{OUT} = 213$  mW/mm, and PAE = 15.1%. In Fig. 4, it is clear that shorter pulse widths (reduced duty cycle) are effective in increasing the linear gain region to higher input powers and do not greatly affect the device gain. The reduced output power for increased pulse widths, thus, is likely a result of current collapse resulting from self-heating or drain dispersion. It is clear that with wider pulse widths the device is held under RF power longer causing potential self-heating effects.

The drain dispersion effect is not as well understood and may occur due to slow negative states near the device surface in the gate drain region causing a virtual gating and increased on-resistance. These slow states have enough time to clear for short pulse widths where the drain voltage is held at  $V_D = 0$  V for longer periods of time. Fig. 5 indicates significant (>30%) drain dispersion at the maximum current when pulsing from the load-pull biasing conditions. Fig. 5 also includes a pinched-off condition,  $V_{Gq} = -10$  V,  $V_{Dq} = 20$  V, curve to differentiate the effects of drain dispersion from self-heating and a gate lag measurement  $V_{Gq} = -10$  V,  $V_{Dq} = 0$  V to show the gate dispersion. Unlike AlGaN/GaN HEMT devices where polarization causes surface charge leading to similar effects [13], surface charge in our device is likely related to traps at the surface of the Al<sub>2</sub>O<sub>3</sub> or at the gate-oxide-Ga<sub>2</sub>O<sub>3</sub> interface, either one being filled by

Fig. 5. Pulsed IV measurements for four different quiescent bias points demonstrating the drain dispersion effects at the same bias point used in load pull measurements (red triangles).

electrons under positive drain biases. The drain dispersion therefore, may have been exacerbated by the processing of the drift region which includes a W dry etch; however, we have observed drain dispersion in devices without this dry etch. Mitigation of drain dispersion may be possible through an alternate surface preparation or passivation layers (gate oxides). These methods are currently under investigation.

The shorter 200 ns pulse widths in Fig. 5 do indicate less self-heating than those of Fig. 2c (10  $\mu$ s pulse widths) as seen by the >20% reduction in the max current. Some of this reduction is likely related to degradation in the device as the measurements were taken at a midpoint and at the end of power measurements. Additional studies are ongoing to characterize, differentiate, and remedy the effects of drain dispersion, self-heating, and device degradation. Despite these limitations, the devices still performed significantly better than previous load-pulled Ga<sub>2</sub>O<sub>3</sub> devices [10], [11].

We also point out that parasitic resistance plays a large role in limiting RF performance, as it does in power switch performance as described in [3]. The curves in Fig. 5 indicate that the power measurements at 20 V will quickly be limited by the high knee voltage of >15 V even under ideal pulsed conditions. In our devices, although the self-aligned Si implant has significantly reduced the source access resistance, the contact resistance and sheet resistance of the implanted regions remains unoptimized [12]. Others have shown reduced contact resistance by etching of the implant region under the contacts [14] or using regrown contact layers [15]. The evaluation of these methods and Si-implant optimization are also ongoing towards future high-performance  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices.

### V. CONCLUSION

We have reported improved RF power performance up to L-band using  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> SAG MOSFETs with sufficient RF gain. The RF device performance indicates early promise for efficient RF power with *PAE* > 23% and *P*<sub>OUT</sub> > 700 mW/mm at 1 GHz. Significant opportunities for device engineering remain to remove parasitic resistance, dc-to-RF dispersion and thermal challenges for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices. A path to using the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> material system for integration of RF and low-loss power conversion circuitry exists for future optimized devices.

#### REFERENCES

- M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui, and S. Yamakoshi, "Gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) metal-semiconductor field-effect transistors on single-crystal β-Ga<sub>2</sub>O<sub>3</sub> (010) substrates," *Appl. Phys. Lett.*, vol. 100, no. 1, Jan. 2012, Art. no. 013504, doi: 10.1063/ 1.3674287.

- [2] J. L. Hudgins, G. S. Simin, E. Santi, and M. A. Khan, "An assessment of wide bandgap semiconductors for power devices," *IEEE Trans. Power Electron.*, vol. 18, no. 3, pp. 907–914, May 2003, doi: 10.1109/ TPEL.2003.810840.

- [3] A. J. Green, K. D. Chabak, E. R. Heller, R. C. Fitch, M. Baldini, A. Fiedler, K. Irmscher, G. Wagner, Z. Galazka, S. E. Tetlak, A. Crespo, K. Leedy, and G. H. Jessen, "3.8-MV/cm breakdown strength of MOVPE-grown Sn-doped β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs," *IEEE Electron Device Lett.*, vol. 37, no. 7, pp. 902–905, Jul. 2016, doi: 10. 1109/LED.2016.2568139.

- [4] K. D. Chabak, J. P. McCandless, N. A. Moser, A. J. Green, K. Mahalingam, A. Crespo, N. Hendricks, B. M. Howe, S. E. Tetlak, K. Leedy, R. C. Fitch, D. Wakimoto, K. Sasaki, A. Kuramata, and G. H. Jessen, "Recessed-gate enhancement-mode β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs," *IEEE Electron Device Lett.*, vol. 39, no. 1, pp. 67–70, Jan. 2018, doi: 10.1109/LED.2017.2779867.

- [5] Z. Hu, K. Nomoto, W. Li, N. Tanen, K. Sasaki, A. Kuramata, T. Nakamura, D. Jena, and H. G. Xing, "Enhancement-mode Ga<sub>2</sub>O<sub>3</sub> vertical transistors with breakdown voltage >1 kV," *IEEE Electron Device Lett.*, vol. 39, no. 6, pp. 869–872, Jun. 2018, doi: 10.1109/LED.2018.2830184.

- [6] Y. Lv, H. Liu, X. Zhou, Y. Wang, X. Song, Y. Cai, Q. Yan, C. Wang, S. Liang, J. Zhang, Z. Feng, H. Zhou, S. Cai, and Y. Hao, "Lateral β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs with high power figure of merit of 277 MW/cm<sup>2</sup>," *IEEE Electron Device Lett.*, vol. 41, no. 4, pp. 537–540, Apr. 2020, doi: 10.1109/LED.2020. 2974515.

- [7] E. Johnson, "Physical limitations on frequency and power parameters of transistors," in *Proc. IRE Int. Conv. Rec.*, New York, NY, USA, Mar. 1966, pp. 27–34, doi: 10.1109/IRECON.1965. 1147520.

- [8] Z. Xia, H. Xue, C. Joishi, J. Mcglone, N. K. Kalarickal, S. H. Sohel, M. Brenner, A. Arehart, S. Ringel, S. Lodha, W. Lu, and S. Rajan, "β-Ga<sub>2</sub>O<sub>3</sub> delta-doped field-effect transistors with current gain cutoff frequency of 27 GHz," *IEEE Electron Device Lett.*, vol. 40, no. 7, pp. 1052–1055, Jul. 2019, doi: 10.1109/LED.2019.2920366.

- [9] K. D. Chabak, D. E. Walker, A. J. Green, A. Crespo, M. Lindquist, K. Leedy, S. Tetlak, R. Gilbert, N. A. Moser, and G. Jessen, "Submicron gallium oxide radio frequency field-effect transistors," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Ann Arbor, MI, USA, Jul. 2018, pp. 1–3, doi: 10.1109/IMWS-AMP.2018.8457153.

- [10] A. J. Green, K. D. Chabak, M. Baldini, N. Moser, R. Gilbert, R. C. Fitch, G. Wagner, Z. Galazka, J. Mccandless, A. Crespo, K. Leedy, and G. H. Jessen, "β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs for radio frequency operation," *IEEE Electron Device Lett.*, vol. 38, no. 6, pp. 790–793, Jun. 2017, doi: 10.1109/LED.2017.2694805.

- [11] M. Singh, M. A. Casbon, M. J. Uren, J. W. Pomeroy, S. Dalcanale, S. Karboyan, P. J. Tasker, M. H. Wong, K. Sasaki, A. Kuramata, S. Yamakoshi, M. Higashiwaki, and M. Kuball, "Pulsed large signal RF performance of field-plated Ga<sub>2</sub>O<sub>3</sub> MOSFETs," *IEEE Electron Device Lett.*, vol. 39, no. 10, pp. 1572–1575, Aug. 2018, doi: 10.1109/ LED.2018.2865832.

- [12] K. J. Liddy, A. J. Green, N. S. Hendricks, E. R. Heller, N. A. Moser, K. D. Leedy, A. Popp, M. T. Lindquist, S. E. Tetlak, G. Wagner, K. D. Chabak, and G. H. Jessen, "Thin channel β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs with self-aligned refractory metal gates," *Appl. Phys. Express*, vol. 12, no. 12, Dec. 2019, Art. no. 126501, doi: 10.7567/1882-0786/ab4d1c.

- [13] R. Vetury, N. Q. Zhang, S. Keller, and U. K. Mishra, "The impact of surface states on the DC and RF characteristics of AlGaN/GaN HFETs," *IEEE Trans. Electron Devices*, vol. 48, no. 3, pp. 560–566, Mar. 2001, doi: 10.1109/16.906451.

- [14] M. H. Wong, Y. Nakata, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, "Enhancement-mode Ga<sub>2</sub>O<sub>3</sub> MOSFETs with Si-ionimplanted source and drain," *Appl. Phys. Express*, vol. 10, no. 4, Apr. 2017, Art. no. 041101, doi: 10.7567/APEX.10.041101.

- [15] Z. Xia, C. Joishi, S. Krishnamoorthy, S. Bajaj, Y. Zhang, M. Brenner, S. Lodha, and S. Rajan, "Delta doped β-Ga<sub>2</sub>O<sub>3</sub> field effect transistors with regrown ohmic contacts," *IEEE Electron Device Lett.*, vol. 39, no. 4, pp. 568–571, Apr. 2018, doi: 10.1109/LED.2018.2805785.