Iron core

# 3D MEMS In-Chip Solenoid Inductor With High Inductance Density for Power MEMS Device

Tiantong Xu<sup>®</sup>, Jiamian Sun, Hanxiao Wu, Haiwang Li, Hanqing Li, and Zhi Tao

Abstract-In this letter, we report the design and measurement of a 3D solenoid inductor that is embedded in a Si substrate and can integrate an iron core. Various inductor designs were fabricated with good structural integrity and repeatability via a CMOS-compatible MEMS fabrication process. The average inductance and guality factor peakto-peak variation of the inductors was below 10%, which indicates that the fabrication process is repeatable. Among the inductors without iron cores, the highest quality factor (37.6 at 21 MHz) was found in a 5-turn inductor, and the highest inductance and inductance density (respectively, 86.6 nH and 21.7 nH/mm<sup>2</sup>) were found in a 20-turn inductor. Among the iron-core inductors, the 15-turn inductor had an inductance of 1063 nH and an inductance density of 354.3 nH/mm<sup>2</sup>, nearly 18 times higher than the same design without an iron core, which is the highest inductance density for a MEMS microinductor to the best of our knowledge. This type of inductor is an important component in RF MEMS and electromagnetic power MEMS devices and can improve their performance and efficiency.

*Index Terms*— Solenoid inductor, power MEMS, high inductance density, CMOS-compatible fabrication process.

## I. INTRODUCTION

THE inductor is the most basic component of electromagnetic devices and the fundamental building block of electronic devices. Micro inductors are now widely used in microsensors [1], microactuators [2], RF MEMS [3], [4], and power MEMS. Power MEMS devices, such as transformers [5], [6], energy harvesters [7], and electromagnetic motors [8], usually require inductors with high inductance for power density and a high quality factor for efficiency. As MEMS devices are becoming increasingly compact, they also require inductors with high current capacity but compact physical dimensions. These demands can be fulfilled by integrating all power electronic components into one chip [9], [10]; higher integration will lower cost, reduce the space needed, and increase power density. Therefore,

Manuscript received July 2, 2019; revised August 26, 2019 and September 9, 2019; accepted September 9, 2019. Date of publication September 13, 2019; date of current version October 29, 2019. This work was supported by the project "High-Speed Moving Component Dynamic Tester" under Grant SQ2017YFZG010204. The review of this letter was arranged by Editor S. Pourkamali. (*Corresponding author: Haiwang Li.*)

T. Xu, J. Sun, H. Wu, H. Li, and Z. Tao are with the School of Energy and Power Engineering, Beihang University, Beijing 100191, China (e-mail: 09620@buaa.edu.cn).

H. Li is with Microsystems Technology Laboratories, Massachusetts Institute of Technology, Boston, MA 02139 USA.

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2019.2941003

Structure of the inductor. The input and output of

Solenoid inductor

Fig. 1. Structure of the inductor. The input and output currents are indicated by the arrows. Ground-signal-ground (GSG) pads were designed for high-frequency measurements.

the inductor fabrication process needs to be CMOS compatible for integration. The reported CMOS-compatible MEMS fabrication technologies can be classified into two categories: on-chip and in-chip inductors. To fabricate on-chip inductors, surface micromachining techniques, such as sacrificial layer [11], [12] and UV-LIGA (Ultra Violet Lithographie, Galvanoformung and Abformung) [13], [14], are mature and widely used. The in-chip inductors can utilize the unused substrate volume and eliminate the inductor height above the substrate surface, which makes them easier to integrate with CMOS devices. Through-silicon-via technology is the most feasible method of fabricating in-chip inductors [15]-[17]. As high-aspect-ratio etching and electroplating is critical for building in-chip inductors, developing fabrication technology for it is still a challenge. Our group has reported the fabricaion process and properties of a silicon embedded inductor which we have been recently working on [18].

## **II. DESIGN AND FABRICATION**

In our design (Fig. 1.), the solenoid inductor is completely embedded in the silicon substrate through deep Si etching and Cu electroplating. The silicon-steel iron core is placed in the middle of the copper inductor. A SiO<sub>2</sub> layer is created by silicon thermal oxidation between the silicon substrate and the copper coil as the insulation layer.

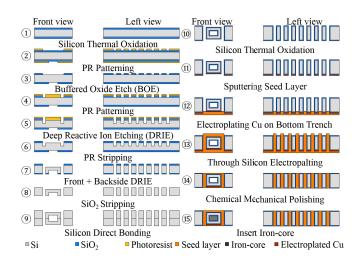

The fabrication process comprises two stages (Fig. 2.). In the first stage, namely the silicon etching and bonding stage, space is created for the solenoid inductor and iron core; 0.5-mm-thick double-side-polished silicon wafers (resistivity  $3.7 \ \Omega$ -cm) are used as substrates. The process was as follows. 1) Use thermal oxidation to create SiO<sub>2</sub> layers on both sides. 2) Coat SPR700 photoresist on both sides, and expose the horizontal trench, through-hole, and iron core patterns using an EVG mask aligner. 3) Perform a buffered oxide etch to remove the exposed oxide layer. 4) Coat AZ4620 photoresist on the top

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see http://creativecommons.org/licenses/by/4.0/

Fig. 2. Inductor fabrication process.

side, and expose the through-hole pattern. 6) Etch the throughholes with an inductively coupled plasma system (SPTS Co.). 7) Use piranha solution to remove the photoresist. 8) Use  $SiO_2$ as the mask layer, etch through-hole and horizontal trench patterns on the top side, and etch iron core and through-hole patterns on the back. 9) Use diluted HF solution to remove all of the  $SiO_2$  layer. 10) Use a bonder (EVG Co.) to conduct a silicon direct bonding process to create the iron-core space inside the substrate.

In the second stage, namely the copper filling stage, an electroplating process is used to create Cu coils. The process was as follows. 10) Use thermal oxidation to produce thick SiO<sub>2</sub> layer as an isolation between inductor and substrate. 11) Use a magnetron sputtering system (Denton Vacuum Co.) to sputter Cu (with Ni as middle layer) on the back as the seed layer. 12) Perform Cu electroplating until it fills the horizontal trenches and seals the through-holes at the back. 13) Cover the backside, preventing further Cu electroplating on this side. A "bottom-up" through-hole electroplating process was conducted to fill the through-holes and topside horizontal trenches. 14) Remove the Cu that had grown above the substrate surface by using a grinding machine (Logitech Co.). 15) Use a dicing machine (Disco Co.) to separate each inductor structure. Insert an iron core (China Baowu Steel Co.) in the center of the solenoid inductor.

### **III. EXPERIMENTAL RESULTS**

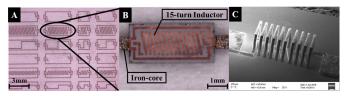

Eight different solenoid inductor designs were fabricated successfully with good structural integrity (Fig. 3 (a).). The inductors had four different turns (5/10/15/20) and two different widths (0.5/1 mm). The height of the inductors was 1 mm, the cross-section of the copper coils was a square with a side length of 100  $\mu$ m, and the gaps between the coils were also 100  $\mu$ m.

To examine the solid structure of the inductor solenoid more clearly, the silicon substrate of a 10-turn inductor was removed by etching in 25% tetramethyl ammonium hydroxide (TMAH) solution at 75 °C. The sample was then transferred to a Zeiss EVO 18 scanning electron microscope for further

Fig. 3. (a) Top view of inductors before dicing and insertion of the iron core. (b) 15-turn inductor after dicing with iron core inside. (c) Entire exposed solenoid coil structure under SEM.

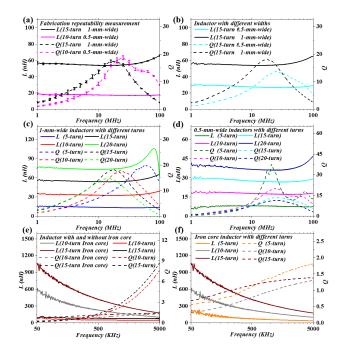

Fig. 4. Frequency-dependent inductance (L) and quality factor (Q) values for selected in-chip solenoid inductors. (a) Fabrication repeatability measurement: two inductor designs from three different process runs were tested. Mean and error bars are plotted. (b) Comparison of the inductor with different widths. (c) Comparison of 1-mm-wide inductors with different numbers of turns. (d) Comparison of 0.5-mm-wide inductors with different numbers of turns. (e) Comparison of inductors with and without iron cores. (f) Comparison of 1-mm-wide iron-core inductors with different numbers of turns.

observation (Fig. 3 (c).). The results show that the inductor structure morphology was fundamentally identical the design pattern and the structural integrity was good.

To test the performance of these inductors, an Agilent N5290A Vector Network Analyzer was used. The test probe was a Cascade ACP40-GSG-250 Air Coplanar Probe in conjunction with the Cascade Summit 12K Probe Station.

First, the performance of in-chip solenoid inductors without iron cores (Fig. 3 (a)) was measured. The testing frequency range was 1 MHz to 100 MHz; measurements were taken at regular intervals of 0.05 MHz (1981 total measurements).

Fig. 4 (a) shows the fabrication repeatability measurements for two inductor designs. For each design, we measured three inductors from different process runs. For all measurement points, the average peak-to-peak variation of the 15-turn 1-mm-wide inductor was 3.07% for inductance and 5.93% for quality factor, and the average peak-to-peak variation of the 10-turn 0.5-mm-wide inductor was 6.90% for inductance

TABLE I ELECTROMAGNETIC PERFORMANCE OF VARIOUS INDUCTOR DESIGNS

| Turns | Width<br>(mm) | Q <sub>peak</sub><br>@frequency<br>(MHz) | Q > 5<br>frequency<br>(MHz) | $\frac{L(nH)}{5}(Q > 5)$ | L <sub>density</sub><br>(nH/mm <sup>2</sup> ) |

|-------|---------------|------------------------------------------|-----------------------------|--------------------------|-----------------------------------------------|

| 5     | 0.5           | 37.6 @ 21.0                              | 6.5–100                     | 7.33-8.17                | 14.7–16.3                                     |

| 10    | 0.5           | 20.1 @ 23.0                              | 4.45-100                    | 16.8–18.7                | 16.8-18.7                                     |

| 15    | 0.5           | 13.8 @ 25.2                              | 5.7-100                     | 26.5-29.0                | 17.7–19.3                                     |

| 20    | 0.5           | 11.4 @ 24.25                             | 6.05–79.9                   | 35.8-42.4                | 17.9–21.2                                     |

| 5     | 1             | 19.8 @ 59.85                             | 5.7-100                     | 13.4–14.6                | 13.4–14.6                                     |

| 10    | 1             | 18.0 @ 22.6                              | 4.15-90.4                   | 32.6-38.3                | 16.3-19.2                                     |

| 15    | 1             | 18.2 @ 17.5                              | 2.35-68.75                  | 53.9-60.0                | 18.0-20.0                                     |

| 20    | 1             | 14.7 @ 14.6                              | 2.3-51.05                   | 73.3-86.6                | 18.3–21.7                                     |

WITHOUT IRON CORE

TABLE II

ELECTROMAGNETIC PERFORMANCE OF INDUCTORS WITHOUT AND

WITH IRON CORES

| Turns | Without iron core                        |                   |                                               | With iron core    |                     |                                               |

|-------|------------------------------------------|-------------------|-----------------------------------------------|-------------------|---------------------|-----------------------------------------------|

|       | Q <sub>peak</sub><br>@frequency<br>(MHz) | L (nH)<br>(Q > 5) | L <sub>density</sub><br>(nH/mm <sup>2</sup> ) | Q (0.05–5<br>MHz) | L (nH)<br>@0.05 MHz | L <sub>density</sub><br>(nH/mm <sup>2</sup> ) |

| 5     | 19.8@59.85                               | 14.6              | 14.6                                          | 0.57-1.74         | 229.5               | 229.5                                         |

| 10    | 18.0@22.6                                | 38.3              | 19.2                                          | 0.31-1.28         | 620.8               | 310.4                                         |

| 15    | 18.2@17.5                                | 60                | 20                                            | 0.68–1.31         | 1063                | 354.3                                         |

and 7.13% for quality factor. These relatively small variations indicate that the fabrication process is stable and repeatable. Fig. 4 (b) and (c) compare the electromagnetic performances of inductors with different numbers of turns. The highest Q was found in a 5-turn inductor, for which the peak Q was 37.6 at 21 MHz, with an inductance of 8.17 nH. The highest inductance density was found in a 20-turn inductor, in which the inductance density was 21.7 nH/mm<sup>2</sup> and the inductance was 86.6 nH, whereas the peak Qwas 14.7 at 14.6 MHz. Fig. 4 (d) shows the influence of width on inductor performance. Performance details for each inductor design are presented in Table I.

Subsequently, the silicon-steel iron cores were inserted into the solenoid inductor, and the performance of the ironcore solenoid inductor was measured. As the performance of silicon steel will obviously decrease at higher frequencies, we decreased the testing frequency range to 0.05–5 MHz, taking measurements at regular intervals of 0.05 MHz (500 data points in all).

Fig. 4 (e) compares the electromagnetic performances of two designs before and after insertion of the iron core. The iron core markedly improves the inductance and inductance density. For the 15-turn 1-mm-wide inductor, the inductance after insertion of the iron core was 1063 nH with an inductance density of 354.3 nH/mm<sup>2</sup>, nearly 18 times higher than the same design without the iron core. However, the silicon steel will generate a large induced current in the high frequency and cause serious eddy current loss, causing the inductor to

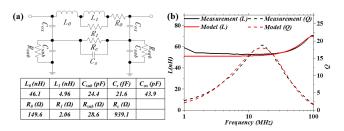

Fig. 5. Equivalent circuit model of a 15-turn 1-mm-wide inductor. (a) Equivalent circuit and extracted parameters. (b) Comparison of measured and modeled parameters.

suffer from a low quality factor. The quality factor of the silicon-steel iron core inductor was approximately one in all measurements. In the future, we will try replacing the silicon-steel core with ferrite to decrease the eddy current loss at high frequency. Fig. 4 (f) compares the iron-core inductors with different numbers of turns. Here the rate of increase in induction is higher than the rate of increase in the number of turns. The performance details for selected inductors with and without iron cores are given in Table II.

Fig. 5 (a) shows an equivalent circuit model of a 15turn 1-mm-wide inductor. In this model,  $R_0$  and  $L_0$  is the theoretical series resistance and inductance. The combination of  $L_1$  and  $R_1$  represents the variation with frequency due to the skin effect and proximity effect. The  $C_{ox}$  represents the coupling capacitance between metal segments and substrate.  $C_s$  represents the parasitic capacitances among different parts of metal segments and  $R_c$  is the substrate loss resistance. The combination of  $R_{sub}$  and  $C_{sub}$  represents the parasitic capacitances between inductor and ground metal. The extracted lumped-circuit parameters of the inductor were shown in the table of Fig. 5 (a). Fig. 5 (b) compares the measured and modeled parameters. The result shows modeled parameters are in good agreement with measurements.

#### **IV. CONCLUSION**

In this letter, we reported the design of a 3D solenoid inductor that is embedded in the substrate and can integrate an iron core. The fabrication process is CMOS-compatible, any standard CMOS process can be conducted after the inductor was fabricated on the silicon substrate. Eight inductor designs were fabricated with good structural integrity and repeatability. Among the inductors without iron cores, the highest quality factor (37.6 at 21 MHz) was found in a 5-turn inductor, and the highest inductance and inductance density (respectively, 86.6 nH and 21.7 nH/mm<sup>2</sup>) were found in a 20-turn inductor. For iron core inductors, an inductance of 1063 nH with an inductance density of 354.3 nH/mm<sup>2</sup> was found in the 15turn structure, which is the highest inductance density for an MEMS inductor reported thus far, to the best of our knowledge. Based on the structural and performance characteristics of this inductor, we believe that this in-chip solenoid inductor can be used in power MEMS devices, improving the power density and efficiency of these devices. We plan to design and study micro transformers, micro-vibration energy harvesters, and micro electromagnetic motors based on this type of inductor in the near future.

#### REFERENCES

- M. B. Coskun, K. Thotahewa, Y.-S. Ying, M. Yuce, A. Neild, and T. Alan, "Nanoscale displacement sensing using microfabricated variable-inductance planar coils," *Appl. Phys. Lett.*, vol. 103, Oct. 2013, Art. no. 143501. doi: 10.1063/1.4823828.

- Art. no. 143501. doi: 10.1063/1.4823828.

[2] S. S. Bedair, J. S. Pulskamp, C. D. Meyer, M. Mirabelli, R. G. Polcawich, and B. Morgan, "High-performance micromachined inductors tunable by lead zirconate titanate actuators," *IEEE Electron Device Lett.*, vol. 33, no. 10, pp. 1483–1485, Oct. 2012. doi: 10.1109/LED.2012.2207700.

- [3] J. J. Yao, "RF MEMS from a device perspective," J. Micromech. Microeng., vol. 10, no. 4, pp. 9–38, Dec. 2000. doi: 10.1088/0960 -1317/10/4/201.

- [4] J.-B. Yoon, B.-K. Kim, C.-H. Han, E. Yoon, and C.-K. Kim, "Surface micromachined solenoid on-Si and on-glass inductors for RF applications," *IEEE Electron Device Lett.*, vol. 20, no. 9, pp. 487–489, Sep. 1999. doi: 10.1109/55.784461.

- [5] J. Y. Park and J. U. Bu, "Packaging compatible microtransformers on a silicon substrate," *IEEE Trans. Adv. Packag.*, vol. 26, no. 2, pp. 160–164, May 2003. doi: 10.1109/tadvp.2003.817341.

- [6] R. Wu, J. Chen, and X. Fang, "A novel on-chip transformer with patterned ground shield for high common-mode transient immunity isolated signal transfer," *IEEE Electron Device Lett.*, vol. 39, no. 11, pp. 1712–1715, Nov. 2018. doi: 10.1109/LED.2018.2871049.

[7] Y. Wang, Q. Zhang, L. Zhao, Y. Tang, A. Shkel, and E. S. Kim,

- [7] Y. Wang, Q. Zhang, L. Zhao, Y. Tang, A. Shkel, and E. S. Kim, "Vibration energy harvester with low resonant frequency based on flexible coil and liquid spring," *Appl. Phys. Lett.*, vol. 109, no. 20, 2016, Art. no. 203901. doi: 10.1063/1.4967498.

- [8] O. Cugat, G. Reyne, J. Delamare, and H. Rostaing, "Novel magnetic micro-actuators and systems (MAGMAS) using permanent magnets," *Sens. Actuator A, Phys.*, vol. 129, nos. 1–2, pp. 265–269, May 2006. doi: 10.1016/j.sna.2005.09.058.

- [9] M. Araghchini, J. Chen, V. Doan-Nguyen, D. V. Harburg, D. Jin, J. Kim, M. S. Kim, S. Lim, B. Lu, D. Piedra, J. Qiu, J. Ranson, M. Sun, X. Yu, H. Yun, M. G. Allen, J. A. Alamo, G. DesGroseilliers, F. Herrault, J. H. Lang, C. G. Levey, C. B. Murray, D. Otten, T. Palacios, D. J. Perreault, and C. R. Sullivan, "A technology overview of the powerchip development program," *IEEE Trans. Power Electron.*, vol. 28, no. 9, pp. 4182–4201, Sep. 2013. doi: 10.1109/TPEL.2013.2237791.

- [10] S. C. O. Mathuna, T. O'Donnell, N. Wang, and K. Rinne, "Magnetics on silicon: An enabling technology for power supply on chip," *IEEE Trans. Power Electron.*, vol. 20, no. 3, pp. 585–592, May 2005. doi: 10.1109/TPEL.2005.846537.

- [11] H. Jiang, Y. Wang, J. L. A. Yeh, and N. C. Tien, "On-chip spiral inductors suspended over deep copper-lined cavities," *IEEE Trans. Microw. Theory Techn.*, vol. 48, no. 12, pp. 2415–2423, Dec. 2000. doi: 10.1109/22.898992.

- [12] W. Xu, S. Sinha, T. Dastagir, H. Wu, D. S. Gardner, Y. Cao, and H. Yu, "Performance enhancement of on-chip inductors with permalloy magnetic rings," *IEEE Electron Device Lett.*, vol. 32, no. 1, pp. 69–71, Jan. 2011. doi: 10.1109/LED.2010.2089779.

- [13] M. K. Ghantasala, J. P. Hayes, E. C. Harvey, and D. K. Sood, "Patterning, electroplating and removal of SU-8 moulds by excimer laser micromachining," *J. Micromech. Microeng.*, vol. 11, no. 2, pp. 133–139, Feb. 2001. doi: 10.1088/0960-1317/11/2/308.

- [14] X. Fang, R. Wu, L. Peng, and J. K. O. Sin, "A novel integrated power inductor with vertical laminated core for improved L/R ratios," *IEEE Electron Device Lett.*, vol. 35, no. 12, pp. 1287–1289, Dec. 2014. doi: 10.1109/led.2014.2362749.

- [15] X. Yu, M. Kim, F. Herrault, C. H. Ji, J. Kim, and M. G. Allen, "Silicon-embedding approaches to 3-D Toroidal inductor fabrication," *J. Microelectromech. Syst.*, vol. 22, no. 3, pp. 580–588, Jun. 2013. doi: 10.1109/JMEMS.2012.2233718.

- [16] R. Wu, S. Raju, M. Chan, J. K. O. Sin, and C. P. Yue, "Silicon-embedded receiving coil for high-efficiency wireless power transfer to implantable biomedical ICs," *IEEE Electron Device Lett.*, vol. 34, no. 1, pp. 9–11, Jan. 2013. doi: 10.1109/LED.2012.2225135.

- [17] R. Wu and J. K. O. Sin, "A novel silicon-embedded coreless inductor for high-frequency power management applications," *IEEE Electron Device Lett.*, vol. 32, no. 1, pp. 60–62, Jan. 2011. doi: 10.1109/LED.2010.2082489.

- [18] T. Xu, J. Sun, H. Wu, H. Li, H. Li, J. Xia, Z. Tao, and M. A. Schmidt, "A 3D MEMS in-chip solenoid inductor of high inductance density for future power-MEMS device," in *Proc. 20th Int. Conf. Solid-State Sensors, Actuat. Microsyst. Eurosensors*, Jun. 2019, pp. 1459–1462. doi: 10.1109/TRANSDUCERS.2019.8808466.