# Analytical Modeling of Cryogenic Subthreshold Currents in 22-nm FDSOI Technology

Hung-Chi Han<sup>®</sup>, Student Member, IEEE, Zhixing Zhao, Steffen Lehmann, Edoardo Charbon<sup>®</sup>, Fellow, IEEE, and Christian Enz<sup>®</sup>, Life Fellow, IEEE

Abstract—The transistor compact model is crucial but has yet to mature for cryogenic electronics. This paper presents a sophisticated analytical model of the MOSFET subthreshold current at cryogenic temperatures, accounting for the thermionic, hopping, source-to-drain tunneling transports, and the Gaussian-distributed interface traps to bridge the gap. Hopping and source-to-drain tunneling transports can co-exist in the subthreshold regime, leading to subthreshold saturation strongly correlated to channel length and drain voltages.

Index Terms—Cryo-CMOS, band tail, FDSOI, hopping, modeling, quantum computing, subthreshold, tunneling.

## I. INTRODUCTION

▶ MOS technology has been proven to be a promising solution to scale-up solid-state quantum computers [1], [2]. In this perspective, CMOS front-end electronics operates at cryogenic temperatures, handling the write-in and readout for quantum bits. However, today's compact models cannot accurately predict transistor performance at cryogenic temperatures [3]. It makes circuit design a real challenge. Although recent works have tempted to modify existing compact models to mitigate the need [3], [4], [5], [6], some cryogenic phenomena are still unclear. For example, the subthreshold swing (SS), measuring the switching efficiency between on- and off-states, decreases and then saturates at cryogenic temperatures [7], [8], [9], [10], [11], [12], [13]. Therefore, transistors do not have sharp subthreshold behavior as predicted by the Boltzmann limit. Nonetheless, the mechanism causing the SS saturation has been debated in the past few years. The saturation of SS has been shown to be due to the exponential band tail that extends from the conduction band or the valence band [7], [8], [14], [15]. If the defect-induced band tail is assumed, the carriers hop via the localized states [16]. On the other hand,

Manuscript received 13 October 2023; revised 2 November 2023; accepted 5 November 2023. Date of publication 8 November 2023; date of current version 29 December 2023. This work was supported by the European Union's Horizon 2020, SEQUENCE, under Grant 871764. The review of this letter was arranged by Editor V. Moroz. (Corresponding author: Hung-Chi Han.)

Hung-Chi Han, Edoardo Charbon, and Christian Enz are with École Polytechnique Fédérale de Lausanne, 1015 Lausanne, Switzerland (e-mail: hung.han@epfl.ch).

Zhixing Zhao and Steffen Lehmann are with GlobalFoundries, 01109 Dresden, Germany.

Color versions of one or more figures in this letter are available at https://doi.org/10.1109/LED.2023.3331022.

Digital Object Identifier 10.1109/LED.2023.3331022

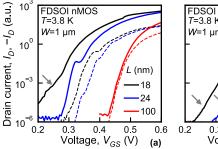

Fig. 1. Experimental transfer characteristics of FDSOI nMOS and pMOS at 3.8 K for various channel lengths. The solid and dashed lines correspond to  $V_{DS}=0.8$  V and 10 mV, respectively. Arrows highlight the parts with significant SDT.

source-to-drain tunneling (SDT) has also been shown to lead to SS saturation for a short-channel device [9], [12], [13], [17]. As shown in Fig. 1, the subthreshold current behaves differently between low and high  $V_{DS}$ , where a significantly large SS presents in a deep weak inversion for extremely short devices, e.g., channel length  $L \lesssim 20$  nm. This behavior can neither be explained by the hopping transport nor by the SDT alone. Instead of a single mechanism, it relies on multiple mechanisms as shown in the simulation work [18]. Hence, this work proposes an analytical subthreshold current and swing model, accounting for thermionic, hopping, and source-to-drain tunneling currents. This model would provide insight into the actual root cause of the degradation.

## II. ANALYTICAL MODELING

At cryogenic temperatures, the thermionic current  $(I_{th})$  may not dominate the subthreshold drain current  $(I_{sub})$  due to the onset of other transport mechanisms, such as tunneling or hopping transports. Among the current components, the resonant tunneling manifests randomly due to the ionized defects in the channel [10], [19]. Also, the resonant tunneling in an FDSOI technology has been modeled based on the single electron transistor [20]. Hence, the model excludes resonant tunneling, and  $I_{sub}$  is then given by

$$I_{sub} = I_{th} + I_{hop} + I_{sdt}, (1)$$

with  $I_{sdt}$  the source-to-drain tunneling current,  $I_{hop}$  the hopping current. The  $I_{th}$  is well established by using Landauer formalism [21]. The following derivation focuses on  $I_{hop}$  and

$I_{sdt}$ , and assumes a two-dimensional gas due to the ultra-thin channel for a 22 nm FDSOI technology, e.g.,  $\lesssim 6 \text{ nm}$  [22].

By adopting a unified current-voltage model [23],  $I_{hop}$ is given by  $I_{hop} = \mu_{hop} k_B T \frac{W}{L} n_{hop} \left( 1 - e^{\frac{-qV_{DS}}{k_B T}} \right)$ elementary charge,  $n_{hop}$  hopping carrier density at source,  $\mu_{hop}$  hopping mobility,  $k_B$  Boltzmann constant, T temperature, and W device width. In the following derivation, it is assumed that  $\mu_{hop}$  remains constant for simplicity, although it theoretically varies with gate bias [24]. The  $n_{hop}$  =  $N_{2D}^c \int_{-\infty}^{E_b} e^{\frac{E-\check{E}_b}{W_t}} f(E) dE$  with  $N_{2D}^c$  two-dimensional density of states,  $E_b$  conduction band edge,  $W_t$  characteristic energy of band tail, and f(E) Fermi-Dirac function [8]. The integral of  $n_{hop}$  yields the Gauss hypergeometric function [25], which can be simplified by the first-order approximation. It leads to  $n_{hop} \approx n_{hop_1} + n_{hop_2}$  with  $n_{hop_1} = N_{2D}^c W_t \frac{\theta}{\theta - 1} e^{\frac{-E_{bf}}{k_B T}}$  and  $n_{hop_2} = N_{2D}^c W_t \frac{1}{\sin(\pi \theta)} e^{\frac{-E_{bf}}{W_t}}$ , where  $\theta = k_B T/W_t$  and  $E_{bf}$  is the energy from bornion and tthe energy from barrier peak to the Fermi level at the source. Inserting the approximated  $n_{hop}$  into the current-voltage model writes  $I_{hop} \approx I_{hop_1} + I_{hop_2}$ . Two currents correspond to  $n_{hop_1}$ and  $n_{hop}$ , and represent the asymptotes of hopping transport;  $I_{hop_1}$  exponentially scales with T, and  $I_{hop_2}$  depends on energy  $W_t$ . The characteristics of  $I_{hop_1}$  and  $I_{hop_2}$  project themselves to the nearest-neighbor hopping and variable-range hopping, which dominate at high and low temperatures, respectively [26]. The latter hops near the Fermi level and has less temperature dependence [27]. On the other hand, the SDT current can be expressed in an analytical form by adopting a quadratic function that describes the short-channel gate barrier, given by [13] The direct tunneling probability depends on the energy  $W_{sdt} = \hbar \sqrt{q V_a} / \left(\pi L \sqrt{2m^*}\right)$  with  $\hbar$  the reduced Plank constant and  $m^*$  the effective mass. The term  $V_a$  is a potential describing the parabolic gate barrier [13].

Consequently, SS is derived from (1) and is written as

$$SS_{tot} = n \left(\frac{k_B T}{q}\right) \ln (10) \left[\alpha_{th} + \alpha_{hop} \beta_{hop_1} + \alpha_{hop} \beta_{hop_2} \frac{k_B T}{W_t} + \alpha_{sdt} \frac{k_B T}{W_{sdt}} \left(1 + \frac{-U_b}{q V_a} \frac{\partial V_a}{\partial V_{pk}}\right)\right]^{-1}, \tag{2}$$

with n the slope factor,  $U_b$  the gate barrier energy, current ratios  $\alpha_{th} = I_{th}/I_{sub}$ ,  $\alpha_{hop} = I_{hop}/I_{sub}$ , and  $\alpha_{sdt} =$  $I_{sdt}/I_{sub}$ . The sum of the current ratios,  $\alpha_{th} + \alpha_{hop} + \alpha_{sdt}$ , equals one. The terms  $\beta_{hop_1} = I_{hop_1}/I_{hop}$  and  $\beta_{hop_2} =$  $I_{hop_2}/I_{hop}$  are the hopping current ratios. Due to the subthreshold regime, it ignores the mobile charges and then writes  $V_{GS} = \Phi_{mf} + \psi_{sf} + (Q_{dep}^* - Q_0)/C_{fox}$  with  $\Phi_{mf}$  the work function difference between the front gate and channel,  $\psi_{sf}$  the front-surface potential referenced to Fermi level at source,  $C_{fox}$  the front-gate capacitance,  $Q_{dep}^*$  the effective depletion change for short-channel effect [28], and  $Q_0$  the interface charges. Gaussian-distributed localized states have been reported to center around the band edge at cryogenic temperatures, resulting in the inflection phenomenon [29]. It is expressed by  $Q_0 = -q \frac{N_0}{2} \left[ \text{erf} \left( \frac{-2E_{bf}}{W_0 \sqrt{2}} \right) + 1 \right]$  with  $W_0$  the width of twice the standard deviation and  $N_0$  the

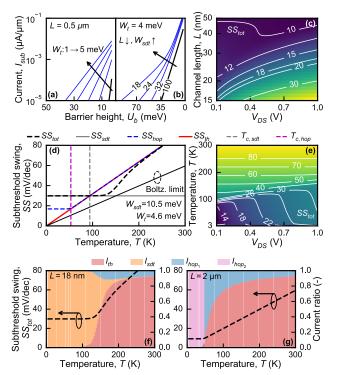

Fig. 2. (a,b)  $W_t$  and  $W_{sdt}$  influence on  $I_{sub}$  versus  $U_b$  at 4 K and  $V_{DS}=1$  V, the various channel lengths in nm are annotated in (b) for each curve. Note that (a, b) are plotted with  $U_b$ , the inflection phenomenon embedded in n is not presented. (c)  $SS_{tot}$  in terms of L and  $V_DS$  with  $U_b=50$  meV at 4 K (d) Decomposition of SS in terms of T for  $V_{DS}=1$  V,  $U_b=0.1$  eV, and L=18 nm, (e)  $SS_{tot}$  with respect to T and  $V_{DS}$  for L=18 nm,  $U_b=10\sqrt{300/T}k_BT$ . Calculated  $SS_{tot}$  vs. T with current decomposition for (f) L=18 nm and (g) L=2  $\mu$ m with  $V_{DS}=1$  V,  $W_t=4$  meV, and  $U_b=0.1$  eV. The color shows the percentage for each current component.

scale of Gaussian [29]. As a consequence,  $n = \frac{\partial V_{GS}}{\partial \psi_{sf}} = 1 + \frac{1}{C_{fox}} \left( \frac{\partial \mathcal{Q}^*_{dep}}{\partial \psi_{sf}} - \frac{\partial \mathcal{Q}_0}{\partial \psi_{sf}} \right)$  includes the short-channel effect and Gaussian-distributed interface charges.

In the proposed model, two energies related to the band-tail states and direct tunneling probability, i.e.,  $W_t$  and  $W_{sdt}$ , are crucial for  $I_{sub}$ . As presented in Fig. 2(a,b), the increase of  $W_t$  and  $W_{sdt}$  lifts  $I_{sub}$  up, of which the raised  $W_{sdt}$  due to the shorten L particularly degrades SS at the lower current level. Fig. 2(c) further analyzes the SDT-induced degradation on  $SS_{tot}$  at 4 K, where the down-scaled L and  $V_{DS}$  are two main reasons that cause the higher  $SS_{tot}$ . Eq. (2) is presented in Fig. 2(d) as a function of temperature with other SS components. The  $SS_{th} = SS_{tot}|_{\alpha_{th}=1,\alpha_{hop}=\alpha_{sdt}=0}$  stands for the thermionic SS, which linearly scales with T following the Boltzmann limit. The  $SS_{hop} = SS_{tot}|_{\alpha_{hop}=1,\alpha_{sdt}=\alpha_{th}=0}$  for  $I_{hop}$ is proportional to T above the critical temperature, denoted by  $T_{c,hop}$ , where  $SS_{hop} = SS_{th}$ . For  $T < T_{c,hop}$ ,  $SS_{hop}$  saturates at the value of  $n\left(\frac{W_t}{q}\right) \ln{(10)}$  with  $\beta_{hop_2} = 1$ . Regarding SDT, thermal energy assists carriers in tunneling the gate barrier, which yields a larger current at higher T. Whereas  $SS_{sdt} =$  $SS_{tot}|_{\alpha_{sdt}=1,\alpha_{th}=\alpha_{hop}=0}$  is temperature-independent and has a value given by  $n\left(\frac{W_{sdt}}{q}\right) \ln{(10)} \left(1 + \frac{-U_b}{qV_a} \frac{\partial V_a}{\partial V_{pk}}\right)^{-1}$ . The critical temperature due to  $I_{sdt}$ , denoted by  $T_{c,sdt}$ , is therefore defined by T such that  $SS_{sdt} = SS_{th}$ . In the case of an extremely

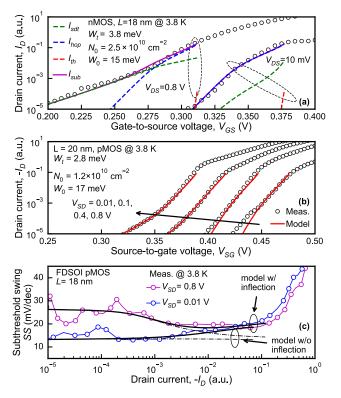

Fig. 3. Model validation by meausrement of 22 nm FDSOI technology at 3.8 K, various voltages are included. (a) transfer characteristic of an nMOS with L=18 nm, each current component is plotted. (b) transfer characteristic of a pMOS with L=20 nm, the model  $I_{sub}$  is compared. (c) subthreshold swing versus  $-I_D$ , Eq. (2) with and without Gaussiandistributed interface charge (inflection) is compared. Tunneling  $m^*$  is 0.12 and 0.13 for electrons and holes, separately.

short channel and high  $V_{DS}$ , it leads to  $W_{sdt} > W_t$ , and  $I_{sdt}$ dominates at cryogenic temperatures, as shown in Fig. 2(b). Consequently, the  $SS_{tot}$  saturates at  $SS_{sdt}$  as  $T < T_{c,sdt}$ . Additionally, it is worth noting that  $SS_{tot}$  is lower than  $SS_{th}$ as  $100 \,\mathrm{K} \lesssim T \lesssim 200 \,\mathrm{K}$ . It is ascribed to  $I_{sdt}$  that contributes significantly to  $I_{sub}$  over the  $I_{th}$  and  $I_{hop}$ . However, Eq. (2) shows  $SS_{tot}$  varying with  $U_b$ . It is difficult to compare the experimental SS to (2) due to the unknown  $U_b$  condition. Nevertheless, the averaged SS from the measurement in Fig. 9 of [11] may provide the reference. Fig. 2(e) gives a more realistic example on  $SS_{tot}$  with respect to T and  $V_{DS}$ , where  $U_b$ changing with T gives a reasonable weak inversion condition. It reveals that the higher  $V_{DS}$  leads to  $SS_{tot}$  saturating at the higher T. Fig. 2(e,g) shows the detailed current break down on  $SS_{tot}$  versus T for  $L = 18 \,\mathrm{nm}$  and  $2 \,\mathrm{\mu m}$ . At  $T = 300 \,\mathrm{K}$ , both cases have around 90% of  $I_{th}$  and 10% of  $I_{hop_1}$ . With T decreasing, for  $L = 18 \,\mathrm{nm}$ ,  $I_{sdt}$  gradually takes over other current components and finally dominates  $I_{sub}$ . In contrast, for  $L = 2 \,\mu\text{m}$ ,  $I_{hop_1}$  competes with  $I_{th}$  from 300 to 50 K, then  $I_{sub} = I_{hop_2}$  below  $T_{c,hop}$ . The sharp transition from  $I_{hop_1}$ to  $I_{hop}$ , is due to the first-order approximation of the Gauss hypergeometric function [25].

## III. EXPERIMENTAL VALIDATION AND DISCUSSION

The proposed model is validated by the cryogenic measurement of a commercial 22 nm FDSOI technology [22]. Fig. 3(a) presents a good agreement of the current model compared to the transfer characteristics of an nMOS at 3.8 K.

At  $V_{DS} = 10 \,\text{mV}$ ,  $I_{hop}$  dominates the  $I_{sub}$  and captures the measured  $I_D$  while  $I_{th}$  and  $I_{sdt}$  are negligible. Conversely, at  $V_{DS} = 0.8 \,\mathrm{V}$ , the experimental  $I_{sub}$  shows two regions with different slopes, separated at  $V_{GS} \approx 0.275 \,\mathrm{V}$ . The region with a lower current level is controlled by  $I_{sdt}$ , while another region is ascribed to  $I_{hop}$ . Note that  $W_t$  for the band tail and  $N_0$  and  $W_0$  for the interface states are fitting parameters, while  $W_{sdt}$  is the function of  $V_a$ , L, and  $m^*$  [13]. Since  $W_{sdt}$  relates to  $V_a$  that changes with  $U_b$ ,  $W_{sdt}$  in Fig. 3(a) ranges from  $1.2 \sim 3.4 \,\mathrm{meV}$  for low  $V_{DS}$  and varies from  $8 \sim 10 \,\mathrm{meV}$  for high  $V_{DS}$ . When  $W_{sdt}$  is significantly larger than  $W_t$ , the SDT yields a much more degraded SS than that hopping transport does. Fig. 3(b) shows the model validation by a pMOS with  $L = 20 \,\mathrm{nm}$  at 3.8 K with various  $V_{SD}$ . Parameters  $(W_t, W_0,$ and  $N_0$ ) are consistent from  $V_{SD} = 10 \,\mathrm{mV}$  to 0.8 V. The high  $V_{SD}$  results in SDT that degrades SS. At  $V_{DS} = 10 \,\mathrm{mV}$ , the model does not fit well to the lower current region, it is likely due to the weak resonant tunneling phenomenon. Regarding the current-dependent characteristic of SS, Eq. (2) compares to the experiments of a pMOS FDSOI with  $L = 18 \,\mathrm{nm}$ at 3.8 K shown in Fig. 3(c). The model accounting for the inflection phenomenon agrees better with the measurement than the one excluding inflection. In the case of  $V_{DS} = 0.8 \,\mathrm{V}$ , a clear transition of SS presenting around  $-I_D = 10^{-3}$  a.u. is ascribed to  $I_{sdt}$  competing with  $I_{hop}$ .

Knowing what transport dominates  $I_{sub}$  can efficiently improve SS. As presented in Fig. 2(c), devices with  $L \gtrsim$ 40 nm has a negligible SDT effect, where SS does not vary with  $V_{DS}$  significantly. In such a case, SS saturation is due to the band tail. Optimal implantation of ions in the silicide process has been reported to reduce the degradation by the band tail and interface states [30]. When SS saturation is mainly due to SDT, lowering  $W_{sdt}$  helps improve SS. In addition to using the minimal L, several methods can reduce the SDT current, such as; (1) implementing a thin tunneling barrier at the source junction [9], (2) increasing  $m^*$  by strain engineering [31] or by taking a certain crystal direction, and (3) reducing the supply voltage. The first two approaches require a different device process, and the second comes at the cost of poorer mobility. As shown in Fig. 2(c,e), bringing  $V_{DS}$  down can substantially reduce SS saturated value. However, such a method may pull a transistor out of the saturation region, raising the issue of gain or linearity. Fortunately, FDSOI technology modulates the threshold voltage electrostatically through the back-gate voltage (model in [32]). The supply voltage can be scaled down by adopting the low-threshold voltage scheme.

## IV. CONCLUSION

An analytical model of the cryogenic subthreshold current and swing has been derived and validated with a commercial 22 nm FDSOI technology. It finds that hopping and source-to-drain tunneling currents can co-exist in a short channel with strong  $V_{DS}$ . Decomposing the subthreshold current into thermionic, hopping, and source-to-drain tunneling components, provides a better understanding of the subthreshold degradation in terms of temperature, voltage, and channel length. This paper proposes approaches to improve cryogenic subthreshold performance by knowing the root reason causing the SS saturation.

#### REFERENCES

- E. Charbon, F. Sebastiano, A. Vladimirescu, H. Homulle, S. Visser, L. Song, and R. M. Incandela, "Cryo-CMOS for quantum computing," in *IEDM Tech. Dig.*, Dec. 2016, pp. 13.5.1–13.5.4, doi: 10.1109/IEDM.2016.7838410.

- [2] B. Patra, R. M. Incandela, J. P. G. van Dijk, H. A. R. Homulle, L. Song, M. Shahmohammadi, R. B. Staszewski, A. Vladimirescu, M. Babaie, F. Sebastiano, and E. Charbon, "Cryo-CMOS circuits and systems for quantum computing applications," *IEEE J. Solid-State Circuits*, vol. 53, no. 1, pp. 309–321, Jan. 2018, doi: 10.1109/JSSC.2017. 2737549

- [3] A. Akturk, M. Holloway, S. Potbhare, D. Gundlach, B. Li, N. Goldsman, M. Peckerar, and K. P. Cheung, "Compact and distributed modeling of cryogenic bulk MOSFET operation," *IEEE Trans. Electron Devices*, vol. 57, no. 6, pp. 1334–1342, Jun. 2010, doi: 10.1109/TED.2010.2046458.

- [4] R. M. Incandela, L. Song, H. Homulle, E. Charbon, A. Vladimirescu, and F. Sebastiano, "Characterization and compact modeling of nanometer CMOS transistors at deep-cryogenic temperatures," *IEEE J. Electron Devices Soc.*, vol. 6, pp. 996–1006, 2018, doi: 10.1109/JEDS.2018.2821763.

- [5] G. Pahwa, P. Kushwaha, A. Dasgupta, S. Salahuddin, and C. Hu, "Compact modeling of temperature effects in FDSOI and FinFET devices down to cryogenic temperatures," *IEEE Trans. Electron Devices*, vol. 68, no. 9, pp. 4223–4230, Sep. 2021, doi: 10.1109/TED.2021. 3097971.

- [6] J. Huang, Y. Zhang, Y. Chen, J. Xu, C. Luo, and G. Guo, "Characterization and compact modeling of short channel MOSFETs at cryogenic temperatures," *Solid-State Electron.*, vol. 204, Jun. 2023, Art. no. 108637, doi: 10.1016/j.sse.2023.108637.

- [7] H. Bohuslavskyi, A. G. M. Jansen, S. Barraud, V. Barral, M. Cassé, L. Le Guevel, X. Jehl, L. Hutin, B. Bertrand, G. Billiot, G. Pillonnet, F. Arnaud, P. Galy, S. De Franceschi, M. Vinet, and M. Sanquer, "Cryogenic subthreshold swing saturation in FD-SOI MOSFETs described with band broadening," *IEEE Electron Device Lett.*, vol. 40, no. 5, pp. 784–787, May 2019, doi: 10.1109/LED.2019. 2903111.

- [8] A. Beckers, F. Jazaeri, and C. Enz, "Theoretical limit of low temperature subthreshold swing in field-effect transistors," *IEEE Electron Device Lett.*, vol. 41, no. 2, pp. 276–279, Feb. 2020, doi: 10.1109/LED.2019.2963379.

- [9] K.-H. Kao, T. R. Wu, H.-L. Chen, W.-J. Lee, N.-Y. Chen, W. C. Ma, C.-J. Su, and Y.-J. Lee, "Subthreshold swing saturation of nanoscale MOSFETs due to source-to-drain tunneling at cryogenic temperatures," *IEEE Electron Device Lett.*, vol. 41, no. 9, pp. 1296–1299, Sep. 2020, doi: 10.1109/LED.2020.3012033.

- [10] H.-C. Han, F. Jazaeri, A. D'Amico, A. Baschirotto, E. Charbon, and C. Enz, "Cryogenic characterization of 16 nm FinFET technology for quantum computing," in *Proc. IEEE 47th Eur. Solid State Circuits Conf. (ESSCIRC)*, Sep. 2021, pp. 71–74, doi: 10.1109/ESS-CIRC53450.2021.9567747.

- [11] H.-C. Han, F. Jazaeri, A. D'Amico, Z. Zhao, S. Lehmann, C. Kretzschmar, E. Charbon, and C. Enz, "Back-gate effects on DC performance and carrier transport in 22 nm FDSOI technology down to cryogenic temperatures," *Solid-State Electron.*, vol. 193, Jul. 2022, Art. no. 108296, doi: 10.1016/j.sse.2022.108296.

- [12] K. Yilmaz, B. Iniguez, F. Lime, and A. Kloes, "Cryogenic temperature and doping analysis of source-to-drain tunneling current in ultrashort-channel nanosheet MOSFETs," *IEEE Trans. Electron Devices*, vol. 69, no. 3, pp. 1588–1595, Mar. 2022, doi: 10.1109/ted.2022. 3145339

- [13] H.-C. Han, H.-L. Chiang, I. P. Radu, and C. Enz, "Analytical modeling of source-to-drain tunneling current down to cryogenic temperatures," *IEEE Electron Device Lett.*, vol. 44, no. 5, pp. 717–720, May 2023, doi: 10.1109/LED.2023.3254592.

- [14] G. Ghibaudo, M. Aouad, M. Casse, S. Martinie, T. Poiroux, and F. Balestra, "On the modelling of temperature dependence of subthreshold swing in MOSFETs down to cryogenic temperature," *Solid-State Electron.*, vol. 170, Aug. 2020, Art. no. 107820, doi: 10.1016/j.sse.2020.107820.

- [15] A. Beckers, J. Michl, A. Grill, B. Kaczer, M. G. Bardon, B. Parvais, B. Govoreanu, K. De Greve, G. Hiblot, and G. Hellings, "Physics-based and closed-form model for cryo-CMOS subthreshold swing," *IEEE Trans. Nanotechnol.*, vol. 22, pp. 590–596, 2023, doi: 10.1109/TNANO.2023.3314811.

- [16] R. Asanovski, A. Grill, J. Franco, P. Palestri, A. Beckers, B. Kaczer, and L. Selmi, "Understanding the excess 1/f noise in MOSFETs at cryogenic temperatures," *IEEE Trans. Electron Devices*, vol. 70, no. 4, pp. 2135–2141, Apr. 2023, doi: 10.1109/TED.2022.3233551.

- [17] J. Wang and M. Lundstrom, "Does source-to-drain tunneling limit the ultimate scaling of MOSFETs?" in *IEDM Tech. Dig.*, Dec. 2002, pp. 707–710, doi: 10.1109/iedm.2002.1175936.

- [18] T. Jiao, E. Antunez, and H. Y. Wong, "Study of cryogenic MOS-FET sub-threshold swing using ab initio calculation," *IEEE Electron Device Lett.*, vol. 44, no. 10, pp. 1604–1607, Oct. 2023, doi: 10.1109/led.2023.3310511.

- [19] F. Jazaeri, A. Beckers, A. Tajalli, and J.-M. Sallese, "A review on quantum computing: From qubits to front-end electronics and cryogenic MOSFET physics," in *Proc. 26th Int. Conf. Mixed Design Integr. Circuits Syst. (MIXDES)*, Jun. 2019, pp. 15–25, doi: 10.23919/MIXDES.2019.8787164.

- [20] S. Pati Tripathi, S. Bonen, A. Bharadwaj, T. Jager, C. Nastase, S. Iordanescu, G. Boldeiu, M. Pasteanu, A. Nicoloiu, I. Zdru, A. Müller, and S. P. Voinigescu, "Characterization and modeling of quantum dot behavior in FDSOI devices," *IEEE J. Electron Devices Soc.*, vol. 10, pp. 600–610, 2022, doi: 10.1109/JEDS.2022.3176205.

- [21] S. Datta, Quantum Transport: Atom to Transistor. Cambridge, U.K.: Cambridge Univ. Press, 2005, doi: 10.1017/CBO9781139164313.

- [22] R. Carter, J. Mazurier, L. Pirro, J.-U. Sachse, P. Baars, J. Faul, C. Grass, G. Grasshoff, P. Javorka, T. Kammler, A. Preusse, S. Nielsen, T. Heller, J. Schmidt, H. Niebojewski, P.-Y. Chou, E. Smith, E. Erben, C. Metze, C. Bao, Y. Andee, I. Aydin, S. Morvan, J. Bernard, E. Bourjot, T. Feudel, D. Harame, R. Nelluri, H.-J. Thees, L. M-Meskamp, J. Kluth, R. Mulfinger, M. Rashed, R. Taylor, C. Weintraub, J. Hoentschel, M. Vinet, J. Schaeffer, and B. Rice, "22 nm FDSOI technology for emerging mobile, Internet-of-Things, and RF applications," in *IEDM Tech. Dig.*, Dec. 2016, pp. 2.2.1–2.2.4, doi: 10.1109/IEDM.2016.7838029.

- [23] C.-K. Park, C.-Y. Lee, K. Lee, B.-J. Moon, Y. H. Byun, and M. Shur, "A unified current-voltage model for long-channel nMOSFETs," *IEEE Trans. Electron Devices*, vol. 38, no. 2, pp. 399–406, Feb. 1991, doi: 10.1109/16.69923.

- [24] L. Wang, Y. Li, X. Gong, A. V. Thean, and G. Liang, "A physics-based compact model for transition-metal dichalcogenides transistors with the band-tail effect," *IEEE Electron Device Lett.*, vol. 39, no. 5, pp. 761–764, May 2018, doi: 10.1109/LED.2018.2820142.

- [25] A. Beckers, D. Beckers, F. Jazaeri, B. Parvais, and C. Enz, "Generalized Boltzmann relations in semiconductors including band tails," J. Appl. Phys., vol. 129, no. 4, Jan. 2021, Art. no. 045701, doi: 10.1063/5.0037432.

- [26] H. Qiu, T. Xu, Z. Wang, W. Ren, H. Nan, Z. Ni, Q. Chen, S. Yuan, F. Miao, F. Song, G. Long, Y. Shi, L. Sun, J. Wang, and X. Wang, "Hopping transport through defect-induced localized states in molybdenum disulphide," *Nature Commun.*, vol. 4, no. 1, Oct. 2013, Art. no. 2642, doi: 10.1038/ncomms3642.

- [27] A. Yildiz, N. Serin, T. Serin, and M. Kasap, "Crossover from nearest-neighbor hopping conduction to Efros-Shklovskii variable-range hopping conduction in hydrogenated amorphous silicon films," *Jpn. J. Appl. Phys.*, vol. 48, no. 11, Nov. 2009, Art. no. 111203, doi: 10.1143/jjap.48.111203.

- [28] J. Lacord, J.-L. Huguenin, T. Skotnicki, G. Ghibaudo, and F. Boeuf, "Simple and efficient MASTAR threshold voltage and subthreshold slope models for low-doped double-gate MOSFET," *IEEE Trans. Electron Devices*, vol. 59, no. 9, pp. 2534–2538, Sep. 2012, doi: 10.1109/TED.2012.2201942.

- [29] A. Beckers, F. Jazaeri, and C. Enz, "Inflection phenomenon in cryogenic MOSFET behavior," *IEEE Trans. Electron Devices*, vol. 67, no. 3, pp. 1357–1360, Mar. 2020, doi: 10.1109/TED.2020.2965475.

- [30] Y. Han, J. Sun, I. Radu, J. Knoch, D. Grützmacher, and Q.-T. Zhao, "Improved performance of FDSOI FETs at cryogenic temperatures by optimizing ion implantation into silicide," *Solid-State Electron.*, vol. 208, Oct. 2023, Art. no. 108733, doi: 10.1016/j.sse.2023.108733.

- [31] M. Chu, Y. Sun, U. Aghoram, and S. E. Thompson, "Strain: A solution for higher carrier mobility in nanoscale MOSFETs," *Annu. Rev. Mater. Res.*, vol. 39, no. 1, pp. 203–229, Aug. 2009, doi: 10.1146/annurev-matsci-082908-145312.

- [32] H.-C. Han, Z. Zhao, S. Lehmann, E. Charbon, and C. Enz, "Novel approach to FDSOI threshold voltage model validated at cryogenic temperatures," *IEEE Access*, vol. 11, pp. 56951–56957, 2023, doi: 10.1109/ACCESS.2023.3283298.