# Hybrid-Integration of SOA on Silicon Photonics Platform Based on Flip-Chip Bonding

Takeshi Matsumoto , Teruo Kurahashi, Ryotaro Konoike , Keijiro Suzuki , *Member, IEEE, Member, OSA*, Ken Tanizawa , *Member, IEEE*, Ayahito Uetake, Kazumasa Takabayashi, Kazuhiro Ikeda , *Member, IEEE, Senior Member, OSA*, Hitoshi Kawashima, *Member, OSA*, Suguru Akiyama, and Shigeaki Sekiguchi

(Invited Paper)

Abstract—A precise flip-chip bonding (FCB) technology for indium phosphide semiconductor optical amplifiers (InP-SOAs) on a silicon photonics platform within less than  $\pm 1$ - $\mu$ m alignment accuracy was developed. For efficient optical coupling and a relaxed alignment tolerance, the mode field on both the InP-SOAs and the Si waveguides was expanded by spot-size converters (SSCs). On the InP-SOAs, width-tapered SSCs were used to obtain an isotropic mode-field having an approximately a 3- $\mu$ m diameter. On the silicon photonics platform, dual-core SSCs were used to expand the same mode-field size of 3  $\mu$ m as for the SSCs on SOAs. Using the FCB technology and the SSCs, an in-line optical amplification of 15 dB was achieved by in-line integrated SOAs with angled waveguides. The optical coupling losses were 7.7 dB, which included 5.1-dB excess losses by misalignment and a gap between InP-SOA and Si waveguides. A  $4 \times 4$  Si switch with a hybrid-integrated 4-ch SOA array was fabricated, and achieved the first demonstration of a lossless Si switch.

*Index Terms*—Flip-chip devices, integrated optics, optical coupling, optical switches, semiconductor optical amplifiers, silicon photonics.

### I. INTRODUCTION

PTICAL matrix switches are key components for future energy-saving networks because they can omit optical-

Manuscript received June 29, 2018; revised September 5, 2018; accepted September 6, 2018. Date of publication September 13, 2018; date of current version February 20, 2019. This work was partly supported by the Project for Developing Innovation Systems of MEXT, Japan. (Corresponding author: Takeshi Matsumoto.)

- T. Matsumoto, T. Kurahashi, and A. Uetake are with the Fujitsu Laboratories Ltd., Atsugi 243-0197, Japan (e-mail: matsumoto.t@jp.fujitsu.com; kurahashi.teruo@jp.fujitsu.com; uetake.ayahito@jp.fujitsu.com).

- R. Konoike, K. Suzuki, K. Ikeda, and H. Kawashima are with the National Institute of Advanced Industrial Science and Technology, Tsukuba 305-8568, Japan (e-mail: r.konoike@aist.go.jp; k.suzuki@aist.go.jp; kaz.ikeda@aist.go.jp; kawashima-h@aist.go.jp).

- K. Tanizawa is with the Quantum ICT Research Institute, Tamagawa University, Machida 194-8610 Japan, and also with the National Institute of Advanced Industrial Science and Technology, Tsukuba 305-8568, Japan (e-mail: tanizawa@lab.tamagawa.ac.jp).

- K. Takabayashi and S. Akiyama are with the Fujitsu Optical Components Ltd., Nakahara-ku 211-8588, Japan, on leave from the Fujitsu Laboratories Ltd., Kanagawa, Japan (e-mail: takabayashi.kaz@jp.fujitsu.com; akiyama. suguru@jp.fujitsu.com).

- S. Sekiguchi is with the Fujitsu Advanced Technologies Ltd., Saiwai-ku 212-8510, Japan, on leave from the Fujitsu Laboratories Ltd., Kanagawa, Japan (e-mail: s.sekiguchi@jp.fujitsu.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JLT.2018.2870128

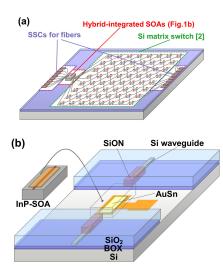

electric conversion at the network nodes [1]-[3]. Until now, several optical switching platforms including free-space, III-V photonic integration and silicon photonic integration have been investigated [4]. In free-space based on microelectromechanical systems (MEMS), large-scale switches with low insertion loss, low crosstalk and polarization-independent operation have been demonstrated. However, the high driving voltage of MEMS switches is prohibitive for low-cost switching systems due to the complexity of drivers. In III-V photonic integration, monolithically-integrated 16 × 16 SOA-based switches have been demonstrated. However, the possible port number is limited by the maximum available InP wafer size. In silicon photonic integration, large-scale and compact switches are expected by utilizing advanced complementary metaloxide-semiconductor (CMOS)-compatible process. Silicon wire waveguides permit small bending radii, on the order of several micrometers, which enable large-scale integration at high density. However, those switches suffer from large cumulative optical losses due to the elements, such as phase shifters, couplers and intersections. Recently, on-chip optical amplification by semiconductor optical amplifiers (SOAs) is expected to be a promising solution to overcome those losses. Until now, various approaches have been investigated, including wafer-bonding [5], [6] and flip-chip bonding (FCB) [7]–[11]. In wafer-bonding technologies, the alignment is lithographically determined on the wafer, which enables high-performance devices with efficient coupling between the SOAs and Si optical platforms. However, there are some difficulties for existing foundries to launch complex technologies, such as the III-V process on a Si wafer. Therefore, FCB technologies are focused on here because discrete InP-SOAs with optimized structures by the standard III–V process can be used. Fig. 1(a) is the schematic structure of a Si matrix switch with a hybrid-integrated InP-SOA. For inline amplification, both input and output waveguides of the SOA are coupled to Si waveguides, as shown in Fig. 1(b). In order to achieve efficient optical coupling and a relaxed alignment tolerance, the mode field on both the InP-SOA and the Si waveguide are expanded by spot-size converters (SSCs). Although in-line integration of InP-SOAs for Si waveguides has been attempted for Si wire [7]–[10] and  $\mu$ m-scale Si waveguides [11], it remains challenging due to the optical losses at both sides of the SOA

Fig. 1. (a) Schematic structure of a Si matrix switch with hybrid-integrated SOAs and (b) configuration of flip-chip bonding for in-line amplification.

caused by misalignment of the SOA chips. A lossless operation of Si switch with flip-chip bonded SOA has not been achieved until recently, but we successfully demonstrated the first lossless operation (In [8], [9], we presented the preliminary results).

In this paper, we reported hybrid-integration of an SOA on a Si optical platform in details. SSCs and hybrid-integration technologies are described for an InP-SOA on a Si optical platform by using precise FCB technologies with less than  $\pm 1$ - $\mu m$  alignment accuracy. Using this, an in-line optical amplification of 15 dB was achieved by a flip-chip bonded SOA with an angled waveguide. A lossless operation was demonstrated for a 4  $\times$  4 Si switch with in-line integrated 4ch-SOA array To the best of our knowledge, our results are the first demonstration of a lossless Si switch with flip-chip bonded SOA.

This paper is comprised of five sections. In Section II, the design and characteristics of SSCs on SOAs and Si optical platforms are shown. In Section III, FCB technologies and estimated excess loss are described. In Section IV, the in-line optical amplification and lossless operation of  $4\times 4$  Si switches by hybrid-integrated SOAs are demonstrated. Finally, the results are summarized in Section V.

#### II. SPOT-SIZE CONVERTERS

In this section, the width-tapered SSCs on SOAs and dual-core SSCs on Si optical platforms for efficient optical coupling and relaxed alignment tolerance are described. At the optical interface between SOAs and Si optical platforms, an isotropic mode field having an approximately 3- $\mu$ m diameter by SSCs was obtained. A dual-core SSC with a wide SiON core as an interface for the optical fibers was also adopted.

# A. Width-Tapered SSCs on the SOAs

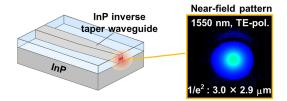

The schematic structures of the SSCs and measured near field pattern (NFP) on a SOA at the wavelength of 1550-nm range are shown in Fig. 2. The SOA had InGaAsP MQWs with semi-insulating InP blocking layer designed for TE polarization [12]. Mode field diameter was defined as a diameter

Fig. 2. Schematic of SSC on a SOA and measured NFP.

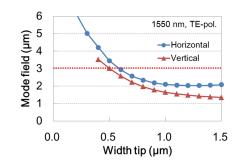

Fig. 3. Calculated mode field diameter of SOA as a function of width tip.

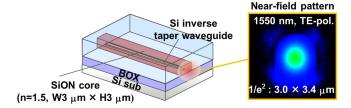

Fig. 4. Schematic of SSC on a Si optical platform and measured NFP.

where the intensity value falls to  $1/e^2$  of the maximum. Fig. 3 shows the calculated mode-field diameter as a function of width tip. The SSC had a 200- $\mu$ m-long tapered waveguide in which the waveguide width was linearly changed from 1.6  $\mu$ m to a submicron wide tip. The tip width of 0.6  $\mu$ m was used to obtain a 3- $\mu$ m mode-field diameter, as shown in Fig. 3.

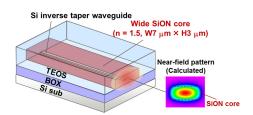

#### B. Dual-Core SSCs on Si Optical Platforms

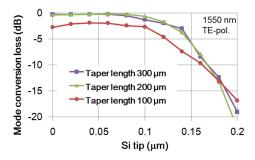

The Si optical platform was fabricated on a 220-nm thick SOI wafer having a 3- $\mu$ m-thick BOX layer. The schematic structures of SSCs and NFP on a Si optical platform at the wavelength of 1550-nm range are shown in Fig. 4. In the SSC region for SOA coupling, the Si tapered waveguide was covered with a lowindex SiON core (n = 1.50). The SiON core had a 3- $\mu$ m-wide and 3- $\mu$ m-high cross section to match the mode-field size of the SSC on the SOA. An efficient optical coupling and relaxed alignment tolerance was expected due to the mode-field matching at a diameter of about 3  $\mu$ m by the SSCs. The Si taper length and tip width are key parameters for adiabatic and efficient mode conversion between the Si tapered waveguide and SiON core. To determine the necessary geometry of the Si taper waveguide, the mode conversion loss at the wavelength of 1550 nm as a function of Si tip width was calculated for three kinds of taper length (see Fig. 5). A tapered waveguide longer than 200  $\mu$ m with a tip width of <100 nm was required. A 300- $\mu$ m-long tapered waveguide with 100-nm width tip was fabricated in an advanced process line equipped with ArF immersion lithography at the National Institute of Advanced Science and Technology

Fig. 5. Calculated mode conversion loss of SSCs on a Si optical platform.

Fig. 6. Schematic of SSC with  $7 \times 3$ - $\mu m$  SiON core on a Si optical platform and calculated NFP.

Fig. 7. Calculated tolerance curve for the optical coupling between SSCs with  $7\times 3$ - $\mu m$  SiON core and DSF.

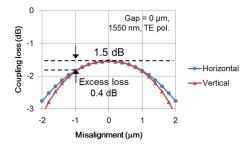

(AIST), Tsukuba, Japan. On the other hand, the Si optical platform has optical fiber coupling for input and output signals. A Si optical switch consists of multi-port input-output connections, so an optical fiber array is desirable. A dispersion shifted fiber (DSF) array with approximately 8- $\mu$ m optical mode was used. A dual-core SSC with a wide SiON core with a 7- $\mu$ m-wide and 3- $\mu$ m-high cross section as an interface to the DSF array was used, as shown in Fig. 6. Fig. 7 shows the simulated tolerance curve for the optical coupling between the dual-core SSCs with a 7 × 3- $\mu$ m SiON core and the DSFs. The optical loss includes 0.3-dB mode conversion loss of SSCs. A low optical loss of 1.5 dB/facet can be seen at the best alignment. Even taking into account 1- $\mu$ m core pitch error on a DSF array, the excess loss can be suppressed within 0.4 dB due to the large optical mode of SSCs and DSFs.

# III. FCB OF AN SOA ON A SILICON OPTICAL PLATFORM

The SOA was flip-chip bonded on the Si trench where the TEOS upper cladding layer, SOI, and BOX layers were removed and AuSn solder was deposited (Sn = 30 wt.%, melting temperature =  $390 \,^{\circ}\text{C}$ ). The FCB process was carried out with passive

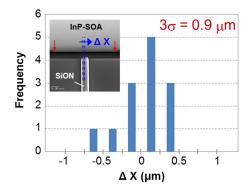

Fig. 8. Distribution of horizontal misalignment for flip-chip bonded SOAs. The inset is a SEM image of waveguides at the coupling site. The waveguide core of SOA is located at center of two red arrows.

Fig. 9. Relationship between AuSn thickness after FCB and load of bonder.

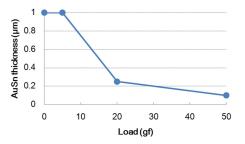

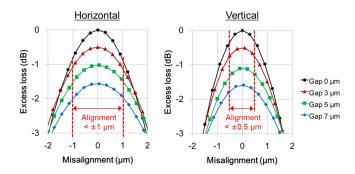

alignment utilizing the marks on both the SOA and the Si optical platform. The distribution of the horizontal misalignment for flip-chip bonded SOAs are shown in Fig. 8. A three-sigma standard deviation (3 $\sigma$ ) of 0.9  $\mu$ m was determined from the SEM observation of 13 test samples. In the vertical direction, the alignment of waveguide heights was adjusted by finely controlling the load of the bonder and the thickness of each layer in the SOA and the Si optical platform. Fig. 9 shows the relationship between the AuSn thickness after FCB and the load of the bonder. In the low load area (<20 gf), the AuSn maintained the as-deposited thickness. When the load was more than 20 gf, the AuSn thickness decreased by approximately 80%. The load between 20 and 50 gf was preferable for a stable AuSn thickness after FCB because it enabled stable alignment of the waveguide heights. The misalignment of waveguides heights was confirmed to be within a range of  $\pm 0.5 \mu m$  by observing cross sections for a few bonded samples. In the gap direction between the SOA and the trench wall of the Si optical platform, the errors were not only due to the FCB misalignment, but also due to the SOA edge position deviation by cleaving. The typical gap was set to 5  $\mu$ m, which was enough to avoid the hit between the SOA and the trench wall. The gap between 3 and 7  $\mu$ m was due to the SOA edge position deviation of  $\pm 2$  $\mu$ m by cleaving. To reduce this large gap for efficient optical coupling, not only improving the cleaving accuracy but also adopting other methods such as using etched-facet SOAs [13] is a promising candidate. Fig. 10 shows the measured tolerance curve for the optical coupling between the SSCs on the SOA and the Si optical platform. The SOA was translated in the horizontal, vertical, and gap directions relative to the Si optical

Fig. 10. Measured tolerance curve for the optical coupling between SSCs on an InP-SOA and a Si optical platform.

platform while measuring the optical coupling. ASE from the SOA was used as a light source. For a 5  $\pm$  2- $\mu m$  gap, an excess loss of <1.6 dB/facet was expected at the best alignment. For our horizontal alignment accuracy of  $\pm 1~\mu m$ , the additional loss was 0.4 dB/facet. For our vertical alignment accuracy of  $\pm 0.5~\mu m$ , an additional 0.2-dB/facet loss can be seen. Therefore, a total excess loss of <2.2 dB/facet was estimated. In the case of in-line integration, the total excess loss was <4.4 dB on both sides.

Die shear testing was also performed on a single chip to evaluate the bond strength of the solder joint before and after thermal cycle tests. The bonding area and die size were 46400  $\mu m^2$  and  $300\times800~\mu m$ , respectively. The temperature changed from -40 to +125 °C for 500 cycles in a nitrogen atmosphere. The rate of temperature change was 6 °C/min. A shear force before and after the thermal cycle test was 360 and 340 gf, which indicates strong bonds with high reliability.

#### IV. IN-LINE AMPLIFICATION

In this section, the FCB technology for InP-SOA was applied to in-line amplification for the Si optical platform. The SOA had InGaAsP MQWs with semi-insulating InP blocking layer designed for TE polarization [12]. A 3- $\mu$ m mode-field diameter at the wavelength of 1550-nm range was obtained at the interface facet using a 200- $\mu$ m-long SSC in which the waveguide width was linearly changed from 1.6 to 0.6  $\mu$ m. First, InP-SOAs with straight waveguides were used for a 1  $\times$  8 Si optical splitter with InP-SOA to demonstrate the in-line amplification. The waveguide was tilted to improve the in-line amplification. The tilted InP-SOA waveguide reduced the back reflection between the SOA and the Si optical platform that limited the amplification. The in-line amplification by the SOA and a 4  $\times$  4 Si switch with a 4ch-SOA array was evaluated to demonstrate the lossless operation of the switch.

#### A. In-Line Amplification by an SOA With Straight Waveguide

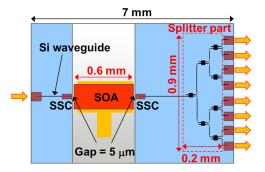

A 1  $\times$  8 Si optical splitter with hybrid-integrated InP-SOA was fabricated to demonstrate the loss-compensated operation of the Si optical platform. Fig. 11 shows schematic view of a 1  $\times$  8 Si optical splitter with the SOA. The 600- $\mu$ m-long SOA with straight waveguide was flip-chip bonded on the 1  $\times$  8 split-

Fig. 11. Layout of  $1 \times 8$  Si optical splitter with hybrid-integrated InP-SOA.

Fig. 12. Transmission spectrum of  $1\times 8$  splitter. Inset shows measured ASE spectrum around 1531 nm.

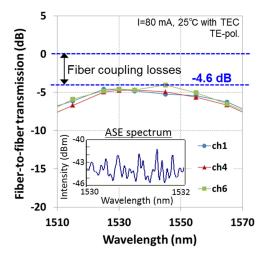

ter. The SOA facets were coated with anti-reflection (AR) films for air. The trench wall of Si optical platform was uncoated. Fresnel reflection was estimated to be approximately 3%, which led to 0.28-dB Fresnel losses at both sides. The footprint of the  $1 \times 8$ splitter part was as small as  $0.2 \text{ mm} \times 0.9 \text{ mm}$  due to the Si wire waveguides. A multimode interference (MMI) coupler was used as the 3-dB splitters and dual-core SSCs with a  $3 \times 3 \mu m$  SiON core as the interface of the SOA and the fiber. Fig. 12 shows the fiber-to-fiber transmission spectrum of the 1 × 8 splitter with InP-SOA operated by an 80 mA current at 25 °C with a thermoelectric cooler (TEC). The difference in the transmission spectrum among the eight output channels was small, which means the fabrication was uniform. The fiber-tofiber transmission was -4.6 dB at the peak wavelength. This transmission included 4.6-dB coupling losses to the two lensed fibers, a 9-dB loss for three-stage splitters, a 1-dB propagation loss for Si waveguides, and a gain of InP-SOA. This result means that a 10-dB net gain was achieved by the in-line InP-SOA, which compensated for the on-chip loss of 10 dB by the Si splitter. However, the SOA chip gain was limited to 16 dB due to the back reflection. From the inset in Fig. 12, we can see a gain ripple of <4 dB, which was worse than a reported value by other group [10]. Our structure for reduced back reflection was described in the next section.

Fig. 13. Schematic view of test chip used for evaluation of in-line amplification.

Fig. 14. Transmission spectrum of the test chip. Inset shows measured ASE spectrum around 1521 nm.

# B. Improvement of In-Line Amplification by an SOA With Angled Waveguide

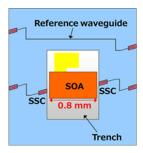

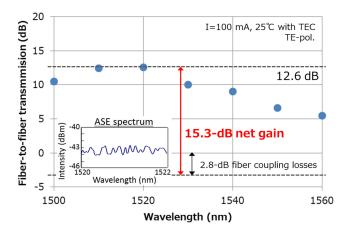

Fig. 13 shows a schematic view of the test chip used for evaluation of the in-line amplification by the in-line integrated SOA. The SOA waveguide was inclined seven degrees to avoid the back reflection that would lead to gain ripples. The SOA length was 800  $\mu$ m and the facets were coated with AR films for an UV epoxy resin. The gaps between the SOA and the Si optical platform were filled with the resin. Dual-core SSCs with 3  $\times$  3- $\mu$ m SiON core were used as the interface of the SOA and the fiber. A reference waveguide for coupling losses to lensed fibers on the same chip was fabricated. Fig. 14 shows the transmission spectrum of this sample operated by a 100-mA current at 25 °C with TEC. The fiber-to-fiber transmission was 12.6 dB at the peak wavelength, which means that a 15.3-dB net gain was achieved since this transmission included 2.8-dB fiber coupling losses. The details of the coupling excess losses between the SOA and the Si test chip are shown in Table I. At the input interface of the SOA, excess losses for the gap, the horizontal and vertical misalignments were 1.2, 0.2, and 0.9 dB/facet, respectively. This means the total excess losses were 2.3 dB/facet. At the output interface of the SOA, excess losses for the gap, the horizontal and vertical misalignments were 1.5, 0.6, and 0.7 dB/facet. This means the total excess losses were 2.8 dB/facet. Therefore, the total excess losses at the both input and output interface were 5.1 dB. The ideal

$\label{eq:table_interpolation} TABLE\ I$  Details of Excess Losses Between SOA and Test Chip

|        |                            | Measured value | Excess loss | Total excess loss |

|--------|----------------------------|----------------|-------------|-------------------|

| Input  | Gap                        | 5.6 μm         | 1.2 dB      | 2.3 dB            |

|        | Horizontal<br>misalignment | 0.6 μm         | 0.2 dB      |                   |

|        | Vertical<br>misalignment   | 1.0 μm         | 0.9 dB      |                   |

| Output | Gap                        | 6.5 μm         | 1.5 dB      | 2.8 dB            |

|        | Horizontal<br>misalignment | 1.2 μm         | 0.6 dB      |                   |

|        | Vertical<br>misalignment   | 1.0 μm         | 0.7 dB      |                   |

Fig. 15. Microscope image of fabricated 4  $\times$  4 Si switch with hybrid-integrated InP-SOA and close-up of 2  $\times$  2 element switch.

coupling losses without the excess losses were estimated to be 2.6 dB by subtracting the 15.3-dB net gain and 5.1-dB excess losses from the 23-dB SOA chip gain. In this work, the depth of the trench was deeper than ideal due to a design error, resulting in large excess losses in the vertical direction. The excess losses can be reduced in the vertical direction from 0.9 to 0.2 dB at the input interface and from 0.7 to 0.2 dB at the output interface if the vertical misalignment is decreased to within 0.5  $\mu$ m. As for the gain ripple, we can see a gain ripple of <1.6 dB from the inset in Fig. 14, which was reduced from <4 dB in the case of the SOA with straight waveguide. This reduced gain ripple enabled the maximum SOA chip gain of 23 dB.

# C. Lossless Operation of a Si Switch With a 4ch-SOA Array

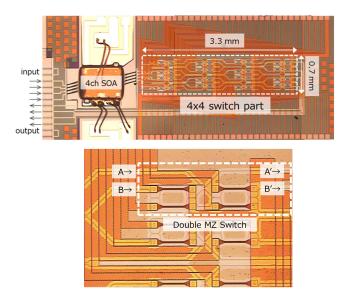

A 4  $\times$  4 Si optical switch with hybrid-integrated InP-SOA was fabricated, as shown in Fig. 15. In this switch, the integrated SOA must be multi-channel to compensate for losses on all paths. A 4ch-SOA array with a narrow channel pitch of 62.5  $\mu$ m and separate electrodes was used for each channel. The 4  $\times$  4 switch consisted of thermo-optic 2  $\times$  2 double-Mach-Zehnder switches with TiN heaters [2], [14]. The footprint of the 4  $\times$  4 switch part was 3.3 mm  $\times$  0.7 mm. Dual-core SSCs with a

Fig. 16. Transmission spectrum of 4  $\times$  4 Si switch with InP-SOA. Inset shows measured ASE spectrum around 1531 nm.

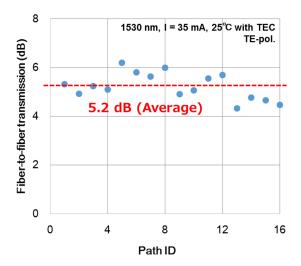

Fig. 17. Transmission of all 16 paths at wavelength of 1530 nm.

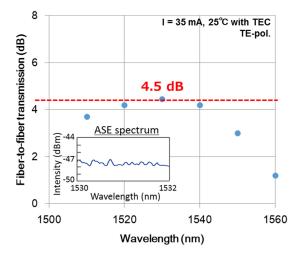

$3 \times 3 - \mu m$  and a  $7 \times 3 - \mu m$  SiON core were used as the interface of the SOA and the fiber, respectively. Fig. 16 shows the fiber-to-fiber transmission of the 4 × 4 switch with the InP-SOA operated by a 35-mA current at 25 °C with TEC. The coupling loss between the SSCs and DSFs was measured to be 1.6 dB/facet, which indicates efficient optical coupling due to the SSC with the  $7 \times 3$ - $\mu$ m SiON core. The fiber-to-fiber transmission was 4.5 dB at the gain peak wavelength. This transmission included 3.2-dB coupling losses to the two fibers, a 1-dB loss for the  $4 \times 4$  switch, a 0.8-dB propagation loss and the gain of the InP-SOA. This result means that a 9.5-dB net gain was achieved by the in-line InP-SOA and a 4.5-dB insertion gain of the  $4 \times 4$  switch. From the inset in Fig. 16, we can see a small gain ripple of <1 dB. The fiber-to-fiber transmission of all 16 paths at a wavelength of 1.53  $\mu m$  is shown in Fig. 17. The horizontal axis is the path ID and specifies the input-output connections. The difference of transmission for each of the switching states was small, which means there was a good uniformity for the Si switch and uniform optical coupling between the Si photonics platform and the SOA. To the best of our knowledge, this is the first demonstration of a lossless operation of Si switch with an

in-line integrated SOA. More detailed switching characteristics and lossless transmission of 8-channel, 32-Gbaud 16-QAM WDM signals through the  $4 \times 4$  Si switch with hybrid-integrated SOA were reported in [9].

#### V. CONCLUSION

Large-scale and compact Si optical matrix switches are key components for optical pass networks, but they suffer from cumulative optical losses. On-chip optical amplification by SOAs is expected to be a promising solution to overcome those losses. A precise FCB technology of an InP-SOA on a Si optical platform within  $\pm 1~\mu m$  alignment accuracy was developed in this work and achieved in-line optical amplification of 15 dB by inline integrated SOA with angled waveguides. A 4  $\times$  4 Si optical switch was fabricated with a hybrid-integrated 4ch-SOA array and demonstrated the lossless operation of the switch. This is the first demonstration of fully loss-compensated Si switch with inline integrated SOA. This technology enhances the ability of Si optical platform and will enable large-scale Si optical platform with an optical leveling function.

#### ACKNOWLEDGEMENT

The device fabrication was supported by TIA SCR of AIST.

#### REFERENCES

- S. Namiki et al., "Ultrahigh-definition video transmission and extremely green optical networks for future," *IEEE J. Sel. Topics Quantum Electron.*, vol. 17, no. 2, pp. 446–457, Apr. 2011.

- [2] K. Suzuki et al., "Broadband silicon photonics 8 × 8 switch based on double-Mach–Zehnder element switches," Opt. Express, vol. 25, no. 7, pp. 7538–7546, Apr. 2017.

- [3] K. Suzuki et al., "Low insertion loss and power efficient 32 × 32 silicon photonics switch with extremely-high-Δ PLC connector," in Proc. Int. Conf. Opt. Fiber Commun., San Diego, CA, USA, 2018, Paper Th4B.5.

- [4] Q. Cheng, S. Rumley, M. Bahadori, and K. Bergman, "Photonic switching in high performance datacenters," *Opt. Express*, vol. 26, no. 12, pp. 16022– 16043. Jun. 2018.

- [5] D. Carrara et al., "Hybrid III-V/silicon photonic integrated circuits for high bitrates telecommunication applications," Proc. SPIE, Integr. Opt. Devices Mater. Technol. XXI, vol. 10106, 2017, Art. no. 101060G.

- [6] A. D. Groote et al., "Transfer-printing-based integration of single-mode waveguide-coupled III-V-on-silicon broadband light emitters," Opt. Express, vol. 24, no. 13, pp. 13754–13762, 2016.

- [7] T. Matsumoto *et al.*, "In-line optical amplification for Si waveguides on 1 × 8 splitter and selector by flip-chip bonded InP-SOAs," in *Proc. Int. Conf. Opt. Fiber Commun.*, Anaheim, CA, USA, 2016, Paper Th1C.1.

- [8] T. Matsumoto et al., "In-line optical amplification for silicon photonics platform by flip-chip bonded InP-SOAs," in Proc. Int. Conf. Opt. Fiber Commun., San Diego, CA, USA, 2018, Paper Tu2A.4.

- [9] R. Konoike et al., "Lossless operation of SOA-integrated silicon photonics switch for 8 × 32-Gbaud 16-QAM WDM signals," in Proc. Int. Conf. Opt. Fiber Commun., San Diego, CA, USA, 2018, Paper Th4B.6.

- [10] F. E. Doany et al., "A four-channel silicon photonic carrier with flipchip integrated semiconductor optical amplifier (SOA) array providing >10-dB gain," in Proc. 66th Int. Conf. Electron. Compon. Technol, 2016, pp. 1061–1068.

- [11] D. Fitsios et al., "Dual SOA-MZI wavelength converters based on III-V hybrid integration on a μm-scale Si platform," IEEE Photon. Technol. Lett., vol. 26, no. 6, pp. 560–563, Mar. 2014.

- [12] K. Morito, S. Tanaka, S. Tomabechi, and A. Kuramata, "A broad-band MQW semiconductor optical amplifier with high saturation output power and low noise figure," *IEEE Photon. Technol. Lett.*, vol. 17, no. 5, pp. 974– 976, May 2005.

- [13] L. Schares et al., "Etched-facet semiconductor optical amplifiers for gainintegrated photonic switch fabrics," in Proc. Eur. Conf. Opt. Commun., Valencia, Spain, 2015, Paper Mo.3.2.1.

[14] T. Goh, A. Himeno, M. Okuno, H. Takahashi, and K. Hattori, "High-extinction ratio and low-loss silica-based 8 × 8 strictly nonblocking ther-mooptic matrix switch," *J. Lightw. Technol.*, vol. 17, no. 7, pp. 1192–1199, Jul. 1999.

**Takeshi Matsumoto** received the B.S. and M.S. degrees in physics from the Osaka University, Osaka, Japan, in 2004 and 2006, respectively.

In 2006, he joined the Fujitsu Laboratories Ltd., Kanagawa, Japan, where he has been working in research and development of semiconductor optical devices. His current research interests include hybrid-integration of semiconductor optical amplifiers on Si optical platforms and spot-size converters.

Mr. Matsumoto is a member of the Japan Society of Applied Physics.

**Teruo Kurahashi** joined the Fujitsu Laboratories Ltd., Kanagawa, Japan, in 1986. He has engaged in the development of lithium niobate modulators, dynamic random access memory, and complementary metal-oxide-semiconductor. He currently works on process engineering for silicon photonics devices.

**Ryotaro Konoike** received the M.S. and Ph.D. degrees from the Department of Electronic Science and Engineering, Kyoto University, Kyoto, Japan, in 2014 and 2017, respectively. At Kyoto University, he researched on the integration of manipulation of photons on a photonic crystal chip containing multiple coupled nanocavities.

He is currently working as a Researcher with the National Institute of Advanced Industrial Science and Technology, Tsukuba, Japan. His research interests include optical switches and integrated silicon optical circuits.

Keijiro Suzuki received the B.E. and M.E. degrees from the Department of Electrical and Electronic Engineering, Shizuoka University, Hamamatsu, Japan, in 2004 and 2006, respectively. He received the Ph.D. degree from the Yokohama National University (YNU), Yokohama, Japan, in 2011. After spending two years at Sumitomo Osaka Cement Co., Ltd., he entered the Department of Electrical and Computer Engineering, YNU, in 2008, and received the Research Fellowship for Young Scientists from JSPS. After spending one year at YNU as a Postdoctoral Fellow, he joined the National Institute of Advanced Industrial Science and Technology, Tsukuba, Japan, in 2012. His research interests include photonic integrated circuits, nanophotonics, and nonlinear optics.

Dr. Suzuki is a member of the OSA, the IEEE Photonics Society, the IEICE, and the JSAP.

**Ken Tanizawa** received the B.E., M.E., and Ph.D. degrees in electronic engineering from the University of Tokyo, Tokyo, Japan, in 2004, 2006, and 2009, respectively.

From 2009 to 2017, he was with the National Institute of Advanced Industrial Science and Technology, Tsukuba, Japan, where he was involved in research on silicon photonics devices and optical signal processing for energy-efficient optical networks. In 2017, he joined the Tamagawa University, Tokyo, Japan, as an Associate Professor. His current research interests include subsystems and optical devices for high-speed and secure fiber-optic transmission.

Dr. Tanizawa is a member of the Institute of Electronics, Information, and Communication Engineers of Japan.

**Ayahito Uetake** received the B.E. and M.E. degrees in applied physics from the Tohoku University, Sendai, Japan, in 2002 and 2004, respectively. In 2004, he joined the Fujitsu Laboratories, Ltd., Atsugi, Japan, and has been engaged in the development of III-V based photonic devices, directly modulated lasers, wavelength tunable lasers, semiconductor optical amplifiers (SOA), optical coupler integrated SOA gate array switches, quantum dots SOAs, and 90° hybrid and integrated optical receivers. Recently, he has developed silicon photonics devices, integration of Si-based optical devices, and III-V and Si hybrid devices.

Kazumasa Takabayashi received the B.E. and M.E. degrees in applied physics from the Tohoku University, Sendai, Japan, in 1998 and 2000, respectively. In 2000, he joined the Fujitsu Laboratories, Ltd., Atsugi, Japan, where he has been working in the research of optical semiconductor devices for optical communication systems. In 2017, he joined the Fujitsu Optical Components Ltd., Nakahara-ku, Japan. He is currently engaged in the development of optical components for optical communication systems.

Mr. Takabayashi is a member of the IEICE.

**Kazuhiro Ikeda** received the B.E. and M.E. degrees in precision science from the Osaka University, Suita, Japan, in 1998 and 2000, respectively, and the Ph.D. degree in electrical engineering (photonics) from the University of California, San Diego, CA, USA, in 2008. In his doctoral thesis, he studied nonlinear optical responses in silicon nitride and amorphous silicon, and developed sidewall corrugated waveguide devices, all for silicon photonics applications.

From 2000 to 2004, he worked for the Furukawa Electric Co., Ltd., on polarization controllers and polarization mode dispersion compensators for optical fiber communications. In 2009, he joined the Graduate School of Materials Science, Nara Institute of Science and Technology, Ikoma, Japan, as an Assistant Professor, where he studied opto-spintronics and plasmonic microresonators for semiconductor lasers. He is currently working as a Research Group Leader with the National Institute of Advanced Industrial Science and Technology, Tsukuba, Japan. His research interests include silicon photonic integrated circuits and hybrid nanophotonics on silicon.

Dr. Ikeda is a senior member of the OSA, and a member of the IEICE, JSAP, and IEEE Photonics Society.

Hitoshi Kawashima received the Ph.D. degree in chemistry from Kyoto University, Kyoto, Japan, in 1993. He was a Postdoctoral Fellow with MIT from 1993 to 1995, where he worked on pulse-shaping technology for femtosecond optical pulses. In 1995, he joined the Electrotechnical Laboratory. In 2001, the Electrotechnical Laboratory and other 14 national research laboratories were reorganized as the National Institute of Advanced Industrial Science and Technology, Tsukuba, Japan. Since 2008, he has been working on silicon photonics and its applications to a circuit switch. His research interests include integrated optics, nonlinear optics, and diagnostic techniques with ultrashort optical pulses.

Dr. Kawashima is a member of OSA, IEICE, and Japan Society of Applied Physics.

**Suguru Akiyama** received the B.S. degree from the Tokyo Institute of Technology, Tokyo, Japan, in 1995, the M.E. degree from the University of Tokyo, in 1997, and the Ph.D. degree from the University of Tsukuba, Japan, in 2013. In 1997, he joined the Fujitsu Laboratories Ltd., Atsugi, Japan, where he has been working in semiconductor optoelectronic devices for optical fiber communications. He is currently working with the Fujitsu Optical Components Ltd., Nakahara-ku, Japan.

Dr. Akiyama is a member of the Institute of Electronics, Information, and Communication Engineers of Japan.

Shigeaki Sekiguchi received the B.E., M.E., and Ph.D. degrees from the Tokyo Institute of Technology, Tokyo, Japan, in 1996, 1998, and 2000, respectively. In 2001, he joined the Fujitsu Laboratories, Ltd., Atsugi, Japan, where he has engaged in research and development of semiconductor optical devices. Since 2009, he has been working in research and development of silicon photonics technologies including switching devices and transceivers.

Dr. Sekiguchi is a member of the Institute of the Japan Society of Applied Physics.