# Computational Complexity Optimization of Neural Network-Based Equalizers in Digital Signal Processing: A Comprehensive Approach

Pedro Freire, Sasipim Srivallapanondh, Bernhard Spinnler, Antonio Napoli, Nelson Costa, Jaroslaw E. Prilepsky, and Sergei K. Turitsyn

(Invited Paper)

Abstract—Experimental results based on offline processing reported at optical conferences increasingly rely on neural networkbased equalizers for accurate data recovery. However, achieving low-complexity implementations that are efficient for real-time digital signal processing remains a challenge. This paper addresses this critical need by proposing a systematic approach to designing and evaluating low-complexity neural network equalizers. Our approach focuses on three key phases: training, inference, and hardware synthesis. We provide a comprehensive review of existing methods for reducing complexity in each phase, enabling informed choices during design. For the training and inference phases, we introduce a novel methodology for quantifying complexity. This includes new metrics that bridge software-to-hardware considerations, revealing the relationship between complexity and specific neural network architectures and hyperparameters. We guide the calculation of these metrics for both feed-forward and recurrent layers, highlighting the appropriate choice depending on the application's focus (software or hardware). Finally, to demonstrate the practical benefits of our approach, we showcase how the computational complexity of neural network equalizers can be significantly reduced and measured for both teacher (biLSTM+CNN) and student (1D-CNN) architectures in different scenarios. This work aims to standardize the estimation and optimization of computational complexity for neural networks applied to real-time digital signal processing, paving the way for more efficient and deployable optical communication systems.

Index Terms—Neural networks, nonlinear equalizer, computational complexity, hardware estimation, signal processing.

Manuscript received 29 December 2023; revised 11 March 2024; accepted 5 April 2024. Date of publication 10 April 2024; date of current version 27 June 2024. The work of Bernhard Spinnler, Antonio Napoli, and Nelson Costa was supported by the European Union' Horizon Europe Research and Innovation Programme, under Grant 101092766 (ALLEGRO). The work of Jaroslaw E. Prilepsky was supported by Leverhulme Trust, under Grant RP-2018-063. The work of Sergei K. Turitsyn was supported by the EPSRC Project TRANSNET. This work was supported by the EU Horizon 2020 Program under the Marie Sklodowska-Curie Grant Agreement 813144 (REAL-NET) and Grant 956713 (MENTOR). (Corresponding author: Pedro Friere.)

Pedro Freire, Sasipim Srivallapanondh, Jaroslaw E. Prilepsky, and Sergei K. Turitsyn are with the Aston Institute of Photonic Technologies, Aston University, B4 7ET Birmingham, U.K. (e-mail: p.freiredecarvalhosourza@aston.ac.uk).

Bernhard Spinnler and Antonio Napoli are with Infinera R&D, 81541 Munich, Germany (e-mail: anapoli@infinera.com).

Nelson Costa is with Infinera Unipessoal, 2790-078 Carnaxide, Portugal (e-mail: ncosta@infinera.com).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JLT.2024.3386886.

Digital Object Identifier 10.1109/JLT.2024.3386886

#### I. INTRODUCTION

VER the last few decades, neural networks (NNs) have begun to find widespread usage in a wide range of signal processing applications: filtering, parameter estimation, signal detection, system identification, pattern recognition, signal reconstruction, time series analysis, signal compression, signal transmission, etc. [1], [2], [3], [4]. Audio, video, image, communication, geophysical, and radar scanning data, are examples of important signal types that typically undergo various forms of signal processing [5], [6], [7]. The key capabilities of NNs in signal processing are: performing distributed processing, emulating nonlinear transformations and processes, self-organizing, and enabling high-speed processing communication applications [8], [9], [10]. With these properties, NNs can provide a very powerful means of solving many signal processing tasks, particularly in the areas related to nonlinear signal processing, real-time signal processing, adaptive signal processing, and blind signal processing [5], [11], [12], [13].

NN methods have also proven to be efficient in several applications in optical communications, particularly in channel equalization [14]. NN structures have demonstrated the potential to significantly enhance transmission quality in various scenarios [15], with computational complexity comparable or better than that of classical approaches [16], [17]. However, additional work is still required to reach product-level applications. One of the most pressing challenges is to demonstrate how such NN-based equalizers can be effectively implemented, taking into account both the training and inference phases. In order to evaluate the computational complexity, the metrics for an assessment should be appropriately addressed.

Real-time signal processing, as an example, is a field that enables technological breakthroughs by effectively incorporating signal processing in hardware: real-time and onboard signal processing are the keys to the evolution of phones and watches into smartphones/smartwatches. To the best of our knowledge, one of the first real-time applications of NNs was discussed in 1989 [18], and numerous works since then have deliberated the challenges of implementing such solutions in hardware exploiting the notion of computational complexity [19], [20], [21], [22], [23], [24], [25], [26], [27], [28]. Similarly, in the NN-based equalizer, computational complexity analysis is necessary.

From a computer science perspective, computational complexity analysis is almost always attributed to the Big-O notation of the algorithm [29], [30], [31]. In general, the Big-O notation is used to express an algorithm's complexity while assessing its efficiency, which means that we are interested in how effectively the algorithm scales with the size of the dataset in terms of running time [32], [33], [34]. However, from the engineering standpoint, the Big-O is often an oversimplified measure that cannot be immediately translated into the hardware resources required to realize the algorithm (NNs) in a hardware platform [20].

Due to this problem that refers to the absence of some "universal" measure, various works started to present complexity in terms of multiply and accumulate (MAC) [19], [20], [21], [22], Kolmogorov complexity [23], the number of bit-operations (BOP) [24], [25], the number of real multiplications (RM) [26], [27], [28]. However, it is not always clear when to use each specific metric, and, more importantly, none of the metrics mentioned above show the benefits of using different strategies of quantization to reduce the complexity of implementing the multipliers.

As far as we know, no work has so far unified the computational metrics itemized above such that we have no universal metrics to compare the complexity when different types of quantization are applied to NN structures. In this paper, we solve this issue by carrying out a systematic computational complexity analysis for a zoo of NN layer types. In addition, we introduce a new useful metric: we coined 'the number of additions and bit shifts' (NABS). This metric takes into account the impact of the weights' quantization type on the reduction of the multipliers' implementation complexity used in an NN layer. Overall, we intend our work to give largely universal measures of complexity to establish a comparison baseline depending on whether the application is software- or hardware-based.

The paper is organized as follows. Firstly, Section II provides an overview of the main strategies enabling low computational complexity NN-based equalizers from training to hardware synthesis, while still maintaining attractive Q-factor gains. In Section III we describe the details of different computational metrics for the training and inference stages. Section IV outlines a method for computing the computational complexity of diverse neural network layers based on their hyperparameters, traversing from the software to the hardware level. The computational complexity growth against the design parameters of each neural network layer is discussed in Section V. Additionally, in Section VI, we explore the impact of quantization on different computational complexity metrics and present a practical study in the realm of channel equalization. This study exemplifies complexity reduction approaches and elucidates the performance and complexity trade-offs associated with compensating nonlinearities in optical coherent transmissions. Our findings are summarized in the conclusion.

## II. OVERVIEW ON COMPLEXITY REDUCTION IN NEURAL NETWORK EQUALIZERS

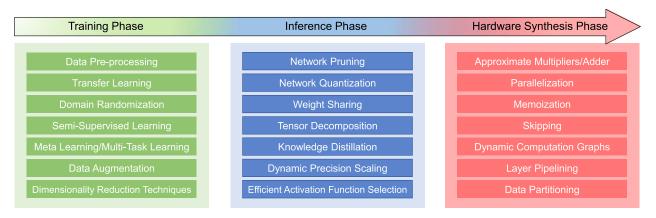

To achieve optimal computational complexity in the pursuit of efficient NN equalizers for resource-constrained hardware, it is necessary to thoroughly investigate three crucial phases: training, inference, and hardware synthesis phases. Fig. 1 illustrates the most common techniques applied to reduce the complexity of NN-based equalizers in each of these phases.

## A. Complexity Reduction in Training

First, during training, reducing complexity is crucial for the efficient and practical deployment of hardware with limited resources. Various complexity reduction techniques are employed to enhance efficiency and performance. Techniques such as transfer learning or approaches to improve generalization, such as data augmentation, domain randomization, and semi-supervised learning, can be applied. These approaches indirectly reduce the need for large amounts of original training data. Effective generalization reduces the need for complex models with a high number of parameters, resulting in faster and more efficient training.

**Data pre-processing** is a crucial step in preparing the input for the NN training. This can be a main factor in enhancing the model efficiency and accelerating convergence because high-quality input data contributes to stable training, improves generalizability, and leads to successful data interpretation by the model [35]. Data pre-processing involves data normalization to have the features on a consistent scale, or feature engineering, which selects and transforms the input features to emphasize the relevant information and get rid of the noisy, irrelevant data.

Transfer learning (TL) adapts the knowledge acquired in the source tasks to the related target tasks. This technique can considerably reduce the training time and resources required. TL is particularly useful when training the models on limited computational resources, as it allows the NN to inherit knowledge from a larger pre-trained model and fine-tune it for a specific task. TL was investigated in equalization tasks in both directly [36] and coherently [37] detected systems. Ref. [37] demonstrated the potential of TL to reduce the number of training epochs and the training dataset without impacting the equalizer's performance.

**Domain randomization** is a systematic approach for data generation aiming to improve the generalization and the robustness of machine learning models in new environments [38]. Domain randomization generates training data from a random distribution with given desired properties and stores it in a library accessible by NN. By using synthetic data, this approach reduces the dependence on real-world data, thus improving the training efficiency [39]. This technique is especially valuable when dealing with complex and dynamic environments as the model becomes more adaptable to variations encountered during deployment.

Semi-supervised learning combines labeled and unlabeled data in training, allowing the model to learn from both. Semi-supervised learning enables NN to leverage the available labeled data more effectively by incorporating information from the unlabeled samples. This method enhances the model's performance without requiring additional labeled data, which makes the model more flexible to transmission changes. This method resembles decision-directed adaptive equalization [40] for channel equalization.

Fig. 1. Main strategies to design low complex NN-equalizers in training, inference, and hardware synthesis phases.

Meta learning involves training models that can efficiently adapt to new tasks with only a small amount of training data based on experiences gained from a variety of learning tasks [41]. This approach explicitly trains the model parameters to enable efficient generalization on new tasks with a small number of gradient steps and minimal training data, making it simple to fine-tune.

Multi-Task Learning is a paradigm where a single model is trained to perform multiple but related tasks simultaneously. In contrast, traditional single-task learning trains multiple separate models for each task independently. Multi-task learning leverages shared representations across tasks and the model's parameters are optimized jointly across all tasks. This training approach can lead to better generalization of the model and reduce the need to deploy several models for different tasks and does not require re-training when performing related tasks. This technique not only reduces the number of models that need to be trained but also reduces the complexity in the inference phase. However, this technique can exhibit a trade-off between overall performance and specific task performance. This approach has been shown to be efficient in the NN-based equalizers in both IM/DD [42] and coherent systems [43].

**Data augmentation** allows datasets to be more diverse and representative by artificially generating additional data points from existing data [44]. Data augmentation used in optical NN-based equalizers is a technique to improve equalization performance and decrease the training complexity of supervised learning in nonlinearity mitigation. In supervised learning tasks, normally a large training dataset is required. The model will also need to be re-trained when the channel conditions change. However, Big Data collection can be challenging. The efficient use of a limited dataset is more desirable for practical implementation. Ref. [45] showed that data augmentation reduces the size of the dataset up to 6 times while maintaining the optical performance. This technique enables a less overfitting model, fewer model parameter requirements, and a faster convergence of the training.

**Dimensionality reduction techniques** address the challenges associated with high-dimensional input spaces. These techniques aim to capture and retain the most informative aspects

of the data while reducing the number of input features significantly [46]. Principal Component Analysis (PCA) [47], for instance, transforms the original features into a lower-dimensional space defined by principal components (a new set of uncorrelated variables), retaining the maximum variance.

## B. Complexity Reduction in Inference

Next, during inference, the NN must accurately equalize the input signal using the minimum computational resources while meeting the required performance metrics. As in the real world, the environments and the resources are more constrained. This result can be achieved by using different techniques, for example, network pruning, sparse representation, knowledge distillation (KD), and tensor decomposition.

Network pruning reduces the complexity of NNs by removing redundant or less significant parameters (weights, connections, neurons, or layers) from a trained NN. Pruning can be carried out without significantly affecting equalization performance, as described in [15], [48], [49]. By eliminating unnecessary parameters, this approach reduces the model's size and computational requirements during inference. Sparse connectivity, achieved through pruning, enables faster execution of the NN on hardware. In most cases, pruning in optical channel equalization has been restricted to the feedforward NN, however, Ref. [15] extended the investigation to the case of recurrent equalizer in coherent optical transmission.

**Network quantization** reduces the precision of the weights and activation functions in NN, for instance, 32-bit floating-point values are converted to 8-bit integers. However, the trade-off between complexity and performance should also be carefully considered, because there might be a performance sacrifice when precision is drastically reduced. This approach has the potential to reduce complexity and memory usage, aiming to make the model more efficient for deployment on resource-constrained device [15], [50].

Weight Sharing compresses the NN weights and biases by keeping only a small number of non-zero coefficients. The redundant or similar values of weights in the NN are collapsed into a single shared weight [15]. The reduction in the number

of unique values of weights decreases the number of parameters that need to be computed and stored, leading to a more compact and memory-efficient model.

**Tensor decomposition** decomposes high-dimensional data into a lower-dimensional space [51]. In other words, a multidimensional tensor is broken down into a combination of simpler tensors. By decomposing tensors, especially weight tensors in NN, into smaller and more manageable components, tensor decomposition reduces the number of parameters and computations needed in the inference phase. In [52], the authors showed that the sparse decomposition of the tensor in convolutional filters can successfully reduce model complexity and memory usage during inference.

Knowledge Distillation (KD) is applied to transfer knowledge from a larger model (teacher) to a more compact one (student) using teacher predictions to assist student learning. KD can reduce the size of the model [53]. The distilled model retains the essential information from the teacher model, making it suitable for deployment in resource-constrained environments during the inference process. Ref. [54] proved to use KD to accelerate the inference of the NN equalizer by recasting the RNN-based equalizer into a feed-forward-based equalizer without significantly compromising the equalization performance.

**Dynamic precision scaling (DPS)** adjusts the precision of the numerical values of the weights and during computation dynamically, based on the specific requirements of each computation. With this approach, the NN can utilize lower precision when the accuracy demands allow, as DPS optimizes the utilization of available resources. This approach provides an effective reduction of complexity during inference. Ref. [55] showed that DPS could be used in both the forward pass (inference) and backward pass for training.

Efficient Activation Function Selection can play an important role in complexity reduction. The expensive activation functions, e.g. hyperbolic tangent or sigmoid can be replaced by the approximated alternatives or with the Look-up Table to reduce the computation [56]. Simpler functions such as ReLU (Rectified Linear Unit) are also commonly chosen because of their simplicity in calculation and speed.

### C. Complexity Reduction in Hardware Synthesis

Complexity reduction techniques of NN in hardware synthesis play a crucial role in optimizing the NN implementation on dedicated hardware. In hardware synthesis, the NN is mapped onto the hardware architecture, and the hardware design is optimized to achieve the desired performance while minimizing resource utilization. There are some techniques to reduce the complexity of the hardware, such as multiplier/adder approximations, parallelization, memoization, and skipping. The choice of suitable techniques depends on the NN architecture, the characteristics of the target hardware, and the desired trade-off between computational efficiency and model accuracy.

Multiplier/adder approximation is to reduce the hardware resource requirements by approximating multiplier and adder which are key components of the hardware implementation for NN computation [57]. The approximation replaces full-precision multipliers and adders with less resource-intensive multipliers and adder implementations, such as approximate adders or low-precision. Binary or ternary multipliers are examples of low-precision alternatives. By using lower-precision multipliers and adder implementations, the overall hardware complexity is reduced. This can lead to more efficient use of hardware resources without significantly sacrificing model accuracy.

Parallelization involves dividing the neural network into multiple sub-networks to be processed simultaneously, aiming for faster and more efficient execution in terms of latency and throughput [58]. This methodology capitalizes on parallel hardware architectures, such as GPUs, yielding heightened computational efficiency. As detailed in Ref. [59], Parallelization can take various forms including: Data Parallelism, where multiple NN instances operate simultaneously on distinct data batches; Model Parallelism, involving the division of a single neural network across multiple processors or GPUs, with different components processed on separate devices; and Pipeline Parallelism (Inter-Layer parallelism), which segments the neural network computation into stages, each executed by a distinct processing unit such that the data flow resembles a sequential assembly line.

**Memoization** stores and reuses intermediate results of expensive computations in memory to avoid recalculation when the same input reappears [60], [61]. This can be especially beneficial in RNN or other architectures with repetitive computations, leading to improved hardware efficiency. Even the simple implementation of memoization in Ref. [61] could speed up different experiments with different workloads ranging from 7% up to 25%.

**Skipping** can be used to decrease the executed workload and reduce computational costs. This method selectively skips certain computations based on their relevance to the final output or the predefined conditions. Skipping approximations can be performed by a simple calculation to evaluate if a more complex computation can be eliminated [60].

**Dynamic computation graph** allows the structure of the NN to change dynamically at runtime [62]. While the static graph fixes the structure of the NN (like the sequence of operations and connections) before the beginning of training, the dynamic graph constructs the structure of the NN on-the-fly during execution. This approach allows flexibility as it adapts the structure efficiently depending on varying input types and conditions.

Layer pipelining splits the processing of different layers in NN into sequential stages that overlap in time to allow parallelization of the computation. This method [63] allows scalable model parallelism with high hardware utilization and training stability. Pipelining algorithm library, GPipe, from [63] is a library to train a giant NN, with efficiency (speeds up the

<sup>1</sup>In addition to the aforementioned parallelization techniques, another subcategory worth mentioning is intra-layer parallelism, often referred to as Tensor Parallelism. This method entails parallelizing computations within a single layer of the neural network. Specifically, it involves partitioning large tensors, such as weight matrices, of a layer across multiple devices, facilitating parallel computations on these segmented chunks.

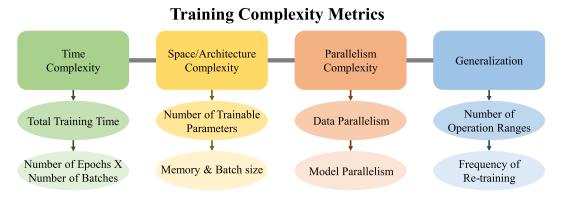

Fig. 2. Main metrics to evaluate complexity in the training phase for NN-equalizers.

process), flexibility (supports any deep network), and reliability (guarantees consistent training).

**Data partitioning** is an approach to divide the input data into subsets to be processed in parallel by different hardware components independently [64]. After that, the result of each partition is combined. Ref. [65] demonstrated that with their data partitioning approach, only small memory storage is required, instead of duplicating the whole data set size over all the processing units.

## D. Insights for Low-Complexity NN Equalizers Implementation

For the training, we believe that one of the most important and promising techniques in reducing computational complexity and enhancing the generalization of NN-based equalizers is multi-task learning. As in real-world scenarios, the equalizers require reconfiguration and must be adjustable to compensate for the variation of impairments as the channel characteristics change [43]. By implementing multi-task learning, the model does not need to be re-trained if performing in the range of knowledge acquired in training, but the model might experience a trade-off between overall performance and specific task performance. This robust approach enables a more practical utilization of NN-based equalizers, aligning closely with real-world demands.

For the inference, we advocate for the utilization of weight clustering techniques to optimize model size and computational complexity. This approach enables us to reduce the NN model's footprint, approaching levels comparable to constrained hardware environments such as CDC complexity [15]. Weight clustering achieves this by consolidating the number of distinct multipliers in matrix multiplication operations to at least the number of clusters per input element. Additionally, it facilitates heterogeneous quantization by minimizing the number of bits required to represent the weights effectively. Such strategies are pivotal in hardware implementations, where resource constraints necessitate efficient utilization of computational resources.

In the domain of hardware synthesis, we investigate various strategies to optimize the implementation of neural

network-based equalizers. This involves delving into partitioning schemes, which encompass different strategies for distributing data and computations across processing units. One such approach involves layer-wise partitioning, where each layer of the neural network is allocated to specific processing units. Alternatively, channel-wise partitioning allocates computations related to individual channels of input data to separate processing units. These partitioning schemes aim to exploit parallelism within the neural network, thereby enhancing hardware efficiency and performance.

Furthermore, we explore parallelization architectures tailored for the efficient execution of parallel processing tasks. Systolic arrays represent one such architecture that orchestrates computations through a pipeline of processing elements arranged in a grid-like fashion. Specialized neural network accelerators are also investigated, leveraging dedicated hardware components optimized for executing neural network operations in parallel. These architectures are designed to exploit inherent parallelism within neural network computations, leading to significant improvements in performance and throughput.

In addition to partitioning and parallelization strategies, we focus on memory access optimization techniques to minimize overhead during data retrieval and processing. This involves optimizing memory access patterns to minimize latency and maximize bandwidth utilization. Techniques such as data prefetching, caching, and memory banking are explored to streamline memory access operations and alleviate bottlenecks associated with partitioned data processing. By optimizing memory access, we aim to enhance overall system efficiency and throughput in hardware implementations of neural network-based equalizers.

#### III. COMPLEXITY METRICS (TRAINING AND INFERENCE)

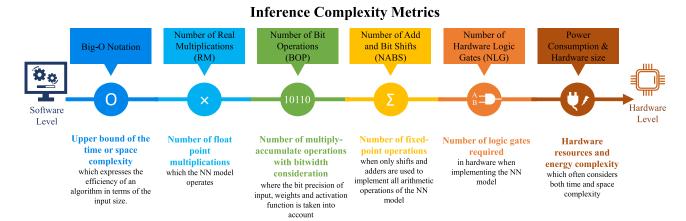

After implementing the mentioned complexity reduction strategies, it is essential to evaluate their effectiveness. This section gives a comprehensive understanding of the model's complexity during the training and real-time inference phases on the target hardware platform. Figs. 2 and 3 show the metrics used to measure the complexity of training and inference phases, respectively.

Fig. 3. Main metrics to evaluate complexity in the inference phase for NN-equalizers.

### A. Complexity Metrics for Training

For training, the computational complexity of the NN should be appropriately evaluated, as it allows for efficient resource allocation and is useful for comparing different models to assess the efficiency and effectiveness of various model architectures. Several metrics can be used to assess the complexity of NNs, which can be categorized into four key areas: time, space/architecture complexity, parallelism complexity, and generalization. Adopting a multidimensional perspective is important because a single metric cannot provide a holistic understanding of the true complexity of training. Each dimension offers unique insights, guiding informed trade-offs between model performance, resource requirements, and generalization capabilities. Next, we will further detail each of these key areas of training complexity measurements:

*Time complexity:* The traditional measures refer to the training time and the number of epochs required to achieve the desired performance. These metrics also take into consideration the learning rate and the optimizer used. Even though the training time metric and the number of epochs metrics show, to some degree, the training complexity, these metrics are a poor benchmark since the training time depends heavily on the hardware resources used and the size of the training dataset. In addition, two NNs with the same number of epochs to achieve the same performance can have very distinct training time, also depending on the batch size. To address these issues, an additional metric is proposed. The product of the number of epochs and the number of batches (NENB), reflects the model's computational demand. More training epochs generally indicate a more complex and computationally demanding model. The number of batches refers to the number of subsets of data used during each epoch, which is affected proportionally by the dataset size and batch size. The number of epochs and the number of batches cannot be evaluated separately, as one model may require more epochs but fewer batches, while another model may require fewer epochs but more batches. Lastly, FLOPs (Floating Point Operations) can be used to measure the number of floating-point operations required to train the model. A higher number of FLOPs typically indicates higher time complexity.

Space/Architecture Complexity: The number of trainable parameters, while commonly used, may not fully capture the complexity due to different architectural designs. For example, two NNs with the same number of trainable parameters can have very distinct training complexity [66]. The model architecture indicates the complexity of the NN architecture itself, such as the depth, width (e.g. the number of layers and neurons) of the network, and specific architectural choices such as recurrent, or convolution. The next metric is the memory requirement for storing the weights, biases of the NN, and intermediate computations during training. The space complexity can be influenced by the batch size used during training. Larger batch sizes might require more memory, particularly on GPU devices.

Parallelism Complexity: This aspect consists of data parallelism and model parallelism. Data parallelism is the parallelism and model parallelism. Data parallelism is the parallelization of training across multiple devices by splitting the dataset. Model parallelism is about distributing the model across different devices for processing. Parallelizability also refers to how scalable the training process is with added computational resources and the efficiency of distributing the training process across multiple GPUs. For example, the MLP feed-forward NN is fully parallelizable and can result in faster training. To be more specific, the training time of RNN compared to the MLP with the same number of trainable parameters can be significantly longer, as the recurrent architecture of RNN is more complex than the feed-forward structure of the MLP.

Generalization: The flexibility/generalizability is assessed by estimating the number of operational ranges in which the NN equalizer operates with an acceptable gain. If the NN can only perform a specific task, it requires frequent re-training in the future, contributing to the overall complexity. Therefore, the NN that performs well in different but related tasks without re-training is preferable [43].

## B. Complexity Metrics for Inference

Accurate computational complexity evaluation is critical in the design of digital signal processing (DSP) devices to better understand the implementation feasibility and bottlenecks for each device's structure. With this in mind, we summarize the four most commonly used criteria for assessing computational complexity, from the software level to the hardware level, in Fig. 3.

1) Real Multiplications: The first, most software-oriented, level of estimation traditionally deals only with counting the number of real multiplications of the algorithm [67], [68] (quite often defined per one processed element, say a sample or a symbol). This metric is the number of real multiplications (RM). When comparing computational complexity, the purpose of this high-level metric is to consider only the multipliers required, ignoring additions, because the implementation of the latter in hardware or software is initially considered cheap, while the multiplier is generally the slowest element in the system and consumes the largest chip area [67], [69]. This ignoring of the additions can also be easily understood by looking at the Big-O analysis of multiplier versus adder. When multiplying two integers with n digits, the computational complexity of the multiplication instance is  $O(n^2)$ , whereas the addition of the same two numbers has a computational complexity of  $\Theta(n)$ [70].<sup>2</sup> As a result, if you are dealing with float values with 16 decimal digits, multiplication is by far the most time-consuming part of the implementation procedure. Therefore, when comparing solutions that use floating-point arithmetic with the same bitwidth precision, the RM metric provides an acceptable comparative estimate to qualitatively assess the complexity against some existing benchmarks (e.g. against the DSP operations for optical channel equalization tasks [68]).

2) Number of Bit-Operations: When moving to fixed-point arithmetic, the second metric known as the number of bitoperations (BOP) must be adopted to understand the impact of changing the bitwidth precision on the complexity. The BOP metric provides a good insight into mixed-precision arithmetic performance since we can forecast the BOP needed for fundamental arithmetic operations like addition and multiplication, given the bitwidth of two operands. In a nutshell, the BOP metric aims to generalize floating-point operations (FLOPs) to heterogeneously quantized NNs, as far as the FLOPs cannot be efficiently used to evaluate integer arithmetic operations [25], [71]. For the BOP metric, we have to include the complexity contribution of both multiplications and additions, since now we evaluate the complexity in terms of the most common operations in NNs: the multiply-and-accumulate operations (MACs) [25], [71], [72]. However, the BOP accounts for the scaling of the number of multipliers with the bitwidth of two operands, and the scaling of the number of adders with the accumulator bitwidth. Note that since most real DSP implementations use dedicated logic macros (e.g. DSP slice in Field Programmable Gate Arrays [FPGA] or MAC in Application Specific Integrated Circuit [ASIC]), the BOP metric fits as a good complexity estimation metric inasmuch as the BOP also accesses the MAC taking into account the particular bitwidth of two operands.

3) Number of Additions and bit Shifts: The progress in the development of new advanced NN quantization techniques [74], [75], [76], [77] allowed implementing the fixed point multiplications participating in NNs efficiently, namely with the use of a few bit-shifters and adders [78], [79], [80]. Since the BOP lacks the ability to properly assess the effect of different quantization strategies on the complexity, a new, more sophisticated metric is required there. We introduce the third complexity metric that counts the number of total equivalent additions to represent the multiplication operation, called the number of additions and bit shifts (NABS). The number of shift operations can be neglected when calculating the computational complexity because, in the hardware, the shift can be performed without extra costs in constant time with the O(1) complexity. Even though the cost of bit shifts can be ignored due to the aforementioned reasons, and only the total number of adders has to be accounted for to measure the computational complexity, we prefer to keep the full name "number of additions and bit shifts" to highlight that the multiplication is now represented as shifts and adders.

4) Number of Logic Gates: The metric closer to the hardware level is the number of logic gates (NLG) that is used for our evaluating method's hardware (e.g. ASIC or FPGA) implementation. It is different from the NABS metric, as now the true cost of implementation is to be presented. In this case, in contrast to the other complexity metrics, the cost of activation functions is also taken into account because, to achieve better complexity, they are frequently implemented using look-up tables (LUT) rather than adders and multipliers. Additionally, other metrics like the number of flip-flops (FFs) or registers, the number of logic blocks used for general logic and memory blocks, or other special functional macros used in the design, are also relevant. As it is clear from this explanation, there is no straightforward equation to convert the NABS to the NLG as the latter depends on the circuit design adopted by the developer. Tools such as Synopsys Synthesis [81] for ASIC implementation can provide this kind of information. However, regarding the FPGA design, it is harder to get a correct estimate of the gate count from the report of FPGA tools [82].

In this paper, we advocate that the NLG metric should be applied to count the number of logic gates used to implement the hardware piece, similar to the concept of the Maximum Logic Gates metric for FPGA devices [73]. The Maximum Logic Gates metric is utilized to approximate the maximum number of gates that can be realized in the FPGA for a design consisting of only logic functions.<sup>3</sup> Additionally, this metric is based on an estimate of the typical number of usable gates per configurable logic block (CLB) or logic cell multiplied by the total number of such blocks or cells [73]. Concerning the correspondence between CLB and logic gates number, see Table I.

It should be noted that Table I is based on an older, now obsolete, 4-input LUT architecture [73]. Newer FPGA families now feature a 6-input LUT architecture, and to address the resource consumption for the new generation of devices, a reasonable approximation would be to increase the 'maximum gate range equivalent per LUT' figure used in [73] by 50%.

$<sup>^2</sup>$ The Big-O notation represents the worst case or the upper bound of the time required to perform the operation, Big Omega  $(\Omega)$  shows the best case or the lower bound, whereas the Big Theta  $(\Theta)$  notation defines the tight bound of the amount of time required; in other words, f(n) is claimed to be  $\Theta(g(n))$  if f(n) is O(g(n)) and f(n) is O(g(n)).

<sup>&</sup>lt;sup>3</sup>On-chip memory capabilities are not factored into this metric.

$TABLE\ I$  Capacity Ranges for XC4000 Series CLB Resources Given in Ref. [73]

| CLB Resource                              | Logic Gate Range |  |  |

|-------------------------------------------|------------------|--|--|

| Gate range per 4-input LUT (2 per CLB)    | 1 to 9           |  |  |

| Gate range per 3-input LUT                | 1 to 6           |  |  |

| Gate range per flip-flop (2 per CLB)      | 6 to 12          |  |  |

| Total gate range per CLB                  | 15 to 48         |  |  |

| Estimated typical number of gates per CLB | 28.5             |  |  |

TABLE II

ESTIMATED CAPACITY RANGES FOR 6 INPUT LUT-BASED CLB RESOURCES

| CLB Resource                           | Logic Gate Range |  |  |

|----------------------------------------|------------------|--|--|

| Gate range per 6-input LUT (8 per CLB) | 6 to 15          |  |  |

| Gate range per flip-flop (16 per CLB)  | 6 to 12          |  |  |

| Total gate range per CLB               | 144 to 312       |  |  |

Note that the gate equivalence figures for FF's (registers) still hold true for the 6-input architecture. It is also worth noting that the CLB architecture has changed substantially since Ref. [73] was published, such that we include Table II linking CLB-gates with a more up-to-date 6-input architecture.

To conclude, we comment on universal metrics between the FPGA and the ASIC implementations. We emphasize that calculating an ASIC gate equivalent to an FPGA DSP slice is not a straightforward task because not all features are necessarily required when implementing the specific arithmetic function in an ASIC. However, utilizing the estimation approach laid out in Ref. [73], a figure can be obtained. Using the Xilinx Ultrascale + DSP48E2 slice basic multiplier functionality as an example (see Xilinx UG579 Fig. 1–1 in Ref. [83]) and pipelining it for maximum performance, it is possible to estimate the number of FFs and adders required for such an ASIC equivalence. Taking into account the structure of the multiplication of a m-bit number by a n-bit number, implemented using an array multiplier architecture, it is equivalent to  $m \times n$  AND gates, n half adders, and  $(m-2) \times n$  full adders.<sup>4</sup> For example, the ASIC equivalence of a 27 × 18 multiplier in an FPGA would have 486 AND gates, 18 half adders, 450 full adders, and 90 FFs.

Note that, estimating the NABS that can be implemented on FPGA hardware presents a considerable challenge, owing to the multitude of factors influencing FPGA implementations. These factors include resource availability such as the number of CLBs and LUTs, the efficacy of programming methodologies to effectively utilize available resources, as well as constraints related to routing, placing, clock frequency, and throughput limitations, among others. Despite the complexity of this estimation, an initial assessment can be made by considering the potential parallelism of NABs per clock cycle, primarily leveraging LUTs and DSP blocks. For instance, one can consider the Xilinx FPGA VCK190 as an example. With 899,840 LUTs and 1,968 DSP blocks available, a rough estimation can be derived in an ideal scenario utilizing LUTs, up to 449,920 additions and bit shifts could theoretically be implemented. This estimation assumes a

simplistic model where each operation requires only 2 LUTs. However, it's important to note that this is an oversimplification, and actual resource utilization may vary due to practical considerations such as routing constraints. Additionally, **utiliz**ing DSP blocks, designed for efficient arithmetic operations, can potentially accommodate an additional 1,968 operations. However, this estimation presupposes optimal utilization of LUTs, which may not always be achievable in practice. Furthermore, it's important to acknowledge that the actual feasibility of implementing NABs on FPGA hardware is influenced by factors such as clock speed, memory requirements, and specific application demands. Therefore, while these estimations provide valuable insights, they serve as initial benchmarks and must be validated through comprehensive analysis and optimization efforts tailored to the specific hardware platform and application requirements.

Finally, this work especially focuses on the four inference complexity metrics of the NN (RM, BOP, NABS, and NLG). Apart from the aforementioned metrics, the power consumption, memory footprint, and complexity of the activation function should be assessed. Power consumption should be considered as it can result in a bottleneck during the implementation phase. Memory footprint refers to the input size of the time series and the number of parameters that need to be saved in the memory, taking into account the quantization scheme. This complexity of the activation function, considering different types of activation functions and the approximation techniques, is another aspect to keep in mind [56].

### C. Usage of the Complexity Metrics in Photonic Hardware

It can be questionable if the aforementioned metrics proposed to access the computational complexity in the inference phase of the electronic hardware can be used to access the complexity in the photonic hardware too. When discussing the complexity of computations in photonic NN hardware [84], [85] or photonics integrated circuits (e.g. PICs), it involves different considerations compared to traditional electronic computing (e.g., FPGA and ASIC). We can discuss metric by metric as follows:

- Real multiplication is also suitable for photonic computing as in the context of NN, matrix-vector multiplications are a core operation. Photonic computing allows multiplications without the need for converting to electronic signals [85].

- 2) Number of bit operations (BOP) are only partially suitable for photonic computing because photonic computing can use the analog properties and continuous values of light, such as amplitude and phase, to encode information. However, digital photonic computing also exists. Digital photonic computing represents information in optical on-off keying or other discrete states. BOP can be relevant but might not be the most comprehensive metric, depending on the types of photonic computing architectures.

- 3) Number of adders and bit shifts (NABS) might not be a suitable metric because the photonic hardware does not directly use shifts and adders in the same way as electronic circuits. The operations in photonic systems are more about manipulating light's physical properties

<sup>&</sup>lt;sup>4</sup>Note that a half adder is equivalent to 1 AND gate + 1 XOR gate, and a full adder is equal to 2 AND gates + 2 XOR gates + 1 OR gate

#### TABLE III

Summary of the Three Computational Complexity Metrics Per Layer (The Number of Real Multiplications, the Number of Bit Operations, the Number of Additions and Bit Shifts) for a Zoo of Neural Network Layers as a Function of Their Designing Hyper-Parameters; the Number of Neurons  $(n_n)$ , the Number of Features in the Input Vector  $(n_i)$ , the Number of Filters  $(n_f)$ , the Kernel Size  $(n_k)$ , the Input Time Sequence Size  $(n_s)$ , the Number of Hidden Units  $(n_h)$ , the Number of Internal Hidden Neuron Units of the Reservoir  $(N_T)$ , Sparsity Parameter  $(s_p)$ , the Number of Output Neurons  $(n_o)$ , Weight Bitwidth  $(b_w)$ , Input Bitwidth  $(b_i)$ , Activation Bitwidth  $(b_a)$  and the Number of Adders Required At Most to Represent the Multiplication  $(X_w)$

| Network type | Real multiplications (RM)                                       | Number of bit-operations (BOP)                                                                                                                                                                                          | Number of additions and bit shifts(NABS)                                                                                                                                                                                                                                       |  |  |

|--------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MLP          | $n_n n_i$                                                       | $n_n n_i [b_w b_i + \operatorname{Acc}(n_i, b_w, b_i)]$                                                                                                                                                                 | $n_n n_i (X_w + 1) \mathrm{Acc}(n_i, b_w, b_i)$                                                                                                                                                                                                                                |  |  |

| 1D-CNN       | $n_f n_i n_k \cdot Output Size$                                 | $OutputSize \cdot n_f \text{Mult}(n_i n_k, b_w, b_i) \\ + n_f \text{Acc}(n_i n_k, b_w, b_i)$                                                                                                                            | $OutputSize \cdot n_f [n_i n_k (X_w + 1) - 1]$ $\cdot Acc(n_i n_k, b_w, b_i)$ $+ n_f Acc(n_i n_k, b_w, b_i)$                                                                                                                                                                   |  |  |

| Vanilla RNN  | $n_s n_h (n_i + n_h)$                                           | $\begin{aligned} n_s n_h \text{Mult}(n_i, b_w, b_i) \\ + n_s n_h \text{Mult}(n_h, b_w, b_a) \\ + 2n_s n_h \text{Acc}(n_h, b_w, b_a) \end{aligned}$                                                                      | $ n_{s}n_{h}[n_{i}(X_{w}+1)-1]\operatorname{Acc}(n_{i},b_{w},b_{i}) +n_{s}n_{h}[n_{h}(X_{w}+1)+1]\operatorname{Acc}(n_{h},b_{w},b_{a}) $                                                                                                                                       |  |  |

| LSTM         | $n_s n_h (4n_i + 4n_h + 3)$                                     | $\begin{aligned} &4n_sn_h \text{Mult}(n_i,b_w,b_i) \\ &+4n_sn_h \text{Mult}(n_h,b_w,b_a) \\ &+3n_sn_hb_a^2 \\ &+9n_sn_h \text{Acc}(n_h,b_w,b_a) \end{aligned}$                                                          | $ \begin{array}{c} 4n_{s}n_{h} \left[n_{i}(X_{w}+1)-1\right] \mathrm{Acc}(n_{i},b_{w},b_{i}) \\ +4n_{s}n_{h} \left[n_{h}(X_{w}+1)+1\right] \mathrm{Acc}(n_{h},b_{w},b_{a}) \\ +6n_{s}n_{h}b_{a} \end{array} $                                                                  |  |  |

| GRU          | $n_s n_h (3n_i + 3n_h + 3)$                                     | $\begin{aligned} &3n_sn_h\text{Mult}(n_i,b_w,b_i)\\ &+3n_sn_h\text{Mult}(n_h,b_w,b_a)\\ &+3n_sn_hb_a^2\\ &+8n_sn_h\text{Acc}(n_h,b_w,b_a) \end{aligned}$                                                                | $ \begin{aligned} & 3n_s n_h \left[ n_i (X_w + 1) - 1 \right] \mathrm{Acc}(n_i, b_w, b_i) \\ & + n_s n_h \left[ 3n_h (X_w + 1) + 5 \right] \mathrm{Acc}(n_h, b_w, b_a) \\ & + 6n_s n_h b_a \end{aligned} $                                                                     |  |  |

| ESN          | $n_s N_r (n_i + N_r s_p + 2 + n_o)$                             | $\begin{aligned} &n_s N_r \text{Mult}(n_i, b_w, b_i) \\ &+ n_s N_r s_p \text{Mult}(N_r, b_w, b_a) \\ &+ n_s N_r \text{Mult}(n_o, b_w, b_a) \\ &+ 2n_s N_r b_a^2 \\ &+ 4n_s N_r \text{Acc}(N_r, b_w, b_a) \end{aligned}$ | $ \begin{vmatrix} n_s N_r \big[ n_i (X_w + 1) - 1 \big] \mathrm{Acc}(n_i, b_w, b_i) \\ + n_s N_r \big[ s_p (N_r X_w + N_r - 1 \big] + 4) \mathrm{Acc}(N_r, b_w, b_a) \\ + n_s N_r \big[ n_o (X_w + 1) - 1 \big] \mathrm{Acc}(n_o, b_w, b_a) \\ + 4 n_s N_r b_a \end{vmatrix} $ |  |  |

| ResNet       | Eq. (36)                                                        | Eq. (38)                                                                                                                                                                                                                | Eq. (40)                                                                                                                                                                                                                                                                       |  |  |

| Transformer  | MultiHead: Eq. (47) Point-wise FFN: Eq. (50) Add&Norm: Eq. (53) | MultiHead: Eq. (48) Point-wise FFN: Eq. (51) Add&Norm: Eq. (54)                                                                                                                                                         | MultiHead: Eq. (49) Point-wise FFN: Eq. (52) Add&Norm: Eq. (55)                                                                                                                                                                                                                |  |  |

through optical components, for example, waveguides, modulators, and detectors.

4) Number of logic gates is not a suitable metric for the photonic hardware, however, a similar concept can be considered. Instead of the gate count as in the electronic domain, we can count the number of optical components like modulators, detectors, and waveguides in the photonic implementation.

It is important to consider other factors when assessing the trade-off between the performance and complexity of equalizers and the associated hardware. For instance, aspects such as power efficiency [84] and the comparison of physical size or chip area are crucial. Note, that a direct comparison of raw power consumption between PICs and ASICs might be misleading. To accurately assess power efficiency, we should consider throughput, which is the amount of data processed per unit of time. A more insightful metric is energy efficiency, obtained by dividing the power consumption by the achieved throughput. This allows for a fair comparison, highlighting the ability of each technology to perform a specific task with minimal energy consumption.

The chip area is another critical factor in many applications. When comparing the area occupied by a PIC and an ASIC equalizer, it is essential to consider the functionality delivered per unit area. A larger PIC might integrate functionalities beyond simple equalization, offering a higher overall value proposition despite its larger footprint [86]. Conversely, a smaller ASIC

might excel in scenarios where compactness is paramount, even with a more limited functional range.

Finally, factors like scalability, reconfigurability, and sensitivity to fabrication imperfections can influence the choice between PICs and ASICs [87].

## IV. MATHEMATICAL COMPLEXITY FORMULATION

In this section, we provide a brief introduction to various types of NN: dense layer, Convolutional Neural Networks (CNN), Vanilla Recurrent Neural Networks (RNN), Long Short-Term Memory Neural Networks (LSTM), Gated Recurrent Units (GRU), and Echo State Networks (ESN). We investigate the computational complexity of each network in terms of RM, BOP, and NABS. In this work, the computational complexity is formulated per layer, and the output layer is not taken into account for the complexity calculation to eliminate redundant computations if multiple layers or multiple NN types are combined. Table III in the section's end summarizes the formulas for the RM, BOP, and NABS for all NN types studied. Furthermore, we have included all the complexity equations utilized in this study in Python code [88]. This resource is intended to aid readers in calculating the complexity of their own NN architectures.

## A. Dense Layer

A dense layer, also known as a 'fully connected layer', is a layer in which each neuron is connected with all the neurons

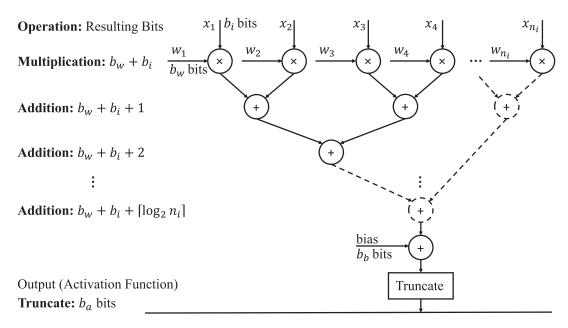

Fig. 4. Data path of a neuron in a quantized dense layer where x is the input vector with size  $n_i$ , w is the weight matrix,  $b_w$  is the weight bitwidth and  $b_i$  is the input bitwidth,  $b_a$  is the activation bitwidth and  $b_b$  is the bias bitwidth.

from the previous layer with a specific weight  $w_{ij}$ . The input vector is mapped to the output vector in a nonlinear manner by the dense layer, due to the participation of a non-linear activation function. Dense layers can be combined to form a Multi-Layer Perceptron (MLP), which is a class of a feed-forward deep NN.

The output vector y of a dense layer given x as an input vector is written as:

$$y = \phi(Wx + b),\tag{1}$$

where y is the output vector,  $\phi$  is a nonlinear activation function, W is the weight matrix, and b is the bias vector. Writing explicitly the matrix operation inside the activation function:

$$Wx + b = \begin{bmatrix} w_{11} & w_{12} & \dots & w_{1n_i} \\ w_{21} & w_{22} & \dots & w_{2n_i} \\ \vdots & \vdots & \dots & \vdots \\ w_{n_n1} & w_{n_n2} & \dots & w_{n_nn_i} \end{bmatrix} \begin{bmatrix} x_1 \\ x_2 \\ \vdots \\ x_{n_i} \end{bmatrix} + \begin{bmatrix} b_1 \\ b_2 \\ \vdots \\ b_{n_n} \end{bmatrix},$$

(2)

where  $n_i$  is the number of features in the input vector and  $n_n$  represents the number of neurons in the layer, we can readily see that the RM of a dense layer can be computed according to the simple, well-known formula:

$$RM_{Dense} = n_n n_i. (3)$$

Now we calculate the BOP of a dense layer, taking into account the bitwidth of two operands, to approximate the computational complexity of NNs when the mixed-precision arithmetic is used. The bitwidth, also known as the precision, is the number of bits used to represent a certain element; for example, each weight in the weight matrix can be represented with  $b_w$  bits. Fig. 4 illustrates the data flow of the MAC operations for a neuron of a dense layer with  $n_i$  input features and  $b_i$  as input bitwidth. The multiplication of the input vector and the weights for one neuron

can be mathematically represented as follows:

$$y_{\text{MUL, one neuron}} = \sum_{n=1}^{n_i} w_n x_n.$$

(4)

Initially, the  $n_i$  multiplications of input vector elements and weights for one neuron take place. When the multiplication of two operands is performed, the resulting bitwidth is the sum of the bitwidths of two operands  $(b_w + b_i)$  as shown in the first row of Fig. 4.

After that,  $n_i - 1$  additions need to be made, and the resulting number of bits can be defined as follows: Considering that the result of the addition of two operands has the bitwidth of the bigger operand plus one bit, we start adding the multiplication results pairwise until only one element remains. In this case, the second row of Fig. 4 shows the first level of pairwise additions, with a resulting bitwidth of  $b_w + b_i + 1$ , and since this pairwise addition process is repeated for  $\lceil \log_2(n_i) \rceil$  levels (until we have just a final single number), the total bitwidth of it is given by  $b_w + b_i + \lceil \log_2(n_i) \rceil$ , i.e. it is the bitwidth required to perform the overall MAC process. Then, the addition of the bias vector is performed. In this work, for all types of networks, we assume that the size of the accumulator defined by the multiplication of the weight matrix and the input vector, is dominant; thereby, the assumption for the bias bitwidth  $b_b$  is as follows:  $b_b < b_w + b_i + b_i$  $\lceil \log_2(n_i) \rceil$ , and the addition of bias, in the end, will not result in the overflow. Finally, the bitwidth of the resulting number is truncated to  $b_a$ , where  $b_a$  is the bitwidth of the activation function [20].

When calculating the BOP for a dense layer, the costs of both multiplications and additions need to be included. Then, the BOP formula takes the form of the sum of two constituents,  $BOP_{Mul}$  and  $BOP_{Bias}$ , corresponding to vector-matrix multiplication and

bias addition:

$$BOP_{Mul} = n_n [n_i b_w b_i + (n_i - 1)(b_w + b_i + \lceil \log_2(n_i) \rceil)],$$

(5)

$$BOP_{Bias} \approx n_n(b_w + b_i + \lceil \log_2(n_i) \rceil). \tag{6}$$

Equation (5) shows the cost of the number of one-bit full adders calculated from the dot product of  $n_i$ -dimensional input vector and weight matrix, as in Refs. [25], [89]. The cost takes into account the bitwidths of the weights and input,  $b_w$  and  $b_i$ . To compute the product of the two operands, we have to use  $n_i n_n$  multiplications and  $n_n(n_i-1)$  additions. The multiplication cost can be calculated by the number of multiplications multiplied by  $b_w b_i$ , which is related to the bit operation, and the number of additions multiplied by the accumulator bitwidth required to do the operation. The final BOP is the contribution of multiplication and the addition of bias of the dense layer. For the convenience of the forthcoming presentation, let us define the short notations:

$$\operatorname{Mult}(n_i,b_w,b_i) = n_i b_w b_i + (n_i - 1) \left( b_w + b_i + \lceil \log_2(n_i) \rceil \right),$$

and

$$Acc(n_i, b_w, b_i) = b_w + b_i + \lceil \log_2(n_i) \rceil.$$

The Acc expression represents the actual bitwidth of the accumulator required for MAC operation, as shown in Fig. 4. Then, the BOP of the dense layer expressed through the layer parameters becomes:

$$BOP_{Dense} = BOP_{Mul} + BOP_{Bias}$$

$$\approx n_n n_i \left[ b_w b_i + (b_w + b_i + \lceil \log_2(n_i) \rceil) \right]$$

$$\approx n_n n_i \left[ b_w b_i + Acc(n_i, b_w, b_i) \right]. \tag{7}$$

Now, we note that with the advancement in NN quantization techniques, there arises the opportunity to approximate multiplication by using shift and few add operations only while still maintaining a good processing accuracy, since the NNs can diminish the approximation error that the quantized approximation introduces [79], [90]. As mentioned in Section III, the number of shifts can be neglected compared to the contribution of adders. The number of adders is different for different types of quantization. To be more specific, let X represent the number of adders required, at most, to perform the multiplication and let b be the bitwidth of the quantized matrix. For uniform quantization, we have X = b - 1. And, for example, when the weight matrix with bitwidth of  $b_w$ , is quantized, we have  $X_w = b_w - 1$  as the number of adders we need at most to perform the multiplication of the weights. In the case of Power-of-Two (PoT)

quantization, we have X=0, because each multiplication costs just a shift [78], [94]. Lastly, for the Additive Powers-of-Two (APoT) quantization, we have X=n, where n denotes the number of additive terms. In APoT, the sum of n PoT terms is used to represent each quantization level [74]. Eventually, the NABS of a dense layer can be derived from its BOP equation, (7):

NABS<sub>Dense</sub>

$$\approx n_n n_i \left[ X_w \text{Acc}(n_i, b_w, b_i) + \text{Acc}(n_i, b_w, b_i) \right]$$

$\approx n_n n_i (X_w + 1) \text{Acc}(n_i, b_w, b_i).$  (8)

As in (8), the multiplication term  $b_w b_i$  in (7) is converted into the number of adders needed to operate the multiplication times the accumulator bitwidth required:  $X_w \operatorname{Acc}(n_i, b_w, b_i)$ .

### B. Convolutional Neural Networks

In CNN, we apply the convolutions with different filters to extract the features and convert them into a lower-dimensional feature set, while still preserving the original properties. CNNs can be used in 1D, 2D, or 3D networks, depending on the applications. In this paper, we focus on 1D-CNNs, which apply to processing sequential data [3]. For simplicity of understanding, the 1D-CNN processing with padding equal to 0, dilation equal to 1, and stride equal to 1, can be summarized as follows:

$$y_i^f = \phi \left( \sum_{n=1}^{n_i} \sum_{j=1}^{n_k} x_{i+j-1,n}^{in} \cdot k_{j,n}^f + b^f \right), \tag{9}$$

where  $y_i^f$  denotes the output, known as a feature map, of a convolutional layer built by the filter f in the i-th input element,  $n_k$  is the kernel size,  $n_i$  is the size of the input vector,  $x^{in}$  represents the raw input data,  $k_j^f$  denotes the j-th trainable convolution kernel of the filter f and  $b^f$  is the bias of the filter f.

In the general case, when designing the CNN, parameters like padding, dilation, and stride also affect the output size of the CNN. It can be formulated as:

OutputSize =

$$\left[\frac{n_s + 2 \, padding - dilation(n_k - 1) - 1}{stride} + 1\right], \tag{10}$$

where  $n_s$  is the input time sequence size.

The RM of a 1D-convolutional layer can be computed as follows:

$$RM_{CNN} = n_f n_i n_k \cdot Output Size, \tag{11}$$

where  $n_f$  is the number of filters, also known as the output dimension. As in (11), there are  $n_i n_k$  multiplications per sliding window, and the number of times that sliding window process needs to be repeated is equal to the output size. Then, the procedure is executed repeatedly for all  $n_f$  filters.

The BOP for a 1D-convolutional layer, after taking into consideration the multiplications and additions, can be represented as:

$$BOP_{CNN} = OutputSize \cdot n_f Mult(n_i n_k, b_w, b_i)$$

$$+ n_f Acc(n_i n_k, b_w, b_i).$$

(12)

<sup>&</sup>lt;sup>5</sup>Note that using the shifts and adders to perform multiplications can cause some quantization noise/error since we are converting from a float-point representation to a fixed-point representation with some defined quantized level of values. However, in NNs, this noise can be partially mitigated by including those quantized weights in the NN training process as in Refs. [75], [76], [77]

<sup>&</sup>lt;sup>6</sup>Note that we can consider other techniques for the representation of such fixed-point multiplication to reduce its complexity e.g. the double-base number system where each multiplication with b bits, at worst, needs no more than b/log(b) additions [91]. For the Canonical Signed Digit (CSD) representation, in the worst-case scenario, we have (b+l)/2 nonzero bits and on average it tends asymptotically to (3b+l)/9 [92], [93]

Equation (12) is derived from (9) and (11). The first term is associated with the convolution operation between the flattened input vector and the sliding windows, and the latter term corresponds to the addition of the bias.

The procedure to derive the NABS is similar to that described in detail in the case of a dense layer, Section IV-A. The NABS of a 1D-convolutional layer is given by:

$$NABS_{CNN} = OutputSize \cdot n_f \left[ n_i n_k (X_w + 1) - 1 \right]$$

$$\cdot Acc(n_i n_k, b_w, b_i)$$

$$+ n_f Acc(n_i n_k, b_w, b_i). \tag{13}$$

To obtain the 1D-convolutional layer's NABS, the multiplication in (12) is represented by the number of adders required, at most, to perform the multiplication times the accumulator bitwidth.

#### C. Vanilla Recurrent Neural Networks

Vanilla RNN is different from MLP and CNN in terms of its ability to handle memory, which is quite beneficial for time series data. RNNs take into account the current input and the output that the network has learned from the prior input. Even though the RNNs introduced efficient memory handling, they still suffer from the inability to capture the long-term dependencies because of the vanishing gradient issue [95]. The equation for the vanilla RNN given a time step t is as follows:

$$h_t = \phi(Wx_t + Uh_{t-1} + b),$$

(14)

where  $\phi$  is, again, the nonlinear activation functions,  $x_t \in \mathbb{R}^{n_t}$  is the  $n_i$ -dimensional input vector at time t,  $h_t \in \mathbb{R}^{n_h}$  is a hidden layer vector of the current state with size  $n_h$ ,  $W \in \mathbb{R}^{n_h \times n_i}$  and  $U \in \mathbb{R}^{n_h \times n_h}$  represent the trainable weight matrices, and b is the bias vector. For more explanations on the vanilla RNN operation, see Ref. [96]. The RM of a vanilla RNN is:

$$RM_{RNN} = n_s n_h (n_i + n_h), \tag{15}$$

where  $n_h$  notes the number of hidden units. From (15), the RM for a time step is  $n_h(n_i+n_h)$ . It can be separated into two terms; the  $n_h n_i$  term corresponds to the multiplication of the input vector  $x_t$  and the weight matrix, and the  $n_h^2$  term arises because of the multiplication to the prior cell output  $h_{t-1}$ . Finally,  $n_s$ , which denotes the number of time steps in the layer, should be taken into account, as the process is repeated  $n_s$  times.

The BOP for a vanilla RNN is given as:

$$BOP_{RNN} = n_s n_h Mult(n_i, b_w, b_i)$$

$$+ n_s n_h Mult(n_h, b_w, b_a)$$

$$+ 2n_s n_h Acc(n_h, b_w, b_a). \tag{16}$$

From (16), the first term is associated with the input vector multiplied by the weight matrix, and the second term corresponds to the multiplications of the recurrent cell outputs. The final term is the contribution of the addition between  $Wx_t + Uh_{t-1}$  and the addition of the bias vector in (14); one can see that the size of the accumulator used in this term, is  $Acc(n_h, b_w, b_a)$ . It is due to the assumption that  $Acc(n_h, b_w, b_a)$  is dominant because it

should be greater than  $Acc(n_i, b_w, b_i)$  as a result of the inequality  $n_h > n_i$ .

As in the case of a dense layer, the NABS of vanilla RNN can be calculated from its BOP equation by converting the multiplication to the number of adders needed at most (X) depending on the quantization scheme and the accumulator size:

$$NABS_{RNN} = n_s n_h [n_i(X_w + 1) - 1] Acc(n_i, b_w, b_i)$$

$$+ n_s n_h [n_h(X_w + 1) + 1] Acc(n_h, b_w, b_a).$$

(17)

## D. Long Short-Term Memory Neural Networks

LSTM is an advanced type of RNNs. Although RNNs suffer from short-term memory issues, the LSTM network can learn long-term dependencies between time steps (t), insofar as it was specifically designed to address the gradient issues encountered in RNNs [97], [98]. There are three types of gates in an LSTM cell: an input gate  $(i_t)$ , a forget gate  $(f_t)$ , and an output gate  $(o_t)$ . More importantly, the cell state vector  $(C_t)$  was proposed as a long-term memory to aggregate the relevant information throughout the time steps. The equations for the forward pass of the LSTM cell given a time step t are as follows:

$$i_{t} = \sigma(W^{i}x_{t} + U^{i}h_{t-1} + b^{i}),$$

$$f_{t} = \sigma(W^{f}x_{t} + U^{f}h_{t-1} + b^{f}),$$

$$o_{t} = \sigma(W^{o}x_{t} + U^{o}h_{t-1} + b^{o}),$$

$$C_{t} = f_{t} \odot C_{t-1} + i_{t} \odot \phi(W^{c}x_{t} + U^{c}h_{t-1} + b^{c}),$$

$$h_{t} = o_{t} \odot \phi(C_{t}),$$

(18)

where  $\phi$  is usually the "tanh" activation function,  $\sigma$  is usually the sigmoid activation function, the sizes of each variable are  $x_t \in \mathbb{R}^{n_i}$ ,  $f_t, i_t, o_t \in (0,1)^{n_h}$ ,  $C_t \in \mathbb{R}^{n_h}$  and  $h_t \in (-1,1)^{n_h}$ . The  $\odot$  symbol represents the element-wise (Hadamard) multiplication.

The RM of an LSTM layer is:

$$RM_{LSTM} = n_s n_h (4n_i + 4n_h + 3), \tag{19}$$

where  $n_h$  is the number of hidden units in the LSTM cell. Similarly to RNNs, the RM can be calculated from the term associated with the input vector  $x_t$  and the term corresponding to the prior cell output  $h_{t-1}$ ; however, each term occurs four times, as we can see in (18). Therefore, we have  $4n_hn_i$  and  $4n_h^2$ , respectively. Moreover, we also need to include the element-wise product that is operated three times in (18), which costs  $3n_h$ . Finally, the process is repeated  $n_s$  times, hence,  $n_s$  is multiplied to the overall number.

The BOP for an LSTM layer is computed based on (19), but also includes the bitwidth of the operands and the number of additions. As a result, the BOP can be represented as:

$$BOP_{LSTM} = 4n_s n_h Mult(n_i, b_w, b_i)$$

$$+ 4n_s n_h Mult(n_h, b_w, b_a)$$

$$+ 3n_s n_h b_a^2$$

$$+ 9n_s n_h Acc(n_h, b_w, b_a). \tag{20}$$

To give more details on the expression, the first two terms in (20) are the contribution of the input vector multiplications and the recurrent cell output association, respectively. The term  $3n_sn_hb_a^2$  refers to 3 times of the element-wise product of two operands with  $b_a$  bitwidth, see (18). For each time step, there are  $n_h$  elements in each vector that need to be multiplied. The last term is for all the additions since we assume that  $Acc(n_h, b_w, b_a)$  gives the dominant contribution, as described in Section IV-C. Finally, the process is then restarted  $n_s$  times.

The NABS of an LSTM layer is derived from the (20) by replacing the multiplications with the shifts and adders including their cost, as mentioned in Section III that the shifts would not be included. The number of adders depends on the quantization technique. The NABS would be as follows:

NABS<sub>LSTM</sub> =

$$4n_s n_h [n_i(X_w + 1) - 1] \operatorname{Acc}(n_i, b_w, b_i)$$

$+ 4n_s n_h [n_h(X_w + 1) + 1] \operatorname{Acc}(n_h, b_w, b_a)$

$+ 6n_s n_h b_a.$  (21)

The first and second terms are the results of input vector multiplications and the recurrent cell operation combined with all addition operations, respectively. In this case, the third term comes from  $3n_sn_h(b_a+b_a)$ . Due to the element-wise product of two operands with bitwidth  $b_a$ , the resulting bitwidth becomes  $b_a+b_a$  as mentioned in Fig. 4.

### E. Gated Recurrent Units

Like LSTM, the GRU network was created to overcome the short-term memory issues of RNNs. However, GRU is less complex, as it has only two types of gates: reset  $(r_t)$  and update  $(z_t)$  gates. The reset gate is used for short-term memory, whereas the update gate is responsible for long-term memory [99]. In addition, the candidate hidden state  $(h'_t)$  is also introduced to state how relevant the previous hidden state is to the candidate state. The GRU for a time step t can be formalized as:

$$z_{t} = \sigma(W^{z}x_{t} + U^{z}h_{t-1} + b^{z}),$$

$$r_{t} = \sigma(W^{r}x_{t} + U^{r}h_{t-1} + b^{r}),$$

$$h'_{t} = \phi(W^{h}x_{t} + r_{t} \odot U^{h}h_{t-1} + b^{h}),$$

$$h_{t} = z_{t} \odot h_{t-1} + (1 - z_{t}) \odot h'_{t},$$

(22)

where  $\phi$  is typically the "tanh" activation function and the rest of the designations are the same as in (18).

The RM of the GRU is calculated in the same way as we did for the LSTM in (19), but the number of operations with the input vector  $x_t$  and with the previous cell output  $h_{t-1}$  is reduced from four (LSTM) to three times as shown in (22). Thus, the expression for the RM becomes:

$$RM_{GRU} = n_s n_h (3n_i + 3n_h + 3). \tag{23}$$

The BOP for the GRU can be calculated in the same manner as we did for the LSTM in (20). However, now, the expression is slightly different in the number of matrix multiplications as the number of gates is now lower. The BOP number can be

represented as:

$$BOP_{GRU} = 3n_s n_h Mult(n_i, b_w, b_i)$$

$$+ 3n_s n_h Mult(n_h, b_w, b_a)$$

$$+ 3n_s n_h b_a^2$$

$$+ 8n_s n_h Acc(n_h, b_w, b_a). \tag{24}$$

The explanation for each line here is identical to that in (20). The NABS of the GRU is derived similarly to the LSTM case:

NABS<sub>GRU</sub> =

$$3n_s n_h [n_i(X_w + 1) - 1] \operatorname{Acc}(n_i, b_w, b_i)$$

+  $n_s n_h [3n_h(X_w + 1) + 5] \operatorname{Acc}(n_h, b_w, b_a)$

+  $6n_s n_h b_a$ . (25)

Again, the explanation for each term in this expression is identical to (21).

### F. Echo State Networks

ESN belongs to the class of recurrent layers, but more specifically, to the reservoir computing category. ESN was proposed to relax the training process while being efficient and simple to implement. The ESN comprises three layers: an input layer, a recurrent layer, known as a reservoir, and an output layer, which is the only layer that is trainable. The reservoir with random weight assignment is used to replace back-propagation in traditional NNs to reduce the computational complexity of training [100]. We notice that the reservoir of the ESNs can be implemented in two domains: digital and optical [101]. With the optical implementation of the reservoir, the computational complexity dramatically falls, however, the degradation of the performance due to the change of domain is noticeable [102]. In this work, we only examine the digital domain implementation. Moreover, we focus on the leaky-ESN, as it is believed to often outperform standard ESNs and is more flexible due to time-scale phenomena [103], [104]. The equations of the leaky-ESN for a certain time step t are given as:

$$a_t = \phi \left( W^r s_{t-1} + W^{\text{in}} x_t \right), \tag{26}$$

$$s_t = (1 - \mu)s_{t-1} + \mu a_t, \tag{27}$$

$$y_t = W^o s_t + b^o, (28)$$

where  $s_t$  represents the state of the reservoir at time t,  $W^r$  denotes the weight of the reservoir with the sparsity parameter  $s_p$ ,  $W^{in}$  is the weight matrix that shows the connection between the input layer and the hidden layer,  $\mu$  is the leaky rate,  $W^o$  denotes the trained output weight matrix, and  $y_t$  is the output vector.

The RM of an ESN is given by

$$RM_{ESN} = n_s N_r (n_i + N_r s_p + 2 + n_o), \tag{29}$$

where  $N_r$  is the number of internal hidden neuron units of the reservoir and  $n_o$  denotes the number of output neurons. From (29), the  $N_r n_i$  multiplications occur from the input vector operations, and the term  $N_r^2 s_p$  is included due to the reservoir layer; to be more specific, the latter term is multiplied with the sparsity parameter  $s_p$  which indicates the ratio of zero values

in the matrix. Eq (27) results in  $2N_r$  multiplications. Unlike the other network types, now we have to include the contribution of the output layer explicitly because it contains the trainable weight matrix, and this layer contributes  $N_r n_o$  multiplications. Eventually, the process is repeated for  $n_s$  times.

The BOP number for an ESN can be represented as:

$$\begin{aligned} \text{BOP}_{\text{ESN}} &= n_s N_r \text{Mult}(n_i, b_w, b_i) \\ &+ n_s N_r s_p \text{Mult}(N_r, b_w, b_a) \\ &+ n_s N_r \text{Mult}(n_o, b_w, b_a) \\ &+ 2n_s N_r b_a^2 \\ &+ 4n_s N_r \text{Acc}(N_r, b_w, b_a). \end{aligned} \tag{30}$$

In (30), the first term is the input vector contribution, the second one is contributed by the reservoir layer, the third term refers to the output layer multiplications, and the fourth term stems from the multiplications in (27). Eventually, all the addition operations are accounted for by the final term.

The NABS of an ESN, which can be calculated similarly as in the LSTM case in Section IV-D, is:

$$NABS_{ESN} = n_s N_r [n_i (X_w + 1) - 1] Acc(n_i, b_w, b_i)$$

$$+ n_s N_r [s_p (N_r X_w + N_r - 1] + 4) Acc(N_r, b_w, b_a)$$

$$+ n_s N_r [n_o (X_w + 1) - 1] Acc(n_o, b_w, b_a)$$

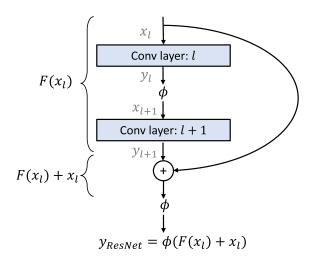

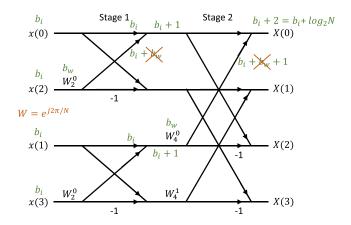

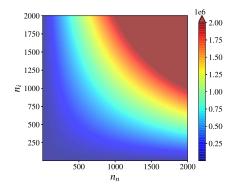

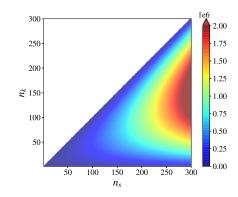

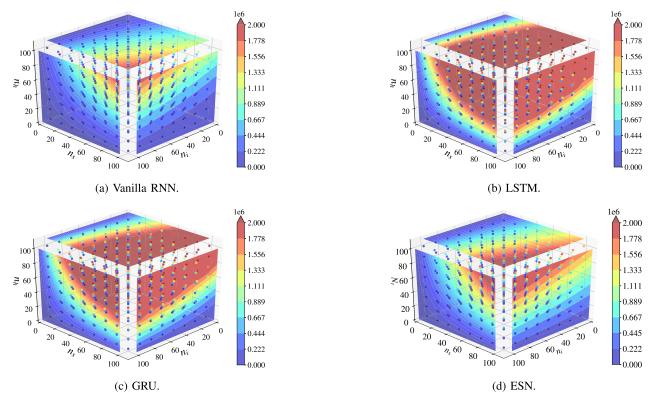

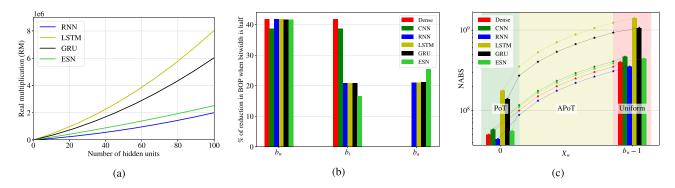

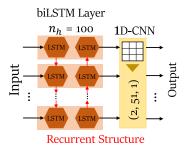

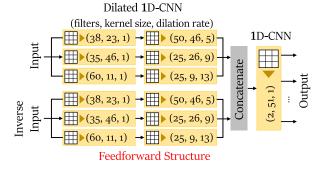

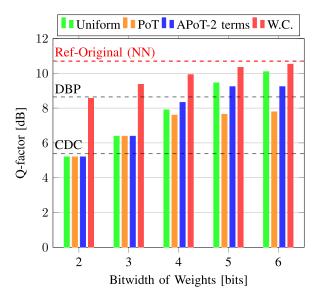

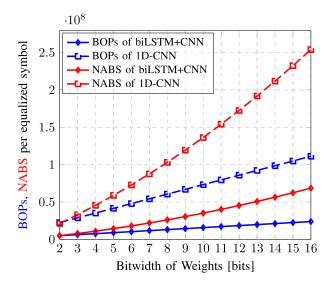

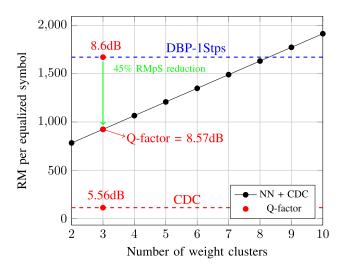

$$+ 4n_s N_r b_a.$$