Open Access

# **OE-CAM: A Hybrid Opto-Electronic Content Addressable Memory**

Volume 12, Number 2, April 2020

Yousra Alkabani Mario Miscuglio Volker J. Sorger Tarek El-Ghazawi

DOI: 10.1109/JPHOT.2020.2966748

# OE-CAM: A Hybrid Opto-Electronic Content Addressable Memory

Yousra Alkabani <sup>(1)</sup>, <sup>1,2</sup> Mario Miscuglio, <sup>1</sup> Volker J. Sorger <sup>(1)</sup>, <sup>1</sup> and Tarek El-Ghazawi

<sup>1</sup>Electrical & Computer Engineering Department, George Washington University, Washington, DC 20052 USA

<sup>2</sup>Computer Engineering Department, Halmstad University, Halmstad 30118, Sweden

DOI:10.1109/JPHOT.2020.2966748

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see http://creativecommons.org/licenses/by/4.0/

Manuscript received November 5, 2019; revised January 7, 2020; accepted January 12, 2020. Date of publication January 15, 2020; date of current version March 2, 2020. Corresponding author: Yousra Alkabani (e-mail: yousra@gwu.edu).

Abstract: A content addressable memory (CAM) is a type of memory that implements a parallel search engine at its core. A CAM takes as an input a value and outputs the address where this value is stored in case of a match. CAMs are used in a wide range of applications including networking, cashing, neuromorphic associative memories, multimedia, and data analytics. Here, we introduce a novel opto-electronic CAM (OE-CAM) utilizing the integrated silicon photonic platform. In our approach, we explore the performance of an experimental OE-CAM and verify the efficiency of the device at 25 Gbit/s while maintaining the bit integrity under noise conditions. We show that OE-CAM enables a) two orders of magnitude faster search functionality resulting in b) a five orders of magnitude lower power-delay-product compared to CAMs implementations based on other emerging technologies. This remarkable performance potential is achieved by utilizing i) a high parallelism of wavelength-division-multiplexing in the optical domain, combined with ii) 10's of GHz-fast opto-electronic components, packaged in iii) integrated photonics for 10-100's ps-short communication delays. We further verify the upper optical input power limit of this OE-CAM to be given by parasitic nonlinearities inside the silicon waveguides, and the minimal detectable optical power at the back-end photoreceiver's responsivity given channel noise. Such energy-efficient and short-delay OE-CAMs could become a key component of functional photonic-augmented ASICS, co-processors, or smart sensors.

**Index Terms:** Content addressable memory (CAM), integrated photonics, optical memory, optical lookup, microring Resonators

### 1. Introduction

A content addressable memory (CAM) is a memory with a search engine at its core used to find values stored within the CAM; upon finding a match it responds with the address where this value is stored. This search operation is usually executed within one clock-cycle because the CAM search engine is capable of searching all locations in parallel. Thus, CAMs are especially useful in different applications that demand short search-return and pattern matching. This includes networking and high-speed routing [1], [2], neuromorphic associative memories [3], multimedia and data compression [4], in addition to cashing and data analytics [5], [6].

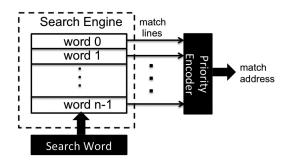

In a generic CAM a search word is applied at the input of the search engine and the search engine outputs a match line per word that signifies whether the search word is found at this location or not (Fig. 1). The output from the search engine is sent to a priority encoder that generates the

Fig. 1. Block diagram of a generic CAM.

TABLE 1

Performance of Emerging Non-Volatile Memory Technologies Based CAMs [22]

|          | SRAM  | DRAM  | PCM  | MRAM | RRAM  |

|----------|-------|-------|------|------|-------|

| read(ns) | < 0.3 | < 1   | < 60 | < 20 | < 50  |

|          | < 0.3 | < 0.5 | 60   | 20   | < 250 |

address at which the search word is found (or the first address in case of multiple matches). The search engine is composed of CAM cells that are capable of storing data and performing the match operation. A CAM cell is similar to a regular memory cell with the addition of extra logic to perform the comparisons between the stored value and the value applied at the search lines. CAMs can be classified as binary CAMs or ternary CAMs; a binary CAM cell stores either a 0 or a 1, whereas a ternary CAM cell can store 0, 1, or a don't-care. In this work, we focus on binary CAMs.

As a type of memory, CAM cells are manufactured using SRAM [7]–[12] or DRAM technology [13], [14]. While DRAM based CAMs provide larger capacities, SRAM based CAMs have seen higher adoption as they provide faster search speed, which is a priority for all applications using CAMs. However, both SRAM and DRAM technologies are facing issues due to technology scaling such as i) response-time delays mainly arising from capacitive RC-delay in electronic circuits, and ii) wasteful power dissipation. This prompts exploring the use of novel technology options to design and implement CAMs. For instance, multiple CAM designs were introduced using emerging non-volatile memory such as Phase Change Memories (PCM) [15]–[17], Spin-Transfer Torque Magneto-resistive Random Access Memories (STT-MRAMs) [18]–[20], and memristors [21]–[24], to name a few (Table 1). These novel technology options provide the promise of highly scalable and energy-efficient memory functionality, while maintaining acceptable read and write speeds.

A CAM read and write delay comparison of representative technology options including SRAM, DRAM, PCM, MRAM, and resistive memories (RRAM) shows almost 2-orders of magnitude variability (Table 1); in detail, SRAM is (on average) 10x faster compared to all other CAM options, while writes of emerging memory technologies are typically slower and more power-hungry. Note, that in most CAM applications, writes are less frequent than searches, thus, the read speed is of higher importance than the write speed. In addition to speed, other CAM performance metrics include energy efficiency and the chip-footprint (component integration) density. With high search speed in mind, integrated photonics can be a compelling technology option to implement a CAM, as we discuss and show in this work. Exemplary, a fully optical CAM that can operate at 10 Gb/s was recently introduced [25], [26], whose design mimics an optical equivalent of a SRAM CAM cell. However, such early attempts of brute-force mapping optical components onto SRAM functionality may not enable the most efficient nor high-performance CAMs. As it stands, the demand for an efficient and low-latency CAM that exploits trusted silicon foundry processes is yet outstanding, and the main rational for our work presented here. Here we introduce a novel opto-electronic CAM design (OE-CAM) that synergistically maps function to technology for the first time. That is, we utilize electronics for the low-speed writes, while performing the reads optically at high-speed.

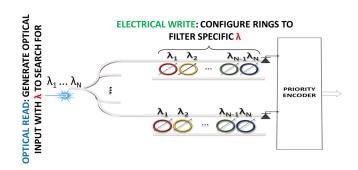

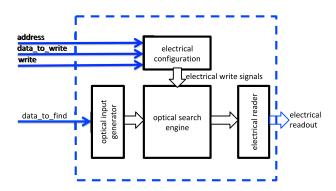

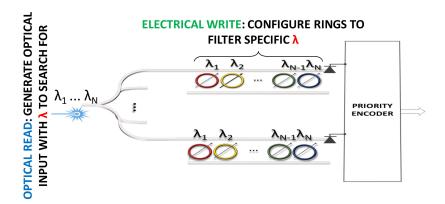

Fig. 2. Overview of the proposed opto-electronic CAM (OE-CAM).

This setting enables satisfying the need of a CAM design to perform both high-speed searches, while allowing for a footprint compact optical CAM cell requiring a low power budget.

While integrated photonics promises superior performance and better power efficiency improvements when compared to other CAM implementation options, the photonics generally shows a higher chip footprint per unit functionality. However, the recently instigated photonic-integrated circuit roadmap anticipates improvement similar to the ITRS, thus technology-scaling and economy-of-scale are expected to enable significant improvements in years to come. The main rationale behind this OE-CAM design presented here is, that a) optics allow for massive data-processing parallelism due to wavelength-division-multiplexing (WDM), and b) the system's read-response is simply given by the time-of-flight of a photon through the OE-CAM structure; hence, given the compactness of integrated photonics, the read delay is just picoseconds (ps)-short, signifying a 10–100x improvement over electronic-only CAM counterparts.

Figure 2 presents an overview of the proposed OE-CAM; the core of the OE-CAM is an optical search engine that operates at high-speed, where the only delays are given by the optoelectronic device response times (10's GHz-fast) during write operation, and ps-short read delays from the photons time-of-flight. In detail, the search values are stored within the optical search engine by electrically reconfiguring the photonic components (namely microring resonators, MRR, see Sections 3 and 4). This is done by placing the to-be-written word (in binary format) on the data to write lines, placing the location to store the word on the address line, then raising the write signal. The search word is input electrically to the system using the data to find line, which is then generated optically at the input of the optical search engine using laser light. The output of the optical search engine represents the match lines for all the locations, which are converted into electrical signals using photodetectors and whose output is fed to an electrical priority encoder to generate the match address. Incidentally, a practical advantage of this OE-CAM design is its ability to become seamlessly integrated in a standard electrical systems (i.e, plug-in module). However, one could integrate and use OE-CAM also in a photonic integrated circuit architecture by replacing the back-end components (photodetector and electrical decoder) with an optical waveguide-based encoder [27]. In this paper, we focus on the design and evaluation of the optical search engine of OE-CAM.

The remainder of the paper is organized as follows; Section 2, discusses related work. The OE-CAM cell and system design of the OE-CAM search engine are presented in Sections 3 and 4. The new design is evaluated in Section 5. Section 6 concludes the work.

### 2. Related Work

CAMs can be classified as binary and ternary CAMs; a cell of a binary CAM can store either a 0 or a 1, whereas a cell of a ternary CAM can store 0, 1, or don't-care. In this work, we focus on binary CAMs. Traditionally CAM cells are implemented using regular SRAM cells in addition to

matching logic. Two main topologies of SRAM based CAMs are used: NAND and NOR [7]. While the NAND implementation consumes less power than the NOR implementation, its delay increases quadratically with the word size due to capacitive delay limitations [7].

A hybrid design combining the advantages of both the NOR and NAND implementations was proposed by Chang and Liao [8]. Other architectural techniques were proposed to reduce the power consumption and improve the throughput of SRAM based CAM cells using precomputations and overlapped search mechanisms [9]–[12]. Moreover, high-density CAMs with DRAM based cells were proposed, but these CAMs are slower than SRAM CAMs and are thus less attractive [13], [14].

As technology scales, SRAM technology suffers from increased energy consumption due to high leakage currents. Thus, it is essential to study different implementations of CAMs using technological alternatives. Multiple CAM implementations using non-volatile memory technologies were recently proposed, including PCM [15]–[17], STT-MRAMs [18]–[20], and memristors [21]–[24]. While those options promise high scalability, they are all at least one order of magnitude slower compared to SRAM-based CAMs and require rather large write energies [22].

In contrast, here we deploy a promising technology harnessing a variety of benefits found in integrated photonics. Mourgias-Alexandris et al. recently introduced an all-optical CAM that supports read and write operations at up to 10 Gbps [25], [26] and a T-CAM based on a similar design was also introduced [28], [29]. Their implementation uses optical components to replicate a traditional SRAM CAM cell and it is based on an optical flip-flop (FF) and an optical XOR gate. At each cell, the FF, responsible for storing the bit, requires two coupled Semiconductor Optical Amplifier-Mach Zehnder interferometer (SOA-MZI) switches in a master-slave configuration that are interconnected through a 5 mm-long waveguide. In addition, the output is connected to the lower branch of an MZI which constitutes the XOR gate, comprising two SOA. While being an intriguing concept, in its current implementation, the hardware overhead is rather high. In contrast, our OE-CAM cells are smaller in size than this implementation and do not require any internal light sources. In fact, our OE-CAM cell is composed of one single ring resonator which makes our cell an order of magnitude more compact than the previous optical implementation. Moreover, OE-CAM is fully compatible with the CMOS technology [30], and if needed can be easily integrated within fully electrical systems. Other possible modulator options that can be explored as an alternative to micro ring resonators are Mach-Zehnder modulators [31] that can have efficient attojoule implementations [32].

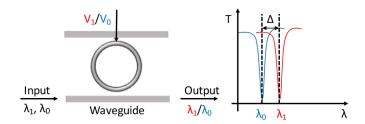

# 3. Cell Structure

An OE-CAM cell is composed of one silicon based micro-ring resonator (MRR), a component that has gained foundry maturity and as such has been widely described in text books and research papers [33], since they provide a fundamentally important function utilized in several applications ranging from spectral filtering in optical links based on Wavelength Division Multiplexing (WDM) [34], [35] to sensors [36]. To summarize their working principle, when a bus waveguide is coupled to a microring resonator, by means of codirectional evanescent coupling, its transmission spectrum shows a dip near the ring's spectral resonances (Fig. 3). Here, the waves in the ring build up a round-trip phase shift that equals an integer times  $2\pi$ , and thus interfere constructively. The resonance property can be used as a spectral selectivity provided by the MRR element and is a function of the optical losses (a) and coupling coefficient (r) (waveguide bus-to-ring), which determines the full width half maximum ( $FWHM = \frac{(1-ra)\lambda_{\text{res}}^2}{\pi n_g L \sqrt{ra}}$ ) and Free spectral range ( $FSR = \lambda^2/(n_g L)$ ) of the ring spectrum, setting ring quality factor ( $Q = FWHM/\lambda_{\text{res}} =$ ) and finesse (Finesse = FSR/FWHM). These parameters become determinant for avoiding (spectral) signal cross-talk among neighboring OE-CAM cells since multiple wavelengths are used to express input bits (see below for detailed operation principles).

Moreover, the microrings can be electrically or thermally actuated and therefore act as spectral switches similar to analog modulators. The temperature actuation, however, is rather slow (in  $\mu$ s

Fig. 3. Cell structure of the CAM. The voltage-controlled read/write operation shifts the MRR resonance which can be cross-references with optical power received by a single back-end photodetector.

TABLE 2 State-of-the-Art Silicon Modulators Based on Micro-Ring Resonators,  $^*$  [39] is Related to ER Measured in Static Condition, Linear Operation Region of 6 dB ER Are Guaranteed Between  $\pm 3.5$  V

| Material                           | Device<br>type                               | IL<br>[dB]   | Footprint $[\mu \mathbf{m}^2]$ | Speed<br>[Gbit/s] | Energy<br>[fJ/bit] | Dynamic ER<br>[dB] |

|------------------------------------|----------------------------------------------|--------------|--------------------------------|-------------------|--------------------|--------------------|

| Graphene-Ring [40]                 | MRR - Loss modulation                        | Ring<br>dep. | 1600                           | 30                | 800                | 3                  |

| Silicon [41]                       | Racetrack - carrier depletion                | -            | 1000                           | 12.5              | 44000              | 1                  |

| Si- pn junction [30]               | MRR - carrier injection                      | -            | 25                             | 12.5              | 8                  | 9                  |

| Si- pn junction [42]               | MRR - carrier depletion                      | -            | 100                            | 19                | -                  | -                  |

| Si [37] interdigitated pn junction | MRR - carrier depletion                      | 1            | 2500                           | 10                | 287                | 4                  |

| Si [38] pn junction                | MRR - carrier depletion                      | 2            | 1000                           | 11                | 50                 | 6.5                |

| Si pn [43]<br>(IMEC)               | MRR - carrier depletion                      | 3            | 100                            | 56                | 45                 | 4                  |

| Si-Thermal [44]                    | MRR - carrier depletion<br>thermally tunable | 3            | 100                            | 40                | 80                 | 7                  |

| Si Vertical pn junction [45]       | MRR - carrier depletion                      | 1            | 25                             | 25                | 4.25               | 6                  |

| Plasmonic [39]                     | Plasmonic-MRR                                | 2.5          | 100                            | 72                | 12                 | 10 (static*)       |

scale), while the modulation of portion of the refractive index or the absorption of silicon is influenced by the actual concentration of electrons and holes (i.e. plasma dispersion). The most used MRR modulators, at the foundry and industrial level, therefore include a p-i-n junction that is side coupled to a wave guide as described in [30] or a p-n junction [37]. While carrier injection-based MRR modulators and tunable filters feature high carrier concentrations, their response speed is limited due to long carriers lifetimes (in *ns* scale). In contrast, depletion-based devices are faster (non limited by the free carrier lifetime), but the signal modulation-depth (i.e. extinction ratio) is typically less pronounced, therefore, the overlap between the optical guided mode and the depletion region has to be maximized. Applying a bias voltage  $V_0$  to these MRRs, the transmission spectrum (T) of the ring has a resonant frequency  $\lambda_0$ . When light passes through the coupled waveguide, the component with wavelength  $\lambda_0$  is coupled into the ring. By raising the bias voltage to  $V_1$ , the resonant frequency shifts to  $\lambda_1$  due to the change in the refractive index of the ring, due to either carrier injection or depletion. The difference between  $V_0$  and  $V_1$  controls the difference between  $\lambda_0$  and  $\lambda_1$  ( $\Delta$ ).

Another major reason to exploit MRRs is the low energy expended in producing each bit of data, which could be particularly low in the order of few fJ·bit<sup>-1</sup>[38], [39] while electronics interconnects usually require 23 pJ·bit<sup>-1</sup>. Table 2 reports the state of the art of silicon modulators based on MRRs. As previously mentioned ring-resonators, based on pn-junctions in reverse bias, provide the best performances in terms of extinction ratio, insertion loss, (reconfiguration, i.e. write) speed and energy consumption along with a relatively compact footprint. In the view of the design of the proposed OE-CAM unit cell, the quality factor of the ring and its free spectral range need to be carefully engineered to match the total number of channels (wavelengths) available, i.e. number of bits which compose a word, and the working spectrum in order to avoid inter-channel crosstalk.

Fig. 4. Resonance wavelength at different locations.

Fig. 3 shows the details of an OE-CAM cell and how it can be triggered directly as a lumped element.

Another aspect to take into consideration is the repeatability and consistency of the process used for fabricating the microring-based electro-optic modulators (EOM). Therefore, EOMs based on active materials which require unique integration techniques, not compatible with CMOS processes, are overlooked. Nevertheless, using foundry available Si microring modulators based pn junction and carrier depletion, it is possible to achieve at least 3 dB modulation range at high speed (> 25 GHz), low energy consumption (< 50 fJ/bit) compact footprint and contained insertion losses. Plasmonic ring modulators are also ignored due to their lower quality factor which would lead to cross talk penalty. Our OE-CAM cell uses electrical writes and optical reads; to write a 0, we apply a bias voltage of  $V_0$  and to write a 1 we change the bias voltage to  $V_1$ . To detect which value is stored in the cell, we send spectrally different input light signals with  $\lambda_i$ where  $i \in \{0, 1\}$  into the MRR-based photonic circuit. Now, if no light is detected at the output of the waveguide (i.e. the optical power exciting the optical search engine is below the detector's threshold), then the value i is stored in this cell. Thus, a photodetector can be added at the end of the waveguide to detect a matching value. However, as will be seen in Section 4, we only need one photodetector per OE-CAM entry and thus, the photodetector is not considered as part of the cell.

### 4. OE-CAM Structure

In this section, we first discuss how OE-CAM cells are combined to construct the optical search engine, followed by showing how multiple OE-CAM search engines can be combined to enable cascadability for constructing larger and parallel-operating search engines.

### 4.1 Construction of OE-CAM Optical Search Engine

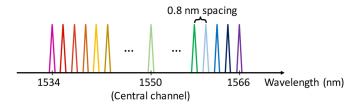

To construct an n-bit OE-CAM entry, we need n MRR rings; ring j can be biased to either resonance wavelength  $\lambda_{0j}$  or  $\lambda_{1j}$ . Those resonance wavelengths are spectrally unique (Fig. 4). As previously discussed, the practical word size n is limited by the spectral bandwidth available to tune the ring resonators and the resolution by which we can divide this spectrum.

The micro-ring resonators are coupled in series to a waveguide constituting the OE-CAM's entry (row), where each entry is terminated by a photodetector, whose output is connected to a priority encoder (Fig. 5).

To store a word in an OE-CAM entry, we apply the proper bias voltage to each cell. For example, if we want to store the word 011....0, we tune the cells to have resonance frequencies of  $\lambda_{00}, \lambda_{11}, \lambda_{12},....,\lambda_{0(n-1)}$ , respectively. To test whether a word is stored in a specific location or not, we apply light with the corresponding bit-position wavelength components; if no light emerges at the end of that entry's waveguide, then a match is found.

To search for a word, input light composed of those resonance frequencies corresponding to the bits of the word is generated, and send to the MRR filter banks (Fig. 5). The input light will be filtered out only if there is a match. For example to search for the pattern 0101, the input light

Fig. 5. OE-CAM search engine design.

Fig. 6. Combining two optical search engines to construct a wider word search engine.

should include the following wavelengths:  $\lambda_{00}$ ,  $\lambda_{11}$ ,  $\lambda_{02}$ , and  $\lambda_{13}$ . Although this is a design of a binary CAM, we can search for a don't-care (x) at a specific position by eliminating the light components representing the resonance frequencies of this bit position. Thus, if we want to search for 0X01, the input should be  $\lambda_{00}$ ,  $\lambda_{02}$ , and  $\lambda_{13}$ .

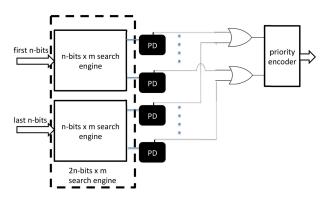

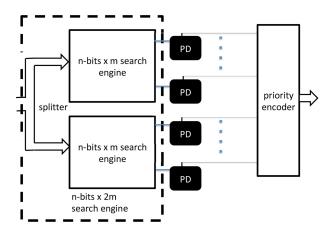

### 4.2 Design Cascadability: Construction of Larger OE-CAM Search Engines

Two OE-CAM optical search engines can be combined horizontally to construct an optical search engine to handle larger word sizes as shown in Fig. 6. In this case, the outputs from the photode-tector at each entry in the first optical search engine, is combined with the corresponding output in the second optical search engine using an OR-gate. The OR-gate output is then fed to the priority encoder. In this case the read-delay will be increased by a delay equivalent to the delay of a 2-input OR-gate, when compared to an optical search engine that is directly manufactured to be the exact size. Moreover, for search words that are longer than the physical number of MRRs, two optical search engines can be combined vertically to increase the number of entries (Fig. 7). In this case a waveguide splitter (1:N fan-out) is inserted at the input in order to pass the input light to all modules and a large encoder is also needed to accommodate the outputs of the photodetectors in both modules. Here the write and read-delays do not increase (assuming the same number of MRRs per row), thus, the OE-CAM is both wavelength and time-parallelized, and multiple optical search engines can be combined vertically and horizontally to construct optical search engines of any size.

Fig. 7. Combining two optical search engines to construct a search engine with more entries.

TABLE 3

Non-Exhaustive State-of-the-Art Graphene, Germanium, and III-V Integrated Photodetectors on Silicon. Plasmonics, Metal Semiconductor Metal, p-i-n Junction in Reverse Bias, and InP-Based Modified Uni-Traveling Carrier (MUTC) Are Considered

| Material               | Device<br>type | Responsivity<br>[A/W] | Dark Current<br>[μΑ] (Bias (V)) | Speed<br>[GHz] | NEP $[pW/\sqrt{Hz}]$ | Footprint $[\mu m^2]$ |

|------------------------|----------------|-----------------------|---------------------------------|----------------|----------------------|-----------------------|

| Germanium<br>[47]      | Plasmonic      | 0.5                   | 20 (-1)                         | 110            | 1-5                  | $0.160 \times 10$     |

| Graphene<br>[48]       | Plasmonic      | 0.5                   | 4000 (0.4)                      | 110            | -                    | 6×1                   |

| Germanium<br>[49]      | MSM            | >0.4                  | 4 (5)                           | 50             | -                    | $2 \times 30$         |

| Germanium<br>[50]      | MSM            | >0.4                  | 0.1 (1)                         | 45             | < 1                  | 2 × 10                |

| Germanium<br>[51]      | MSM            | 0.1                   | 86 (1)                          | 40             | -                    | 0.7×20                |

| Germanium<br>[52]      | p-i-n          | 1                     | 0.1 (-2 V)                      | 31             | ≈1                   | 4×100                 |

| Germanium<br>IMEC [53] | p-i-n          | 0.7                   | <0.04(-1)                       | >56            | ≈0.01                | 0.5 × 14              |

| Germanium<br>[54]      | p-i-n          | 0.8                   | 0.003 (-1 V)                    | 45             | 0.04                 | 5.3×8                 |

| GalnAsSb<br>[55]       | p-i-n          | 0.4                   | 1.1 (-1 V)                      | -              | 1.5                  | 60×60                 |

| Germanium<br>[56]      | p-i-n          | 0.8                   | 4 (-1)                          | 120            | < 3                  | 10 × 10               |

| Germanium<br>[57]      | MSM            | 1                     | 300 (5 V)                       | 25             | -                    | 10×3.5                |

| InP<br>[58]            | MUTC           | 0.9                   | 0.01 (-5V)                      | 48             | -                    | 20×3.5                |

# 5. Evaluation

The read-speed of the proposed design is limited by the time-of-flight of the photon in the photonic integrated circuit and the response-time of the photodetector. Current integrated photodetector technologies can reach up to 50 GHz speed, with a responsivity of at least 0.6 A/W and a noise equivalent power (NEP) of 1 pW/ $\sqrt{Hz}$  operating in reverse bias (-1 V), as shown in Table 3. The speed of the detector is constrained by the maximum physical length of the device, thus the number of bits of the CAM. Incidentally, similar arguments were made by Tait *et al.* [46] when discussing MRR-based weight banks for photonic integrated neural network. The length of the OE-CAM is therefore constrained by the pitch of the MRR, where an indicative estimation of the total length I

can be obtained via:

$$I = Pitch_{MRR} \times N_{bit} + I_{Spliter}$$

(1)

where  $l_{\text{Splitter}} = 500 \ \mu\text{m}$  and the Pitch<sub>MRR</sub> is 25  $\mu$ m. The corresponding time-of-flight of the photon t is:

$$t = 1.6 \text{ ps} + 0.08 \text{ ps} \times N_{\text{bit}}$$

(2)

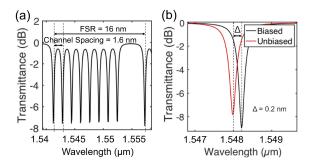

In order to respect the maximum reading speed of 50 GHz, imposed by the detector, reversing the equation (2), we derive the upper-bound of the number of bits, N<sub>bit</sub>, to be 230 bits, which in our case corresponds to the number of wavelengths. Nevertheless, the number of channels can not be arbitrary chosen, but it has to respect the total bandwidth available for the WDM modulation and the corresponding spacing between channels (i.e. different wavelengths) is crucial for ensuring signal integrity. Therefore, our system is designed to exploit Dense-WDM with 40 channels (Fig. 4), leading to a spacing amongst the channels of 0.8 nm, which sets the total number of bits. This is achievable due to strong optical confinement of silicon waveguides using microring resonators with more than 50 nm Free Spectral Range (FSR) with Quality factors (Q) close to 10<sup>4</sup>, which allow as many as 50 channels [49], [59]. Assuming approximately 0.8 nm channel spacing, the resonance bandwidth can be broadened up to 0.4 nm, while maintaining an estimated crosstalk level of -10 dB. [49] In this reverse engineering approach, we use the NEP of the detector as reference for estimating the required laser input power and thus the total number of entries (words). Selecting a conservative NEP of 1pW/ $\sqrt{Hz}$ , we indeed find a detectable (SNR = 1) threshold at 50 GHz of 223 nW for each individual channel. Assuming the total number of entries (K), the total power needed to be provided to the OE-CAM can then be computed as:

$$P = K \times P_{\text{Channel}} \times N \tag{3}$$

For avoiding all-optical nonlinearities in the Silicon waveguide platform (e.g. two photon absorption), we consider a conservative 10 mW as the maximum optical power running through the system, thus obtaining the total number of entries, *K* to be 1121. To summarize, an OE-CAM performing reads at 50 GHz could support up to 40 bits using D-WDM and about 1100 entries, ensuring signal integrity maintaining a cross talk level below -10 dB, is realistic requiring a chip footprint of about 28 mm<sup>2</sup>.

$$Area = N \times K \times Area_{MRR} \tag{4}$$

Regarding the write-speed, diverse technologies and implementations display different performances and modulation efficiency. Even though a detailed discussion is out of the scope of this work, here, we provide a reasonable working range; the write-speed limiting factor in our design is given by the speed at which the refractive index variation occurs in the MRR-based modulators, because of the injection/depletion of carriers, which is used to tune the refractive index. This mechanism is not limited by the recombination times of the generated carriers, but rather by the capacitance of the junction hampered by capacitive effects, that can be minimized at the device engineering stage. It is worth mentioning that capacitive effects can be also used as retention mechanism at the expense of writing speed. Current silicon-based MRR modulators [42], [60] exhibit a speed up to 30 GHz, with a driving voltage of usually few Volts (1-2 V) and an efficiency  $(V\pi I)$  of few tenths of V·cm. Experimental results that corroborate our estimation are reported in [38], where Silicon-based electro-optic MRRs exhibit a modulation in a working spectrum of 0.1 nm and a speed of 11 GHz and as low as 2 dB insertion losses. According to our assumptions on the detection bandwidth and modulation efficiency, Table 4 summarizes the design parameters of an OE-CAM primarily based on a series of MRRs using the above discussed values from experimental device demonstrations.

Table 5 shows a comparison of the search power delay product (PDP) of optimized CAM cells based on CMOS, PCM, Magnetic Tunnel Junctions (MTJ), and memristors reported in [17] and our OE-CAM cell. This product is a figure of merit which symbolizes the energy efficiency of the logic mechanism and it is computed as the product between the switching delay (1/50 GHz) and the power required. Our OE-CAM achieves a PDP of just 4.5aJ which is an impressive five orders of

TABLE 4

Characteristics of OE-CAM

| Parameter                       | OE-CAM        |

|---------------------------------|---------------|

|                                 | '             |

| cell Elements                   | MRR           |

| Read time (ns)                  | 0.02          |

| Write time (ns)                 | 0.03          |

| Write energy (fJ/bit)           | 100-200       |

| Density (kbit/cm <sup>2</sup> ) | 160           |

| Operating Voltage               | $\approx -2V$ |

TABLE 5

Comparison of the Search Power Delay Product [17]

| CAM      | CMOS        | PCM    | MTJ    | Memristors | OE-CAM |

|----------|-------------|--------|--------|------------|--------|

| PDP (f.) | J)   14.129 | 36.430 | 52.367 | 15.448     | 0.004  |

Fig. 8. Hierarchical schematic of a 8-bit OE-CAM. Writing and reading emulation.

magnitude savings in search PDP over other technologies. However, thermal interactions between on-chip heat-sources and ring resonators can limit this number, as the micro-ring resonators are extremely sensitive to temperature-induced changes in refractive index. In order to mitigate this effect two main strategies could be considered: (1) Computer aided resonance locking [61]; (2) Thermal-aware Integration strategies [62]. Even if the latter still enables high-speed modulation it requires a great deal of additional power, therefore we believe that integration strategies aiming to minimize cross-talk and thermal effect, using for instance thermal polymers [63] would give a pathway for a high speed modulation using ring resonators without trading off energy consumption.

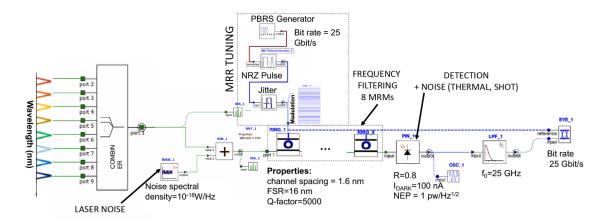

We now focus on the simulation of the architecture and its performance. The software used in this analysis is Lumerical Interconnect. We emulate the read- and write-mechanism for one entry of 8 bit. This is intended to be purely illustrative, since the results could be extended to the previously discussed case of a more populated bandwidth. The emulated architecture is represented in Fig. 8. At the input, we minimize the crosstalk penalty by considering individual sources spaced by 1.6 nm (WDM). The first MRR is modulated by a a pseudo-random bit sequence (PRBS) generator at 25 GHz, which codes a sequence of non-return to zero (NRZ) pulses. The quality-factor of the rings is considered to be 5000, which is practical at the foundry level, with an FSR of 16 nm, and an operating voltage of 0.5 to -1 V that translates to proportional frequency shifts [53]. Additionally, a noise spectral density ( $10^{-18}$ W/Hz) is added to the laser sources. The ring resonator

Fig. 9. (a) Transmitted optical power spectrum indicating the ring FSR of 16 nm and channel spacing of 1.6 nm. (b) Transmitted power versus wavelength for biased and unbiased ring modulator.

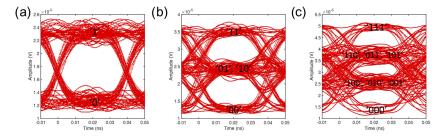

Fig. 10. Output eye diagrams of the EO-CAM for 25 Gbit/s modulation rates of silicon microring modulators (for 1 (a), 2 (b) and 3 (c) MRRs) with a Q-factor of 5000 and 1.6 nm spacing between channels.

(RING\_1) resonant frequency is 193.45 THz (1550.8 nm). The modulation mimics writing in the CAM. (Fig. 9)

In a first iteration, the other rings instead behave as passive Bessel-like filters. A jitter source is added to the digital signal which modulates the MRR, to model the short-term variations of the phase. A photodetector converts the analog optical signal into electrical, which is filtered and used as input of bit-error-rate (BER) using as reference the modulation signal (Fig. 10(a)). The detector is considered to be affected by both Thermal (300 K) and shot noise (1 pW/ $\sqrt{Hz}$ ). The eye diagram curves confirm the signal integrity at 25 Gb/s in writing/reading operations. The pattern highlights a width of 35 ps and 1 ps time variation of the zero crossing. For just one ring modulated on or off corresponds a Bit error rate (BER) of  $4.4 \times 10^{-9}$ .

The uncertainty that limits our device scheme is strictly related to the channel bandwidth, in other words, the crosstalk. As reported by Jayatilleka *et al.* [64], based on experimental results in photonic integrated circuit, low inter-channel and intra-channel crosstalk power penalties are demonstrated for MRR filters for data rates up to 20 Gb/s, in this range of proximity [64]. Although, a higher order MRR filter allows reducing concurrent inter-channel and the intra-channel crosstalk, it introduces drawbacks in terms of footprint and power required for the modulation.

Ultimately, we also modulate at the same time 2 MRRs (Fig. 10(b)) and 3 MRRs (Fig. 10(c)), controlled by different pseudo-random bit sequences. Similarly to a PAM modulation, the different levels are still distinguishable, highlighting the robustness of the network. Interestingly, when the resonances of the rings are perfectly aligned to the input wavelengths and concomitantly assuming conservative values of electrical noise at the input, as well as phase jitter, all the bit permutations (such as '01' and '10') fall on the same state 10b, c. Although, in a real platform implementations, minute fabrication differences can lead to splitting of the permutation states. For low level of noise and cross-talk one can engineer the resonances to discriminate between multiple state arising by the above-mentioned systematic error or by modulation of side wavelengths, with just one adjacent

channel, and central wavelengths with 2 adjacent channels for obtaining more information of a partial match.

### 6. Conclusion

In this work we have introduced a novel opto-electronic CAM (OE-CAM) with an optical search engine at its core. OE-CAM uses electrical writes to store values in the optical search engine by tuning microring resonators, and achieves high-speed optical search. Our design enables search speeds that are on average 100x faster than CAMs implemented using other emerging technologies. Moreover, it has a search PDP that is five orders of magnitude less than other CAMs. We have verified this performance by simulating an 8-bits OE-CAM using Lumerical Interconnect and verified the efficiency of the device at 25 Gbit/s while maintaining the bit integrity under photodetector noise and cross-talk conditions. This high performance opto-electronic search engine using integrated photonics is enabled by a high-degree of parallelism by utilizing wavelength-division-multiplexing, short photon delays inside this relatively compact design, and 10's GHz-fast response times of modern opto-electronic components. Such hybrid search engines are therefore promising candidates for future heterogeneous photonic-electronic integrated circuits.

### References

- [1] D. E. Taylor, "Survey and taxonomy of packet classification techniques," ACM Comput. Surv., vol. 37, no. 3, pp. 238-275, 2005.

- [2] W. Li, X. Li, and H. Li, "MEET-IP: Memory and energy efficient TCAM-based IP lookup," in Proc. IEEE 26th Int. Conf. Comput. Commun. Netw., 2017, pp. 1–8.

- [3] S. Moradi, N. Qiao, F. Stefanini, and G. Indiveri, "A scalable multicore architecture with heterogeneous memory structures for dynamic neuromorphic asynchronous processors (DYNAPs)," IEEE Trans. Biomed. Circuits Syst., vol. 12, no. 1, pp. 106-122, Feb. 2018.

- [4] K.-J. Lin and C.-W. Wu, "A low-power CAM design for LZ data compression," IEEE Trans. Comput., vol. 49, no. 10, pp. 1139-1145, Oct. 2000.

- [5] J. P. Wade and C. G. Sodini, "A ternary content addressable search engine," IEEE J. Solid-State Circuits, vol. 24, no. 4, pp. 1003-1013, Aug. 1989.

- [6] R. Karam, R. Puri, S. Ghosh, and S. Bhunia, "Emerging trends in design and applications of memory-based computing and content-addressable memories," Proc. IEEE, vol. 103, no. 8, pp. 1311-1330, Aug. 2015.

- [7] K. Pagiamtzis and A. Sheikholeslami, "Content-addressable memory (CAM) circuits and architectures: A tutorial and survey," IEEE J. Solid-State Circuits, vol. 41, no. 3, pp. 712-727, Apr. 2006.

- [8] Y. J. Chang and Y. H. Liao, "Hybrid-type CAM design for both power and performance efficiency," IEEE Trans. Very Large Scale Integration Syst., vol. 16, no. 8, pp. 965–974, Aug. 2008.

- [9] C.-S. Lin, J.-C. Chang, and B.-D. Liu, "A low-power precomputation-based fully parallel content-addressable memory," IEEE J. Solid-State Circuits, vol. 38, no. 4, pp. 654-662, Apr. 2003.

- [10] N. Onizawa, S. Matsunaga, V. C. Gaudet, and T. Hanyu, "High-throughput low-energy content-addressable memory based on self-timed overlapped search mechanism," in Proc. 18th IEEE Int. Symp. Asynchronous Circuits Syst., 2012, pp. 41-48.

- [11] N. Onizawa, S. Matsunaga, V. C. Gaudet, W. J. Gross, and T. Hanyu, "High-throughput CAM based on a synchronous overlapped search scheme," IEICE Electron. Exp., vol. 10, no. 7, pp. 20 130 148-20 130 148, 2013.

- [12] N. Onizawa, S. Matsunaga, V. C. Gaudet, W. J. Gross, and T. Hanyu, "High-throughput low-energy self-timed CAM based on reordered overlapped search mechanism," IEEE Trans. Circuits Syst. I: Regular Papers, vol. 61, no. 3, pp. 865-876, Mar. 2014.

- [13] V. Lines et al., "66 MHZ 2.3 M ternary dynamic content addressable memory," in Proc. IEEE Memory Technol., Des. Testing, Records Int. Workshop, 2000, pp. 101–105.

- [14] H. Noda et al., "A cost-efficient high-performance dynamic TCAM with pipelined hierarchical searching and shift redundancy architecture," IEEE J. Solid-State Circuits, vol. 40, no. 1, pp. 245-253, Jan. 2005.

- [15] B. Rajendran et al., "Demonstration of CAM and TCAM using phase change devices," in Proc. 3rd IEEE Int. Memory Workshop, 2011, pp. 1-4.

- [16] Q. Guo, X. Guo, Y. Bai, and E. Ipek, "A resistive TCAM accelerator for data-intensive computing," in Proc. 44th Annu. IEEE/ACM Int. Symp. Microarchi., 2011, pp. 339-350.

- [17] P. Junsangsri, J. Han, and F. Lombardi, "Design and comparative evaluation of a PCM-based CAM (content addressable memory) cell," IEEE Trans. Nanotechnol., vol. 16, no. 2, pp. 359-363, Mar. 2017.

- [18] S. Matsunaga et al., "Standby-power-free compact ternary content-addressable memory cell chip using magnetic tunnel junction devices," *Appl. Phys. Exp.*, vol. 2, no. 2, 2009, Art no. 023004. [19] W. Xu, T. Zhang, and Y. Chen, "Design of spin-torque transfer magnetoresistive RAM and CAM/TCAM with high

- sensing and search speed," IEEE Trans. Very Large Scale Integration Syst., vol. 18, no. 1, pp. 66-74, Jan. 2010.

- [20] S. Matsunaga et al., "Fully parallel 6T-2MTJ nonvolatile TCAM with single-transistor-based self match-line discharge control," in Proc. IEEE Symp. VLSI Circuits, 2011, pp. 298–299.

- [21] F. Alibart, T. Sherwood, and D. B. Strukov, "Hybrid CMOS/nanodevice circuits for high throughput pattern matching applications," in Proc. IEEE NASA/ESA Conf. Adaptive Hardware Syst., 2011, pp. 279–286.

- [22] K. Eshraghian, K.-R. Cho, O. Kavehei, S.-K. Kang, D. Abbott, and S.-M. S. Kang, "Memristor MOS content addressable memory (MCAM): Hybrid architecture for future high performance search engines," *IEEE Trans. Very Large Scale Integration Syst.*, vol. 19, no. 8, pp. 1407–1417, Aug. 2011.

- [23] M. İmani, S. Patil, and T. Š. Rosing, "Approximate computing using multiple-access single-charge associative memory," *IEEE Trans. Emerging Topics Comput.*, vol. 6, no. 3, pp. 305–316, Jul.-Sep. 2018.

- [24] X. Wang, Y. Yang, and M. Shang, "A novel content addressable memory based on hybrid memristor-CMOS architecture," in *Proc. IEEE 37th Chin. Control Conf.*, 2018, pp. 8502–8506.

- [25] G. Mourgias-Alexandris, C. Vagionas, A. Tsakyridis, P. Maniotis, and N. Pleros, "Optical content addressable memory matchline for 2-bit address look-up at 10 Gb/s," *IEEE Photon. Technol. Lett.*, vol. 30, no. 9, pp. 809–812, May 2018.

- [26] G. Mourgias-Alexandris, C. Vagionas, A. Tsakyridis, P. Maniotis, and N. Pleros, "A 10 Gb/s all-optical match-line for optical content addressable memory (CAM) rows," in *Proc. Opt. Fiber Commun. Conf., Optical Society of Amer.*, 2018, pp. W2A–39.

- [27] S. Sun *et al.*, "Hybrid photonic-plasmonic nonblocking broadband 5 × 5 router for optical networks," *IEEE Photon. J.*, vol. 10, no. 2, pp. 1–12, Nov. 2017.

- [28] P. Maniotis and N. Pleros, "All-optical ternary-content addressable memory (T-CAM) cell and row architectures for address lookup at 20 Gb/s," Opt. Quantum Electron., vol. 49, no. 11, 2017, Art no. 348.

- [29] G. Mourgias-Alexandris, C. Vagionas, A. Tsakyridis, P. Maniotis, and N. Pleros, "All-optical ternary content addressable memory (T-CAM) cell for ultra-fast address look-ups in router applications," in CLEO: Science and Innovations. Optical Society of Amer., May 2018, pp. STh3B-7.

- [30] Q. Xu, S. Manipatruni, B. Schmidt, J. Shakya, and M. Lipson, "12.5 gbit/s carrier-injection-based silicon micro-ring silicon modulators," Opt. Express, vol. 15, no. 2, pp. 430–436, 2007.

- [31] R. Amin et al., "0.52 v mm ito-based mach-zehnder modulator in silicon photonics," APL Photon., vol. 3, no. 12, 2018, Art no. 126104.

- [32] R. Amin et al., "Attojoule-efficient graphene optical modulators," Appl. Opt., vol. 57, no. 18, pp. D130–D140, 2018.

- [33] J. Heebner, R. Grover, and T. Ibrahim, Optical Microresonators: Theory, Fabrication, and Applications, ser. Springer Series in Optical Sciences. New York: Springer-Verlag, 2008. [Online]. Available: https://www.springer.com/us/book/ 9780387730677

- [34] A. H. Atabaki et al., "Integrating photonics with silicon nanoelectronics for the next generation of systems on a chip," Nature, vol. 556, no. 7701, p. 349, Apr. 2018. [Online]. Available: https://www.nature.com/articles/s41586-018-0028-z

- [35] T. J. Kippenberg, R. Holzwarth, and S. A. Diddams, "Microresonator-Based optical frequency combs," Science, vol. 332, no. 6029, pp. 555–559, Apr. 2011. [Online]. Available: https://science.sciencemag.org/content/332/6029/555

- [36] J. Juan-Colás, A. Parkin, K. E. Dunn, M. G. Scullion, T. F. Krauss, and S. D. Johnson, "The electrophotonic silicon biosensor," *Nature Commun.*, vol. 7, p. 12769, Sep. 2016. [Online]. Available: https://www.nature.com/articles/ncomms12769

- [37] M. Ziebell et al., "Ten Gbit/s ring resonator silicon modulator based on interdigitated PN junctions," Opt. Express, vol. 19, no. 15, pp. 14 690–14 695, Jul. 2011. [Online]. Available: https://www.osapublishing.org/oe/abstract.cfm?uri=oe-19-15-14690

- [38] P. Dong et al., "Low V<sub>pp</sub>, ultralow-energy, compact, high-speed silicon electro-optic modulator," Opt. Express, vol. 17, no. 25, p. 22484, Dec. 2009. [Online]. Available: https://www.osapublishing.org/oe/abstract.cfm?uri=oe-17-25-22484

- [39] C. Haffner et al., "Low loss plasmon-assisted electro-optic modulator," Nature, vol. 556, no. 7702, pp. 483–486, Apr. 2018. [Online]. Available: https://www.ncbi.nlm.nih.gov/pmc/articles/PMC5935232/

- [40] C. T. Phare, Y.-H. Daniel Lee, J. Cardenas, and M. Lipson, "Graphene electro-optic modulator with 30 GHz bandwidth," Nature Photon., vol. 9, no. 8, pp. 511–514, Aug. 2015. [Online]. Available: https://www.nature.com/articles/nphoton. 2015.122

- [41] J.-B. You, M. Park, J.-W. Park, and G. Kim, "12.5 Gbps optical modulation of silicon racetrack resonator based on carrier-depletion in asymmetric p-n diode," *Opt. Express*, vol. 16, no. 22, pp. 18 340–18 344, Oct. 2008. [Online]. Available: https://www.osapublishing.org/oe/abstract.cfm?uri=oe-16-22-18340

- [42] F. Y. Gardes et al., "High-speed modulation of a compact silicon ring resonator based on a reverse-biased PN diode," Opt. Express, vol. 17, no. 24, pp. 21 986–21 991, Nov. 2009. [Online]. Available: https://www.osapublishing.org/oe/abstract.cfm?uri=oe-17-24-21986

- [43] M. Pantouvaki, P. Verheyen, J. De Coster, G. Lepage, P. Absil, and J. Van Campenhout, "56 Gb/s ring modulator on a 300 mm silicon photonics platform," in *Proc. IEEE Eur. Conf. Opt. Commun.*, Valencia, Spain, Sep. 2015, pp. 1–3. [Online]. Available: http://ieeexplore.ieee.org/document/7341888/

- [44] G. Li et al., "40 Gb/s thermally tunable CMOS ring modulator," in Proc. IEEE 9th Int. Conf. Group IV Photon., San Diego, CA, USA, Aug. 2012, pp. 1–3. [Online]. Available: http://ieeexplore.ieee.org/document/6324190/

- [45] E. Timurdogan, C. M. Sorace-Agaskar, J. Sun, E. S. Hosseini, A. Biberman, and M. R. Watts, "An ultralow power athermal silicon modulator," *Nature Commun.*, vol. 5, no. 1, p. 4008, Dec. 2014. [Online]. Available: http://www.nature. com/articles/ncomms5008

- [46] A. N. Tait et al., "Neuromorphic photonic networks using silicon photonic weight banks," Sci. Reports, vol. 7, no. 1, p. 7430, Aug. 2017. [Online]. Available: https://doi.org/10.1038/s41598-017-07754-z

- [47] Y. Salamin et al., "100 GHz plasmonic photodetector," ACS Photon., vol. 5, no. 8, pp. 3291–3297, Aug. 2018. [Online]. Available: http://pubs.acs.org/doi/10.1021/acsphotonics.8b00525

- [48] P. Ma, Y. Salamin, B. Baeuerle, A. Josten, W. Heni, A. Emboras, and J. Leuthold, "Plasmonically enhanced graphene photodetector featuring 100 Gbit/s data reception, high responsivity, and compact size," ACS Photon., vol. 6, no. 1, pp. 154–161, Jan. 2019. [Online]. Available: https://doi.org/10.1021/acsphotonics.8b01234

- [49] L. Chen and M. Lipson, "Ultra-low capacitance and high speed germanium photodetectors on silicon," Optics Express, vol. 17, no. 10, p. 7901, May 2009. [Online]. Available: https://www.osapublishing.org/oe/abstract.cfm?uri=oe-17-10-7901

- [50] L. Chen, P. Dong, and M. Lipson, "High performance germanium photodetectors integrated on submicron silicon waveguides by low temperature wafer bonding," *Opt. Express*, vol. 16, no. 15, p. 11513, Jul. 2008. [Online]. Available: https://www.osapublishing.org/oe/abstract.cfm?uri=oe-16-15-11513

- [51] S. Assefa et al., "CMOS-Integrated 40 GHZ Germanium Waveguide Photodetector for On-Chip Optical Interconnects," in Proc. Opt. Fiber Commun. Conf. Nat. Fiber Opt. Engineers Conf., San Diego, California, 2009, p. OMR4. [Online]. Available: https://www.osapublishing.org/abstract.cfm?uri=OFC-2009-OMR4

- [52] T. Yin, R. Cohen, M. M. Morse, G. Sarid, Y. Chetrit, D. Rubin, and M. J. Paniccia, "31 GHZ Ge n-i-p waveguide photodetectors on silicon-on-insulator substrate," Opt. Express, vol. 15, no. 21, pp. 13 965–13 971, Oct. 2007. [Online]. Available: https://www.osapublishing.org/oe/abstract.cfm?uri=oe-15-21-13965

- [53] H. Chen et al., "-1 V Bias 56 Gbps germanium waveguide p-i-n photodetector with silicon contacts," in *Proc. Opt. Fiber Commun. Conf. Exhib.*, Mar. 2016, pp. 1–3.

- [54] C. T. DeRose et al., "Ultra compact 45 GHz CMOS compatible Germanium waveguide photodiode with low dark current," Opt. Express, vol. 19, no. 25, pp. 24 897–24 904, Dec. 2011. [Online]. Available: https://www.osapublishing. org/oe/abstract.cfm?uri=oe-19-25-24897

- [55] N. Hattasan, A. Gassenq, L. Cerutti, J.-B. Rodriguez, E. Tournie, and G. Roelkens, "Heterogeneous Integration of GalnAsSb p-i-n photodiodes on a silicon-on-insulator waveguide circuit," *IEEE Photon. Technol. Lett.*, vol. 23, no. 23, pp. 1760–1762, Dec. 2011. [Online]. Available: http://ieeexplore.ieee.org/document/6025258/

- [56] L. Vivien et al., "Zero-bias 40 Gbit's germanium waveguide photodetector on silicon," Opt. Express, vol. 20, no. 2, p. 1096, Jan. 2012. [Online]. Available: https://www.osapublishing.org/oe/abstract.cfm?uri=oe-20-2-1096

- [57] L. Vivien et al., "High speed and high responsivity germanium photodetector integrated in a Silicon-On-Insulator microwaveguide," Opt. Express, vol. 15, no. 15, p. 9843, 2007. [Online]. Available: https://www.osapublishing.org/oe/abstract.cfm?uri=oe-15-15-9843

- [58] X. Xie et al., "High-power and high-speed heterogeneously integrated waveguide-coupled photodiodes on silicon-on-insulator," J. Lightw. Technol., vol. 34, no. 1, pp. 73–78, Jan. 2016. [Online]. Available: http://ieeexplore.ieee.org/document/7302005/

- [59] Q. Xu, D. Fattal, and R. G. Beausoleil, "Silicon microring resonators with 1.5-μm radius," Opt. Express, vol. 16, no. 6, p. 4309, Mar. 2008. [Online]. Available: https://www.osapublishing.org/oe/abstract.cfm?uri=oe-16-6-4309

- [60] T. Baba et al., "50-Gb/s ring-resonator-based silicon modulator," Opt. Express, vol. 21, no. 10, pp. 11 869–11 876, May 2013. [Online]. Available: https://www.osapublishing.org/oe/abstract.cfm?uri=oe-21-10-11869

- [61] Z. Wang et al., "Resonance control of a silicon micro-ring resonator modulator under high-speed operation using the intrinsic defect-mediated photocurrent," Opt. Express, vol. 25, no. 20, p. 24827, Oct. 2017. [Online]. Available: https://www.osapublishing.org/abstract.cfm?URI=oe-25-20-24827

- [62] "Thermal-aware synthesis of integrated photonic ring resonators," in *Proc. IEEE/ACM Int. Conf. Comput.Aided Des.*, San Jose, CA, USA. [Online]. Available: http://ieeexplore.ieee.org/document/7001405/

- [63] K. Padmaraju and K. Bergman, "Resolving the thermal challenges for silicon microring resonator devices," Nanophotonics, vol. 3, no. 4-5, Jan. 2014. [Online]. Available: https://www.degruyter.com/view/j/nanoph.2014.3.issue-4-5/nanoph-2013-0013/nanoph-2013-0013.xml

- [64] H. Jayatilleka, K. Murray, M. Caverley, N. A. F. Jaeger, L. Chrostowski, and S. Shekhar, "Crosstalk in SOI Microring Resonator-Based Filters," J. Lightw. Technol., vol. 34, no. 12, pp. 2886–2896, Jun. 2016. [Online]. Available: http://ieeexplore.ieee.org/document/7272050/