Open Access

# **Rearrangeable-Nonblocking Five-Port Silicon Optical Switch for 2-D-Mesh Network on Chip**

IEEE Photonics Journal

An IEEE Photonics Society Publication

Volume 10, Number 3, June 2018

DOI: 10.1109/JPHOT.2018.2841401 1943-0655 © 2018 IEEE

# Rearrangeable-Nonblocking Five-Port Silicon Optical Switch for 2-D-Mesh Network on Chip

Ting Zhou<sup>(1)</sup>,<sup>1,2</sup> Hao Jia<sup>(1)</sup>,<sup>1,2</sup> Jincheng Dai,<sup>1,2</sup> Shanglin Yang,<sup>1,2</sup> Lei Zhang<sup>(1)</sup>,<sup>1,2</sup> Xin Fu,<sup>1,2</sup> and Lin Yang<sup>(1)</sup>,<sup>1,2</sup>

<sup>1</sup>State Key Laboratory of Integrated Optoelectronics, Institute of Semiconductors, Chinese Academy of Sciences, Beijing 100083, China <sup>2</sup>College of Materials Science and Opto-Electronic Technology, University of Chinese Academy of Sciences, Beijing 100049, China

DOI:10.1109/JPHOT.2018.2841401

1943-0655 © 2018 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Manuscript received April 10, 2018; revised May 15, 2018; accepted May 24, 2018. Date of publication May 28, 2018; date of current version June 18, 2018. National Key R&D Program of China (2017YFA0206402, 2016YFB0402501); National Natural Science Foundation of China (NSFC) (61575187, 61535002, 61505198, 61704168). Corresponding author: L. Yang (e-mail: oip@semi.ac.cn).

**Abstract:** We propose and experimentally demonstrate a five-port silicon optical switch based on the optimized Spanke–Beneš structure for 2-D-mesh network on chip. We optimize it by substituting optical waveguide crossings for  $2 \times 2$  optical switching units. By this approach, the total number of optical switching units is reduced from 10 to 8 compared to a five-port optical switch based on Spanke–Beneš structure. The  $2 \times 2$  optical switching unit is based on balanced Mach–Zehnder interferometers with integrated titanium nitride microheaters on both arms. The average operating power consumption of the whole switch is 215 or 178 mW for the left arm or right arm by using single-arm driving, which will be reduced to 89 mW by using dual-arm driving. The insertion losses (excluding coupling losses) of the five optical links under "all-cross" and "all-bar" states are 3.2–6.0 and 3.3–6.2 dB, respectively, in the wavelength range of 1525–1565 nm. The optical signal-to-noise ratios are larger than 12.2 dB in 1525–1565 nm. 40-Gb/s data transmission experiment is implemented to verify the transmission functionality. The 10–90% rising and 90–10% falling time of the optical switching units in the device by thermal tuning are all ~17  $\mu$ s.

Index Terms: Silicon photonics, optical switch, optical network.

## 1. Introduction

Photonic network-on-chip (NoC) has been recognized to promise future large-capacity, low-latency and low-power-consumption interconnect of high-performance many-core chip multiprocessors (CMP) [1]–[3]. In the past several years, various photonic NoC, such as Mesh, Fat-Tree, Clos, torus and flattened butterfly, have been proposed and demonstrated [4]. Among them, 2D-Mesh has been widely used in practical application because of its simple grid-type shape and regular structure, which is the most appropriate for the two-dimensional layout on a chip [4], [5]. In a 2D-Mesh photonic NoC, a routing node has four ports (West, South, East, and North) to connect with other routing nodes and a local port to connect with the processing element. Thus a five-port optical switch is appropriate for constructing the routing node [5], [6].

Performance of switches in routing nodes is deemed to be one of the main factors impacting the performance of NoC [5], [6]. To reduce the insertion losses and power consumption of the

switch, optimizing the topology of the optical switch to get the same functionality with less optical switching units (OSUs), and improving the performance of single OSU are two major approaches. For the merits of compactness and compatibility with the standard complementary metal-oxidesemiconductor (CMOS) process, silicon photonic platform has been adopted to demonstrate optical switching networks based on several switch topology structures, such as Spanke-Beneš, Beneš, and PILOSS, in the past several years [7]-[11]. Spanke-Beneš structure can construct switch with arbitrary number of ports, while the port number of Beneš structure must be a power of two [7], [8]. Although the losses of PILOSS network are very uniform, compared with Spanke-Beneš network, it has nearly twice the number of switching units and many waveguide crossings, which increase the insertion losses (ILs) and crosstalk [7], [9], [12]. Consequently, Spanke-Beneš structure is more appropriate to construct a five-port optical switch. Composed of N(N-1)/2 OSUs, Spanke-Beneš network is originally designed for situations where path crossovers are not allowed, to avoid the relatively high IL and crosstalk of a waveguide crossing whose performance is limited by early fabrication process in thirty years ago [7]. Yet now a waveguide crossing usually has lower IL and crosstalk than an OSU constructed by MZI [13]. For a five-port reconfigurable non-blocking optical switch based on Spanke-Beneš structure, there exist many redundant switching states, which is the fundamental of further optimization. On the premise of maintaining the original function, substituting some OSUs by waveguide crossings makes the switch lighter and perform better in ILs, crosstalk and power consumption.

Several optical structures for constructing an optical switch such as Mach-Zehnder interferometers (MZIs) [10], [11], [13], directional couplers (DCs) [14], microring resonators (MMRs) [15] and multimode interferometers (MMIs) [16], have been demonstrated on silicon-on-insulator (SOI) platform. Among them, MZIs have larger tolerance to fabrication imperfections and lower temperature sensitivity [17]. Nevertheless, the slight length difference between its two arms, caused by fabrication imperfection, induces random phase errors into the waveguides. It requires an extra voltage to compensate these phase shifts in the single-arm driving situation, which usually leads to relatively high driving voltage and further results in higher operating power consumption of the whole switch. Compared with single-arm driving, dual-arm driving is more power-efficient, since the random phase error of one arm can be regarded as a phase compensation to the other arm in a specific switching state.

In this paper, we propose and experimentally demonstrate an optimized thermo-optic five-port optical switch based on Spanke-Beneš structure on SOI platform for 2D Mesh NoC. It consists of eight Mach-Zehnder optical switches (MZSs), which is optimized by substituting two optical wave-guide crossings for two 2  $\times$  2 Mach-Zehnder optical switches of a typical five-port Spanke-Beneš switch. Dual-arm driving is exploited for phase shifting to reduce the operating power consumption of the whole switch. The insertion losses (ILs) and optical signal-to-noise ratios (OSNR) of five optical links under "all-cross" and "all-bar" states are measured in the wavelength range of 1525  $\sim$  1565 nm. 40 Gbps data transmission experiment is implemented to verify the transmission functionality. The measured 10%  $\sim$  90% rising and 90%  $\sim$  10% falling time of the OSUs upon thermal tuning are all about 17  $\mu$ s.

## 2. Optimized Optical Switch Design

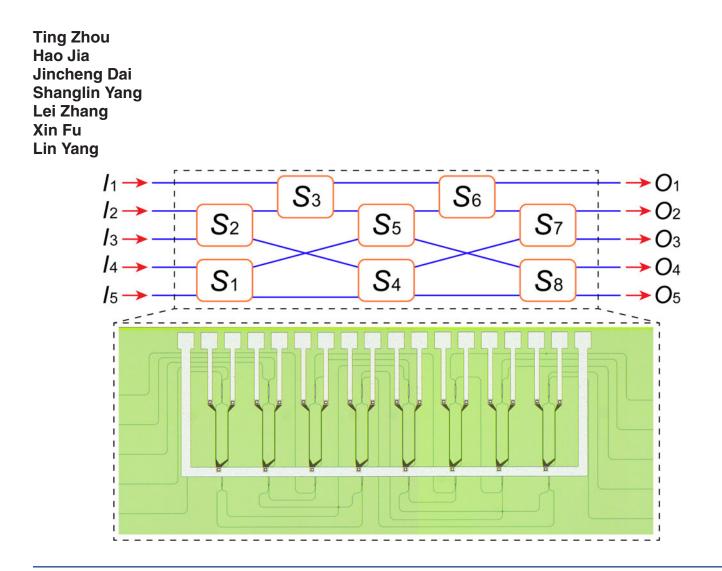

Fig. 1(a) shows the architecture of the five-port optical switch based on Spanke-Beneš planar permutation network. It is composed of ten 2 × 2 OSUs  $S_1 \sim S_{10}$  without waveguide crossings and can be divided into five stages. We label five input/output ports of the switch as  $I_1 \sim I_5/O_1 \sim O_5$  and denote the optical link from input  $I_i$  to output  $O_j$  as  $I_i \rightarrow O_j$  (i, j = 1, 2, 3, 4, 5). The optical switch in Fig. 1(a) is rearrangeably nonblocking, which means that for a special input-output (IO) connection in the network, the path needs to be rearranged to accommodate the other IO configurations, which makes its path is not unique [12]. For instance, if we denote the *i*-th OSU in "cross" or "bar" state as  $S_i^C/S_i^B$ , in a special IO configuration, the optical paths for IO connections  $I_1 \rightarrow O_2$  and  $I_2 \rightarrow O_3$  can be expressed as  $I_1 \rightarrow S_3^B \rightarrow S_6^C \rightarrow S_7^B O_2$  and  $I_2 \rightarrow S_2^C \rightarrow S_9^B \rightarrow S_5^B \rightarrow S_{10}^B \rightarrow S_7^B O_3$  respectively. In case the IO configuration is changed from  $I_1 \rightarrow O_2, I_2 \rightarrow O_3$  to  $I_1 \rightarrow O_5, I_2 \rightarrow O_3$ , the optical

Fig. 1. (a) Architecture of the five-port optical switch based on Spanke-Beneš, (b) Architecture of the five-port optical switch by substituting optical waveguide crossing for OSUs  $S_9$  and  $S_{10}$ .

path for  $I_2 \rightarrow O_3$  need to be rearranged though its IO connection has no change. The switch in Fig. 1(a) has ten OSUs, which are either in "cross" or "bar" state, thus there are  $2^{10} = 1024$  possible configurations for the switch. Nevertheless, for a five-port optical switch, its IO configurations are 5! = 120 which is much smaller than the 1024 possible configurations for the switch, indicating that there are repetitive configurations which are mapping to the same IO configurations. Ordinarily a 2 × 2 OSU is used to connect different optical paths and manipulate the direction of optical streams. However, if a OSU is constrained in "cross" state and the switch can still be rearrangeably nonblocking by adjusting the configurations of the other OSUs, the OSU can be replaced by a waveguide crossing. By this means the OSU count in the switch can be reduced and the structure of the switch is simplified. Owing to the very low IL and high OSNR of a waveguide crossing [13], this substitution reduces the ILs and crosstalk of the optical paths passing through these replaced OSUs. Since a waveguide crossing is a passive component, it has no power consumption compared with an OSU which usually needs an extra voltage applying to it to maintain "cross" state. Consequently, the operating power consumption of the switch can be reduced.

As illustrated in Fig. 1(b), the optimized five-port switch comprises eight OSUs and two waveguide crossings. Compared with the switch in Fig. 1(a),  $S_9$  and  $S_{10}$  are replaced by two waveguide crossings. It is noteworthy that once an OSU is replaced by a waveguide crossing, some IO configurations may be lost and the total IO configurations are less than 120, which means that the switch is blocking. Thus, verifying the rearrangeably nonblocking characteristic of the optimized switch is an essential prerequisite. Here we testify it by adopting a transfer matrix approach, which is very common to describe the IO configuration of a switch [18]. Similar to the switch in Fig. 1(a), the optimized switch can be divided into five stages and the permutation matrix of the switch can be calculated by multiplying the transfer matrix of each separate stage as the light propagation sequence. For instance, the transfer matrix of stage 1 and stage 2 can be expressed as

$$\boldsymbol{T}_{stage1} = \begin{pmatrix} 1 & 0 & 0 \\ 0 & \boldsymbol{S}_2^{CB|} & 0 \\ 0 & 0 & \boldsymbol{S}_1^{C|B} \end{pmatrix}, \quad \boldsymbol{T}_{stage2} = \begin{pmatrix} \boldsymbol{S}_3^{C|B} & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 1 \\ 0 & 0 & 0 & 1 \end{pmatrix},$$

respectively. Here  $\mathbf{S}_{i}^{C|B}$  (i = 1, 2, 3, ..., 8) is the transfer matrix of OSU  $S_{i}$  in "cross" or "bar" state and given by  $\mathbf{S}_{i}^{C} = \begin{pmatrix} 0 & 1 \\ 1 & 0 \end{pmatrix}$  and  $\mathbf{S}_{i}^{B} = \begin{pmatrix} 1 & 0 \\ 0 & 1 \end{pmatrix}$ . By this means the permutation matrix of the switch is given by

#### $T = T_{stage5} \cdot T_{stage4} \cdot T_{stage3} \cdot T_{stage2} \cdot T_{stage1}$

For a *N*-port switch which can be divided into *M* stages, the permutation matrix of the switch can be given by

$$T = T_{stageM} \cdot T_{stageM-1} \cdots T_{stage2} \cdot T_{stage1}$$

If we define set  $T_{set} = \{T\}$ , which contains all possible values of permutation matrix T. We use the notation  $|T_{set}|$  to represent the number of elements contained in  $T_{set}$ . For a *N*-port switch, the

| 4000 $\mu$ m × 895 $\mu$ m Al →<br>Coupling area $I_1$      | 100 μm<br>Ο1 | ling area |

|-------------------------------------------------------------|--------------|-----------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$       | O2<br>O3     |           |

| 14                                                          | O4           |           |

| /₅ Waveguide crossing→ Heater(TiN) ↑<br>2×2 M-Z switching u | O5           |           |

Fig. 2. Micrograph of the fabricated 2  $\times$  2 four-mode optical switch.

judgment is given by

$\begin{cases} |T_{set}| = N!, & nonblocking \\ |T_{set}| < N!, & blocking \end{cases}$

Since a permutation matrix is only mapping to one I/O configuration,  $|T_{set}| = 120$  for a nonblocking five-port switch. Once  $|T_{set}|$  is less than 120, the optimized switch loses some I/O configurations and is blocking. Using this judgment, the rearrangeably nonblocking characteristic of the switch can be verified. As there are  $2^8 = 256$  possible configurations for the optimized switch, it is difficult to manually calculate  $|T_{set}|$ . A MATLAB script has been written to operate the calculation taking full advantage of MATLAB matrix functions and computing capability. The result shows  $|T_{set}| = 120$ , verifying that the optimized switch is rearrangeably nonblocking.

2 × 2 Mach-Zehnder switching unit is used as the OSU in the optimized five-port optical switch for its larger tolerance to imperfect fabrication and lower temperature sensitivity. 2 × 2 multimode interference (MMI) coupler with paired interference mechanism is adopted to realize the power splitting and combining because of its better performance in power splitting imbalance [19]. It is 6  $\mu$ m in width, 43  $\mu$ m in length, 220 nm in height and 70 nm in slab thickness, which is optimized by three-dimensional finite-difference time-domain method. The calculated propagation loss of the MMI coupler is 0.3 dB. The length of each arm of the OSU is 240  $\mu$ m covered by a 200  $\mu$ m length micro-heater.

#### 3. Device Fabrication

Fig. 2 shows the micrograph of the fabricated device with a footprint of 4000  $\mu$ m × 895  $\mu$ m. An 8-inch silicon-on-insulator wafer with a 220-nm-thick top silicon layer and a 3- $\mu$ m-thick buried silicon dioxide layer is used to fabricate the device. The patterns are defined by 248-nm deep ultraviolet photolithography. Inductively coupled plasma etching is employed to form the silicon rib waveguides, which are 400 nm in width, 220 nm in height and 70 nm in slab thickness and only supports fundamental quasi-TE mode. A 1500-nm-thick silicon dioxide layer is deposited on the silicon layer by plasma-enhanced chemical vapor deposition (PECVD) to prevent the absorption of the optical field by the metal. Then a 150-nm-thick titanium nitride is sputtered on the separate layer and 1- $\mu$ m-wide and 200- $\mu$ m-long TiN micro-heaters are fabricated on the two arms of the Mach-Zehnder optical switch to realize the thermal tuning. Via holes are etched after depositing a 300-nm-thick silicon dioxide layer by PECVD. Finally, aluminum wires and square pads with the size of 70  $\mu$ m × 70  $\mu$ m are fabricated.

#### 4. Experiment and Result Discussion

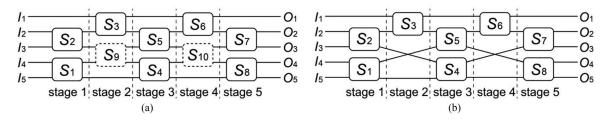

The bottom half of Fig. 3 illustrates the experimental setup for characterizing the transmission spectra of the device. Light emitted from an amplified spontaneous emission source (ASE) is coupled into the device by a lensed fiber with a spot size of 5  $\mu$ m. Then the output light is measured

Fig. 3. Experimental setup for characterizing the device (TL, tunable laser; ASE, amplified spontaneous emission; MD, modulator; PC, polarization controller; PPG, pulse pattern generator; AFG, arbitrary function generator; DCP, direct-current power; DUT, device under test; EDFA: Erbium-doped fiber amplifier; TF: tunable filter; DCA, digital communication analyzer; OSA, optical spectrum analyzer).

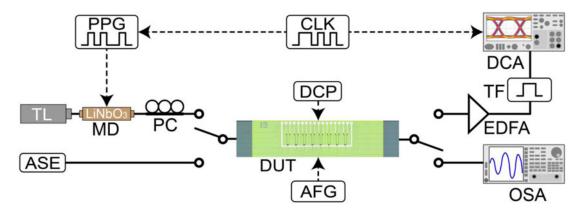

Fig. 4. Transmission spectra for the signal and noise of the optical links in the shown routing states (IL, insertion loss; OSNR, optical signal-to-noise ratios).

by an optical spectrum analyzer (OSA). Direct- current powers are utilized to control the driving voltages applied to the phase-shifting arms of the OSUs to toggle their states ("cross" or "bar"). The eight OSUs should be in "cross" state in theory when no driving voltages are applied to them. Due to the random phase errors caused by fabrication imperfection of the waveguides, the OSUs are not exactly in "cross" state and need extra voltages to correct these random phase errors. Theoretically, these phase errors can be corrected by applying a correction voltage to either phaseshifting arm of each OSU. To reduce the power consumption of the switch, we first choose the arm with lower correction voltage of each OSU to finish the phase errors correction, after which the switch is in "all-cross" state. Then we apply a voltage to the other phase-shifting arm of each OSU to toggle the switch to "all-bar" state. Usually, the local communication in one processor core is carried by electrical interconnect, so light injected into one port should not be guided to the output of the same port like the switch do in "all-bar" state. Here the switch in "all-bar" state is specially measured for performance characterization. Straight waveguides with the same coupling structures as those of the device are used to normalize the transmission spectra of the switch in the two states, which are shown in Fig. 4. The ILs of the switch are composed of three parts: the propagation losses of connected waveguides, ILs of waveguide crossings and ILs of OSUs. The measured IL of the waveguide crossing is  $\sim$ 0.05 dB and the propagation loss of the connected waveguide is 2.5 dB/cm. The ILs of the OSU vary from 0.7  $\sim$  2.8 dB in "cross" state and 1.1  $\sim$ 3.3 dB in "bar" state in the wavelength range of 1525  $\sim$  1565 nm [20]. Due to the dispersion of the

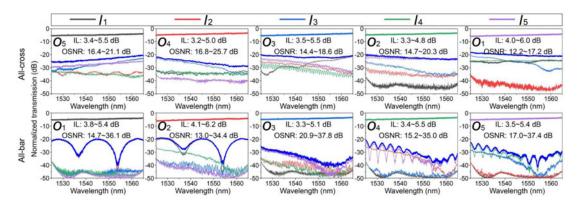

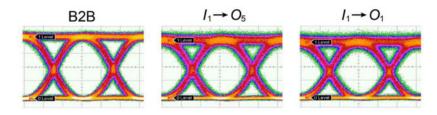

Fig. 5. Eye diagrams for 40 Gbps data transmission for optical links  $I_1 \rightarrow O_5$  and  $I_1 \rightarrow O_1$ .

OSUs based on Mach-Zehnder interferometers, slight wavelength dependence is observed in the transmission spectra. As illustrated in Fig. 4, the ILs of the five optical links under "all-cross" and "all-bar" states are within  $3.2 \sim 6.0$  dB and  $3.3 \sim 6.2$  dB respectively in the wavelength range of  $1525 \sim 1565$  nm. The crosstalk between two optical links is caused by the OSUs and waveguide crossings which are common to their paths. In the worst case, the total noise for an optical link is the summation of the crosstalk from the other four optical links, as shown in the bold blue curve in Fig. 4. The results show that the OSNRs of five optical links under "all-cross" and "all-bar" states are  $12.2 \sim 25.7$  dB and  $13.0 \sim 37.8$  dB respectively in the wavelength range of  $1525 \sim 1565$  nm. The relatively low OSNR is mainly caused by the power imbalance of the 3 dB MMI coupler in the Mach-Zehnder switch due to the fabrication imperfection. In theory, a 1 dB power imbalance limits the crosstalk smaller than -40 dB [21]. To further reduce ILs and improve the OSNRs of the switch, a more advanced fabrication process should be considered [11].

The experimental setup for data transmission characterization is shown in the top half of Fig. 3. Continuous-wave (CW) light at 1550 nm emitted from a tunable laser (TL) is first modulated by the LiNbO<sub>3</sub> optical modulator, which is driven by 40 Gbps pseudo-random binary sequence (PRBS) with a length of  $2^{31} - 1$  generated by a pulse pattern generator. Then the light is set to transverse electric (TE) polarization by a polarization controller (PC). The light derived from the PC is sent to a straight waveguide with the same coupling structure as that of the device. The output optical signal is then amplified by an erbium-doped fiber amplifier (EDFA) and filtered by a tunable filter (TF) before being sent to the DCA for back to back (B2B) eye diagram observation. Similarly, the straight waveguide is then replaced by the device under test (DUT) for eye diagram observation of optical links. 40 Gbps data transmission experiment is implemented for optical links  $I_1 \rightarrow O_5$  and  $I_1 \rightarrow O_1$  in the optical paths  $I_1 \rightarrow S_3^C \rightarrow S_5^C \rightarrow S_8^C O_5$  and  $I_1 \rightarrow S_3^B \rightarrow S_6^B O_1$  respectively. As shown in Fig. 5, the observed eye diagrams are open and clear, verifying the data transmission function of the switch with the data rate of 40 Gbps. Compared with B2B eye diagram, the observed eye diagrams are slightly deteriorative, which is caused by the propagation losses of the measured optical links.

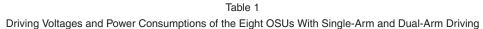

Single-arm driving is commonly employed to control the phase difference between the two phaseshifting arms of a MZS [22]. Nevertheless, random phase errors caused by fabrication imperfection require extra voltages to calibrate the initial phase of the phase-shifting arms. Table 1 lists the driving voltages and power consumptions of the eight OSUs with single-arm and dual-arm driving. The results show that the power consumption of a single OSU to achieve a " $\pi$ " phase shift is 17 ~ 30 mW. The total power consumptions are 199 mW/231 mW and 173 mW/182 mW in "all-cross"/"all-bar" state when the switch is driving by left phase-shifting arm and right phaseshifting arm respectively. In the case of dual-arm driving, the total power consumption can be reduced to 97 mW/80 mW in "all-cross"/"all-bar" state. If we assume that each OSU works in either state ("cross" or "bar") half of the operating time, the average operating power consumptions of the whole switch are 215 mW/178 mW for single-arm driving and 89 mW for dual-arm driving. Compared with single-arm driving, dual-arm driving saves about half of the power consumption for the device. Ideally, there are no random phase errors in the phase-shifting arms. In this case, single-arm and dual-arm driving have equal power consumption in theory. The extra power consumption depends on the phase deviation from theoretical value for each phase-shifting arm. Consequently, improving

| "All-cross"<br>state |           | OSU         | S1  | S <sub>2</sub> | S₃  | S4  | $S_5$ | $S_6$ | S7  | S <sub>8</sub> |

|----------------------|-----------|-------------|-----|----------------|-----|-----|-------|-------|-----|----------------|

|                      | Left arm  | Voltage (V) | 9.6 | 7.2            | 5.8 | 8.7 | 9.5   | 2.7   | 6.4 | 9.4            |

|                      |           | Power (mW)  | 38  | 22             | 12  | 35  | 38    | 3     | 13  | 38             |

|                      | Right arm | Voltage (V) | 4.9 | 7.9            | 8.7 | 6.2 | 4.4   | 10.5  | 8.6 | 4.7            |

|                      |           | Power (mW)  | 10  | 32             | 35  | 19  | 9     | 42    | 17  | 9              |

|                      | Dual-arm  | Voltage (V) | 4.9 | 7.2            | 5.8 | 6.2 | 4.4   | 2.7   | 6.4 | 4.7            |

|                      |           | Power (mW)  | 10  | 22             | 12  | 19  | 9     | 3     | 13  | 9              |

| "All-bar"<br>state   | Left arm  | Voltage (V) | 6.0 | 10.5           | 9.5 | 4.3 | 5.8   | 13.4  | 9.9 | 5.7            |

|                      |           | Power (mW)  | 12  | 52             | 38  | 9   | 12    | 67    | 30  | 11             |

|                      | Right arm | Voltage (V) | 8.8 | 2.2            | 4.3 | 9.8 | 9.0   | 7.3   | 4.0 | 9.0            |

|                      |           | Power (mW)  | 35  | 2              | 9   | 39  | 36    | 21    | 4   | 36             |

|                      | Dual-arm  | Voltage (V) | 6.0 | 2.2            | 4.3 | 4.3 | 5.8   | 7.3   | 4.0 | 5.7            |

|                      |           | Power (mW)  | 12  | 2              | 9   | 9   | 12    | 21    | 4   | 11             |

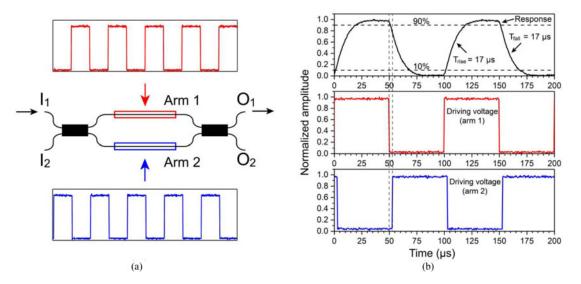

Fig. 6. (a) Schematic of OSU driven by dual-arm; (b) dynamic response of the OSU and the driving signals of the two arm.

fabrication is effective to reduce the power consumption. Air-trench can also be implemented to improve the heat efficiency and further make the device power-efficient [23].

The switching speed of the switch is characterized by measuring time-domain dynamic response of the OSUs. Two 10 KHz square-wave electrical signals from an arbitrary function generator are separately applied to the two phase-shifting arms of an OSU simultaneously and a real-time oscilloscope is used for response time measurement. The schematic of OSU driven by dual-arm is illustrated in Fig. 6(a). To balance the rising and falling time of the OSU, the phase difference of two driving voltages applied to the two phase-shifting arms is about 190.5°, which a little deviates from its theoretical value of 180°. The result shows that the 10% ~ 90% rising time and 90% ~ 10% falling time of the OSUs upon thermal tuning are all about 17  $\mu$ s, as shown in Fig. 6(b). To improve the dynamic switching performance of the switch in a 2D Mesh network, an electro-optic tuning mechanism with higher switching speed can be considered in the future [24].

#### 5. Conclusion

In conclusion, a five-port silicon optical switch based on optimized Spanke-Beneš structure for 2D-Mesh NoC is proposed and experimentally demonstrated. Optical waveguide crossings are utilized to replace the 2 × 2 optical switching units in the original switch. The ILs, crosstalk and power consumption can be reduced by this approach. A dual-arm driving method is exploited for tuning the switching state and the average operating power consumption of the whole switch is reduced from 178 mW/215 mW (single-arm driving) to 89 mW (dual-arm driving). The ILs of five optical links under "all-cross"/"all-bar" states are  $3.2 \sim 6.0 \text{ dB}/3.3 \sim 6.2 \text{ dB}$  respectively in the wavelength range of  $1525 \sim 1565 \text{ nm}$ . The optical signal-to-noise ratios are larger than 12.2 dB in  $1525 \sim 1565 \text{ nm}$ . 40 Gbps data transmission experiment is implemented to verify the transmission functionality. The measured result shows the  $10\% \sim 90\%$  rising time and the  $90\% \sim 10\%$  falling time of the OSUs upon thermal tuning are all ~17  $\mu$ s. The optimized five-port switch is more compact and perform better in ILs, crosstalk and power consumption than original switch on Spanke-Beneš structure and shows promising potential for future application in 2D-Mesh NoC.

#### References

- R. G. Beausoleil, P. J. Kuekes, G. S. Snider, S. Y. Wang, and R. S. Williams, "Nanoelectronic and nanophotonic interconnect," *Proc. IEEE*, vol. 96, no. 2, pp. 230–247, Feb. 2008.

- [2] D. A. B. Miller, "Device requirements for optical interconnects to silicon chips," Proc. IEEE, vol. 97, no. 7, pp. 1166–1185, Jul. 2009.

- [3] L. Thylén and L. Wosinski, "Integrated photonics in the 21st century," Photon. Res., vol. 2, no. 2, pp. 75–81, Apr. 2014.

- [4] E. Salminen, A. Kulmala, and T. D. Hamalainen, "Survey of network-on-chip proposals," White Paper, OCP-IP, vol. 1, p. 13, Mar. 2008.

- [5] S. D. Chawade, M. A. Gaikwad, and R. M. Patrikar, "Review of XY routing algorithm for network-on-chip architecture," *Int. J. Comput. Appl.*, vol. 43, no. 21, pp. 975–8887, 2012.

- [6] H. Gu, J. Xu, and Z. Wang, "A novel optical mesh network-on-chip for gigascale systems-on-chip," in Proc. Asia South Pac. Conf. Circuits Syst., 2008, pp. 1728–1731.

- [7] R. A. Spanke and V. E. Beneš, "N-stage planar optical permutation network," Appl. Opt., vol. 26, no. 7, pp. 1226–1229, Apr. 1987.

- [8] V. E. Beneš, "Algebraic and topological properties of connecting networks," Bell Labs Tech. J., vol. 41, no. 4, pp. 1249– 1274, 1962.

- [9] T. Shimoe, K. Hajikano, and K. Murakami, "Path-independent insertion loss optical space switch," in *Proc. Opt. Fiber Commun. Conf.*, 1987, Art. no. WB2.

- [10] L. Lu, L. Zhou, Z. Li, and J. Chen, "Broadband 4 × 4 nonblocking silicon electrooptic switches based on Mach–Zehnder interferometers," *IEEE Photon. J.*, vol. 7, no. 1, Feb. 2015, Art. no. 7800108.

- [11] K. Tanizawa *et al.*, "Ultra-compact 32 × 32 strictly-non-blocking Si-wire optical switch with fan-out LGA interposer," *Opt. Exp.*, vol. 23, no. 13, pp. 17599–17606, Jun. 2015.

- [12] N. Dupuis and B. G. Lee, "Impact of topology on the scalability of Mach–Zehnder-based multistage silicon photonic switch networks," J. Lightw. Technol., vol. 36, no. 3, pp. 763–772, Feb. 2018.

- [13] L. Lu et al., "16 × 16 non-blocking silicon optical switch based on electro-optic Mach-Zehnder interferometers," Opt. Exp., vol. 24, no. 9, pp. 9295–9307, May 2016.

- [14] Y. Shoji, K. Kintaka, S. Suda, H. Kawashima, T. Hasama, and H. Ishikawa, "Low-crosstalk 2 × 2 thermo-optic switch with silicon wire waveguides," Opt. Exp., vol. 18, no. 9, pp. 9071–9075, Apr. 2010.

- [15] A. Biberman, H. L. R. Lira, K. Padmaraju, N. Ophir, J. Chan, and M. Lipson, "Broadband silicon photonic electrooptic switch for photonic interconnection networks," *IEEE Photon. Technol. Lett.*, vol. 23, no. 5, pp. 504–506, Apr. 2011.

- [16] W. Wang, H. Zhou, J. Yang, M. Wang, and X. Jiang, "Highly integrated 3 × 3 silicon thermo-optical switch using a single combined phase shifter for optical interconnects," *Opt. Lett.*, vol. 37, no. 12, pp. 2307–2309, Jun. 2012.

- [17] K. Padmaraju and K. Bergman, "Resolving the thermal challenges for silicon microring resonator devices," *Nanophotonics*, vol. 3, nos. 4/5, pp. 269–281, Aug. 2014.

- [18] N. Dupuis *et al.*, "Modeling and characterization of a nonblocking 4 × 4 Mach–Zehnder silicon photonic switch fabric," *J. Lightw. Technol.*, vol. 33, no. 20, pp. 4329–4337, Oct. 2015.

- [19] N. Š. Lagali, M. R. Paiam, R. I. MacDonald, K. Rhoff, and A. Driessen, "Analysis of generalized Mach-Zehnder interferometers for variable-ratio power splitting and optimized switching," *J. Lightw. Technol.*, vol. 17, no. 12, pp. 2542– 2550, Dec. 1999.

- [20] L. Yang *et al.*, "Reconfigurable nonblocking 4-port silicon thermo-optic optical router based on Mach–Zehnder optical switches," *Opt. Lett.*, vol. 40, no. 7, pp. 1402–1405, Apr. 2015.

- [21] N. Dupuis et al., "Nanosecond-scale mach-zehnder-based CMOS photonic switch fabrics," J. Lightw. Technol., vol. 35, no. 4, pp. 615–623, Feb. 2017.

- [22] S. Zhao, L. Lu, L. Zhou, D. Li, Z. Guo, and J. Chen, "16 × 16 silicon Mach–Zehnder interferometer switch actuated with waveguide microheaters," *Photon. Res.*, vol. 4, no. 5, pp. 202–207, Oct. 2016.

- [23] Y. Sun *et al.*, "A low-power consumption MZI thermal optical switch with a graphene-assisted heating layer and air trench," *RSC Adv.*, vol. 7, no. 63, pp. 39922–39927, 2017.

- [24] M. Yang *et al.*, "Non-blocking 4x4 electro-optic silicon switch for on-chip photonic networks," *Opt. Exp.*, vol. 19, no. 1, pp. 47–54, Jan. 2011.