# All-Optical Address Decoder Using Injection-Locking Property of External-Cavity-Based Single-Mode FP-LD

Volume 5, Number 2, April 2013

Hoai Tran Quoc Bikash Nakarmi Yong Hyub Won

DOI: 10.1109/JPHOT.2013.2259585 1943-0655/\$31.00 ©2013 IEEE

# All-Optical Address Decoder Using Injection-Locking Property of External-Cavity-Based Single-Mode FP-LD

Hoai Tran Quoc, Bikash Nakarmi, and Yong Hyub Won

Korea Advanced Institute of Science and Technology (KAIST), Daejeon 305-701, Korea

DOI: 10.1109/JPHOT.2013.2259585 1943-0655/\$31.00 © 2013 IEEE

Manuscript received March 28, 2013; revised April 16, 2013; accepted April 18, 2013. Date of publication April 23, 2013; date of current version April 30, 2013. This work was supported by a grant from the R&D Program (Industrial Strategic Technology Development) funded by the Ministry of Knowledge Economy (MKE), Republic of Korea. Corresponding author: H. Tran Quoc (e-mail: hoaitq@ kaist.ac.kr).

**Abstract:** A novel all-optical address decoder (AOAD) using an external-cavity-based single-mode Fabry–Pérot laser diode (SMFP-LD) is proposed and demonstrated. The proposed AOAD is the combination of logic gates that are cascaded together to give specific functions of the decoder. The working principles of all logic gates are based on the single-and multi-input injection-locking properties of SMFP-LD. The outputs of the proposed AOAD have contrast ratios of above 27 dB in the spectrum domain, clear waveforms, and clear eyes diagrams with good BER at the data rate of 10 Gb/s. The proposed AOAD has several advantages such as a simple and cascadable structure, low cost, and low bias current (below 19 mA) compared with other optical technologies.

**Index Terms:** All-optical address decoder (AOAD), injection locking, single-mode Fabry–Pérot laser diode (SMFP-LD), optical processing.

### 1. Introduction

An address decoder is a circuit that has two or more bits of address bus as inputs and has one or more device selection lines as outputs. In electronics field, the address decoder is represented in all integrated-circuit families, processors, standard FPGA, and ASIC libraries [1]. Likewise, all-optical address decoder (AOAD) is the essential building block for all-optical systems that use optical buses. For example, AOAD should be presented in all-optical switching, control, memory, and future all-optical arithmetic logic units (ALUs) where outputs are based on the combination of inputs. In general, all-optical computing and controlling, using light instead of electrons as a fast and low energy replacement, have several advantages compared with those of electronics, such as higher bandwidth, data transparency, less power consumption [2], higher parallelism, more flexibility in layout, and less loss in communication [3]. To our knowledge, there has been only one proposal on AOAD so far using a semiconductor optical amplifier (SOA) [4]; however, the decoder scheme in [4] not only requires many components such as SOA, erbium-doped fiber amplifier (EDFA), and optical demultiplexer (DEMUX) but is also expensive and requires high bias current (~250 mA). To overcome the requirement of high current and expensive components, a Fabry-Pérot laser diode (FP-LD) may be one of the candidates for the same. Various optical units have been demonstrated using multimode FP-LD (MMFP-LD) [5], [6] and single-mode FP-LD (SMFP-LD) [7]-[9]; however, the cascading of many individual FP-LDs and the relationship between the required input power to

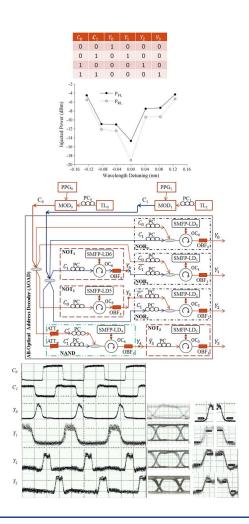

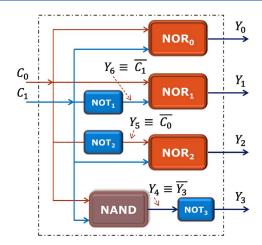

Fig. 1. Block diagram of an AOAD, where  $C_0$  and  $C_1$  are inputs;  $Y_0$ ,  $Y_1$ ,  $Y_2$  and  $Y_3$  are outputs;  $Y_4$ ,  $Y_5$  and  $Y_6$  are the outputs of  $NOT_3$ ,  $NOR_2$  and  $NOT_1$  which are the inputs of  $NOT_3$ ,  $NOR_2$  and  $NOR_1$ , respectively.

get fully lock state and to release locking state of the SMFP-LD at given wavelength detuning have not been considered in detail.

In this paper, we analyzed input power and detuning wavelength requirements to injection-lock SMFP-LD and released SMFP-LD's locking state, and we applied those principles to demonstrate a  $2\times4$  AOAD using single- and multi-input injection-locking properties in SMFP-LD. Since SMFP-LD has self-locking mode, it does not need additional probe beam, which is required in other optical technologies [5], [6]. Hence, the proposed AOAD using SMFP-LD has several advantages such as simple in configuration, power and cost efficient, and cascadable structure.

## 2. Operation Principle

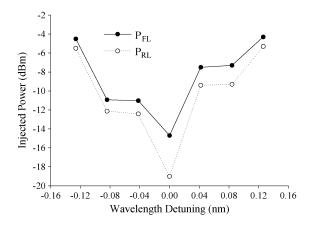

The proposed decoder operation is based on the single-input and multi-input injection-locking properties of SMFP-LDs, in which the self-locked mode (dominant mode) is suppressed when the single-input beam or multi-input beams is/are injected with proper input power and wavelength detuning [7]. In addition, the cascading property of SMFP-LDs also plays a crucial role for the implementation of AOAD. From the block diagram in Fig. 1, we can observe that AOAD is composed of several logic gates (NOT, NOR, and NAND), which are connected together to get the desired logic functions. The NOT and NOR gates work on single-input injection-locking principle in which power of single input at logic "1" is enough to suppress the dominant mode, whereas the NAND gate works on multi-input injection-locking principle, which states that the dominant mode will be suppressed only when all the inputs are logic "1" [8]. In multi-input injection-locking, the total input power of N injected beams is set in such a way that the dominant mode of SMFP-LD is suppressed only when all N inputs are logic "1", otherwise (one or more beam is/are logic "0") it is not suppressed. Since logic gates NOT, NOR, and NAND inside the AOAD are connected in cascading order, it is also possible to connect the AOAD in cascading order to make the desired complex functions. The cascadable feature can be obtained due to the fact that SMFP-LDs can be connected serially if input power and wavelength are controlled and matched properly for injection locking. In general, the locking strength of the input beam and hence the suppression of dominant mode is dependent on two parameters, i.e., wavelength detuning range and input power, which are related to each other. Lower detuning requires lower injected power for injection locking, and higher wavelength detuning needs higher input power. However, too small wavelength detuning may cause unstable locking. The relationship between wavelength detuning and injection locking is experimentally measured, as shown in Fig. 2. The change in temperature will shift the dominant mode of the SMFP-LD, which can be considered as advantage as it provides wavelength tunability of SMFP-LD. To maintain the fixed dominant mode, the SMFP-LD was kept firmly by using

Fig. 2. Required power to get fully lock state (PFL) and to release locking state (PRL) of the SMFP-LD at given wavelength detuning.

TABLE 1

Truth table of an AOAD

| $C_0$ | $c_1$ | <i>Y</i> <sub>0</sub> | <i>Y</i> <sub>1</sub> | <i>Y</i> <sub>2</sub> | <i>Y</i> <sub>3</sub> |

|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|

| 0     | 0     | 1                     | 0                     | 0                     | 0                     |

| 0     | 1     | 0                     | 1                     | 0                     | 0                     |

| 1     | 0     | 0                     | 0                     | 1                     | 0                     |

| 1     | 1     | 0                     | 0                     | 0                     | 1                     |

commercially available 4-pin coaxial pigtailed package, and its temperature was precisely controlled by using commercially available thermal electric cooler (TEC), which has the stability guarantee of less than 0.01 °C. Table 1 shows the truth table of AOAD, in which the outputs  $Y_0$ ,  $Y_1$ ,  $Y_2$ , and  $Y_3$  are logic "1" only when the input logic combination  $C_0$  and  $C_1$  is set at (0,0), (0,1), (1,0), and (1,1), respectively. All other combinations of inputs should provide the logic "0" at respective outputs. The Boolean expressions for output ports  $Y_0$ ,  $Y_1$ ,  $Y_2$ , and  $Y_3$  with inputs  $C_0$  and  $C_1$  can be written as  $Y_0 = \overline{C_0 + C_1}$ ,  $Y_1 = \overline{C_0 + Y_6} = \overline{C_0 + \overline{C_1}}$ ,  $Y_2 = \overline{Y_5 + C_1} = \overline{C_0} + \overline{C_1}$ , and  $Y_3 = \overline{Y_4} = \overline{C_0}\overline{C_1} = C_0C_1$ , and the corresponding expressions using logic gates are  $Y_0 = NOR(C_0, C_1)$ ,  $Y_1 = NOR(C_0, NOT(C_1))$ ,  $Y_2 = NOR(NOT(C_0), C_1)$ , and  $Y_3 = NOT(NAND(C_0, C_1)) = AND(C_0, C_1)$ . Hence, the experimental setup of the AOAD can be constructed, as shown in Fig. 3.

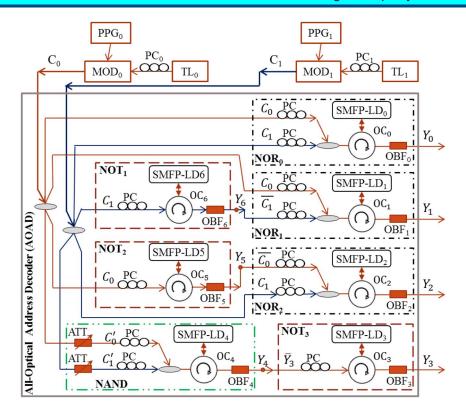

In Fig. 3,  $C_0$ ,  $C_1$ ,  $\overline{C_0}$ ,  $\overline{C_1}$ ,  $Y_0$ ,  $Y_1$ ,  $Y_2$ ,  $Y_3$ , and  $Y_4$  have wavelengths  $\lambda_{C_0}$ ,  $\lambda_{C_1}$ ,  $\lambda_5$ ,  $\lambda_6$ ,  $\lambda_0$ ,  $\lambda_1$ ,  $\lambda_2$ ,  $\lambda_3$ , and  $\lambda_4$ , respectively. To get desired logical functions, power, wavelength detuning, and polarization of  $C_0$ ,  $C_1$ ,  $\overline{C_0}$ ,  $\overline{C_1}$ , and  $Y_4$  are controlled properly by tuning the corresponding bias current, temperature, and polarization controller in such a way that, in the case of output  $Y_0$ , the SMFP-LD0 is fully locked when either  $C_0$  or  $C_1$  is logic "1". Under such condition, the SMFP-LD0 is also locked when both  $C_0$  and  $C_1$  are logic "1". In general, the self-locking mode of SMFP-LD0 (at  $\lambda_0$ ) is suppressed when  $(C_0, C_1)$  is (0,1), (1,0), or (1,1) and not suppressed when both  $C_0$  and  $C_1$  are logic "0". Hence, the output  $Y_0$  has a logic function of NOR gate. In the case of output  $Y_1$ , the self-locking mode of SMFP-LD1 (at  $\lambda_1$ ) is suppressed when  $(C_0, \overline{C_1})$  is (0,1), (1,0), or (1,1) and not suppressed when  $(C_0, \overline{C_1})$  is (0,0). When  $C_1$  is logic "1", the SMFP-LD6 is fully locked and there is logic "0" at output  $Y_6$  ( $\overline{C_1}$  at wavelength  $\lambda_6$ ). In other words,  $Y_1$  is logic "0" when  $(C_0, C_1)$  is (0,0), (1,1), or (1,0) and is logic "1" when  $(Y_5, C_1)$  is (0,1), (1,0), or (1,1) and is logic "1" when  $(C_0, C_1)$  is (0,0). In other words,  $Y_2$  is logic "0" when  $(C_0, C_1)$  is (0,1), (1,0), or (1,1) and is logic "1" when  $(C_0, C_1)$  is (1,0). In

Fig. 3. Experimental setup of a  $2\times4$  AOAD where, TL: Tunable Laser, OBF: Optical Bandpass Filter, PC: Polarization Controller, OC: Optical Circulator, MOD: Modulator, PPG: Pulse Pattern Generator, ATT: Optical Attenuator.

the case of output  $Y_3$ , the power of  $C_0$ ,  $C_1$ , and  $Y_4$  are adjusted so that the SMFP-LD<sub>3</sub> is not suppressed when  $(C_0, C_1)$  is (0,0), (0,1), or (1,0) (the power of single-input beam is not enough to lock the SMFP-LD<sub>3</sub>), and the SMFP-LD<sub>3</sub> is fully locked when  $(C_0, C_1)$  is (1,1) (multi-input injection-locking). In other words,  $Y_4$  is logic "0" when only  $(C_0, C_1)$  is (1,1) and is logic "1" for all other three cases (NAND gate). Hence,  $Y_3$  is logic "1" only when  $(C_0, C_1)$  is (1,1) and logic "0" when  $(C_0, C_1)$  is (0,0), (0,1), or (1,0) (AND gate). Finally, the AOAD is realized under the principle of single-input and multi-input injection-locking properties of SMFP-LD. All the logic functions are verified to match with the truth table in Table 1.

# 3. Experimental Setup and Results

Fig. 3 shows the experimental setup for AOAD using injection-locking property of SMFP-LD. The threshold current, working current, and working temperature of SMFP-LD $_0$  to SMFP-LD $_6$  are (9 mA, 12 mA, 13.9 °C), (11 mA, 15 mA, 26.3 °C), (11 mA, 15 mA, 26.3 °C), (9 mA, 12 mA, 13.9 °C), (11 mA, 15 mA, 26.3 °C), (13 mA, 19 mA, 13.5 °C), and (12 mA, 16 mA, 13.5 °C), respectively. Under those working conditions, SMFP-LDs have the dominant modes at  $\lambda_0$  (1543.44 nm),  $\lambda_1$  (1538.76 nm),  $\lambda_2$  (1538.76 nm),  $\lambda_3$  (1543.44 nm),  $\lambda_4$  (1538.76 nm),  $\lambda_5$  (1548.00 nm), and  $\lambda_6$  (1544.52 nm), respectively. Two input light beams from TL $_0$  and TL $_1$  are set at the wavelengths of  $\lambda_{C_0}$  (1550.48 nm) and  $\lambda_{C_1}$  (1552.80 nm). The polarization controllers PC $_0$  and PC $_1$  were used to minimize the polarization-dependent loss in the Mach–Zehnder modulator, whereas other PCs are used to get maximum possible TE optical power injected into SMFP-LDs. Due to injection-locking property of FP-LD, the more TE power is injected into the SMFP-LD, the more suppression of the SMFP-LD's side modes and the higher power at the injected mode. With TM input beams, FP-LD shows absorption phenomena that can be used for the demonstration of the positive logic units such as AND, OR, and others [10]. Optical bandpass filters (OBFs) are used to pass only desired output wavelengths at

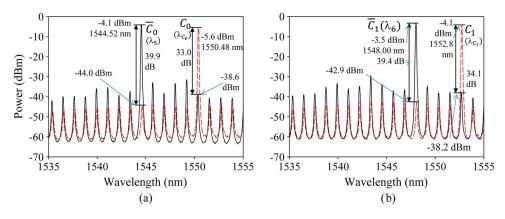

Fig. 4. Output spectra of the NOT<sub>1</sub> (SMFP-LD<sub>6</sub>) and NOT<sub>2</sub> (SMFP-LD<sub>5</sub>) gates of the AOAD.

the outputs. SMFP-LD $_0$  to SMFP-LD $_3$  and SMFP-LD $_5$  to SMFP-LD $_6$  work under the principle of single-input injection-locking, in which power of single-input beam is enough to suppress the dominant mode of SMFP-LD; however, SMFP-LD $_4$  works on multi-input injection-locking, in which power of single-input beam is not enough to suppress the dominant mode, i.e., two input beams are required for the SMFP-LD $_4$ . The input light beams are modulated with 10-Gb/s non-return-to-zero pseudorandom bit sequences of  $2^{31}-1$  that are generated from an Anritsu MP1763B pulse pattern generator.

To know the dependency of required injected power to fully lock ( $P_{FL}$ ) an SMFP-LD and to release ( $P_{RL}$ ), the SMFP-LD's locking state at given wavelength detuning, one side mode was selected and the input wavelength was tuned around the chosen side mode, as shown in Fig. 2. In this figure, the negative wavelength detuning corresponds to the case input wavelength that is smaller than the side mode wavelength. We found that the required powers to fully lock the SMFP-LD and to release its locking state in the experiments are about -7.5 and -9.3, respectively, given that the wavelength detuning is about 0.04 nm to 0.08 nm (their were not significantly different in required powers to lock and to release the SMFP-LD in the experiment).

Fig. 4 shows the spectra of the SMFP-LD<sub>5</sub> ( $\lambda_5$ ) (a) and SMFP-LD<sub>6</sub> ( $\lambda_6$ ) (b), which work as the NOT gates with the single-input  $C_0$  and  $C_1$ , respectively. Chosen side modes' wavelengths are 1550.44 and 1552.72 nm, which are corresponding to the wavelength detunings of 0.04 and 0.08 nm. The measured powers of inputs  $C_0$  and  $C_1$  before the circulators  $OC_5$  and  $OC_6$  are -4.9 and -5.1 dBm, respectively, which are greater than the required power (-7.5 dBm) to fully lock the corresponding SMFP-LDs. When  $C_0$  is logic "0" (-38.6 dBm, black solid line), output  $\overline{C_0}$  is logic "1" (-4.1), and when  $C_0$  is logic "1" (-5.6 dBm, measured by OSA, red dash line), output  $\lambda_6$  ( $\overline{C_0}$ ) is logic "0" (-44 dBm). Similarly, when  $C_1$  is logic "0" (-38.2 dBm, black solid line), output  $\overline{C_1}$  is logic "1"(-3.5 dBm), and when  $C_1$  is logic "1" (-4.1 dBm, red dash line), output  $\lambda_5$  ( $\overline{C_1}$ ) is logic "0" (-42.9 dBm).

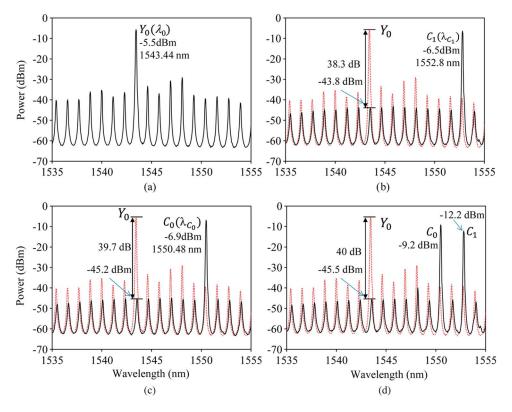

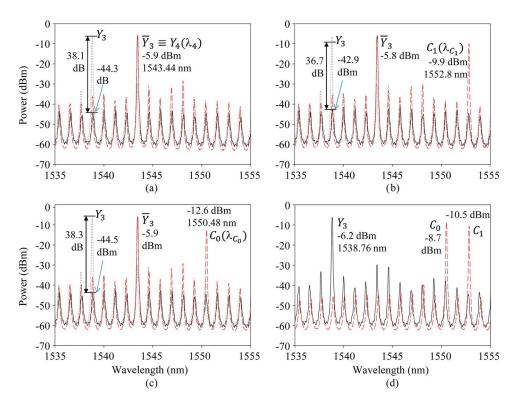

Fig. 5 shows the output spectra of the SMFP-LD<sub>0</sub>,  $Y_0$  before the filter OBF<sub>0</sub> when  $(C_0, C_1)$  is (a) (0,0); (b) (0,1); (c) (1,0); and (d) (1,1), respectively. The chosen side modes' wavelengths are 1550.44 and 1552.76 nm, which are corresponding to wavelength detunings of 0.04 and 0.04 nm. Because powers of inputs  $C_0$  and  $C_1$  at logic "1", measured before OC<sub>1</sub>, are -4.9 and -5.1 dBm, respectively, either power of  $C_0$  or  $C_1$  is enough to fully lock the SMFP-LD<sub>0</sub> when  $C_0$  or  $C_1$  is logic "1", and the locking state is released when both of them are logic "0". Indeed, when both  $C_0$  and  $C_1$  are logic "0", there is no input beam injected into the SMFP-LD<sub>0</sub> and the only spectrum of the SMFP-LD<sub>0</sub> is observed at output  $Y_0$ , as shown in Fig. 5(a). Hence, the self-locked mode at wavelength  $\lambda_0$  (1543.44 nm) is not suppressed or, in other words,  $Y_0$  has logic high (logic "1") in this case. When  $C_0$  is logic "0" and  $C_1$  logic "1", the power of input beam  $C_1$  is enough to lock the SMFP-LD<sub>0</sub>, as shown in Fig. 5(b) (solid black). The contrast ratio (CR) is about 38.3 dB compared between with and without input  $C_1$  to the SMFP-LD. Similarly, the SMFP-LD is fully locked with a

Fig. 5. Output spectra at the output port  $Y_0$  of the AOAD in cases  $(C_0, C_1, Y_0)$  are (a) (0,0,1), (b) (0,1,0), (c) (1,0,0), and (d) (1,1,0), respectively.

CR of about 29.7 and 40 dB when  $(C_0, C_1)$  is (1,0) and (1,1), respectively. In conclusion, the output  $Y_0$  is logic "1" only when  $(C_0, C_1)$  is (0,0).

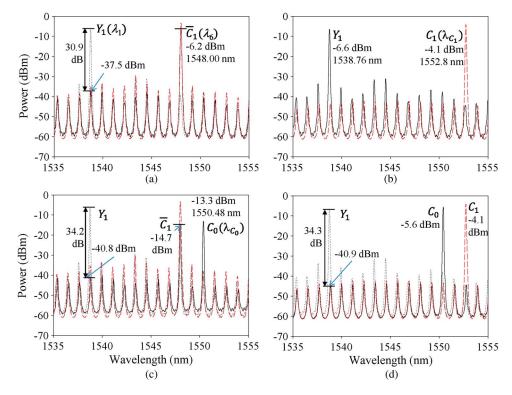

In the case of output  $Y_1$ , since the SMFP-LD<sub>6</sub> is used as the NOT<sub>1</sub> gate to invert the input signal  $C_1$ , required inputs' logic states are changed, as compared with the case output  $Y_0$ , to get the output  $Y_1$  to be logic "1". Indeed, Fig. 6 shows the spectra before filters OBF<sub>1</sub> (black solid line) and OBF<sub>6</sub> (red dot line) when  $(C_0, C_1)$  is (a) (0,0); (b) (0,1); (c) (1,0); and (d) (1,1), respectively, and the spectrum of the SMFP-LD<sub>1</sub> without any injection (black dot line). The chosen side modes' wavelengths with respect to the inputs  $C_0$  and  $\overline{C_1}$  are 1547.96 and 1550.40 nm, which are corresponding to wavelength detunings of 0.04 and 0.08 nm, respectively. The powers of inputs  $C_0$ and  $\overline{C_1}$  measured before OC<sub>1</sub> are -4.9 and -5.2 dBm, respectively. Hence, all the modes of SMFP-LD<sub>1</sub> are fully suppressed when either  $C_0$  or  $\overline{C_1}$  is logic "1", and the locking state of SMFP-LD<sub>1</sub> is released only when both  $C_0$  and  $\overline{C_1}$  are logic "0". Fig. 6(a) shows that when both  $C_0$  and C<sub>1</sub> are logic "0", there is no input beam injected into the SMFP-LD<sub>6</sub> and the self-locked mode of the SMFP-LD<sub>6</sub> is not suppressed; hence, C<sub>1</sub> is logic "1", which causes SMFP-LD<sub>1</sub> to be locked fully at wavelength  $\lambda_6$ . Therefore,  $Y_1$  is logic "0". The power of the side mode at  $\lambda_2$  (1538.76 nm) is about -37.5 dBm, and the CR is about 30.9 dB. When  $C_0$  is logic "0" and  $C_1$  is logic "1" [see Fig. 6(b)], the SMFP-LD<sub>5</sub> is locked by  $C_1$ ; therefore,  $\overline{C_1}$  is logic "0". The self-locked mode at wavelength  $\lambda_2$ (1538.76 nm) is not suppressed or, in other words,  $Y_1$  is logic "1". When  $C_0$  is logic "1" and  $C_1$  is logic "0" [see Fig. 6(c)], the SMFP-LD<sub>6</sub> is not locked by the input  $C_1$ ; therefore,  $\overline{C_1}$  is logic "1". Hence, the SMFP-LD<sub>1</sub> is locked by both inputs  $C_0$  and  $\overline{C_1}$ , which cause the output  $Y_1$  to be logic "0". The CR is about 34.2 dB compared to SMFP-LD<sub>1</sub> when there is no input. In case  $(C_0, C_1)$  is (1,1), the SMFP-LD<sub>5</sub> is fully locked by the input  $C_1$ , which causes the output  $\overline{C_1}$  to be logic "0"; therefore, the SMFP-LD<sub>2</sub> is injection-locked by only input  $C_0$  and the output  $Y_1$  is logic "0" with a CR of about 34.3 dB. In conclusion, the output  $Y_1$  is at logic high with only one case  $(C_0, C_1)$  is (0,1).

Fig. 6. Output spectra at the output port  $Y_1$  of the AOAD in cases  $(C_0, C_1, Y_1)$  are (a) (0,0,0), (b) (0,1,1), (c) (1,0,0), and (d) (1,1,0), respectively.

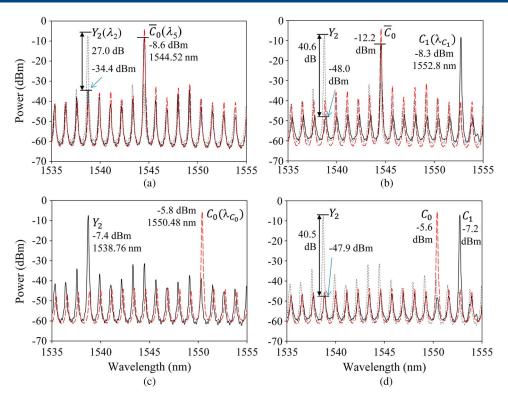

In the case of output  $Y_2$ , the SMFP-LD<sub>5</sub> is used as a NOT<sub>2</sub> gate to invert the input signal  $C_0$  (1550.48 nm). Fig. 7 shows the spectra before OBF<sub>2</sub> (black solid line), the spectra before the filter at output  $\overline{C_0}$  (1544.52 nm) of the SMFP-LD<sub>5</sub> (red dot line) when  $(C_0, C_1)$  is (a) (0,0); (b) (0,1); (c) (1,0); and (d) (1,1), respectively, and the spectrum of the SMFP-LD<sub>2</sub> without any injection (black dot line). Powers of inputs  $\overline{C_0}$  and  $C_1$  measured before OC<sub>3</sub>, when  $\overline{C_0}$  and  $C_1$  are logic "1", are -4.8 and -5.1 dBm, respectively. Due to the similarity between this part and the previous  $Y_0$  and  $Y_1$  parts, we just show some specific values that belong to this part. The chosen side modes' wavelengths are 1544.44 and 1550.40 nm, which are corresponding to wavelength detunings of 0.08 and 0.08 nm. The output  $Y_2$  is logic high only when  $(\overline{C_0}, C_1)$  is (0,0) or  $(C_0, C_1)$  is (1,0), in other words. In other cases of inputs  $(C_0, C_1)$  ((a) (0,0), (b) (0,1), and (d) (1,1)), the outputs of  $Y_2$  are logic low because the SMFP-LD<sub>2</sub> is locked by  $\overline{C_0}$  or/and  $C_1$ . CRs are about 27.0, 40.6, and 40.5 dB in the cases of (0,0), (0,1), and (1,1), respectively.

Fig. 8 shows the spectra before the filter OBF<sub>3</sub> (black solid line), the spectra before the filter OBF<sub>4</sub> (red dash line) when  $(C_0, C_1)$  is (a) (0,0); (b) (0,1); (c) (1,0); and (d) (1,1), respectively, and the spectrum of the SMFP-LD<sub>3</sub> without any injection (black dot line). The chosen side modes of the SMFP-LD<sub>4</sub> have wavelengths 1550.44 and 1552.76 nm and wavelength detunings are 0.04 and 0.04 nm, respectively. Powers of inputs  $C_0$  and  $C_1$  are attenuated to about -10.1 dBm  $(C_0')$  and -10.3 dBm  $(C_1')$ , respectively, by using optical attenuators, which are lower than the released power (-9.6 dBm) and are not enough to lock the SMFP-LD<sub>4</sub>  $(\lambda_4 = 1543.44)$ . Only one input  $C_0'$  or  $C_1'$  cannot lock the SMFP-LD<sub>4</sub>; however, the total power of  $C_0'$  and  $C_1'$ , about -7.2 dBm, is enough to fully lock the SMFP-LD<sub>4</sub>. Further, the output power of the SMFP-LD<sub>4</sub> measured at  $Y_4$  is about -6.9 dBm (enough to fully lock the SMFP-LD<sub>3</sub>) corresponding to the side mode wavelength of SMFP-LD<sub>3</sub> that is 1543.40 nm (0.04-nm wavelength detuning) in case  $(C_0, C_1)$  is (0,0), (0,1), and (1,0), respectively, and is less than -40 dBm (not enough to fully lock the SMFP-LD<sub>3</sub>) in case  $(C_0, C_1)$  is (1,1). Fig. 8(a) shows that when both  $C_0$  and  $C_1$  are logic "0", there is no input beam

Fig. 7. Output spectra at the output port  $Y_2$  of the AOAD in cases  $(C_0, C_1, Y_2)$  are (a) (0,0,0), (b) (0,1,0), (c) (1,0,1), and (d) (1,1,0), respectively.

Fig. 8. Output spectra at the output port  $Y_3$  of the AOAD in cases  $(C_0, C_1, Y_3)$  are (a) (0,0,0), (b) (0,1,0), (c) (1,0,0), and (d) (1,1,1), respectively.

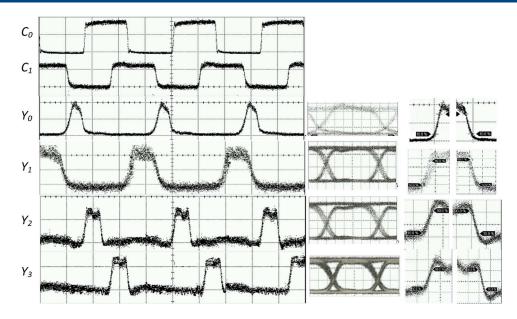

Fig. 9. Waveforms, eyes diagrams and rising/falling edges of the AOAD at output ports  $Y_0$ ,  $Y_1$ ,  $Y_2$   $Y_3$ ; measured with the time scale of 500 ps/div, 20 ps/div and, 100 ps/div respectively.

injected into the SMFP-LD<sub>4</sub> and the self-locked mode of the SMFP-LD<sub>4</sub> is not suppressed; hence,  $Y_4$  (at  $\lambda_4$  1543.44 nm) is logic "1", which causes SMFP-LD<sub>3</sub> to be fully locked at wavelength  $\lambda_4$ . Therefore,  $Y_3$  is logic "0". The power of the side mode at  $\lambda_3$  (1538.8 nm) is about -44.3 dBm, and the CR is about 38.1 dB.

When  $(C_0, C_1)$  is (0,1) and (1,0) [see Fig. 8(b) and (c)], the SMFP-LD<sub>4</sub> is not locked or the self-locked mode at wavelength  $\lambda_4$  is not suppressed; in other words, the powers of  $C_0$  and  $C_1$  are adjusted in such a way that single input power is not enough to lock the SMFP-LD<sub>4</sub>. Hence, the SMFP-LD<sub>3</sub> is locked by  $Y_4$  (considered as  $\overline{Y_3}$ ), which causes the output  $Y_3$  to be logic "0". The CRs are about 36.7 and 38.3 dB, respectively, compared to SMFP-LD<sub>3</sub> when there is no input. In case  $(C_0, C_1)$  is (1,1) in Fig. 8(d), the SMFP-LD<sub>4</sub> is locked by the combined powers of both  $C_0$  and  $C_1$ , which results in logic "0" at output  $Y_4$ . Hence, the SMFP-LD<sub>3</sub> is not locked and  $Y_3$  is logic "1". In conclusion, the output  $Y_3$  is logic "1" with only the case  $(C_0, C_1)$  is (1,1). In conclusion, the proposed AOAD using the injection-locking property of SMFP-LD is successfully verified in the spectrum domain for all the cases of inputs  $(C_0, C_1)$ .

Fig. 9 shows the output waveforms, eyes diagrams, and rising–falling times at the corresponding outputs of the AOAD. Two input data ( $C_0$  and  $C_1$ ) were modulated with 16-bit NRZ signals at 10 Gb/s. The PRBS signal length was  $2^{31}-1$ . From the output waveforms, we can see that  $Y_0$  has logic "1" only when both inputs are at logic "0",  $Y_1$  has logic "1" only when  $C_0=0$  and  $C_1=1$ ,  $Y_2$  is logic "1" only when  $C_0=1$  and  $C_1=1$ . For all other conditions, the corresponding outputs are logic "0", which are matched with the results in the spectrum domain and prove the logic function of the  $2\times 4$  AOAD. The extinction ratios of outputs' eyes diagrams measured at ports  $Y_0$ ,  $Y_1$ ,  $Y_2$ , and  $Y_3$  are 10.94, 12.12, 10.8, and 10.68 dB, and the corresponding rising–falling times of outputs' waveforms are about (45,46), (47,43), (43,49), and (47,47) ps. The waveforms of all cases are clear enough to have good BER, as shown in Fig. 10.

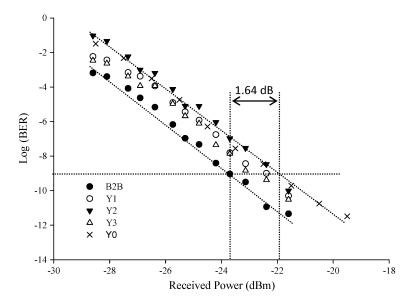

Fig. 10 shows the BER measurements of AOAD. All the outputs have no noise floor up to BER of  $10^{-12}$  at the data rate of 10 Gb/s. The highest BER power penalty is measured about 1.64 dB for output port  $Y_2$ . The little difference in power penalty between different outputs of the decoder may come from the differences in polarization controller and nonidentical wavelength detuning.

Fig. 10. BER and power penalty measurements for the AOAD.

## 4. Discussion and Conclusion

The key issues with the implementation of AOAD are single-input and multi-input injection-locking properties of SMFP-LDs and the cascading of different logic gates to form the desired functional device. Hence, proper power management and wavelength detuning should be considered carefully. Since injection locking is dependent on wavelength detuning, wavelength matching is considered as one of the critical parameters. However, this can be overcome with the management of input beam powers that are injected to respective SMFP-LDs. Since SMFP-LDs are used, external probe beams are not required as needed in conventional FP-LDs and SOAs. In addition, the maximum bias current for the SMFP-LDs that we have used is below 19 mA, which is low compared with that of other optical technologies.

In this paper, we have proposed and experimentally demonstrated an AOAD using an SMFP-LD. The decoder has clear spectra, waveform, eyes diagram, reasonable rising–falling time, and BER for all the outputs. The output spectra and waveforms satisfy the desired logic functions of an address decoder, as shown in the truth table in Table 1. Since SMFP-LD is made from cheap commercial FP-LD, which requires small bias current, and the scheme using SMFP-LD does not require additional probe beam and associated components to have injection locking, the proposed scheme is power and cost efficient and has simple configuration features compared with other technologies, including commercially available FP-LD technology. The experiment is carried out with a data rate of 10 Gb/s; however, the speed can be increased to a higher data rate [11]. The proposed AOAD can be used for all-optical control unit, all-optical address decoding, label swapping based on the time-to-wavelength converter [12], and other signal processing. Since several components such as optical waveguide [13], polarization controller [14], circulator [15], coupler [16], [17], and tunable filter [18] have been successfully integrated as reported in respective references [13]–[18], the AOAD can be integrated after finding the proper solution for SMFP-LD integration, which we are considering in near future works.

### **Acknowledgment**

The authors are deeply thankful to all interested persons at MKE and the Korea Evaluation Institute of Industrial Technology (KEIT).

### References

- [1] P. Horowitz and W. Hill, The Art of Electronics, 2nd ed. Cambridge, MA, USA: Cambridge Univ. Press, 1989, p. 685 766.

- [2] L. Ladouceur, H. Wang, A. S. Garg, and K. Bergman, "Low-power, transparent optical network interface for high bandwidth off-chip interconnects," *Opt. Exp.*, vol. 17, no. 8, pp. 6550–6561, Apr. 2009.

- [3] F. J. Levi, "Optical interconnects in systems," Proc. IEEE, vol. 88, no. 6, pp. 750-757, Jun. 2000.

- [4] Y. Wang, X. Zhang, J. Dong, and D. Huang, "Simultaneous demonstration on all-optical digital encoder and comparator at 40 Gb/s with semiconductor optical amplifiers," *Opt. Exp.*, vol. 15, no. 23, pp. 15 080–15 085, Nov. 2007.

- [5] M. R. Uddin, J. S. Cho, and Y. H. Won, "Single to multi-wavelength conversion using gain modulation in an FP-LD," *IEICE Electron. Exp.*, vol. 5, no. 23, pp. 1024–1029, Dec. 2008.

- [6] M. R. Uddin, J. S. Cho, and Y. H. Won, "All-optical multicasting NOT and NOR logic gates using gain modulation in an FP-LD," *IEICE Electron. Exp.*, vol. 6, no. 2, pp. 104–110, Jan. 2009.

- [7] Y. D. Jeong, Y. H. Won, S. O. Choi, and J. H. Yoon, "Tunable single-mode Fabry-Pérot laser diode using a built-in external cavity and its modulation characteristics," *Opt. Lett.*, vol. 31, no. 17, pp. 2586–2587, Sep. 2006.

- [8] B. Nakarmi, M. R. Uddin, T. Q. Hoai, and Y. H. Won, "Demonstration of all-optical NAND gate using single-mode Fabry-Pérot laser diode," *IEEE Photon. Technol. Lett.*, vol. 23, no. 4, pp. 236–238, Feb. 2011.

- [9] B. Nakarmi, M. R. Uddin, T. Q. Hoai, and Y. H. Won, "A simple controlled all-optical ON/OFF switch using gain modulation in single mode FP-LD," *IEEE Photon. Technol. Lett.*, vol. 23, no. 4, pp. 212–214, Feb. 2011.

- [10] H. Yoo, Y. D. Jeong, and Y. H. Won, "All-optical wavelength conversion using absorption modulation of an injection-locked Fabry–Perot laser diode," *IEEE Photon. Technol. Lett.*, vol. 16, no. 2, pp. 536–538, Feb. 2004.

- [11] E. K. Lau, H. K. Sung, and M. C. Wu, "Frequency response enhancement of optical injection-locked lasers," *IEEE J. Quantum Electron.*, vol. 44, no. 1, pp. 90–99, Jan. 2008.

- [12] M. C. Cardakli, S. Lee, and A. E. Willner, "Reconfigurable optical packet header recognition and routing using time-to-wavelength mapping and tunable fiber Bragg gratings for correlation decoding," *IEEE Photon. Technol. Lett.*, vol. 12, no. 5, pp. 552–554, May 2000.

- [13] W. S. Choi, J. H. Jang, B. A. Yu, Y. L. Lee, W. Zhao, J. W. Bae, and I. Adesida, "Low loss high mesa optical waveguides based on InGaAsP/InP heterostructures," *J. Nanosci. Nanotechnol.*, vol. 6, no. 11, pp. 3562–3566, Nov. 2006.

- [14] J. J. G. M. van der Tol, L. M. Augustin, U. Khalique, and M. K. Smit, "Polarization control and its application to waveguide devices," in *Proc.* 13th MicroOpt. Conf., 2007, vol. 13, pp. 48–51.

- [15] T. Zaman, X. Guo, and R. J. Ram, "Integrated optical circulator in InP," in Proc. CLEO, 2005, vol. 2, pp. 1321-1323

- [16] J. S. Parker, P. R. A. Binetti, Y. J. Hung, E. J. Norberg, and L. A. Coldren, "RIE lag directional coupler based integrated InGaAsP/InP ring mode-locked laser," in *Proc. DRC*, 2011, vol. 69, pp. 263–264.

- [17] J. H. Ahn, K. R. Oh, J. S. Kim, S. Lee, W. Kim, H. M. Pyun, and H. M. Park, "Uniform and high coupling efficiency between InGaAsP-InP buried heterostructure optical amplifier and monolithically butt-coupled waveguide using reactive ion etching," *IEEE Photon. Technol. Lett.*, vol. 8, no. 2, pp. 200–202, Feb. 1996.

- [18] B. W. Tilma, Y. Jiao, P. J. V. Veldhoven, J. Peter, B. Smalbrugge, H. P. M. M. Ambrosius, P. J. Thijs, X. J. M. Leijtens, R. Notzel, M. K. Smit, and E. A. J. M. Bente, "InP-based monolithically integrated tunable wavelength filters in the 1.6–1.8 μm wavelength region for tunable laser purposes," *J. Lightwave Technol.*, vol. 29, no. 18, pp. 2818–2830, Sep. 2011.