# Reconfigurable Optical Directed Logic Circuits Based on Mode Division Multiplexing Technology

Mingrui Yuan, Yiyang Li, Huifu Xiao, Xudong Zhou, Pengfei Cao<sup>®</sup>, Lin Cheng<sup>®</sup>, Guanghui Ren<sup>®</sup>, Qinfen Hao<sup>®</sup>, Jiuzhi Xue, Arnan Mitchell<sup>®</sup>, and Yonghui Tian<sup>®</sup>

Abstract—Reconfigurable optical directed logic circuits (RODLC) aim to perform arbitrary logic operations using the optical switch network, in which the electrical signals regarded as the logic operands are applied to the optical switch to control the propagation of light over time, and the logic operation results are obtained at the output ports of the optical switch network in the form of light. In this paper, a novel RODLC is proposed and experimentally demonstrated by utilizing an optical switch array with the prosperous optical mode division multiplexing (MDM) technology to perform arbitrary logic functions. As a proof of concept, a RODLC with two optical mode (de)multiplexers and twelve thermo-optic microring resonators on a silicon-on-insulator substrate is fabricated based on standard microfabrication technology. To demonstrate its reconfigurability to perform arbitrary logic functions, eight logic operations: NOT, AND, NAND, OR, NOR, XOR, XNOR, as well as one combination operation of four-operand, with the operation speed of 10 Kbps are successfully implemented as examples. The demonstrated RODLC characterized with reconfigurability, scalability, and ability for large-scale integration, will contribute to the flourishing development of optical computing and information processing in large-scale optical hybrid integrated circuits.

Manuscript received 28 March 2023; revised 21 April 2023; accepted 22 April 2023. Date of publication 25 April 2023; date of current version 4 May 2023. This work was supported in part by the National Key R&D Program of China under Grant 2022YFB2804202, in part by the National Natural Science Foundation of China under Grants 62075091 and 62205135, in part by the Open Research Fund of State Key Laboratory of Transient Optics and Photonics under Grant 2022M711443, in part by the Australian Research Council under Grant DP190102773, and in part by by Jiangsu Industrial Technology Research Institue. (*Corresponding author: Yonghui Tian.*)

Mingrui Yuan, Yiyang Li, Huifu Xiao, and Xudong Zhou are with the School of Physical Science and Technology, Lanzhou University, Lanzhou 730000, China (e-mail: yuanmr@lzu.edu.cn; liyiyang19@lzu.edu.cn; xi-aohf@lzu.edu.cn; zhouxd18@lzu.edu.cn).

Pengfei Cao and Lin Cheng are with the School of Information Science and Engineering, Lanzhou University, Lanzhou 730000, China (e-mail: caopf@lzu.edu.cn; chenglin@lzu.edu.cn).

Guanghui Ren and Arnan Mitchell are with the Integrated Photonics and Applications Centre, School of Engineering, RMIT University, Melbourne, VIC 3001, Australia (e-mail: guanghui.ren@rmit.edu.au; arnan.mitchell@rmit.edu.au).

Qinfen Hao is with the Institute of Computing Technology, Chinese Academy of Sciences, Beijing 100190, China (e-mail: haoqinfen@ict.ac.cn).

Jiuzhi Xue is with the Smart Liquid Crystal Technologies Company Limited, Changshu 215500, China, and also with the Jiangsu Industrial Technology Research Institute, Nanjing 210000, China (e-mail: jiuzhi.xue@jitri-lci.com).

Yonghui Tian is with the School of Physical Science and Technology, Lanzhou University, Lanzhou 730000, China, and also with the State Key Laboratory of Transient Optics and Photonics, Chinese Academy of Sciences, Xian 710119, China (e-mail: siphoton@lzu.edu.cn).

Digital Object Identifier 10.1109/JPHOT.2023.3270341

*Index Terms*—Optical logic operation, mode division multiplexing, optical switch, microring resonators.

## I. INTRODUCTION

PTICAL directed logic circuit is a promising information processing scheme that aims to perform various Boolean logic operations by applying electrical operands to the optical switch in the network to control its operation states, and the final operation results are directed to the output ports of the optical switch network in the form of light [1], [2], [3], [4], [5]. In the optical switch network, all the optical switches can be manipulated simultaneously, and the light can propagate in the network with high speed, therefore, optical directed logic possesses the advantages of low latency and large bandwidth in highly integrated on-chip optical information processing systems compared to conventional electrical logic [6]. As a result, this scheme is considered an attractive option for future high-speed and bit-rate optical computing, information encryption, optical networking systems, and highly integrated on-chip optical subsystems. In the recent few years, different types of independent optical directed logic gates such as XOR/XNOR [7], [8], OR/NOR [9], and their combinational logic devices such as full adders [10], Feynman gate [11], parity checker [12], directed priority encoder [13], automated logic synthesis [14], have been reported to meet particular application requirements in different situations. These logic devices have driven the development of electro-optic integrated systems, however, it is difficult for them to perform arbitrary logic operations that meet large and complex information processing requirements. To solve this problem, researchers have worked on developing reconfigurable optical directed logic circuits (RODLC) that can generate arbitrary logic functions [15], [16], [17], [18], [19], [20]. However, wavelength division multiplexing (WDM) technology was adopted to implement the sum of products calculation in those RODLC. Despite its remarkable flexibility, reconfigurability and ubiquity, multiple on-chip lasers to generate different wavelengths are required in the reported works to ensure proper logic operations, which will inevitably increase the difficulty and cost of the fabrication process [21].

Optical mode is another physical dimension of light that can be utilized for information processing [22], [23]. Different orthogonal modes at a single wavelength can be used as carriers to transmit information in the spatial dimension, thus providing a promising wavelength-division compatible solution for large

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

bandwidth and parallel information processing [24]. Based on the fact that the modes supported in the waveguide have different transmission properties, a device that implements five optical directed logic operations using a cascaded Mach-Zehnder structure has been proposed and demonstrated successfully in 2021 [25]. Such a device requires only one laser and has the advantage of simple structure and large bandwidth compared to those using WDM-based technology. Therefore, due to the advantages of reconfigurability, scalability, easy large-scale integration, simple fabrication process, and low cost [26], [27], [28], [29], [30], mode division multiplexing (MDM) technology is considered a promising solution for implementing multifunctional and complex optical logic circuits. Nevertheless, RODLC using MDM technology is still expected to accomplish arbitrary logic operations, including both fundamental and combinational logic.

In this paper, we propose and experimentally demonstrate a RODLC based on MDM to achieve multiple logic operations. To the best of our knowledge, it is the first time to demonstrate the RODLC to achieve arbitrary logic operations by utilizing MDM technology. Compared with the RODLC based on WDM technology in [19], [20], the proposed device only needs one working wavelength, which avoids the requirement of multiple lasers and greatly reduces the manufacturing cost. For proof of concept, the experiment of directed logic operation based on the thermo-optic effect of three optical modes is successfully presented. The proposed and demonstrated device is strongly believed to be a promising candidate for future optical information processing.

# II. DEVICE WORKING PRINCIPLE, DESIGN, AND FABRICATION

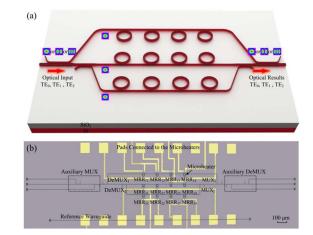

Generally speaking, an arbitrary logical function can be expressed as a combination of sum and product [16]. This means that any logic function Y can be written as  $Y = Y_1 + Y_1$  $Y_2 + \ldots + Y_m \ (m \ge 1)$ , where  $Y_m$  indicates the product of variables  $Y_m = a_1 \ \overline{a_2} a_3 \dots \overline{a_n} \ (n \ge 1)$ , and an opposite logic value of  $a_n$  is represented by  $\overline{a_n}$ . Based on this formulation, an MDM-based RODLC that can perform any logic operations, including fundamental and combinational logic, is proposed and experimentally demonstrated in this paper. An overview of the proposed device is illustrated in Fig. 1(a), which consists of (de)multiplexers (MUXs) and microring resonator (MRR) arrays. When the device is in operation, the higher-order  $(TE_m)$ modes in the multimode waveguide are demultiplexed to several TE<sub>0</sub> modes into the corresponding access waveguide, and then transmitted to the microring arrays for signal modulation to logical multiplication. After being modulated, the several TE<sub>0</sub> modes carried with preliminary calculated information are multiplexed into the multimode waveguide for logical addition. For the sake of simplicity, we consider the case of three optical modes. The micrograph in Fig. 1(b) shows the fabricated device that contains the RODLC and two auxiliary mode (de)MUXs. The auxiliary (de)MUXs are fabricated to generate  $TE_0$ ,  $TE_1$  and TE2 modes. In the logic circuit, three optical modes are input into the multimode waveguide, and four MRRs are placed on the side of the access waveguides for coupling. Asymmetric directional

Fig. 1. (a) Schematic diagram and (b) micrograph of the proposed RODLC.

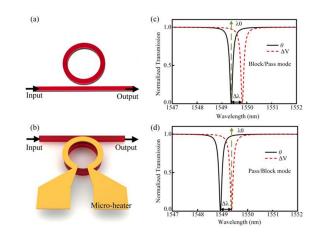

Fig. 2. (a) Optical switch consisting of an MRR and a bus waveguide. (b) Optical switch modulated by a micro-heater above. (c) Transmission spectra of the MRR optical switch operating in *block/pass* mode and (d) in *pass/block* mode.

couplers (ADCs) are adopted to make up mode (de)MUXs. The photonic circuit (excluding the electrical contact pads) has a total size of  $0.2 \text{ mm} \times 1.3 \text{ mm}$ .

As a basic structure of the RODLC, Fig. 2(a) shows an optical switch structure based on MRRs, which consists of a separate MRR and a bus waveguide. To control the working state of the optical switch, micro-heaters fabricated above the MRRs are used to modulate light by applying the electrical pulse sequences (EPS), which takes advantage of the thermo-optic effect principle (see Fig. 2(b)). The output logical result is directly affected by the state of each optical switch. In general, each optical switch has two different modes of operation. Fig. 2(c) and (d) illustrate the two modes, namely *block/pass* mode and *pass/block* mode, respectively. As shown in Fig. 2(c), the working wavelength is chosen at  $\lambda_0$ . If the resonant wavelength is exactly at  $\lambda_0$ , a low level of optical power (marked as logic '0') is obtained when a low level of EPS is applied to this MRR. And a high level of optical power (marked as logic '1') is obtained when a high level of EPS is applied. This operation mode is called *block/pass* mode, and the same logic value as EPS is obtained in the output. If the resonant wavelength is less than  $\lambda_0$ , the state of affairs is

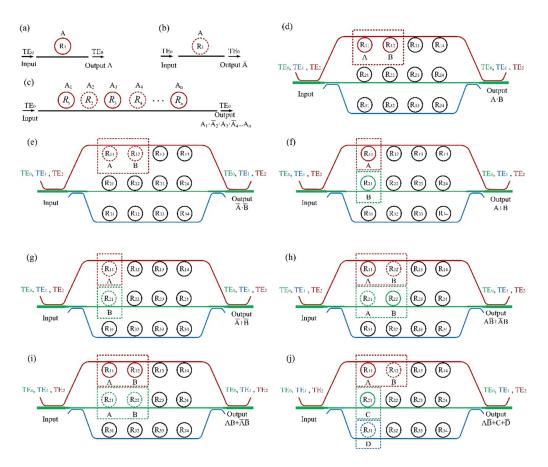

Fig. 3. Logic circuit diagrams of the device for (a) one MRR operating in *block/pass* mode for one optical mode input, (b) one MRR operating in *pass/block* mode for one optical mode input, (c) multiple MRRs operating in different working modes for one optical mode input, and (d)–(j) logic operations for the three mode inputs. The rings with the same color indicate that the MRRs are working in the same optical mode. The solid and dotted line rings indicate that the MRRs are working in block/pass mode and *pass/block* mode, respectively.

exactly the opposite of the above. The logic value opposite to EPS is obtained in the output, which is the so-called *pass/block* mode (see Fig. 2(d)).

Random combinations of the above two operation modes allow for arbitrary logical multiplication. As shown in Fig. 3, the logic functions implemented at the output depend entirely on the operation mode of each MRR. Supposing a bundle of the fundamental mode, a continuous wave (CW) of wavelength  $\lambda_0$  is coupled into the waveguide, we can obtain  $Y_1 = a_1$  from Fig. 3(a) and  $Y_2 = \overline{a_1}$  from Fig. 3(b). In Fig. 3(c), MRRs work in both block/pass mode and pass/block mode, so a logic function  $Y_3 = a_1 \ \overline{a_2} a_3 \overline{a_4} \dots a_n$  is obtained. Similarly, arbitrary logical multiplication is implemented by changing MRRs' operation modes and their number. However, it is significant to add up the results of multiple logic products modulated by EPS loaded on each row of MRRs. Here we propose utilizing MDM technology to achieve logical addition, which can avoid a series of problems caused by multiple laser wavelengths. ADCs are adopted to compose mode (de)MUXs due to the mode coupling principle. When the effective refractive index of a higher-order mode in the multimode waveguide is equal to the effective refractive index of TE<sub>0</sub> in an adjacent access waveguide, the so-called phase matching condition is met, and the mode coupling occurs [31]. Consequently, the higher-order mode in the multimode

waveguide is converted to  $TE_0$  of the adjacent access waveguide and continues to transmit forward, and vice versa. After being modulated by EPS loaded on MRRs, the TE<sub>0</sub> modes with the product calculation results are multiplexed to a multimode waveguide for logical addition. As shown in Fig. 3(d)-(j), the logic circuit contains three groups of MRRs, and the MRRs in the same operation group are multiplexed into the same working mode. Multi-mode optical signals with the modes of  $TE_0$ ,  $TE_1$  and  $TE_2$  are simultaneously coupled into the circuit and demultiplexed into different operation groups by the MDM technology. After performing simultaneous multiplication operations, these signals are multiplexed for additional operations to obtain the logical result  $Y = Y_1 + Y_2 + \ldots + Y_m$ , where  $Y_m$  indicates the product of arbitrary variables. It should be noted that the number of addition operations is determined by the number of input modes, and the number of operands within each multiplication operation is determined by the number of MRRs in the corresponding operation group. As with the Field Programmable Gate Array (FPGA), the resonant wavelengths of MRRs that are not used for logic operations can be tuned away from the circuit's working wavelength.

For the proposed RODLC, another key technology is to multiplex/demultiplex the individual modes with high accuracy, low loss, and low crosstalk. Here, the input optical signal contains three different modes  $TE_0$ ,  $TE_1$  and  $TE_2$  at the same wavelength, and the waveguide widths supporting the transmission of the three modes are 0.45  $\mu$ m, 0.93  $\mu$ m, and 1.42  $\mu$ m, respectively. The coupling lengths of the  $TE_1$  and  $TE_2$  mode (de)MUXs are 27  $\mu$ m and 34.5  $\mu$ m, and the adiabatic taper lengths between the bus waveguides of TE<sub>1</sub> mode and TE<sub>0</sub>, TE<sub>2</sub> mode are 150  $\mu$ m. The coupling distance of the ADCs in all (de)MUXs is designed to be 0.2  $\mu$ m. The radii of twelve MRRs are designed to be 10  $\mu$ m, the ring waveguide widths of MRRs are 0.45  $\mu$ m, and the gap between the straight and ring waveguides is 0.13  $\mu$ m. The center distance between each row of MRRs is designed to be 150  $\mu$ m, and the distance between two adjacent rows of MRRs is 100  $\mu$ m. For testing convenience, mode (de)MUXs are also designed on both sides of the device for the input and output of multimode signals. In addition, a straight reference waveguide is designed under the device to minimize process errors.

A circuit that can perform any logic operation with twelve operands is fabricated on a silicon-on-insulator (SOI) wafer. For the SOI substrate, the thickness of the buried oxide layer is 3  $\mu$ m and the thickness of the top silicon layer is 220 nm. The waveguide patterns are fabricated on ZEP520A resist using electron beam lithography (EBL), followed by complete etching of the waveguide using an inductively coupled plasma (ICP) etching process. Subsequently, plasma-enhanced chemical vapor deposition (PECVD) technology is employed to deposit a 2  $\mu$ m thick silicon dioxide layer on the structures [32]. Here, the thermo-optic scheme is used to modulate the MRR-based optical switches as a proof-of-principle, thereby reducing the complex device layer structure and simplifying the fabrication steps. The  $\Omega$ -shaped titanium micro-heater with a thickness of 100 nm is fabricated for the thermo-optical modulator using mask-less lithography (MLA150), electron beam evaporation deposition, and lift-off processes. 50  $\mu$ m wide gold nanowires used to connect the micro-heaters are deposited subsequently. Finally, a 500 nm thick layer of silicon dioxide is deposited to protect the open circuit.

### **III. RESULTS AND DISCUSSION**

A test system consisting of an amplified spontaneous emission (ASE) source, a tunable voltage source (TVS) and an optical spectrum analyzer (OSA) is used to characterize the performance of the fabricated logic circuit. CW light from the ASE is coupled to the input port of the device through a single-mode fiber, then coupled from the output port of the device to an output single-mode fiber, and finally reaches the OSA to get the output spectrum. The voltage is generated by TVS and loaded on the electrical contact pads of micro-heaters through a radio frequency wire connected with a GGB DC probe. The input and output of the optical signals in the chip are realized by grating couplers with an etched depth of 70 nm, a period of 640 nm, and a duty cycle of 0.5. Through the grating coupler, CW light can be coupled as a quasi-transverse electrical fundamental mode to the single-mode waveguide. Experimental results for the entire circuit show that the insertion loss of the straight waveguide is about 13.5 dB which includes the insertion loss of the grating couplers and the loss introduced during the alignment of the

coupling fiber in the experiment (about 6–7 dB for each end face). In the wavelength range of 1525–1565 nm, the transmission loss is about 1 dB for TE<sub>0</sub> and about 6.5 dB for TE<sub>1</sub> and TE<sub>2</sub>. The large insertion loss of TE<sub>1</sub> and TE<sub>2</sub> mode is owing to four times (de)multiplexing operations, thus introducing an extra 5.5 dB loss relative to TE<sub>0</sub> mode. By measuring the reference MUX-deMUX, the coupling loss of one (de)MUX is about 1.37 dB. As for MMRs, the fabrication process errors lead to differences in their resonant wavelengths and extinction ratios, nonetheless, all the extinction ratios are better than 23 dB for TE<sub>0</sub> and TE<sub>2</sub> input, respectively.

For the proposed three-mode logic circuit that can implement arbitrary logic operations with twelve operands, we demonstrate only partial logic operations with four operands as a verification. Here, we divide the twelve MMRs into three groups according to the different optical modes. The group corresponding to  $TE_0$  is composed of MRR<sub>11</sub>, MRR<sub>12</sub>, MRR<sub>13</sub>, and MRR<sub>14</sub>; the group corresponding to TE<sub>1</sub> is composed of MRR<sub>21</sub>, MRR<sub>22</sub>, MRR<sub>23</sub>, and MRR<sub>24</sub>; the group corresponding to TE<sub>2</sub> is composed of MRR<sub>31</sub>, MRR<sub>32</sub>, MRR<sub>33</sub>, and MRR<sub>34</sub>. Due to the reconfigurable characteristics of the device, each MRR can operate in either *block/pass* or *pass/block* modes, and thus the voltage loaded on each MRR is not unique. Here, the working wavelength is 1550 nm, and the modulation voltages required to modulate the resonant peak of each MRR from the initial position to the working wavelength are called compensation voltage  $V_{\rm c}$ . For MRRs operating in *block/pass* mode, the loaded low/high voltages are  $V_{\rm c}/2.36$  (V) (where  $V_{\rm c} < 2.36$  V), respectively, while for MRRs operating in pass/block mode, the low/high voltages loaded are  $0/V_{\rm c}$  (V) (where  $V_{\rm c} > 0$ ), respectively. It is worth noting that to offset the parameter deviation introduced due to the inhomogeneous fabrication process, the compensation voltage  $V_{\rm c}$ with slight differences needs to be loaded on each MRR. A high voltage of 2.36 V is chosen as the minimum value at which all the resonant peaks of the MRRs are red-shifted out of the working wavelength and a high level of optical power can be obtained.

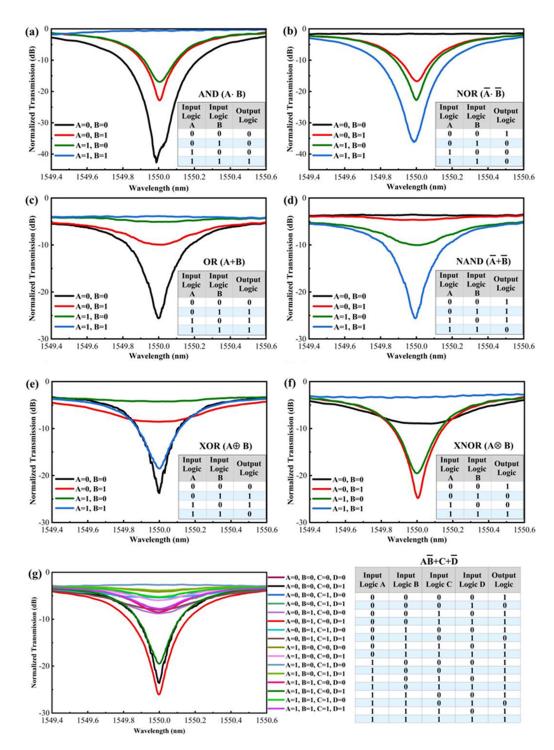

The working modes of MRRs define the combinations of logical operations, and by changing these working modes, any combination of logic can be achieved. The measured static response spectra of the six basic logic operations: AND, NOR, OR, NAND, XOR, XNOR, and one combination operation of four-operand, as well as the corresponding truth tables, are shown in Fig. 4(a)–(g). As can be seen in Fig. 4(a), when light with  $TE_0$  mode is input the device, by controlling both MRR<sub>11</sub> and MRR<sub>12</sub> in *block/pass* mode through operands A and B, in the case of  $V_{\rm A} = 1.73$  V,  $V_{\rm B} = 1.49$  V (A = 0, B = 0), a low power of light is obtained in output port (black line in Fig. 4(a)); in the case of  $V_{\rm A} = 1.73$  V,  $V_{\rm B} = 2.36$  V (A = 0, B = 1), low power of light is obtained in output port (red line in Fig. 4(a)); in the case of  $V_{\rm A} = 2.36$  V,  $V_{\rm B} = 1.49$  V (A = 1, B = 0), low power of light is obtained in output port (green line in Fig. 4(a)); in the case of  $V_{\rm A} = 2.36$  V and  $V_{\rm B} = 2.36$  V (A = 1, B = 1), high power of light is obtained in output port (blue line in Fig. 4(a)). Therefore, the fabricated device can implement AND logic in the output port of the circuit. Similarly, when controlling both MRR<sub>11</sub> and MRR<sub>12</sub> in pass/block mode through operands A and B, the NOR logic can be implemented (Fig. 4(b)). When two beams of light with

Fig. 4. Static response spectra and truth table of the circuit. (a)–(f) Corresponding to AND, NOR, OR, NAND, XOR, and XNOR logic when setting A and B as logical operands, respectively. (g) Corresponding to combination operation results when setting A, B, C, and D as logical operands.

$TE_0$  and  $TE_1$  mode are input the device, the operation results of OR, NAND, XOR and XNOR logic are achieved, respectively, as shown in Fig. 4(c)–(f). When three beams of light with  $TE_0$ ,  $TE_1$  and  $TE_2$  mode are input the device, the operation results of a combination operation of four-operand is achieved, as shown in Fig. 4(g). Note that all the transmission spectra in Fig. 4 are normalized to the reference waveguide fabricated near the device to eliminate the losses introduced by the grating couplers.

To characterize the dynamic response of the circuit, an experimental setup including a tunable laser (TL), two arbitrary function generators (AFGs), an oscilloscope (OSC), a polarization controller (PC) and a photo-detector (PD) are used. The CW light with a wavelength of 1550 nm and power of 13.35 dBm from the TL is coupled into the device through PC to ensure that the input light is in TE polarization mode, then coupled from the output port of the device to a single-mode fiber. The

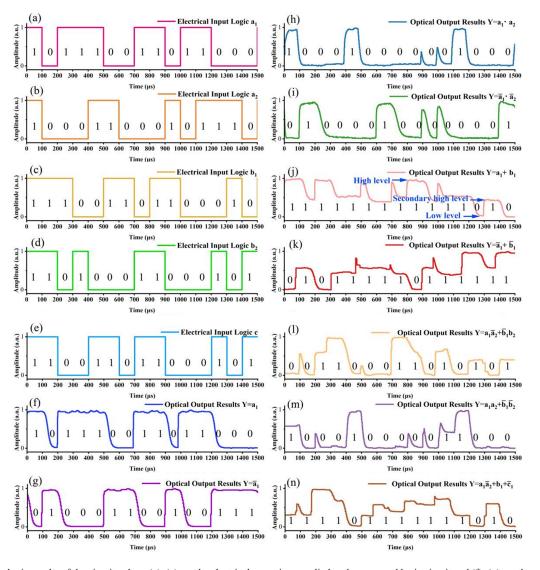

Fig. 5. Dynamic logic results of the circuit, where (a)-(e) are the electrical operations applied to the proposed logic circuit and (f)-(n) are the results of the logic operations.

output single-mode fiber is connected to the optical input port of a PD, then the PD electrical output port is connected to the input port of the OSC to obtain the waveform. Four pseudo random binary sequences (PRBS) with a preset period of 15 bits, each bit with 0.1 ms (10 Kbps), are generated by two AFGs as the four operands (A, B, C, and D). The high and low voltages of each operand are obtained from the static measurement results. Subsequently, the dynamic optical logic results are presented on the OSC through the PD.

Fig. 5(a)–(e) show the tuning voltage waveforms applied to each MRR, where the high/low level of each code signal is determined by the compensation voltage value  $V_c$  of MRR, respectively. Taking the logic function Y = a as an example, with only TE<sub>0</sub> mode input, MRR<sub>11</sub> operates in *pass/block* mode and is loaded with a dynamic modulation signal with a low/high level of 1.73/2.36 V. Fig. 5(a) shows the waveform of the dynamic modulation signal loaded on the MRR<sub>11</sub>, and Fig. 5(f) shows the corresponding dynamic response. In contrast, when the low/high level of the dynamic modulation signal is set to 0/1.73 V, the MRR<sub>11</sub> operates in *block/pass* mode, which results in a response waveform with the logic value opposite to the drive signal as shown in Fig. 5(a), realizing  $Y = \bar{a}$  (see Fig. 5(g)). Additionally, other logic operations can also be performed by the device (see Fig. 5(h)-(n)). The drop delay of the dynamic response is about 35  $\mu$ s, while the rise delay is about 9  $\mu$ s. The higher drop delay is due to the slower thermal dissipation when the high level is switched to a low level. The dynamic response performance can be further improved by changing the MRR modulation method and optimizing the MRR parameters. It should be noted that the high levels of these optical signals are different owing to the different losses of the mode (de)MUXs. By defining the secondary high level as logic '1' (as shown in Fig. 5(j), the performance of the device will not be affected. Moreover, there are some small peaks in the spectrum of Fig. 5, which are caused by the change in the operating state of the switch. As discussed in Ref. [33], these small peaks are very short in time and will not affect the logic results. The above dynamic experimental results show that the circuit can perform

any twelve-operand logic operation successfully by changing the number of operating modes and the mode of operation of the optical switch (MRR). Due to the use of the thermo-optical modulation scheme, the proposed logic circuit operates at 10 kbps. To improve the response time of the thermal tuning and thus obtain a higher speed of logic operation, electro-optical high-speed modulation techniques that take advantage of the plasma dispersion effect can also be applied to the proposed devices [7], [8], [20], [33]. In addition, other advanced modulation schemes, such as on-chip electro-absorption modulators based on the saturable absorption properties of graphene [34], [35] and epitaxially grown germanium-silicon materials [36], [37], will further promote the proposed logic circuits toward high-rate applications.

#### IV. CONCLUSION

In this paper, a novel RODLC that can realize arbitrary logic operations is proposed and experimentally demonstrated. The proposed device based on MDM technology avoids the multiwavelength problem encountered in the conventional approach. The circuit is designed and fabricated by using standard micromachining processes. Static and dynamic results show that the fabricated circuit achieves the expected logic combinations and performs dynamic operations at a speed of 10 Kbps successfully. The logic operations of NOT, AND, NOR, OR, NAND, XOR, XNOR logic operations as well as one combination operation are successfully demonstrated. The proposed device is reconfigurable, scalable, and easily integrated with electronic components on a large scale, which will pave the way for a wide range of new applications for optical information processing in future ultra-large-scale optoelectronic hybrid integrated circuits.

#### REFERENCES

- J. Hardy and J. Shamir, "Optics inspired logic architecture," *Opt. Exp.*, vol. 15, no. 1, pp. 150–165, 2007.

- [2] H. J. Caulfield and S. Dolev, "Why future supercomputing requires optics," *Nature Photon.*, vol. 4, no. 5, pp. 261–263, 2010.

- [3] H. J. Caulfield, R. A. Soref, and C. S. Vikram, "Universal reconfigurable optical logic with silicon-on-insulator resonant structures," *Photon. Nanostructures*, vol. 5, no. 1, pp. 14–20, 2007.

- [4] J. Shamir, H. J. Caulfield, W. Micelli, and R. J. Seymour, "Optical computing and the Friedkin gates," *Appl. Opt.*, vol. 25, no. 10, pp. 1604–1607, 1986.

- [5] Q. Xu and R. Soref, "Reconfigurable optical directed-logic circuits using microresonator-based optical switches," *Opt. Exp.*, vol. 19, no. 6, pp. 5244–5259, 2011.

- [6] R. Soref, F. De Leonardis, Z. Ying, V. M. Passaro, and R. T. Chen, "Silicon-based group-IV O-E-O devices for gain, logic, and wavelength conversion," ACS Photon., vol. 7, no. 3, pp. 800–811, 2020.

- [7] L. Zhang et al., "Electro-optic directed logic circuit based on microring resonators for XOR/XNOR operations," *Opt. Exp.*, vol. 20, no. 11, pp. 11605–11614, 2012.

- [8] L. Yang, L. Zhang, C. Guo, and J. Ding, "XOR and XNOR operations at 125 GB/S using cascaded carrier-depletion microring resonators," *Opt. Exp.*, vol. 22, no. 3, pp. 2996–3012, 2014.

- [9] P. Zhou, L. Zhang, Y. Tian, and L. Yang, "10 GHz electro-optical OR/NOR directed logic device based on silicon micro-ring resonators," *Opt. Lett. Opt. Exp.*, vol. 39, no. 7, pp. 1937–1940, 2014.

- [10] Z. Ying et al., "Silicon microdisk-based full adders for optical computing," Opt. Lett., vol. 43, no. 5, pp. 983–986, 2018.

- [11] Y. Tian et al., "Experimental demonstration of an optical Feynman gate for reversible logic operation using silicon micro-ring resonators," *Nanophotonics*, vol. 7, no. 1, pp. 333–337, 2018.

- [12] Z. Liu et al., "On-chip optical parity checker using silicon photonic integrated circuits," *Nanophotonics*, vol. 7, no. 12, pp. 1939–1948, 2018.

- [13] H. Xiao et al., "Experimental realization of a CMOS-compatible optical directed priority encoder using cascaded micro-ring resonators," *Nanophotonics*, vol. 7, no. 4, pp. 727–733, 2018.

- [14] Z. Ying et al., "Automated logic synthesis for electro-optic logic-based integrated optical computing," *Opt. Exp.*, vol. 26, no. 21, pp. 28002–28012, 2018.

- [15] Q. Xu and R. Soref, "Reconfigurable optical directed-logic circuits using microresonator-based optical switches," *Opt. Exp.*, vol. 19, no. 6, pp. 5244–5259, 2011.

- [16] C. Qiu, X. Ye, R. Soref, L. Yang, and Q. Xu, "Demonstration of reconfigurable electro-optical logic with silicon photonic integrated circuits," *Opt. Lett.*, vol. 37, no. 19, pp. 3942–3944, 2012.

- [17] C. Qiu, W. Gao, R. Soref, J. T. Robinson, and Q. Xu, "Reconfigurable electro-optical directed-logic circuit using carrier-depletion micro-ring resonators," *Opt. Lett.*, vol. 39, no. 24, pp. 6767–6770, 2014.

- [18] Y. Qi, C. Qiu, W. Gao, X. Zhong, and Y. Su, "Silicon reconfigurable electrooptical logic circuit enabled by a single-wavelength light input," *IEEE Photon. Technol. Lett.*, vol. 31, no. 6, pp. 435–438, Mar. 2019.

- [19] Y. Tian et al., "Reconfigurable electro-optic logic circuits using microring resonator-based optical switch array," *IEEE Photon. J.*, vol. 8, no. 2, Apr. 2016, Art. no. 7801908.

- [20] Y. Tian et al., "Experimental demonstration of a reconfigurable electrooptic directed logic circuit using cascaded carrier-injection micro-ring resonators," *Sci. Rep.*, vol. 7, no. 1, 2017, Art. no. 6410.

- [21] D. Dai, "Silicon nanophotonic integrated devices for on-chip multiplexing and switching," J. Lightw. Technol., vol. 35, no. 4, pp. 572–587, Feb. 2017.

- [22] D. J. Richardson, J. M. Fini, and L. E. Nelson, "Space-division multiplexing in optical fibres," *Nature Photon.*, vol. 7, no. 5, pp. 354–362, 2013.

- [23] G. Li, N. Bai, N. Zhao, and C. Xia, "Space-division multiplexing: The next frontier in optical communication," *Adv. Opt. Photon.*, vol. 6, no. 4, pp. 413–487, 2014.

- [24] X. Wu, C. Huang, K. Xu, C. Shu, and H. K. Tsang, "Mode-division multiplexing for silicon photonic network-on-chip," *J. Lightw. Technol.*, vol. 35, no. 15, pp. 3223–3228, Aug. 2017.

- [25] H. Xiao et al., "Demonstration of various optical directed logic operations by using an integrated photonic circuit," *Opt. Lett.*, vol. 46, no. 10, pp. 2457–2460, 2021.

- [26] L. W. Luo et al., "WDM-compatible mode-division multiplexing on a silicon chip," *Nature Commun.*, vol. 5, no. 1, 2014, Art. no. 3069.

- [27] Y. Zhang, Y. He, Q. Zhu, C. Qiu, and Y. Su, "On-chip silicon photonic 2 × 2 mode- and polarization-selective switch with low inter-modal crosstalk," *Photon. Res.*, vol. 5, no. 5, pp. 521–526, 2017.

- [28] D. Dai et al., "10-channel mode (de)multiplexer with dual polarizations," *Laser Photon. Rev.*, vol. 12, no. 1, 2018, Art. no. 1700109.

- [29] H. Xiao et al., "On-chip reconfigurable and scalable optical mode multiplexer/demultiplexer based on three-waveguide-coupling structure," *Opt. Exp.*, vol. 26, no. 17, pp. 22366–22377, 2018.

- [30] Y. Liu et al., "Arbitrarily routed mode-division multiplexed photonic circuits for dense integration," *Nature Commun.*, vol. 10, no. 1, 2019, Art. no. 3263.

- [31] H. A. Haus, Waves and Fields in Optoelectronics. Marietta, OH, USA: CBLS, 2004.

- [32] L. Martinu and D. Poitras, "Plasma deposition of optical films and coatings: A review," J. Vac. Sci. Technol. A, vol. 18, no. 6, pp. 2619–2645, 2000.

- [33] Y. Tian, L. Zhang, and L. Yang, "Electro-optic directed AND/NAND logic circuit based on two parallel microring resonators," *Opt. Exp.*, vol. 20, no. 15, pp. 16794–16800, 2012.

- [34] M. Liu et al., "A graphene-based broadband optical modulator," *Nature*, vol. 474, no. 7349, pp. 64–67, 2011.

- [35] C. T. Phare, Y.-H. D. Lee, J. Cardenas, and M. Lipson, "Graphene electrooptic modulator with 30 GHz bandwidth," *Nature Photon.*, vol. 9, no. 8, pp. 511–514, 2015.

- [36] J. Liu et al., "Waveguide-integrated, ultralow-energy GeSi electroabsorption modulators," *Nature Photon.*, vol. 2, no. 7, pp. 433–437, 2008.

- [37] D. Feng et al., "High speed GeSi electro-absorption modulator at 1550 nm wavelength on SOI waveguide," *Opt. Exp.*, vol. 20, no. 20, pp. 22224–22232, 2012.