# Optically Synchronized Phased Arrays in CMOS

Matan Gal-Katziri<sup>®</sup>, *Member, IEEE*, Craig Ives, *Graduate Student Member, IEEE*, Armina Khakpour, *Graduate Student Member, IEEE*, and Ali Hajimiri<sup>®</sup>, *Fellow, IEEE*

Abstract—Optical synchronization of large-span arrays offers significant benefits over electrical methods in terms of the weight, cost, power dissipation, and complexity of the clock distribution network. This work presents the analysis and design of the first phased array transmitter synchronized using a fully monolithic CMOS optical receiver. We demonstrate a bulk CMOS, 8-element, 28-GHz phased array building block with an on-chip photodiode (PD) that receives and processes the optical clock and uses an integrated PLL to generate eight independent phase-programmable RF outputs. The system demonstrates beam steering, data transmission, and remote synchronization of array elements at 28 GHz with fiber lengths up to 25 m, in order to show the scaling benefits of our approach. The provision of small footprint and cost-effective CMOS transceivers with integrated optoelectronic receivers enables exciting opportunities for low-cost and ultralight array systems.

Index Terms—CMOS, injection-locked oscillators (ILOs), optoelectronics, phased arrays, photodiodes (PDs), silicon photonics.

# I. INTRODUCTION

OW-COST, functionally complex silicon mm-wave and RF integrated circuits (RFICs) [1]–[5] have significantly changed the nature and potential applications of phased arrays. These RFICs enable very large span, low-cost, lightweight, and flexible phased arrays [6], which may be implemented in a dense or sparse fashion [7], and used in a range of emerging applications.

In a modern modular phased array, a common reference signal is distributed to *sub-modules*, which are usually fully functional phased arrays themselves. Each sub-module is governed by a single RFIC which drives several radiating *elements* and performs local beamforming tasks that are essential for the array's functionality.

As array spans become large, electrically synchronizing these submodules becomes more challenging. Methods for

Manuscript received April 28, 2021; revised August 27, 2021; accepted December 8, 2021. Date of publication January 19, 2022; date of current version May 26, 2022. This article was approved by Associate Editor David Stoppa. This work was supported by the Caltech SSPP Program. (Corresponding author: Matan Gal-Katziri.)

Matan Gal-Katziri was with the California Institute of Technology, Pasadena, CA 91125 USA. He is now with the School of Electrical Engineering, Ben-Gurion University, Be'er-Sheva 8443944, Israel (e-mail: matangk@bgu.ac.il).

Craig Ives and Ali Hajimiri are with the California Institute of Technology, Pasadena, CA 91125 USA.

Armina Khakpour was with the California Institute of Technology, Pasadena, CA 91125 USA. She is now with Qualcomm Inc., San Diego, CA 92121 USA.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSSC.2021.3136787.

Digital Object Identifier 10.1109/JSSC.2021.3136787

reference distribution relying on local synthesis were introduced [8]–[10], but are limited in performance. Clock distribution at RF, on the other hand, may become prohibitively expensive and power hungry. Neither of these options scales well with the size, span, or operation frequency of the array. Furthermore, as future arrays shift toward flexible [6], lightweight [5], and cost-effective [10] implementations, the support infrastructure (Fig. 1) for reference, signal, and power distribution becomes a dominant factor in the system's cost, power consumption, and mass.

Optical timing synchronization (OTS), where the timing information is modulated onto an optical carrier and distributed over a long distance, can overcome some of the challenges mentioned above in RF and digital systems. Optical timing distribution has been envisioned in the past [11] and has been realized in various applications today. Several radio astronomy telescopes use or have used optical references to synchronize remote antennas [12]–[15], and optical RF distribution plays a critical role in radio-over-fiber systems [16], [17]. Some work has been done for optical distribution of digital clocks using monolithic CMOS photodiodes (PDs) with varying degrees of integration and success [18]–[20], while other works implement data receiver building blocks using monolithic CMOS PDs [21]–[23].

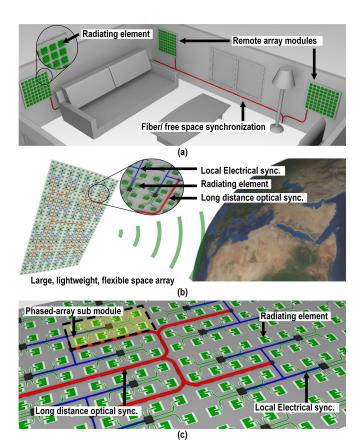

Considering the advantages of OTS and related prior work, silicon RFICs using optical synchronization can benefit a variety of applications. Indoors, applications that require multiple modules distributed throughout a room can benefit from OTS; for example, mapping the interior of a house for robotic navigation or creating 3-D models [Fig. 1(a)]. In order to reach acceptable scanning resolutions of subcentimeter, these systems have to either work in mm-wave frequency bands or use interferometry. If mm-wave bands are used, obstacles must be avoided to reduce losses, which requires multiple antenna modules spread across the room, while interferometry inherently requires multiple modules. Another example is wireless power transfer, for which the avoidance of obstacles may be desirable for efficiency and safety reasons, warranting multiple modules as well. In all such cases, OTS provides a low-cost and flexible alternative to electrical wiring.

Outdoor terrestrial and space applications can also take advantage of the physical flexibility of OTS to enable large arrays, possibly bendable and/or conformable, which may be used in communications, radar, imaging, radio astronomy, and so on. Moreover, constructing these systems out of a large number of sub-modules enables economies of scale and design flexibility, such as hybrid solutions using OTS with local electrical timing distribution, as illustrated in Fig. 1(b) and (c).

Fig. 1. Application examples for fully integrated OTS chips. (a) Indoor communication, imaging, power transfer, and entertainment systems, (b) large-scale phased arrays for space applications, and (c) very large arrays with complete or partial (between remote domains) optical synchronization across the array.

These advantages are exemplified in space-to-earth solar power transfer [24] or space-based radio telescopes, which heavily rely on extremely low-mass, foldable, highly efficient and modular phased-array sheets. For both examples, OTS through either fiber or free space provides a low-loss, low-mass solution to the problem of transmitting a reference over large distances. In terrestrial applications, multiaperture coherent radar can yield an SNR increase of up to  $N^3$  through the synchronization of N apertures [25]. Radio astronomers have used aperture synthesis for decades to synthesize extremely large radio telescope apertures through timing synchronization [26], and the same technique may be used for terrestrial imaging applications [27].

In Sections II–VII, we will present the design and demonstration of the first complete and functional optically synchronized phased array in CMOS, with an on-chip bulk CMOS PD. We start with an analysis of the benefits and potential use cases of optically synchronized arrays. Then, we will present our OTS system architecture and implementation. We will discuss the various system building blocks and their measurements and finish with measurements of our phased array transmitter, optically synchronized to a remote optical source up to 25 m away from it. Our OTS array demonstrates beam-steering, data transfer, and multimodule synchronization capabilities.

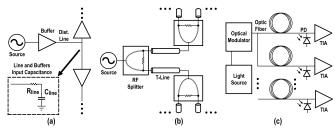

Fig. 2. Electronic (a) low frequency and (b) RF timing synchronization. (c) OTS.

## II. TIMING SYNCHRONIZATION SCHEMES

In this section, we will review and compare different methods to distribute a timing reference over large distances. We will compare the materials and performance of an optical reference scheme with common electrical design approaches and draw conclusions about its limitations and potential use cases.

#### A. Overview and Materials

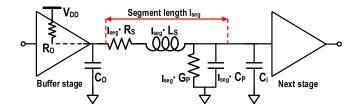

Fig. 2 illustrates three design approaches to distribute a clock reference to a synchronous array. The first [Fig. 2(a)] approach treats the line as a network of lumped elements and assumes unmatched load terminations [6], [28], [29]. As the array size increases, the lines must be buffered in order maintain the signal integrity and the validity of the model. In practice, the line capacitance limits the use of this design approach to sub-GHz frequencies. Therefore, it will be denoted as low-frequency timing synchronization (LFTS). This method is cost-effective, power-efficient, and widely used, but the addition of buffers adds jitter and PVT-dependent skew to the clock signal. These deteriorate the quality of transmitted data [30]–[32] and limit the focusing capability of the array [33]. For systems that operate at radio frequencies, the use of LFTS also requires high multiplication ratio frequency synthesizers on each sub-module, which further limits the overall system performance.

A second approach utilizes RF design techniques [Fig. 2(b)] to overcome the noise and scaling limitations of LFTS [34]–[36]. Here, the clock is distributed along matched transmission lines and buffering is not required. This enables the use of significantly higher clock frequencies, practically up to tens of GHz. This approach will be denoted radiofrequency timing synchronization (RFTS) even though it can also be implemented at lower frequencies (e.g. Ethernet, USB). The clock SNR deteriorates due to the attenuation of the lines and the signal splitters, but can always be improved by increasing the clock source power. This trade-off enables RFTS to achieve superior performance at the expense of increased power dissipation. At high clock frequencies, RFTS enables the use of low multiplication ratio synthesizers. Despite its advantages, RFTS at GHz clock rates is not often used in low-cost consumer applications, due to the cost of high-performance RF materials.

It is also possible to use an optical link to distribute timing information [Fig. 2(c)]. An OTS approach benefits from the

TABLE I

Comparison of Representative RF and Optical Fiber Materials:

Mass, Signal Attenuation, and Cost (As of May 2021)

| Material                     | Mass density               | Loss     | Cost                          |

|------------------------------|----------------------------|----------|-------------------------------|

| RG58 coax                    | 170 g/m                    | 2.3 dB/m | ~\$1.8/m**                    |

| 20 mil RO4350B               | 1.83 g/cm <sup>3</sup>     | 6.3 dB/m | $\sim$ \$30/cm <sup>2</sup> * |

| 60 mil FR-4                  | $\sim$ 2 g/cm <sup>3</sup> | 25 dB/m  | $\sim$ \$0.1/cm <sup>2*</sup> |

| SMF-28 jacketed <sup>†</sup> | 17.4 g/m                   | 3 dB/km  | ~\$0.5/m**                    |

| SMF-28 bare <sup>†</sup>     | 2.9 g/m                    | 3 dB/km  | ~\$0.5/m***                   |

- † Optical materials, at 780 nm

- \* Based on publicly available small-batch (10s of boards) run quotes

- \*\* Based on the lowest price breaks for bulk quantities available online

- \*\*\* Bulk cost of bare fiber assumed to be similar to jacketed

low loss of the propagation media at the cost of additional optoelectronic hardware, usually with limited efficiency. This approach supports arbitrary clock frequencies [16], practically limited by the capabilities of the electronic front-end (FE), with a potential advantage in the cost, mass, and loss of the clock lines over electrical networks (Table I). Clearly, these benefits are substantial only if the optical packaging and interface are simple and robust enough so as not to become the main cost and area driver of the OTS system.

For large systems, such as radio telescopes or space-toearth power transfer, optical fiber is an inexpensive way to span large distances with low loss, little to no EMI, and low sensitivity to environmental changes [37]. For comparatively small systems that require large arrays, electro-optical printed circuit boards (EOCBs) with pick-and-place-compatible mirror elements can be mass-produced on standard or flexible substrates [38], [39]. This is less costly than aligning fibers to every RFIC, since individual fibers or fiber arrays can be passively aligned to the edge of the board using proven techniques [40]. For either large or small systems, the option of OTS through free space, when attenuation is low, eliminates the need for a physical connection. Optical fiber, free space optics, and EOCBs may be used in various combinations, depending on the requirements of the system. Additional benefit may be gained through low cost integration of the optical-to-electrical conversion, for example, monolithic PDs in CMOS.

Next, we will use a simplified timing distribution model to compare the performance of the various approaches and draw conclusions regarding their potential applications.

# B. Performance Comparison

The power dissipation and noise added by distribution networks, along with their mass, cost, complexity, and functionality, determine the use cases for the different clocking schemes. For our analysis, we will assume a 1-D array model with radiators operating at a wavelength  $\lambda$ . This simplified arrangement enables us to draw conclusions that are applicable to more complex configurations (different fan-outs, 2-D, etc.). We consider a modular, scalable phased array. The clock signal is fed to each of the array's *sub-modules*, each mounted

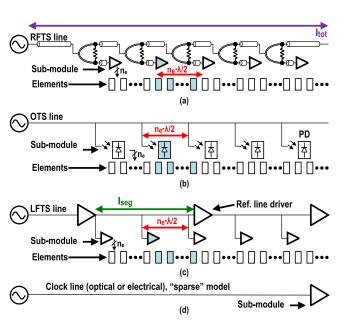

Fig. 3. Clock distribution line models for (a) RFTS, (b) OTS, (c) LFTS, and (d) sparse array (optical or electrical). Submodules and their associated radiators are highlighted.

with a single RFIC that drives  $n_e$  radiating *elements*. Fig. 3 illustrates the models for the different distribution methods. The sub-modules are spaced in such a way that the radiating elements form a 1-D array and are separated  $\lambda/2$  apart. Notably, LFTS is slightly different than the other two methods because it requires additional buffers along the clock line, with a separation that is generally a function of the clock frequency and not  $\lambda$ . We will denote the models in Fig. 3(a)–(c) as *dense*. The model in Fig. 3(d) where a single sub-module is driven by a long line will be denoted *sparse* and will be used as a special case where multiple splitters and sub-module loads do not affect the system performance.

We start with the cases of RFTS and OTS [Fig. 3(a) and (b)], where the clock is sent over a matched network to the sub-modules' RFICs. The network power dissipation can be derived from the required SNR at the RFIC's FE amplifier output. Assuming that the amplifier is driven and adds white noise, with a noise factor F, at a temperature T, the spectral density of its normalized phase noise floor  $S_{\phi}$  is related to the input power,  $P_{\text{chip}}$  by  $[42]^2$

$$S_{\phi}(f) = F \cdot \frac{kT}{P_{\text{chip}}}.$$

(1)

The integrated phase error  $\Delta\phi_{\rm rms}$  depends on the amplifier brick-wall bandwidth B. Thus,  $\Delta\phi_{\rm rms}^2\approx S_\phi\cdot B$  and can be related to the amplifier timing error  $\Delta t_{\rm rms}$  by  $\Delta\phi_{\rm rms}=2\pi f_{\rm ck}\Delta t_{\rm rms}$ , where  $f_{\rm ck}$  is the input clock frequency. The required input power to the RFIC's receiver can be found from the FE amplifier performance and the timing error that is dictated by the system, such that

$$P_{\rm chip} pprox rac{F \cdot kTB}{(2\pi f_{

m ck} \Delta t_{

m rms})^2}.$$

(2)

<sup>&</sup>lt;sup>1</sup>Advancements in optical phased array transceivers have enabled solid-state optical beamforming and steering with wide grating-lobe-free FOV [41].

<sup>&</sup>lt;sup>2</sup>It should be noted that this is the power spectrum of phase in units of radian<sup>2</sup>/Hz.

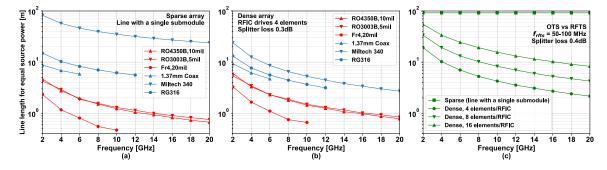

Fig. 4. Array span above which RFTS power dissipation exceeds OTS power dissipation assuming (a) sparse array with one element at its end or (b) dense array, PCB materials are red, coaxial lines are blue. Subplot (c) compares between OTS and RFTS at the 100-MHz frequency range.

An RFTS scheme utilizes an electronic network of lines and splitters. The insertion loss  $L_{\rm rf}$  of a matched transmission line with a length of  $n_e \cdot \lambda/2$  and a loss of  $\alpha$  dB/m, followed in the 1-D case by a single splitter with a loss of  $\alpha_{\rm spl}$  in dB can be expressed as

$$L_{\rm rf} = 10^{-(\alpha \cdot n_e \cdot \lambda/2 + \alpha_{\rm spl})/20}.$$

(3)

A 1-D RFTS network that drives M sub-modules will dissipate

$$P_{\text{rfts}} = \frac{P_{\text{chip}}}{\eta_{\text{src}}} \cdot \sum_{m=1}^{M} \left(\frac{1}{L_{\text{rf}}}\right)^{m} \tag{4}$$

to deliver  $P_{\rm chip}$  to each sub-module from a centralized source with an efficiency  $\eta_{\rm src}$ . This is a geometric series with a sum of

$$P_{\text{rfts}} = \frac{P_{\text{chip}}}{L_{\text{rf}} \cdot \eta_{\text{src}}} \cdot \frac{1 - L_{\text{rf}}^{-M}}{1 - L_{\text{rf}}^{-1}}.$$

(5)

Contrary to RFTS, an OTS scheme delivers  $P_{\rm chip}$  to the RFIC's FE amplifier via a PD with a limited efficiency  $\eta_{\rm pd}$ . For typical distances, line<sup>3</sup> (fiber or free space, assuming that all the transmitted power is collected) loss is negligible compared to the PD loss, and the power dissipation of an OTS network driving M sub-modules is

$$P_{\rm ots} = M \cdot \frac{P_{\rm chip}}{\eta_{\rm pd} \eta_{\rm src}}.$$

(6)

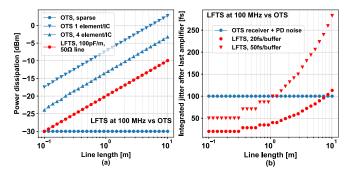

We can now use (5) and (6) in order to find the length  $l_{tot}(M)$  beyond which the exponentially increasing loss associated with RFTS is larger than the linearly increasing loss of the OTS network. For arrays beyond that span, OTS is favorable from a power dissipation perspective. Fig. 4 illustrates this calculation for several common RF materials. In Fig. 4(a), we first consider a sparse array, with a single long line driving a single sub-module at its end [no splitting, as in Fig. 3(d)], while Fig. 4(b) accounts for dense arrays with  $\lambda/2$ spaced elements [as shown in Fig. 3(a)-(c)]. This is done assuming similar FE amplifiers for RFTS and OTS, a 20% efficient PD, and a realistic RF splitter loss of 0.3 dB over the optical splitter. The RF and optical source efficiencies are assumed to be 50% and 30%, respectively. No local frequency multiplication is assumed at the sub-module output. We see that at a reference frequency above 10 GHz, OTS is favorable

Fig. 5. LFTS network segment model.

Fig. 6. OTS versus LFTS. (a) Power dissipation and (b) noise comparison.

for lines longer than about 1 m when compared to PCBbased RFTS, and 6 m when compared to coaxial lines. One exception is specialty RF lines with exceptionally low loss. Those, however, are about two orders of magnitude heavier and more expensive than optical fibers. Fig. 4(c) compares a high-frequency OTS reference versus an RFTS signal at a sub-GHz frequency, as sometimes done using terminated twisted pairs. Note that the comparison is made assuming the necessary frequency multiplication for the electrical timing signal and no frequency multiplication for OTS. In this case, the electrical line loss is small, about 0.2 dB/m at the range between 50 and 100 MHz, and a realistic splitter loss is around 0.4 dB [45] over the optical splitter. One important observation from Fig. 4(b) and (c) is that for low-loss lines, the presence of power splitters dominates the loss of the electrical infrastructure.

The power dissipation of LFTS is usually calculated from the energy that can be stored in its lumped-element model equivalent. We assume that the line in Fig. 3(c) is segmented into parts that are significantly shorter electrically than the

<sup>&</sup>lt;sup>3</sup>See Table I for line loss. Splitters exist with loss <0.1 dB [43], [44].

reference wavelength. Then, each segment is modeled as shown in Fig. 5. The buffer spacing  $l_{\rm seg}$  is, in general, independent of the spacing of the submodules. The maximum LFTS clock frequency  $f_{\rm lfts}$  is, by definition, limited to approximately the resonance frequency associated with  $l_{\rm seg}$ , and it can be expressed in terms of  $C_P$  and  $L_S$ , the parallel capacitance, and series inductance per unit length, as

$$f_{\rm lfts} < \frac{1}{2\pi \cdot l_{\rm seg} \cdot \sqrt{C_P L_S}}. (7)$$

The width of each segment is usually chosen, so its resistive and dielectric losses  $R_S$  and  $G_P$  are negligible, and its length is made short enough for it to be treated as a lumped capacitor. The power dissipation of a line of length  $l_{\rm tot}$  is then

$$P_{\rm lfts} \approx f_{\rm lfts} \cdot l_{\rm tot} \cdot C_P V^2$$

(8)

where V is the buffer supply voltage. Fig. 6(a) compares the power dissipations of LFTS at 100 MHz and OTS as derived in (6), assuming a timing synchronization error of 100 fs and an amplifier bandwidth of 5% of the OTS clock frequency. For LFTS, we assume a capacitance per unit length of 100 pF/m as approximately exhibited by most PCB and coaxial materials for a 50- $\Omega$  characteristic impedance. Interestingly, OTS is superior to LFTS for sparse arrays due to its length-independent power dissipation. However, OTS power dissipation scales with the number of PDs, so this advantage diminishes as the array becomes more dense.

For a noise performance comparison, we estimate  $n_{\text{buf}}$ , the required number of LFTS line buffers, which are cascaded and add jitter to the system

$$n_{\text{buf}} > \lceil l_{\text{tot}} \cdot 2\pi \cdot f_{\text{lfts}} \cdot \sqrt{C_P L_S} \rceil.$$

(9)

It is noteworthy that we consider here segment lengths *comparable* to the clock electrical wavelength, even though they should actually be much shorter in order to be regarded as capacitive loads. This is done to not rule out resonant lumped-model designs, despite the fact that they are prone to phase drifts, do not generally scale well in size for high-Q line resonators, and are not commonly used. Consideration of such long segments results an overly optimistic jitter prediction for LFTS. The cascaded noise at the end of the distribution line is

$$N_{\text{max}} = N_{\text{buf}} \cdot \sqrt{n_{\text{buf}}} \tag{10}$$

assuming that each buffer has a noise of  $N_{\text{buf}}$  and that the buffer noise sources are independent of each other. Fig. 6(b) shows how the LFTS-only approach presents growing noise performance challenges if used to synchronize large and/or distant array domains.

Two other important noise considerations in designing distribution networks for large arrays are pickup and drift. Long conductors are prone to couple stray signals, especially if they are poorly terminated. Meter-long lines, for example, may pick-up FM radio signals and corrupt low-frequency, low-noise references in these frequency ranges. OTS is inherently resilient to this phenomenon. In addition, both optical fibers

Fig. 7. OTS phased array transmitter system architecture.

and metal transmission lines are subject to thermal expansion and to drift in their dielectric and dimensional properties due to environmental conditions. Uncompensated optical fiber delay typically varies by 20–40 ps/km/°C [12], [46]. The electrical length variation of a coaxial cable is about 20 ppm/°C [47] which translates to about 83 ps/km/°C with the reported speed of propagation (0.8c).

## C. Analysis Summary

From a pure performance perspective, OTS is a good candidate as a clocking platform for large arrays, for example, as a *complement* to a local LFTS scheme.<sup>4</sup> While electrical references are utilized in mid-size arrays [48], [49], larger implementations (>40 k elements), for example, [50], may benefit from an optical reference clock. The strongest competitor to OTS in sparse applications is a low-frequency reference that is distributed using RFTS methods. However, metal lines are still heavier than a bare fiber, and the low reference frequency may require the use of high multiplication ratio synthesizers. These limit the system performance and produce close-in spurs that are not easily filtered away from the output signal.

Additionally, OTS is less prone to EMI on the clock reference and demonstrates lower sensitivity to environmental conditions. While drift compensation of large networks is outside the scope of this work, the phase drift of fibers can be further reduced either by feedback [37], [51]–[53] or material/structure engineering [46], [54].

Contrary to electrical references, the large bandwidth of an optical fiber also supports clock and data distribution on a single line, without the limitations of conductor trace coupling and board area. The flexibility of fiber enables its use in lightweight, bendable array interconnects. Free-space optical synchronization can potentially enable efficient synchronization<sup>5</sup> of physically disconnected modules, and the possibility of distributing extremely high reference frequencies may be an attractive option in THz systems. The advantages in OTS motivate its development as an attractive reference distribution method.

<sup>&</sup>lt;sup>4</sup>As long as its PVT variations are not a limiting factor.

<sup>&</sup>lt;sup>5</sup>Wireless synchronization is also possible by an RF signal broadcast to an array. However, it may interfere with other system parts that also work at RF, and the limited directivity may result in performance issues.

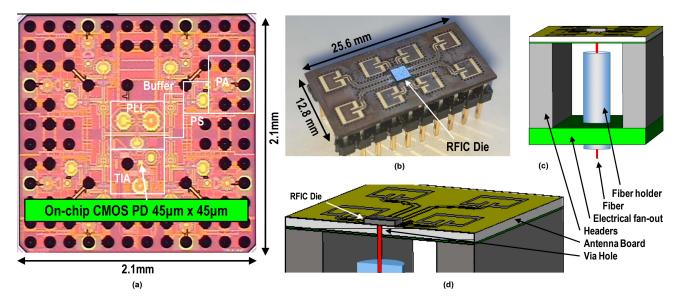

Fig. 8. The phased array building block. (a) Die photograph, (b) fully assembled PCB, (c) structure of the fiber mount, and (d) cross section of the fiber coupling.

## III. SYSTEM ARCHITECTURE

#### A. Overview

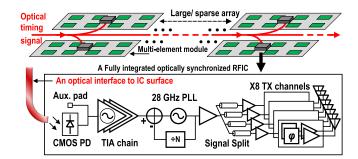

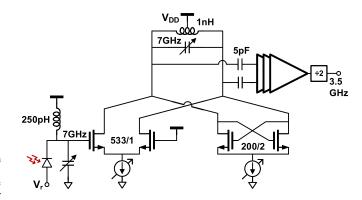

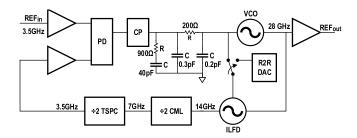

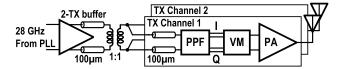

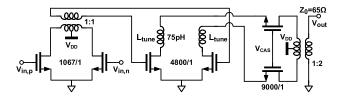

With the analysis conclusions in mind, we demonstrate an OTS system using a bulk CMOS RFIC phased array building block fabricated in a 65-nm process. It has eight RF outputs in the 28-GHz frequency range, synchronized to an optical reference at 7 GHz. The fiber interface is through a simple via hole in the chip carrier board and does not require additional mask processing. This paves the way for a low-cost packaging approach which justifies the clock infrastructure comparison in Table I. The RFIC in Fig. 7 has three main functional sections. The FE receiver contains a CMOS integrated PD which operates near the visible wavelength range and an injection-locked transimpedance amplifier (TIA) chain to amplify the optical signal to 1-V supply digital levels. The digital clock signal is fed into a low-noise, fully integrated synthesizer (PLL) with a low multiplication ratio to generate and distribute the desired output RF frequency. Lastly, the signal is buffered and distributed to drive eight TX channels with independently controlled phase and amplitude to demonstrate the beam-forming and data transfer capabilities of our approach.

## B. A Modular Phased Array Building Block

The RFIC is flip-chip bonded [Fig. 8(a) and (b)] to a modular circuit board with eight 28-GHz transmit patch antennas, spaced  $0.6\lambda$  apart. The module size is  $1.2\lambda \times 2.4\lambda$  to allow uniform tiling of RFIC boards into a larger array. Fig. 8(c) and (d) illustrates the interface between the optical signal and the chip surface. A 125- $\mu$ m-diameter optical fiber is inserted through a 140  $\mu$ m via that is aligned with the 45- $\mu$ m-wide on-chip PD. This gives sufficient tolerance to ensure reliable coupling to the PD. Optical coupling is further improved through the use of index matching gel, and mechanical stability is ensured by epoxying the fiber to a rigid support, which

is shown in Fig. 8(c). The headers and bottom board that hold the fiber support are also used to distribute power and communication signals to the array submodule.

## IV. FRONT-END DESIGN

# A. High-Speed Photodiode

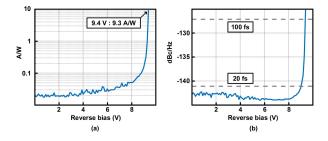

Full integration of PDs in bulk CMOS provides a direct optical interface to a standard electronic chip with well-studied trade-offs. The integrated PD is a three finger, n+/p-well diode with shallow-trench isolation (STI) guard rings and a deep n-well diffusion current block, as studied and described in [55]. The responsivity is shown in Fig. 9(a) and was measured at 780 nm, which is the optical wavelength that is intensity modulated by the reference. In the case of single-tone reference distribution, it is possible to resonate the PD capacitance with an inductor, which also provides dc biasing to the cathode (Fig. 10). The PD anode is connected to a reverse bias pin,  $V_r$ , which can be set independently to a desired reverse bias (as low as -9.5 V before breakdown occurs).

Considering just the PD and the resonant tank, the two main sources of noise are thermal noise and shot noise. The thermal noise will most likely be dominated by the integrated inductor, which typically has  $Q \approx 10$ . However, at bias voltages close to breakdown, the shot noise will be significantly greater than the thermal noise [Fig. 9(b)] [56].

To analyze the shot noise, we note that the early McIntyre model [57], [58] was shown to overestimate avalanche noise in a CMOS APD [55], [59]–[61] and was subsequently improved upon by later models [62], [63]. Nevertheless, we have adopted the early model as a simple way to estimate the upper bound of shot noise generated by our APD. Following [60], the data for electron and hole ionization rates are taken from [64], and  $k_{\rm eff}$  is found numerically, as derived in [58]. The parameter  $k_{\rm eff}$  is used together with the avalanche gain to determine the

Fig. 9. (a) CMOS PD responsivity, measured at 780 nm with about -25-dBm input power. The fluctuations reflect the intensity noise of the source laser. (b) PD and tank noise output assuming an infinite extinction ratio,  $P_{\rm in}=9$  dBm,  $r_s=2$   $\Omega$ , and Q=10. The dashed lines show the  $S_{\phi,\rm pd}$  required for 100- and 20-fs jitter.

excess noise factor, given by [56]

$$F = k_{\rm eff}M + (1 - k_{\rm eff}) \left(2 - \frac{1}{M}\right). \tag{11}$$

We note that inductor parallel resistance is approximately  $Q^2 \cdot r_s$ , where  $r_s$  is the series resistance and Q is the quality factor of the inductor [65]. Then, neglecting the PD dark current, the shot noise spectral density is  $2qM^2FR_0P_{in}$ , and the thermal noise spectral density is  $4kT/Q^2r_s$  [56]. By normalizing to the signal,  $MR_0P_{in}$ , the PD phase noise spectral density can be expressed in dB as

$$S_{\phi, \text{pd}} = 10 \log \left[ \frac{2q M^2 F R_0 P_{\text{in}} + 4kT/Q^2 r_s}{(M R_0 P_{\text{in}})^2} \right]$$

(12)

where M is the avalanche gain and  $R_0$  is the zero bias responsivity. Using the plot in Fig. 9(b), one may determine the reverse bias necessary to achieve a particular jitter specification at the input to the FE amplifier.

# B. Front-End Amplifier

The receiver TIA can be configured either as a driven LNA as specified in (1)–(6), or as a tuned injection-locked [66] TIA (TIL-TIA), as illustrated in Fig. 10, to boost the FE sensitivity at the expense of a limited lock range. This has the added benefit of built-in test capability; by allowing the TIL-TIA to self-oscillate, we can characterize the complete PLL and output path without an input signal. The reference is further divided by 2–3.5 GHz, which eases on-chip signal distribution and reduces the coupling to the first tuned amplifier. The combined TIL-TIA and divider together nominally draw 9 mA from a 1-V supply. In order to make sure that our FE does not contribute excess noise to the overall system output when operated as an oscillator, we analyze and estimate its short-and long-term phase variations.

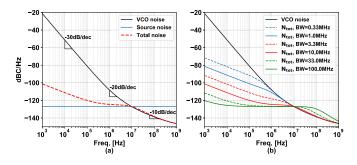

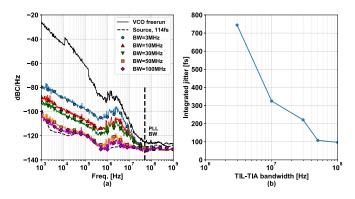

1) Injection-Locked Amplifier With a Subsequent PLL: The phase noise of the TIL-TIA is the short-term random phase deviation of its output compared to the phase of the injected signal. It can be shown (Appendix A) that an injection locked oscillator shapes the noise of the injected signal  $\mathcal{L}_i(\Delta\omega)$  and the free-running oscillation  $\mathcal{L}_f(\Delta\omega)$  similar to a first-order PLL. Our TIL-TIA is used to amplify a weak injection signal,

Fig. 10. Schematic of the TIL-TIA, where  $V_r$  is the reverse bias. W and L are given in units of 60-nm effective channel length and not repeated for symmetric devices.

so in that case its output phase noise is

$$\mathcal{L}_{\text{tiltia}}(\Delta\omega) \approx \frac{\Delta\omega^2}{\Delta\omega^2 + (\omega_L^2 - \Delta\omega_0^2)} \mathcal{L}_f(\Delta\omega) + \frac{(\omega_L^2 - \Delta\omega_0^2)}{\Delta\omega^2 + (\omega_L^2 - \Delta\omega_0^2)} \mathcal{L}_i(\Delta\omega) \quad (13)$$

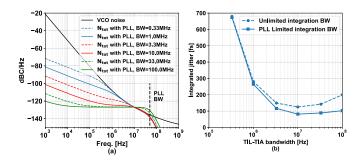

where  $\omega_L$  is the TIL-TIA lock range, and  $\Delta\omega_0$  is the difference between the injection frequency and the TIL-TIA free-running frequency. Examining (13), we notice the interchangeable effect that increasing the lock range and injecting a signal closer to the TIL-TIA center-frequency have on the output noise. Fig. 11(a) shows how the TIL-TIA approximate transfer function shapes its output noise, while Fig. 11(b) illustrates how modifying the circuit's bandwidth affects the output noise. We assume here the phase noise curve of a typical CMOS LC oscillator, and a signal source with an SNR floor of -128 dBc/Hz at 7 GHz, corresponding to a jitter of 100 fs when integrated over a 50-MHz SSB bandwidth. Unsurprisingly, optimum noise performance is achieved for a bandwidth chosen roughly at the intersection of the reference and the free-running oscillator noise curves. This could be a challenge as this bandwidth depends on the injection strength. The constraint is alleviated, however, by the subsequent on-chip synthesizer which further limits the TIL-TIA noise bandwidth. Fig. 12(a) illustrates how an additional second-order low-pass filter of the form

$$\mathcal{L}(\Delta\omega)_{\text{pll}} = \frac{\omega_{\text{pll}}^2}{\omega_{\text{pll}}^2 + 2\xi\omega_{\text{pll}}s + s^2} \mathcal{L}(\Delta\omega)_{\text{tiltia}}$$

(14)

shapes the TIL-TIA output noise, and Fig. 12(b) shows how the limited subsequent PLL bandwidth significantly relaxes the requirement for accurate injection strength control; as long as the injection strength is above a certain threshold, it should not limit the overall system noise performance. The filtering effect of injection locking was measured with a standalone TIL-TIA, as illustrated in Fig. 13, with the first-order filtering effect clearly demonstrated. It is noteworthy that the phase noise shape of the measured free-running oscillator is somewhat different from the analytical derivation due to supply noise and the absence of an amplitude-limiting mechanism in the measured circuit.

Fig. 11. TIL-TIA noise output (a) under injection with SNR floor of -128 dBC and (b) combined VCO and source noise as a function of TIL-TIA loop bandwidth.

Fig. 12. Noise output of (a) bandwidth-limited TIL-TIA and (b) effect of limiting the noise bandwidth on lock-range (TIL-TIA bandwidth) sensitivity.

Fig. 13. Measured TIL-TIA noise output (a) under variable injection strength and (b) integrated up to 50 MHz versus the lock range.

2) Phase Drift of an Injection-Locked Amplifier: Being a first-order feedback loop, the TIL-TIA tracks the input signal with a constant phase shift. Phase drift is a slow long-term variation of this phase shift due to environmental changes that affect the integrated circuit. As mentioned, utilizing a TIL-TIA implies a small injection. In this case, the constant phase difference  $\theta_0$  of an LC injection-locked oscillator (ILO) can be expressed as a function of the free-running and injection frequencies  $\omega_0$  and  $\omega_{\rm inj}$ , respectively; of the output and injection strengths  $I_o$  and  $I_{\rm inj}$ , respectively; and of the tank quality factor Q [67], [68], so that

$$\sin\left(\theta_0\right) \approx \frac{2Q}{\epsilon} \cdot \frac{\omega_0 - \omega_{\rm inj}}{\omega_0} \tag{15}$$

where  $\epsilon = I_{\rm inj}/I_o$  is the injection strength ratio. A similar effect exists when utilizing tuned amplifiers in RF chains (Appendix B), but for a TIL-TIA the situation is exacerbated by a factor of  $1/\epsilon$ .

This sets a lower limit on the injection strength depending on the oscillator sensitivity and the permissible long-term output timing drift. If a TIL-TIA drives a frequency multiplier (a PLL usually), its required phase error  $\theta_{\rm tia,max}$  can be expressed in terms of the allowable PLL output timing drift  $t_{\rm out,max}$ , where the PLL output frequency is  $f_{\rm out}$ , and its multiplication ratio is N, so

$$\theta_{\text{tia,max}} = t_{\text{out,max}} \cdot \frac{2\pi f_{\text{out}}}{N}.$$

(16)

Re-writing  $\Delta_{\omega} = (\omega_0 - \omega_{\rm inj})/\omega_0$  and substituting (16) into (15)

$$\epsilon > \frac{2Q\Delta_{\omega}}{\theta_{\text{tia,max}}} \tag{17}$$

where, for small angles,  $\sin \theta_0 \approx \theta_0$ . Conversely,  $\Delta_{\omega}$  can be defined in terms of  $\Delta_{\omega t}$ , the rate of frequency drift, and the allowed phase drift period  $t_{\text{cor}}$ , as

$$\Delta_{\omega} \approx \Delta_{\omega t} t_{\rm cor}.$$

(18)

In that case, (17) can be re-arranged to set an upper limit for how frequently phase correction algorithms must be utilized to maintain acceptable required long-term drift

$$t_{\rm cor} < \frac{\epsilon}{2Q\Delta_{ot}} \theta_{\rm tia, max}.$$

(19)

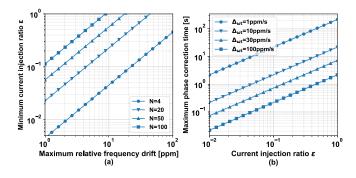

Fig. 14(a) illustrates how (17) can be used to estimate the minimum injection ratio  $\epsilon$  for a maximum output phase drift of 100 fs as a function of the normalized frequency drift for different division ratios, assuming a TIL-TIA with a nominal Q = 10. Notably, using a low-multiplier PLL subsequent to the TIL-TIA significantly eases the design requirements. Fig. 14(b) shows how (19) can be used to estimate the maximum allowed time interval before phase estimate algorithms (e.g., [10]) must be utilized to correct for TIL-TIA frequency drift. In this case, we assume that frequency drift results mainly from temperature changes and that the temperature fluctuates on the order of 0.1 °C/s. Temperature frequency drifts of uncompensated CMOS LC oscillators are on the order of 100 ppm/°C [69], [70], which translates to a frequency drift of 10 ppm/s. For our TIL-TIA, operated with normalized injection strengths of 0.05–0.1, this requires phase correction once every few seconds, an achievable task for modern integrated systems. Drift compensation techniques [69], [71], [72] can be used to further increase the phase correction intervals.

## V. LOW-MULTIPLIER FREQUENCY SYNTHESIS

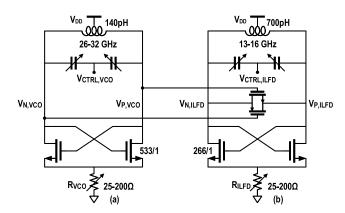

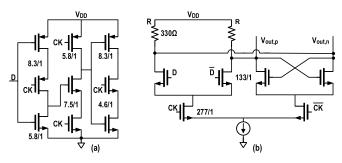

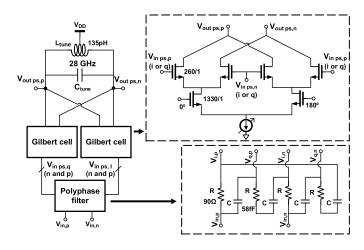

The frequency multiplying PLL [73] (3.5–28 GHz) in Fig. 15 is co-designed with the receiver amplifier to limit the output phase bandwidth to 50 MHz and reduce the reference-related jitter, while keeping the VCO noise sufficiently low. Due to the high output frequency, the divider circuitry is composed of an injection-locked frequency divider [74] (ILFD; Fig. 16) with a frequency range that is matched

Fig. 14. TIL-TIA noise output (a) under variable injection strength and (b) integrated up to 50 MHz versus the lock range.

Fig. 15. Top schematic of the PLL.

Fig. 16. Schematic of the PLL (a) VCO and the (b) first-stage ILFD divider. W and L are given in units of 60-nm effective channel length and not repeated for symmetric devices.

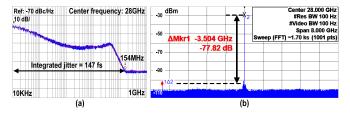

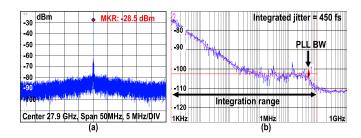

to the VCO [75] control voltage dependence, followed by current mode logic (CML) and true-single-phase clock (TSPC) dividers (Fig. 17). Using a small multiplication ratio enables us to achieve low jitter performance of 147 fs, as shown in Fig. 18(a). The low clock multiplier reduces the risk of harmonic locking and the large spacing of reference spurs from the carrier assists in suppressing them by the loop filter, the tuned RF path, and the antennas' bandwidths. As a result, our PLL demonstrates reference spurs at a power of -77 dB below the carrier as illustrated in Fig. 18(b). The asymmetric spur measurement might be due to amplitude noise in the measurement and/or asymmetric antenna bandwidth, which is also included in the measurement. The improved spurious tone rejection eases the system compliance with spectral disturbance level requirements.

Fig. 17. Flip-flop building block schematics of (a) TSPC and (b) CML dividers. W and L are given in units of 60-nm effective channel length and not repeated for symmetric devices.

Fig. 18. PLL measured (a) phase noise and (b) integer spurs at 28 GHz.

Fig. 19. TX channel schematic.

## VI. TX CHANNELS

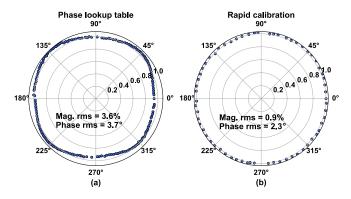

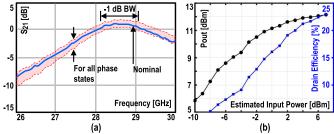

TX channels (Fig. 19) are intentionally designed to enable the demonstration of a broad range of applications. The PLL output is buffered by four independently programmable VGAs and routed to quadrants of pairs of TX channels. Each channel is composed of a first-order RC polyphase filter (PPF) [76], a vector modulator (VM) [77], and a power amplifier (PA), as shown in Figs. 20 and 21. The VGAs directly drive two unbuffered PPFs to reduce the power consumption. Those are followed by independently controlled VMs which double as buffer stages to minimize the coupling between the channels. The VMs are calibrated offline using a gradient descent algorithm to a 6-bit resolution with phase and amplitude errors of 2.3° and 0.9% rms (Fig. 22), respectively. The calibration is done with a network analyzer that measures the output phases of the TX channels and matches an I/Q setting for each desired phase. In our specific implementation, the VM state is programmed by a slow serial link which limits the transmission speed to several Mbps. This is not a fundamental limitation [78] and programming speed can be increased by using a parallel or an analog data interface, for example. Another interesting idea is to expand the optical clock approach and distribute phase modulated data optically as well, similar to the electrical implementation in [79] and [80]. Each phase shifter drives a two-stage PA with an output -1-dB bandwidth of about 1 GHz, output power of more than +12 dBm at 28 GHz, and a drain efficiency of 23% (Fig. 23).

Fig. 20. Phase shifter schematics with Gilbert cell and polyphase filter. W and L are given in units of 60-nm effective channel length and not repeated for symmetric devices.

Fig. 21. Schematic of the PA. W and L are given in units of 60-nm effective channel length and not repeated for symmetric devices.

Fig. 22. Phase shifter accuracy using (a) initial lookup table and (b) rapid search calibration algorithm.

The total output power from the chip is more than +21 dBm from a 1-V power supply. The output PA stage can work in a linear or switching mode [81] and has series inductors added between the driving transistors and the cascode in order to align the output voltage and current waveforms, which slightly increases the drain efficiency.

The contribution of the TX channel to the system's noise is negligible since it is driven by a large, almost rail-to-rail signal. The expected combined jitter added by the *standalone* TIL-TIA and PLL blocks is about 180 fs. Neglecting amplitude fluctuations and long-term drifts, the receiver-ignorant [32], [82]–[84] EVM can be calculated from jitter: EVM  $\approx$

Fig. 23. PA (a) small signal normalized gain, (b) output power, and drain efficiency.

$2\pi f_o t_{\rm rms}$ , where  $f_o$  is the output frequency. At 28 GHz, the cascaded subcircuits account for an EVM  $\approx 3.1\%$ .

# VII. MEASUREMENT RESULTS

# A. Experimental Setup

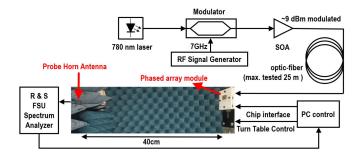

With the system architecture quantitatively evaluated, and its subblocks characterized, we assembled a single transmitter sub-module in a small anechoic space. A 7-GHz signal modulates the laser source that distributes a clock reference to the phased-array transmitter over a 25-m fiber, as illustrated in Fig. 24. Out of a variety of methods for generating the RF reference at the PD, an externally modulated laser was chosen for overall simplicity. Other possibilities include using a directly modulated laser, the beat-tone output of two lasers, an optoelectronic oscillator, or an optical frequency comb, among others [16], [85]. These, however, imposed noise, cost, and/or availability challenges with currently available off-theshelf hardware. The narrow depletion region dictates the use of a short wavelength, which was constrained to 780 nm at the lowest by hardware availability for our output power requirements. A spectrum analyzer with vector signal analysis capability serves as a remote receiver about 40 cm away from the RFIC to record its far-field radiation pattern.

# B. Single-Module Optical Synchronization

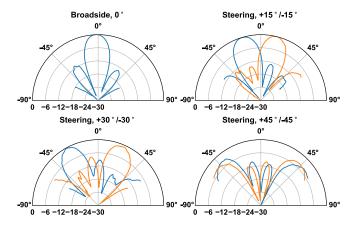

Fig. 25 shows the RFIC output signal spectrum at 28 GHz and its measured phase noise. This measurement demonstrates significantly lower noise than that reported earlier in [86], due to optimized laser modulation and fiber-PD alignment. The measurement in Fig. 25 was done with an integrated CMOS PD. The measured system timing jitter is degraded (compared to Fig. 18) by the limited performance of the laser source and by the limited extinction ratio of the optical modulator. The measured 28-GHz RF signal also includes additional amplitude noise due to the absence of an amplitude limiting mechanism at the spectrum analyzer input. Fig. 26 shows the beam steering capabilities of the optically synchronized array with symmetrical radiation patterns from  $0^{\circ}$  to  $\pm 45^{\circ}$ .

$<sup>^6</sup>$ We measured an extinction ratio of 3 dB at the chip input, which translates to a  $4(2)^{1/2}$  ratio of dc/RF amplitude, or a degradation of 15 dB in the SNR floor.

Fig. 24. Test setup for a single optically synchronized RFIC module.

Fig. 25. (a) Output of an optically synchronized RFIC module. (b) System phase noise with an optical reference (a system with an external PD shows similar performance).

Fig. 26. Beam steering of an optically synchronized RFIC module, CMOS PD mounted next to the RFIC (integrated PD shows similar performance).

# C. Data Transmission

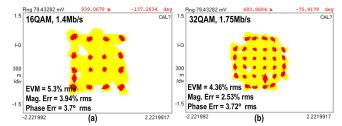

Transmission of 16-QAM and 32-QAM modulated data streams through the array is demonstrated by programming the IQ phase-shifter steering angles. This is done for a single output channel in order to minimize multipath reflections, using a pseudorandom custom logic state machine implemented on an FPGA. The modulation does not assume a specific communication protocol. Data rate is limited by the serial interface programming speed, but the output bandwidth [Fig. 23(a)] of the chip is greater than 1 GHz and can support much higher data rates. We transmitted strings of 4096 symbols with a total transmission time of 11.6 ms. As estimated in (19) and in Fig. 14, significant timing drift is expected to occur on the order of seconds and was not noticed in this measurement. Therefore, calibration for phase drift was not necessary here. Fig. 27 shows the raw measurement

Fig. 27. OTS wireless transmission of (a) 16-QAM and (b) 32-QAM modulated signals.

Fig. 28. Test setup showing optical synchronization of two RFIC modules.

of the received signal, measured by a signal analyzer. These results demonstrate a significantly improved EVM and double the data rate compared to those reported earlier in [86], thanks to optimized programming procedures and receiver setup. The measured EVM is  $\sim 5\%$  which is larger than expected due to the additional noise in the transmission (see Section VII-B). The EVM reported here includes the effect of a deterministically imperfect constellation generated using the VM and can be further improved in principle.

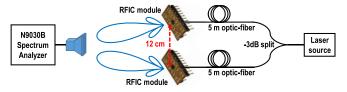

# D. Synchronizing Two Remote Phased Arrays

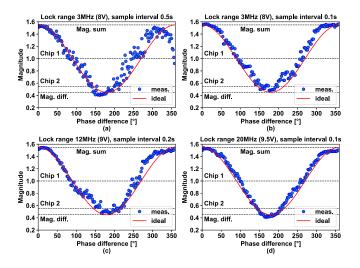

Lastly, we use OTS to synchronize two electrically distant array elements. We drive two phased array modules through two 5-m optical fibers carrying the same optical signals, as shown in Fig. 28, leading to an electrical distance of more than 10 m. First, we verify that the modules are indeed synchronized. For this purpose, we activate a single element on each module. The power received from each module is different because the elements are not aligned identically with the receiver. We varied the phase setting of one module with respect to the other over 360°. Fig. 29 illustrates the verification that the modules are indeed synchronized, that their received signals can be coherently added or subtracted, and that the quality of the phase coherence depends on the injection strength. For a very narrow lock range at slow sample intervals [Fig. 29(a)], the coherent addition suffers from significant phase drift until eventually one of the sources loses lock. As the injection strength increases and measurement time shortens, the signal addition follows the expected sinusoidal pattern very closely [Fig. 29(d)].

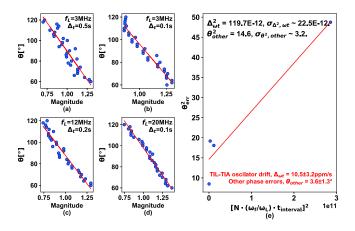

We can use the linear regions of the phase combination to roughly estimate statistical information about phase drift over time,<sup>7</sup> as illustrated in Fig. 30(a)–(d). We use a least mean squares fit to find the phase variance of the measurements.

<sup>&</sup>lt;sup>7</sup>We do not use a sinusoidal fit because it contains additional information about phase combination that leads to overly optimistic phase error estimates.

Fig. 29. Two chip phase coherence measurement. The lock range is changed by controlling the PD reverse bias voltage. (a) 3 MHz at 0.5-s intervals. (b) 3 MHz at 0.1-s intervals. (c) 12 MHz at 0.2-s intervals. (d) 20 MHz at 0.1-s intervals.

Fig. 30. Estimating phase drift from coherence measurement. (a)–(d) Linear fit of measurements to phase errors. (e) Drift from phase errors at different injection strengths.

Assuming that the noise sources are additive and that the phase samples are independent, the phase combination variance is

$$\theta_{err}^2 = \theta_{\rm inj}^2 + \theta_{\rm other}^2. \tag{20}$$

where  $\theta_{\rm inj}$  is the lock-range-dependent phase drift and  $\theta_{\rm other}$  represents noise associated with other sources such as frequency multiplication and fiber phase drift.  $\theta_{\rm inj}$  can be rewritten from (16) to (19) as

$$\theta_{\rm inj} = N \cdot \frac{\omega_f}{\omega_L} \cdot \Delta_{\omega t} \cdot t_{\rm interval} \tag{21}$$

where  $t_{\text{interval}}$  is the time period between samples. The plot of  $\theta_{\text{err}}^2$  versus  $[N \cdot (\omega_f/\omega_L) \cdot t_{\text{interval}}]^2$  in Fig. 30(e) is used to predict the TIL-TIA integrated oscillator drift and the phase deviation added by other sources.<sup>8</sup> It is noteworthy that the linear approximation of phase error is mainly determined by the last point in the dataset, where the multiplication  $(\omega_f/\omega_L)$ .

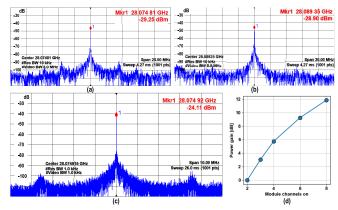

Fig. 31. Optical synchronization of two modules. (a) Module 1 peak power is -29.25 dBm, (b) module 2 is -28.90 dBm, and (c) combined peak power is -24.11 dBm, demonstrating coherent addition of the two module outputs. (d) Normalized power versus number of active elements radiated by a single RFIC module.

Fig. 32. Phase difference between the input and output of a tuned load. (a) Circuit schematic and (b) phasor diagram.

$t_{\rm interval}$  is significantly larger than the other points. In addition, the deviation of a single-phased array submodule is actually smaller by up to 30%, since we measure the sum of the phase deviation of two similar submodules with nonidentical amplitudes. Overall, the measured TIL-TIA drift is well within the range of  $\sim$ 10 ppm/s as estimated in Section IV-B2. The remaining phase error is very similar to the short-term phase noise measured in Fig. 27. Based on Section II-B, the expected drift for 5 m of uncompensated fiber is 100 fs/°C, which is probably not significant given the estimated temperature drift of 0.1°C/s in the measurements that were carried out so far.

In a second measurement, half the array elements in each module are turned on and steered toward the receiver, so the received signals have similar magnitudes. Once both of the chips are operating concurrently, we measure a coherent increase of received power by  $\sim$ 5 dB. This is comparable to the total power received by a single module with all its array elements steered broadside, as illustrated in Fig. 31. The small difference from a perfect coherent addition of 6 dB is probably due to a static phase offset between the two separate modules.

# VIII. CONCLUSION

This work presents the design and measurement of the first fully integrated OTS *system* in a bulk CMOS process. By quantitatively analyzing the benefits of an OTS system and estimating its performance, we are able to demonstrate an optically synchronized 28-GHz phased array transmitter with beam steering, remote module synchronization, and data transmission capabilities. The implementation of OTS in low-cost CMOS enables the scaling of arrays in high-volume, lightweight, low-cost, and large-span commercial applications.

<sup>&</sup>lt;sup>8</sup>The averages and the error margins are calculated using the two values  $y = (\langle x \rangle \pm 3\sigma_x)^{1/2}$ , for both the oscillator drift and the other phase errors.

By reducing the mass, cost, and loss of the synchronization infrastructure, we provide an attractive alternative to traditional high-frequency clocking schemes.

#### APPENDIX A

# INJECTION-LOCKED OSCILLATOR AS A FIRST-ORDER PLL

A simple model [87] of injection-locked LC-oscillators will be further investigated here. The discussion starts with the small signal model of an ILO introduced in [88]

$$\frac{d\theta}{dt} = \omega_i - \omega_f - \frac{\omega_f}{2Q} \cdot \frac{\epsilon \sin \theta}{1 + \epsilon \cos \theta}$$

(22)

where  $\theta$  is the phase difference between the phase of the injected signal  $\theta_i$  and the phase of the ILO output  $\theta_{\rm osc}, \omega_i$ , and  $\omega_f$  are the injection and oscillator free-running frequencies, respectively, Q is the tank quality factor, and  $\epsilon = I_{\rm inj}/I_f$  is the normalized injection strength. Defining  $f = d\theta/dt$ , the first-order differential of small phase and frequency deviations from the equilibrium point (bold letters are *vectors*) is

$$\mathbf{x} = \mathbf{x_0} + \mathbf{dx} = (\omega_{i0} + \Delta\omega_i, \ \omega_{f0} + \Delta\omega_f, \ \theta_0 + \Delta\theta) \quad (23)$$

$$f \approx f_0 + \frac{\partial f}{\partial \omega_i} \Big|_{x_0} \Delta \omega_i + \frac{\partial f}{\partial \omega_f} \Big|_{x_0} \Delta \omega_f + \frac{\partial f}{\partial \theta} \Big|_{x_0} \Delta \theta.$$

(24)

The partial derivatives are

$$\frac{\partial f}{\partial \omega_i}\Big|_{x_0} = 1$$

(25)

$$\frac{\partial f}{\partial \omega_f}\Big|_{x_0} = -\left[1 + \frac{\epsilon \sin \theta_0}{2Q(1 + \epsilon \cos \theta_0)}\right] \triangleq -K_f \qquad (26)$$

$$\frac{\partial f}{\partial \theta}\Big|_{x_0} = -\frac{\omega_f \epsilon}{2Q} \cdot \frac{\epsilon + \cos \theta_0}{(1 + \epsilon \cos \theta_0)^2} \triangleq -K_{\theta}. \tag{27}$$

We note that by definition  $f_0 = 0$  at equilibrium, so the differential equation can be approximated as

$$\frac{d\Delta\theta}{dt} = \Delta\omega_i - K_f \cdot \Delta\omega_f - K_\theta \cdot \Delta\theta \tag{28}$$

and in Laplace domain

$$s\Delta\theta = s\Delta\theta_i - sK_f \cdot \Delta\theta_f - K_\theta \cdot \Delta\theta. \tag{29}$$

Since  $\theta = (\theta_i - \theta_{osc})$ , then  $\Delta\theta = (\Delta\theta_i - \Delta\theta_{osc})$  and the differential equation can be rewritten as

$$s \Delta \theta_{\text{osc}} = s K_f \cdot \Delta \theta_f + K_\theta \cdot (\Delta \theta_i - \Delta \theta_{\text{osc}}) \tag{30}$$

or

$$\Delta\theta_{\rm osc} = \frac{sK_f \cdot \Delta\theta_f + K_\theta \cdot \Delta\theta_i}{s + K_\theta}.$$

(31)

With the frequency-domain transfer function defined around the equilibrium point, it is now clear how the noise spectra of the input and free-running oscillator are shaped by the injection-lock dynamics. If the noise sources are independent, then

$$\mathcal{L}(\Delta\omega)_{\text{osc}} = \frac{\Delta\omega^2 K_f^2}{\Delta\omega^2 + K_\theta^2} \mathcal{L}(\Delta\omega)_f + \frac{K_\theta^2}{\Delta\omega^2 + K_\theta^2} \mathcal{L}(\Delta\omega)_i \quad (32)$$

which is mathematically identical to a first-order PLL. Utilizing an ILO as an amplifier implies  $\epsilon \ll 1$ , so

$$K_f \approx 1, \ K_\theta \approx \frac{\omega_f \epsilon}{2O} \cos \theta_0.$$

(33)

With a weak injection also [67]

$$\sin \theta_0 \approx \frac{2Q}{\epsilon} \cdot \frac{\omega_{f0} - \omega_{i0}}{\omega_{f0}}.$$

(34)

Substituting  $\cos^2 \theta = 1 - \sin^2 \theta$

$$K_{\theta}^{2} \approx \left(\frac{\omega_{f}\epsilon}{2Q}\right)^{2} \cdot \left[1 - \left(\frac{2Q}{\epsilon\omega_{f}}\right)^{2} (\omega_{f0} - \omega_{i0})^{2}\right]$$

(35)

or, more simply

$$K_{\theta}^{2} \approx \omega_{L}^{2} - \Delta \omega_{0}^{2} \tag{36}$$

were  $\omega_L$  is the ILO lock range, and  $\Delta\omega_0$  is the difference between the injection frequency and free-running frequency of the oscillator.

#### APPENDIX B

# PHASE SENSITIVITY OF A PARALLEL-LC TUNED AMPLIFIER

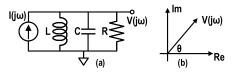

Assuming an harmonic excitation  $I(j\omega)$ , the output voltage can be written in phasor notation as shown in Fig. 32.

$$V(j\omega) = \frac{j\omega L}{(1 - \omega^2 LC) + j\omega L/R} \cdot I(j\omega). \tag{37}$$

The output phase  $\theta$  relative to the current is derived from

$$\tan(\angle V) = \frac{\operatorname{Im}\{V\}}{\operatorname{Re}\{V\}} = \frac{R}{\omega L} \cdot \frac{\omega_0^2 - \omega^2}{\omega_0^2}$$

(38)

and for a small deviation around resonance

$$\theta(\omega - \omega_0) \approx \theta(\omega_0) + \frac{d\theta}{d\omega}(\omega - \omega_0) \approx 2Q \cdot \frac{\omega_0 - \omega}{\omega_0}.$$

(39)

This is similar to the phase variation that was derived in (15) for a small injection, where  $\sin\theta \approx \tan\theta \approx \theta$  but without the added sensitivity to the normalized injection strength  $\epsilon$ .

## ACKNOWLEDGMENT

The authors would like to thank Muse Semiconductor for the invaluable input throughout the fabrication process and Keysight Technologies for the generous assistance with high-performance measurement instrumentation. They would also like to thank for the thorough and constructive feedback from the anonymous reviewers.

## REFERENCES

- X. Guan, H. Hashemi, and A. Hajimiri, "A fully integrated 24-GHz eight-element phased-array receiver in silicon," *IEEE J. Solid-State Circuits*, vol. 39, no. 12, pp. 2311–2320, Dec. 2004.

- [2] A. Natarajan, A. Komijani, and A. Hajimiri, "A fully integrated 24-GHz phased-array transmitter in CMOS," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2502–2514, Dec. 2005.

- [3] A. Natarajan, A. Komijani, X. Guan, A. Babakhani, and A. Hajimiri, "A 77-GHz phased-array transceiver with on-chip antennas in silicon: Transmitter and local lo-path phase shifting," *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 2807–2819, Dec. 2006.

- [4] A. Babakhani, G. Xiang, A. Komijani, A. Natarajan, and A. Hajimiri, "A 77-GHz phased-array transceiver with on-chip antennas in silicon: Receiver and antennas," *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 2795–2806, Dec. 2006.

- [5] M. R. M. Hashemi et al., "A flexible phased array system with low areal mass density," *Nature Electron.*, vol. 2, no. 5, pp. 195–205, May 2019, doi: 10.1038/s41928-019-0247-9.

- [6] M. Gal-Katziri, A. Fikes, F. Bohn, B. Abiri, M. R. Hashemi, and A. Hajimiri, "Scalable, deployable, flexible phased array sheets," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Aug. 2020, pp. 1085–1088.

- [7] P. Rocca, G. Oliveri, R. J. Mailloux, and A. Massa, "Unconventional phased array architectures and design methodologies—A review," *Proc. IEEE*, vol. 104, no. 3, pp. 544–560, Mar. 2016.

- [8] S. Jeon et al., "A scalable 6-to-18 GHz concurrent dual-band quad-beam phased-array receiver in CMOS," *IEEE J. Solid-State Circuits*, vol. 43, no. 12, pp. 2660–2673, Dec. 2008.

- [9] M. Gal-Katziri and A. Hajimiri, "A sub-picosecond hybrid DLL for large-scale phased array synchronization," in *Proc. A-SSCC*, Nov. 2018, pp. 231–234.

- [10] A. Hajimiri, B. Abiri, F. Bohn, M. Gal-Katziri, and M. H. Manohara, "Dynamic focusing of large arrays for wireless power transfer and beyond," *IEEE J. Solid-State Circuits*, vol. 56, no. 7, pp. 2077–2101, Jul. 2021, doi: 10.1109/JSSC.2020.3036895.

- [11] J. Goodman, F. Leonberger, S.-Y. Kung, and R. Athale, "Optical interconnections for VLSI systems," *Proc. IEEE*, vol. 72, no. 7, pp. 850–866, Jul. 1984, doi: 10.1109/PROC.1984.12943.

- [12] K. Y. Lau, G. F. Lutes, and R. L. Tjoelker, "Ultra-stable RF-over-fiber transport in NASA antennas, phased arrays and radars," J. Lightw. Technol., vol. 32, no. 20, pp. 3440–3451, Oct. 15, 2014, doi: 10.1109/JLT.2014.2312930.

- [13] J. M. Payne and W. P. Shillue, "Photonic techniques for local oscillator generation and distribution in millimeter-wave radio astronomy," in *Proc. Int. Top. Meeting Microw. Photon. (MWP)*, 2002, pp. 9–12, doi: 10.1109/MWP.2002.1158847.

- [14] W. Shillue et al., "The ALMA photonic local oscillator system," in Proc. XXX URSI Gen. Assem. Sci. Symp., Aug. 2011, pp. 1–4, doi: 10.1109/URSIGASS.2011.6051254.

- [15] R. A. Perley, C. J. Chandler, B. J. Butler, and J. M. Wrobel, "The expanded very large array: A new telescope for new science," *Astrophys. J.*, vol. 739, no. 1, p. L1, Aug. 2011, doi: 10.1088/2041-8205/739/1/11.

- [16] J. Beas, G. Castanon, I. Aldaya, A. Aragon-Zavala, and G. Campuzano, "Millimeter-wave frequency radio over fiber systems: A survey," *IEEE Commun. Surveys Tuts.*, vol. 15, no. 4, pp. 1593–1619, 4th Quart., 2013, doi: 10.1109/SURV.2013.013013.00135.

- [17] S. Akiba, M. Oishi, Y. Nishikawa, K. Minoguchi, J. Hirokawa, and M. Ando, "Photonic architecture for beam forming of RF phased array antenna," in *Proc. Opt. Fiber Commun. Conf.* Washington, DC, USA: OSA, 2014, pp. 1–3, doi: 10.1364/OFC.2014.W2A.51.

- [18] J. Leu and V. Stojanovic, "Injection-locked clock receiver for monolithic optical link in 45 nm SOI," in *Proc. IEEE Asian Solid-State Circuits Conf.*, Nov. 2011, pp. 149–152, doi: 10.1109/ASSCC.2011. 6123624.

- [19] C. Debaes, D. Argawal, A. Bhatnagar, H. Thienpont, and D. A. B. Miller, "High-impedance high-frequency silicon detector response for precise receiverless optical clock injection," *Proc. SPIE*, vol. 4654, pp. 78–88, Mar. 2002, doi: 10.1117/12.463842.

- [20] A. M. Kern, "PLL-based active optical clock distribution," M.S. thesis, Massachusetts Inst. Technol., Cambridge, MA, USA, 2004.

- [21] H.-S. Kang, M.-J. Lee, and W.-Y. Choi, "Low-cost multistandard radioover-fiber downlinks based on CMOS-compatible Si avalanche photodetectors," *IEEE Photon. Technol. Lett.*, vol. 21, no. 7, pp. 462–464, Apr. 1, 2009, doi: 10.1109/LPT.2009.2013356.

- [22] S. Nayak, A. H. Ahmed, A. Sharkia, A. S. Ramani, S. Mirabbasi, and S. Shekhar, "A 10-Gb/s–18.8 dBm sensitivity 5.7 mW fully-integrated optoelectronic receiver with avalanche photodetector in 0.13-μm CMOS," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 8, pp. 3162–3173, Aug. 2019, doi: 10.1109/TCSI.2019. 2009284

- [23] Q. Pan, Y. Wang, Y. Lu, and C. P. Yue, "An 18-Gb/s fully integrated optical receiver with adaptive cascaded equalizer," *IEEE J. Sel. Topics Quantum Electron.*, vol. 22, no. 6, pp. 361–369, Nov. 2016, doi: 10.1109/JSTQE.2016.2574567.

- [24] Caltech Space Solar Power Project. Accessed: Aug. 20, 2021. [Online]. Available: https://www.spacesolar.caltech.edu/

- [25] K. M. Cuomo, S. D. Coutts, J. C. McHarg, N. B. Pulsone, and F. Robey, "Wideband aperture coherence processing for next generation radar (NexGen)," Lincoln Lab., Lexington, MA, USA, Tech. Rep. NG-3, Jul. 2004.

- [26] M. Ryle and A. Hewish, "The synthesis of large radio telescopes," Monthly Notices Roy. Astron. Soc., vol. 120, no. 3, pp. 220–230, Mar. 1960.

- [27] C. S. Ruf, C. T. Swift, A. B. Tanner, and D. M. Le Vine, "Interferometric synthetic aperture microwave radiometry for the remote sensing of the earth," *IEEE Trans. Geosci. Remote Sens.*, vol. GRS-26, no. 5, pp. 597–611, Sep. 1988.

- [28] T. Sowlatiet et al., "A 60-GHz 144-element phased-array transceiver for backhaul application," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3640–3659, Dec. 2018.

- [29] G. Mangraviti et al., "A 4-antenna-path beamforming transceiver for 60 GHz multi-Gb/s communication in 28 nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Jan. 2016, pp. 246–247.

- [30] A. Hajimiri, A. Komijani, A. Natarajan, R. Chunara, X. Guan, and H. Hashemi, "Phased array systems in silicon," *IEEE Commun. Mag.*, vol. 42, no. 8, pp. 122–130, Aug. 2004.

- [31] A. Lacaita, Integrated Frequency Synthesizers for Wireless Systems. Cambridge, U.K.: Cambridge Univ. Press, 2007.

- [32] T. Hohne and V. Ranki, "Phase noise in beamforming," *IEEE Trans. Wireless Commun.*, vol. 9, no. 12, pp. 3682–3689, Dec. 2010.

- [33] O. M. Bakr and M. Johnson, "Impact of phase and amplitude errors on array performance," Dept. Elect. Comput. Eng., UCB/EECS, UC Berkeley, CA, USA, Tech. Rep. UCB/EECS-2009-1, Jan. 1999. [Online]. Available: http://www.eecs.berkeley.edu/Pubs/TechRpts/2009/EECS-2009-1 html

- [34] S. Shahramian, M. J. Holyyoak, and Y. Baeyens, "A 16-element W-band phased-array transceiver chipset with flip-chip PCB integrated antennas for multi-gigabit wireless data links," *IEEE Trans. Microw. Theory Techn.*, vol. 66, no. 7, pp. 3389–3402, Jul. 2018, doi: 10.1109/TMTT.2018.2822304.

- [35] K. Kibaroglu, M. Sayginer, and G. M. Rebeiz, "A low-cost scalable 32-element 28-GHz phased array transceiver for 5G communication links based on a 2 × 2 beamformer flip-chip unit cell," *IEEE J. Solid-State Circuits*, vol. 53, no. 5, pp. 1260–1274, May 2018, doi: 10.1109/JSSC.2018.2791481.

- [36] J. D. Dunworth et al., "A 28 GHz bulk-CMOS dual-polarization phasedarray transceiver with 24 channels for 5G user and basestation equipment," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 70–72.

- [37] Y. He et al., "Long-distance telecom-fiber transfer of a radio-frequency reference for radio astronomy," Optica, vol. 5, no. 2, pp. 138–146, Feb. 2018. [Online]. Available: http://www.osapublishing.org/optica/abstract.cfm?URI=optica-5-2-138

- [38] F. Betschon et al., "Mass production of planar polymer waveguides and their applications," Proc. SPIE, vol. 7607, Feb. 2010, Art. no. 76070M.

- [39] T. Lamprecht et al., "EOCB-platform for integrated photonic chips direct-on-board assembly within Tb/s applications," in Proc. IEEE 68th Electron. Compon. Technol. Conf. (ECTC), May 2018, pp. 854–858.

- [40] J. Kremmel, T. Lamprecht, N. Crameri, and M. Michler, "Passively aligned multichannel fiber-pigtailing of planar integrated optical waveguides," *Opt. Eng.*, vol. 56, no. 2, Feb. 2017, Art. no. 026115.

- [41] R. Fatemi, A. Khachaturian, and A. Hajimiri, "A nonuniform sparse 2-D large-FOV optical phased array with a low-power PWM drive," *IEEE J. Solid-State Circuits*, vol. 54, no. 5, pp. 1200–1215, May 2019.

- [42] W. P. Robins, Phase Noise in Signal Sources: Theory and Applications. London, U.K.: Institution of Electrical Engineers, 1984.

- [43] Low Insertion Loss FBT Fiber Otic Splitter for FTTH and CATV. Accessed: Aug. 20, 2021. [Online]. Available: http://www.soptofiber.com/sale-12588703-low-insertion-loss-fiberoptical-splitter-compact-size-for-ftth-and-catv.html

- [44] Y. Wang, S. Gao, K. Wang, and E. Skafidas, "Ultra-broadband and low-loss optical power splitter based on tapered silicon waveguides," in *Proc. IEEE Opt. Interconnects Conf. (OI)*, Apr. 2015, pp. 80–81.

- [45] Mini-Circuits. Adp-2-10-75+. Accessed: Aug. 20, 2021. [Online]. Available: https://www.minicircuits.com/pdfs/ADP-2-10-75+.pdf

- [46] E. N. Fokoua, M. N. Petrovich, T. Bradley, F. Poletti, D. J. Richardson, and R. Slavík, "How to make the propagation time through an optical fiber fully insensitive to temperature variations," *Optica*, vol. 4, no. 6, pp. 659–668, Jun. 2017. [Online]. Available: http://www.osapublishing.org/optica/abstract.cfm?URI=optica-4-6-659

- [47] P. Clements, "Electrical length stability of coaxial cable in a field environment," JPL, Pasadena, CA, USA, Tech. Rep. 32, 1972, pp. 97–100, vol. 1526.

- [48] X. Luo et al., "A scalable Ka-band 1024-element transmit dual-circularly-polarized planar phased array for SATCOM application," IEEE Access, vol. 8, pp. 156084–156095, 2020.

- [49] G. Gultepe, T. Kanar, S. Zihir, and G. M. Rebeiz, "A 1024-element Ku-band SATCOM dual-polarized receiver with >10-dB/K G/T and embedded transmit rejection filter," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 7, pp. 3484–3495, Jul. 2021.

- [50] E. Brookner, "Phased-array and radar astounding breakthroughs—An update," in *Proc. IEEE Radar Conf.*, May 2008, pp. 1–6.

- [51] H. Hahn and H. J. Halama, "Compensation of phase drift on long cables," U.S. Patent 3434061 A, Mar. 1969.

- [52] E. Mendes, S. Baron, and M. Taylor, "TCLink: A timing compensated high-speed optical link for the HL-LHC experiments," in *Proc. Top. Workshop Electron. Part. Phys. (TWEPP)*, Mar. 2020, p. 57, doi: 10.22323/1.370.0057.

- [53] D. Sikora et al., "Phase drift compensating RF link for femtosecond synchronization of E-XFEL," *IEEE Trans. Nucl. Sci.*, vol. 67, no. 9, pp. 2136–2142, Sep. 2020.

- [54] M. Y. Peng et al., "Long-term stable, sub-femtosecond timing distribution via a 1.2-km polarization-maintaining fiber link: Approaching 10<sup>-21</sup> link stability," Opt. Exp., vol. 21, no. 17, pp. 19982–19989, Aug. 2013. [Online]. Available: http://www.opticsexpress.org/abstract.cfm?URI=oe-21-17-19982

- [55] M.-J. Lee and W.-Y. Choi, "Performance optimization and improvement of silicon avalanche photodetectors in standard CMOS technology," *IEEE J. Sel. Topics Quantum Electron.*, vol. 24, no. 2, pp. 1–13, Mar. 2018.

- [56] G. P. Agrawal, Fiber-Optic Communication Systems. Hoboken, NJ, USA: Wiley, Jun. 2002.

- [57] R. J. McIntyre, "Multiplication noise in uniform avalanche diodes," IEEE Trans. Electron Devices, vol. ED-13, no. 1, pp. 164–168, Jan. 1966, doi: 10.1109/T-ED.1966.15651.

- [58] R. J. McIntyre, "The distribution of gains in uniformly multiplying avalanche photodiodes: Theory," *IEEE Trans. Electron Devices*, vol. ED-19, no. 6, pp. 703–713, Jun. 1972, doi: 10.1109/T-ED.1972.17485.

- [59] M.-J. Lee, H. Rucker, and W.-Y. Choi, "Optical-power dependence of gain, noise, and bandwidth characteristics for 850-nm CMOS silicon avalanche photodetectors," *IEEE J. Sel. Topics Quantum Electron.*, vol. 20, no. 6, pp. 211–217, Nov. 2014, doi: 10.1109/JSTQE.2014.2327796.

- [60] A. Pauchard, P.-A. Besse, and R. Popovic, "Dead space effect on the wavelength dependence of gain and noise in avalanche photodiodes," *IEEE Trans. Electron Devices*, vol. 47, no. 9, pp. 1685–1693, Sep. 2000, doi: 10.1109/16.861578.

- [61] L. Pancheri, M. Scandiuzzo, D. Stoppa, and G.-F. D. Betta, "Low-noise avalanche photodiode in standard 0.35-μm CMOS technology," *IEEE Trans. Electron Devices*, vol. 55, no. 1, pp. 457–461, Jan. 2008, doi: 10.1109/TED.2007.910570.

- [62] R. J. McIntyre, "A new look at impact ionization—Part I: A theory of gain, noise, breakdown probability, and frequency response," *IEEE Trans. Electron Devices*, vol. 46, no. 8, pp. 1623–1631, Aug. 1999, doi: 10.1109/16.777150.

- [63] P. Yuan et al., "A new look at impact ionization—Part II: Gain and noise in short avalanche photodiodes," *IEEE Trans. Electron Devices*, vol. 46, no. 8, pp. 1632–1639, Aug. 1999, doi: 10.1109/16.777151.

- [64] R. van Overstraeten and H. de Man, "Measurement of the ionization rates in diffused silicon p-n junctions," *Solid-State Electron.*, vol. 13, no. 1, pp. 583–608, May 1970, doi: 10.1016/0038-1101(70)90139-5.

- [65] A. M. Niknejad, Electromagnetics for High-Speed Analog and Digital Communication Circuits. Cambridge, U.K.: Cambridge Univ. Press, Feb. 2007.

- [66] R. Adler, "A study of locking phenomena in oscillators," Proc. IRE, vol. 34, no. 6, pp. 351–357, 1946.

- [67] B. Razavi, "A study of injection locking and pulling in oscillators," *IEEE J. Solid-State Circuits*, vol. 39, no. 9, pp. 1415–1424, Sep. 2004.

- [68] B. Hong and A. Hajimiri, "A general theory of injection locking and pulling in electrical oscillators—Part I: Time-synchronous modeling and injection waveform design," *IEEE J. Solid-State Circuits*, vol. 54, no. 8, pp. 2109–2121, Aug. 2019.

- [69] H. Akima, A. Dec, T. Merkin, and K. Suyama, "A 10 GHz frequency-drift temperature compensated LC VCO with fast-settling low-noise voltage regulator in 0.13 μm CMOS," in *Proc. IEEE Custom Integr. Circuits Conf.*, Sep. 2010, pp. 1–4.

- [70] Y. You, D. Huang, J. Chen, and S. Chakraborty, "A 12 GHz 67% tuning range 0.37 pS RJ<sub>rms</sub> PLL with LC-VCO temperature compensation scheme in 0.13 μm CMOS," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Jun. 2014, pp. 101–104.

- [71] Y. Chang et al., "A temperature compensated VCO using feed-forward gain multiplication for cellular applications," in Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC), May 2015, pp. 187–190.

- [72] T. Liu, X. Wang, R. Wang, G. Wu, T. Zhang, and P. Gui, "A temperature compensated triple-path PLL with K<sub>VCO</sub> non-linearity desensitization capable of operating at 77 K," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 11, pp. 2835–2843, Nov. 2017.

- [73] B. Razavi, RF Microelectronics. Upper Saddle River, NJ, USA: Prentice-Hall, 2012.

- [74] M. A. Tiebout, "A CMOS direct injection-locked oscillator topology as high-frequency low-power frequency divider," *IEEE J. Solid-State Circuits*, vol. 39, no. 7, pp. 1170–1174, Jul. 2004.

- [75] A. Hajimiri and T. H. Lee, "A general theory of phase noise in electrical oscillators," *IEEE J. Solid-State Circuits*, vol. 33, no. 2, pp. 179–194, Feb. 1998.

- [76] J. Kaukovuori, K. Stadius, J. Ryynänen, and K. A. I. Halonen, "Analysis and design of passive polyphase filters," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 10, pp. 3023–3037, Nov. 2008.

- [77] A. Natarjan, A. Komijani, X. Guan, A. Babakhani, Y. Wang, and A. Hajimiri, "A 77 GHz phased-array transmitter with local LO-path phase-shifting in silicon," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2006, pp. 639–648.

- [78] W. Zhu et al., "A 24–28-GHz four-element phased-array transceiver front end with 21.1%/16.6% transmitter peak/OP1 dB PAE and subdegree phase resolution supporting 2.4 Gb/s in 256-QAM for 5-G communications," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 6, pp. 2854–2869, Jun. 2021.

- [79] S. Shahramian, M. J. Holyoak, A. Singh, and Y. Baeyens, "A fully integrated 384-element, 16-tile, W-band phased array with selfalignment and self-test," *IEEE J. Solid-State Circuits*, vol. 54, no. 9, pp. 2419–2434, Sep. 2019.

- [80] J.-O. Plouchart et al., "Si-based 94-GHz phased array transmit and receive modules for real-time 3D radar imaging," in *IEEE MTT-S Int.* Microw. Symp. Dig., Jun. 2019, pp. 532–535.

- [81] S. Cripps, RF Power Amplifiers for Wireless Communications. Boston, MA, USA: Artech House, 2006.

- [82] S. Ek et al., "A 28-nm FD-SOI 115-fs jitter PLL-based LO system for 24–30-GHz sliding-IF 5G transceivers," *IEEE J. Solid-State Circuits*, vol. 53, no. 7, pp. 1988–2000, Jul. 2018.

- [83] M. R. Khanzadi, D. Kuylenstierna, A. Panahi, T. Eriksson, and H. Zirath, "Calculation of the performance of communication systems from measured oscillator phase noise," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 61, no. 5, pp. 1553–1565, May 2014.

- [84] I. Galton and C. Weltin-Wu, "Understanding phase error and jitter: Definitions, implications, simulations, and measurement," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 1, pp. 1–19, Jan. 2019.

- [85] A. Matsko, "Advances in the development of spectrally pure microwave photonic synthesizers," *IEEE Photon. Technol. Lett.*, vol. 31, no. 23, pp. 1882–1885, Dec. 1, 2019, doi: 10.1109/LPT.2019.2947901.

- [86] M. Gal-Katziri, C. Ives, A. Khakpour, and A. Hajimiri, "A 28 GHz optically synchronized CMOS phased array with an integrated photodetector," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2021, pp. 111–114.

- [87] S. Kalia, M. Elbadry, B. Sadhu, S. Patnaik, J. Qiu, and R. Harjani, "A simple, unified phase noise model for injection-locked oscillators," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Jun. 2011, pp. 1–4.

- [88] L. J. Paciorek, "Injection locking of oscillators," Proc. IEEE, vol. 53, no. 11, pp. 1723–1727, Nov. 1965.

Matan Gal-Katziri (Member, IEEE) received the B.S. degree in physics and electrical engineering from Ben-Gurion University, Beer-Sheva, Israel, in 2009, and the M.S. and Ph.D. degrees in electrical engineering from the California Institute of Technology, Pasadena, CA, USA, in 2016 and 2020, respectively.

He studied integrated magnetic sensors for biomedical applications and investigated high-power and low-mass antenna arrays with Caltech's Space-Solar Power Program RF Team until 2021. Since

2021, he has been with Ben-Gurion University. His research interests are large antennas and arrays for communication and remote-sensing applications.

Dr. Gal-Katziri was awarded the Analog Devices Outstanding Student Designer Award in 2015 and won the IMS advanced practice paper award for his work on flexible arrays transmitters in 2020.

Craig Ives (Graduate Student Member, IEEE) received the B.S. degree in electrical engineering from the University of California at San Diego, San Diego, CA, USA, in 2017, and the M.S. degree in electrical engineering from the California Institute of Technology, Pasadena, CA, in 2020, where he is currently pursuing the Ph.D. degree.

Armina Khakpour (Graduate Student Member, IEEE) received the B.S. degree in electrical engineering from the University of Toronto, Toronto, ON, Canada, in 2019, and the M.S. degree in electrical engineering from the California Institute of Technology, Pasadena, CA, USA, in 2021.

She is currently an IC Design Engineer with Qualcomm Inc., San Diego, CA.