# A *Ka*-Band SATCOM Transceiver in 65-nm CMOS With High-Linearity TX and Dual-Channel Wide-Dynamic-Range RX for Terrestrial Terminal

Yun Wang<sup>®</sup>, Member, IEEE, Dongwon You, Student Member, IEEE, Xi Fu, Graduate Student Member, IEEE, Takeshi Nakamura, Ashbir Aviat Fadila, Teruki Someya<sup>®</sup>, Member, IEEE, Atsuhiro Kawaguchi, Junjun Qiu<sup>®</sup>, Graduate Student Member, IEEE, Jian Pang<sup>®</sup>, Member, IEEE, Kiyoshi Yanagisawa, Bangan Liu<sup>®</sup>, Member, IEEE, Yuncheng Zhang<sup>®</sup>, Graduate Student Member, IEEE, Haosheng Zhang<sup>®</sup>, Member, IEEE, Rui Wu<sup>®</sup>, Member, IEEE, Shunichiro Masaki<sup>®</sup>, Daisuke Yamazaki, Atsushi Shirane, Member, IEEE, and Kenichi Okada<sup>®</sup>, Senior Member, IEEE

Abstract—In this article, a Ka-band satellite communication (SATCOM) transceiver is first presented using a standard CMOS technology. The proposed Ka-band SATCOM transceiver consists of a high-linearity transmitter (TX) and dual-channel receiver (RX); both TX and RX are based on direct-conversion architecture. By implementing the dual-channel RX, multiple multiplexing modes, including polarization multiplexing and frequency multiplexing, can be enabled depending on the application. The RX variable gain is distributed in both RF blocks and baseband blocks to achieve a wide input dynamic range. The LNA employs a dual-coupling transformer for a low-noise figure (NF) and wideband input matching; moreover, it enhances the amplifier unilateralization characteristic to mitigate the loading effect from switched attenuators. An adjacent channel interference (ACI) cancellation scheme is proposed to further enhance the RX linearity in the frequency multiplexing mode. In the TX, single-turn high-quality-factor transformer is employed to realize matching network and four-way power combining. A prototype of the SATCOM transceiver is fabricated in a standard 65-nm CMOS process. Under 1.05-V supply voltage, the TX achieves a  $P_{\rm SAT}$  of 20.5 dBm and an average output power of 12 dBm with 2% error vector magnitude (EVM) and a 37.6-dB ACPR. The dual-channel RX achieves an NF of 5.4 dB, an IIP3 of -30 dBm on the high-gain mode, the ACI cancellation is measured of 7.9 dB with a 100-MHz signal bandwidth.

Index Terms—Adjacent channel interference (ACI), block upconverter (BUC), CMOS, direct-conversion, DVB-S2X, dynamic range, error vector magnitude (EVM), ground segment, Ka-band, linearity, low-noise amplifier (LNA), low-noise block converter (LNB), millimeter-wave, power amplifier (PA), receiver (RX), satellite communication (SATCOM), satellite, System on Chip (SoC), terrestrial terminal, transmitter (TX).

Manuscript received March 17, 2021; revised June 27, 2021; accepted July 1, 2021. Date of publication July 26, 2021; date of current version January 28, 2022. This article was approved by Associate Editor Pietro Andreani. (Corresponding author: Yun Wang.)

Yun Wang, Dongwon You, Xi Fu, Takeshi Nakamura, Ashbir Aviat Fadila, Teruki Someya, Atsuhiro Kawaguchi, Junjun Qiu, Jian Pang, Kiyoshi Yanagisawa, Bangan Liu, Yuncheng Zhang, Haosheng Zhang, Rui Wu, Atsushi Shirane, and Kenichi Okada are with the Tokyo Institute of Technology, Tokyo 152-8550, Japan (e-mail: yun@ssc.pe.titech.ac.jp).

Shunichiro Masaki and Daisuke Yamazaki are with Socionext, Yokohama 222-0033, Japan.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSSC.2021.3096190.

Digital Object Identifier 10.1109/JSSC.2021.3096190

### I. Introduction

THE artificial satellites have been invented for more than half a century to obtain a wide spherical view on the earth and realize long-distance instant communication around the world. The satellites can be mainly categorized by dedicated functions of earth imagery mapping, meteorological monitoring, space observation, global positioning, broadcasting, and communication [1]–[3]. Recent advancements in satellite communication (SATCOM) and spaceflight technology provide ever-promising high-speed low-latency global Internet access by using massive satellite constellations. Compared to the conventional long-distance optical fiber network or microwave relay, the SATCOM provides realistic, highly portable, and low-cost user-end terminal deployment in the mountain or insular area [4]–[9].

Among the various communication methods, SATCOM is the most unique one with its repeat station orbiting the earth. According to the orbit altitudes, the satellites can mainly be divided into three types: high earth orbit, medium earth orbit (MEO), and low earth orbit (LEO). The high earth orbit mostly indicates the geosynchronous orbit (GSO) or the geostationary orbit (GEO) for a special case. GEO satellites are popular for communication purposes due to their fixed position, wide earth surface coverage, and visibility. The LEO satellites are becoming more popular and attractive owing to the high demand on low-latency wideband Internet using SATCOM. The LEO satellites are much closer to the earth than a GEO one; both the smaller signal propagation time delay and lower free-space path loss (FSPL) featured in LEO are essential to a reliable high-speed SATCOM link establishment. Another promotion on the development of LEO satellites is that the advancement of economy space launch to the LEO makes the large-scale LEO satellite constellation possible for private companies. A SATCOM system usually consists of two segments: the space segment and the ground segment. The space segments are mostly the communication payloads of satellites used as transponders; the ground segment can be service provider hub or user terminal (UT) known as

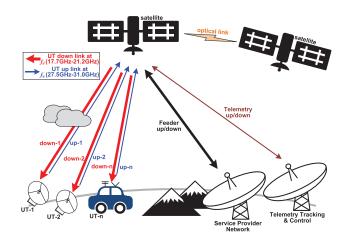

Fig. 1. SATCOM scenario and the terrestrial/non-terrestrial network.

earth station or terrestrial terminal. This work presents a *Ka*-band SATCOM transceiver for terrestrial terminals on a standard CMOS technology, which can eventually lead to the next-generation low-cost highly integrated compact solution for user-end SATCOM products.

The silicon-based millimeter-wave wireless transceivers have been significantly researched for improving integration level, system performance, and frequency of operation, especially for applications in 60-GHz WiGig [10]-[20], 5G new radio [21]–[37], and sensing radar [38]–[42]. These systems are optimized for in-door short-range usage, phased-array enhanced beamforming, and signal detection, respectively. In contrast, the integrated SATCOM transceivers are seldom reported due to the particular requirements on linearity, dynamic range, and noise performance. Designed for SATCOM Ka frequency bands with downlink at 17.7–21.2 GHz and uplink at 27.5–31 GHz, as shown in Fig. 1, this article introduces a Ka-band SATCOM transceiver [43] with expanded discussion on the SATCOM link budget, system requirements, detailed circuit design, and more measurement results. A four-path power-combining power amplifier (PA) enables a highly linear transmitter (TX), which guarantees the high average power ( $P_{avg}$ ) low error vector magnitude (EVM) output signal in the uplink. For the downlink, the adaptive receiver (RX) gain enables a broadened dynamic range based on the received signal level. The RX input port is designed to maintain a wideband low-noise figure (NF) matching with enhanced immunity on the switched load impedance. An adjacent channel interference (ACI) cancellation block is implemented for dual-channel operation. This article is organized as follows. Section II discusses the SATCOM link budget and system architecture. Section III describes the in-depth design of the SATCOM transceiver. Section IV introduces the detailed measurement results. Section V concludes this article.

# II. SATCOM TERRESTRIAL SYSTEM DESIGN

Substantial research results and developments have been reported in the silicon-based millimeter-wave transceiver operating in 28-/39-/60-/77-GHz frequency bands driven by exponentially increased data traffic capacity. There are few

reports on the CMOS SATCOM transceiver since the specific requirements on SATCOM link usually leads to III–V compound individual monolithic microwave integrated circuit (MMIC) components, which eventually making the SATCOM terminal cumbersome and expensive. In order to overcome the large FSPL between satellite and UT, the high-power highly linear uplink and low-noise downlink are required. The SATCOM link budget and hybrid-integrated transceiver architecture are discussed in this section.

# A. SATCOM Link Budget Design

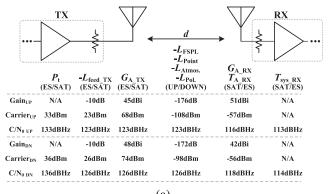

The key difference of an established SATCOM data link compared to conventional wireless link is that the satellite payload behaves as a transponder between the service provider terminal and the UT. The SATCOM total data link quality will be determined by both uplink and downlink. The uplink is analyzed at first as an example. As shown in Fig. 2(a), by applying the Friis transmission formula, the carrier-to-noise power density ratio can be expressed as follows:

$$\left(\frac{C}{N_0}\right)_{\rm up} = P_{t,\rm ES} \cdot G_{\rm TXA,ES} \cdot \frac{G_{\rm RXA,Sat}}{T_{\rm Sat\_total}} \cdot \left(\frac{\lambda_{\rm up}}{4\pi d}\right)^2 \cdot \frac{1}{L_{\rm oth}} \cdot \frac{1}{k}$$

(1)

$$d = \sqrt{(r+h)^2 - r^2 \cdot \cos^2 \theta_{EL}} - r \cdot \sin \theta_{EL}$$

(2)

where  $(C/N_0)_{up}$  denotes the uplink carrier power-to-noise power density ratio, and  $P_{t,ES}$ ,  $G_{TXA,ES}$ ,  $G_{RXA,Sat}$ ,  $T_{Sat\_total}$ ,  $\lambda_{\rm up}$ , d, and k denote the earth station transmitted power, earth station TX antenna gain, satellite RX antenna gain, satellite RX noise temperature, uplink wavelength, satellite-to-earth station slant distance, and Boltzmann's constant, respectively. The slant distance d is dependent on the satellite elevation angle  $\theta_{EL}$  and the orbit altitude h. The earth radius r is a constant of 6371 km.  $L_{\text{oth}}$  is the sum of the additional losses, for example, the antenna polarization error loss  $L_{Pol.}$  and the antenna pointing error loss  $L_{Point}$ . The essential parameters for a high-quality uplink decided by earth station are mainly  $P_{t,ES}$ and  $G_{TXA,ES}$ , while  $G_{TXA,ES}$  is proportional to the effective aperture area of an antenna. Since the antenna physical aperture size cannot be designed excessively huge for a portable and reasonable installation, the most significant parameter is  $P_{t,ES}$ , which should be carefully driven as high as possible.

A similar calculation for downlink can be shown as follows:

$$\left(\frac{C}{N_0}\right)_{\rm dn} = P_{t,\rm Sat} \cdot G_{\rm TXA,Sat} \cdot \frac{G_{\rm RXA,ES}}{T_{\rm ES\_total}} \cdot \left(\frac{\lambda_{\rm dn}}{4\pi d}\right)^2 \cdot \frac{1}{L_{\rm oth}} \cdot \frac{1}{k}$$

(3)

where  $(C/N_0)_{\rm dn}$ ,  $P_{t,\rm Sat}$ ,  $G_{\rm TXA,Sat}$ ,  $G_{\rm RXA,ES}$ ,  $T_{\rm ES\_total}$ , and  $\lambda_{\rm dn}$  denote the downlink carrier-to-noise power density ratio, the satellite transmitted power, the satellite TX antenna gain, the satellite RX antenna gain, the earth station RX noise temperature as a function of elevation angle at 19 GHz [44], and the downlink wavelength, respectively. For earth station, the key parameter to decide the link quality is RX total noise temperature  $T_{\rm ES\_total}$ .

Fig. 2. (a) SATCOM link budget for both uplink and downlink. (b) Calculated system  $C/N_0$  as a function of the elevation angle.

The SATCOM total link quality of uplink and downlink is then

$$\frac{1}{(C/N_0)_{\text{tot}}} = \frac{1}{(C/N_0)_{\text{up}}} + \frac{1}{(C/N_0)_{\text{dn}}}.$$

(4)

It can be found that, for SATCOM earth station transceiver design, the dominant two parameters are TX output power  $P_{t, \text{ES}}$  and RX noise temperature  $T_{\text{ES\_total}}$ .

Assuming that an LEO SATCOM constellation is used with distance d = 500 km, a typical 74-cm-size aperture antenna is used with a 45-dBi gain at 29 GHz and a 42-dBi gain at 19 GHz in the UT, and the antenna effective aperture area and gain in LEO satellite are assumed 6 dB higher than in the UT. The RX overall NFs are 3 dB in the satellite and 5 dB in the UT. A 10-dB additional loss in each link is considered, including the antenna pointing error, the polarization error, and the insertion loss. The TX total gain and NF are assumed 60 and 14 dB in both uplink and downlink. For a linear operation, the UT TX OIP3 and RX IIP3 are 20 dBW and -30 dBm, respectively. Based on system consideration in Section II-B, the uplink  $(C/N_0)_{up}$  is calculated 113 dB·Hz with the output power  $P_{t,ES}$  of 3 dBW. The downlink  $(C/N_0)_{dn}$ is calculated 114 dB·Hz with the output power  $P_{t,Sat}$  of 6 dBW. The up/down link total CNR supports 300-MS/s 256-APSK modulation [45]. The calculated system  $C/N_0$  as a function of the elevation angle is shown in Fig. 2(b). The total link  $C/N_0$  is degraded by increased link distance and antenna noise temperature; 60° elevation angle tuning will result in a 6-dB CNR degradation. Further increase in the output transmitted power in an earth station of the service provider can enhance the link quality with a wider system dynamic range and higher data rate.

|            | CMOS TX | GaN PA | cascaded |  |  |  |

|------------|---------|--------|----------|--|--|--|

| Gain (dB)  | 30      | 30     | 60       |  |  |  |

| OIP3 (dBm) | 25      | 50     | 48.8     |  |  |  |

| NF (dB)    | 14      | 25     | 14.1     |  |  |  |

| (b)        |         |        |          |  |  |  |

|            |         |        |          |  |  |  |

|            | GaAs LNA    | CMOS RX   | cascaded    |  |

|------------|-------------|-----------|-------------|--|

| Gain (dB)  | 20~25       | 0 ~ 30    | 25 ~ 50     |  |

| IIP3 (dBm) | 1           | -30 ~ -10 | -50 ~ -25   |  |

| NF (dB)    | NF (dB) 1.3 |           | 1.37 ~ 4.16 |  |

| (c)        |             |           |             |  |

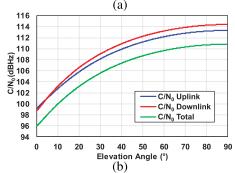

Fig. 3. (a) SATCOM transceiver block diagram with a hybrid system integration. (b) CMOS GaN hybrid TX link budget. (c) GaAs CMOS hybrid RX link budget.

# B. SATCOM Terrestrial Solution

The two dominant parameters for a terrestrial terminal or an earth station are concluded as the TX output power  $P_{t,ES}$ and the RX noise temperature  $T_{ES\_total}$ . From the analyzed link budget, the  $P_{t,ES}$  is assumed to be 3 dBW, which is feasible by using only one commercially available external GaN solid-state amplifier at 6-dB power backoff [46]. An external GaAs or InP LNA can be used to further enhance the RX overall noise performance [47]. The digital-intensive high-integrated CMOS System-on-Chip (SoC) core chip with the external PA LNA blocks results in a low-cost compact-area high-performance solution for the SATCOM system, including the block upconverter (BUC) and the low-noise block converter (LNB). Fig. 3(a) shows the block diagram of the possible SATCOM terrestrial solution with hybrid system integration. It consists of an external multiple-input multipleoutput (MIMO) antenna system in light purple, a GaN/GaAs high-performance amplification block in light blue, and a digital intensive CMOS in light orange. The SATCOM CMOS SoC is focused in this work, and the CMOS GaN/GaAs hybrid integration system link budgets are given in Fig. 3(b) and (c) [46], [47]. The CMOS TX is required to be highly linear to drive the external PA. The CMOS RX gain is subject to the received signal power level; the dynamically controlled gain is required to maintain the best signal-to-noise ratio (SNR) for demodulation. Considering the atmospherical and cosmic effects, such as the rain attenuation and sun outage, the controllable gain range can be further extended.

| TABLE I                   |               |

|---------------------------|---------------|

| SATCOM TRANSCEIVER TARGET | SPECIFICATION |

| TX frequency          | 1-channel 29 GHz |  |  |

|-----------------------|------------------|--|--|

| Bandwidth             | 300 MHz          |  |  |

| Satellite distance    | 500 km ~ 2000 km |  |  |

| BUC output power      | 3 dBW            |  |  |

| CMOS TX output power  | 12 dBm           |  |  |

| CNR <sub>0,up</sub>   | 110 dB⋅Hz        |  |  |

| Modulation            | 256 APSK         |  |  |

| RX frequency          | 2-channel 19 GHz |  |  |

| Bandwidth             | 300 MHz          |  |  |

| LNB G/T               | 15 dB/K          |  |  |

| Satellite distance    | 500 km ~ 2000 km |  |  |

| CMOS RX noise figure  | 5 dB             |  |  |

| CMOS RX Gain          | 30 dB            |  |  |

| CMOS RX Dynamic Range | 30 dB            |  |  |

| ACI cancellation      | 10 dB            |  |  |

| CNR <sub>0,dn</sub>   | 110 dB⋅Hz        |  |  |

| Modulation            | 256 APSK         |  |  |

From the perspective of satellite application and CMOS implementation, there are a few considerations.

- The millimeter-wave CMOS PA output power is constrained by limited supply voltage in standard CMOS technology, and multiple-path power combining is required to be capable of driving a GaN amplifier.

- 2) Due to the strong end-user traffic asymmetry in the downlink and the uplink, the downlink dominates around 80% in the data traffic, and a multiple-channel RX is then desired for boosting the downlink speed. With multiple receiving channels, the antenna polarization can also be employed for enriching the resource allocation method.

- 3) The satellite direct-to-home (DTH) TV service can be improved by receiving from multiple satellites, and the received signal in one channel will be jammed by another channel if the power difference is too high. As a result, an ACI tolerant RX is required in the multisatellite application.

- 4) The dynamic range of the CMOS SATCOM RX chip is contingent on the following factors in practical use; hence, the gain range is required to be wide.

- a) The preceding antenna and external LNA in different applications may be different and result in a wide input power range.

- b) The atmospherical and cosmic effects on SATCOM link, such as the rain attenuation and the sun outage, require the established link to be high power for the robustness.

- c) The SATCOM link power and modulation can be adaptively adjusted based on the throughput for optimized resource allocation and battery saving.

- d) The dual-channel RX in FDMA mode will have a wide-range input power from satellites in different directions.

Table I shows a target specification of the CMOS *Ka*-band SATCOM transceiver for terrestrial usage. The transceiver is designed for LEO satellites orbiting the earth at a

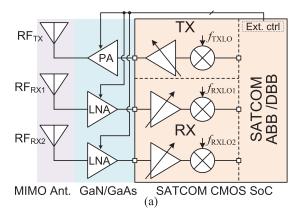

Fig. 4. CMOS Ka-band SATCOM transceiver block diagram.

500–2000-km distance. The up/down total link supports 256 APSK modulation with a 300-MHz bandwidth. The SATCOM LNB G/T is assumed of 15 dB/K, and the NF of CMOS RX targets 5 dB. The RX design target also includes a 30-dB dynamic range and a 10-dB ACI cancellation. The TX targets a linear output at 12 dBm.

### III. SATCOM TRANSCEIVER CIRCUIT DESIGN

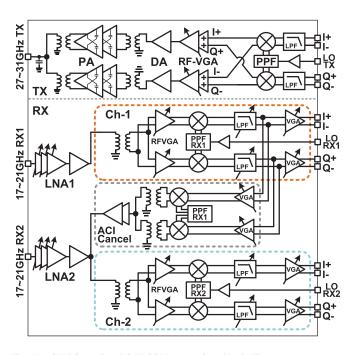

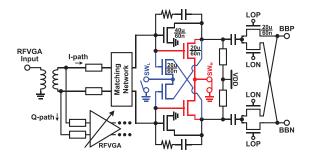

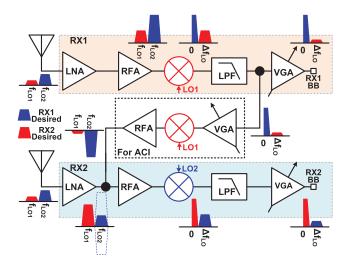

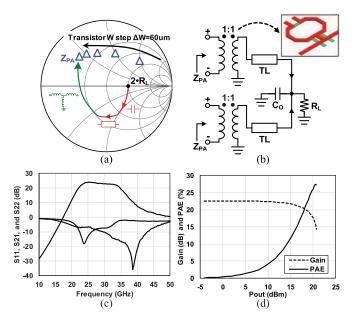

Fig. 4 shows the entire block diagram of the Ka-band SATCOM transceiver, including the RF front-end and the analog baseband. The transceiver is composed of one 29-GHz TX for uplink and two 19-GHz RXs for downlink. Both the TX and the RX are in direct-conversion architecture with differential analog baseband. The direct-conversion architecture is chosen for the system integration simplicity and higher dynamic range over the digital IF architecture. The TX includes a pair of RC low-pass filters (LPFs), a double-balanced mixer, an RF variable-gain amplifier (RF-VGA), a drive amplifier (DA), and a four-way two-stage power-combining PA. The TX LO is generated by using a poly-phase filter (PPF) from an external LO input. On the RX side, the received 19-GHz RF signal is amplified with a three-stage low-noise amplifier (LNA) followed by an RF-amplifier and an RF-VGA. Switched gain controls are distributed in the LNA and the RF-VGA. The RF signal is down-converted to baseband through a double-balanced mixer. PPF and external LO are also used for the quadrature LO generation in RX. The RX analog baseband circuitry consists of a differential two-stage active LPF and a 10-bit digital-to-analog converter (DAC)-controlled VGA. The active LPF employs Akerberg Mossberg topology for wide bandwidth characteristics up to 300 MHz. The RX includes an ACI cancellation negative feedback network by up-converting the RX1 high-power-level adjacent channel filtered baseband signal to the RF domain and summing with the RX2 input.

Fig. 5. SATCOM RX gain, NF, and IIP3 level diagram.

The mixers in RX1 and ACI cancellation block are driven with anti-phase LOs for generating desired ACI-canceling RF signal.

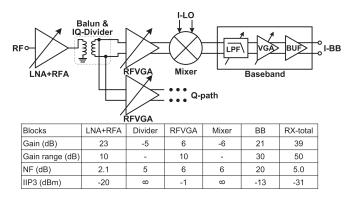

### A. Receiver

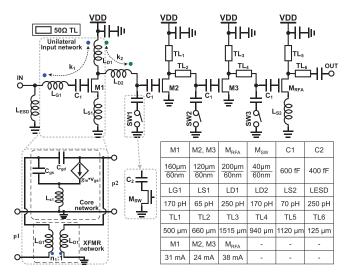

The SATCOM RX gain, noise, and linearity link budget are planned first, as shown in Fig. 5. The RF signal is amplified through a single-ended LNA and divided into I-path and Q-path with differential circuit topology. The total gain is 18 dB in the RF path and 20 dB in the baseband path. The variable gain stages are also distributed in both RF and baseband paths. The main purpose of variable gain in the RF stage is to prevent the baseband circuit from being saturated when the gain provided by external LNA is too high. In this case, the LNA design is critical from the perspective of system overall NF and linearity. Fig. 6 shows the proposed LNA with switched attenuation and unilateral input network. The LNA is based on a common-source configuration, and ground-shorted switches are inserted between the LNA stages. In order to support a wide input power range, the first gain stage and the last gain stage are enhanced by inductive source degeneration for higher linearity, and the transistor sizes are also chosen larger for the capability of high-power input signal. Since the variable attenuation is enabled by the ground-shorted switch, the dramatic load impedance change will cause severe input matching mismatch if the signal has significant reverse path. The weakly coupled transformer feedback provides possible solution of mitigating the reverse signal path without degrading NF [48], [49]. The criterion of the amplifier unilateralization is

$$h_{12(\text{Core})} = -h_{12(\text{XFMR})} \tag{5}$$

where  $h_{(Core)}$  and  $h_{(XFMR)}$  represent the hybrid h-parameters of LNA first-stage core network and the transformer network, as shown in Fig. 6. Considering the gate-drain capacitance  $C_{\rm gd}$ , the calculated LNA core network  $h_{12(Core)}$  is

$$h_{12(\text{Core})} = -\frac{C_{\text{gd}}}{C_{\text{gd}} + \frac{C_{\text{gs}}}{1 + sL_{s1}(sC_{\text{gs}} + g_m)}}$$

(6)

and the transformer network  $h_{12(XFMR)}$  is

$$h_{12(XFMR)} = k_1 \cdot n_1. \tag{7}$$

Fig. 6. Circuit schematic of RX LNA and RF-VGA.

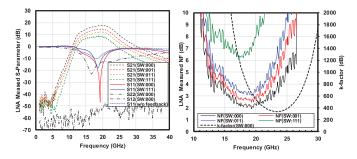

Fig. 7. RX three-stage LNA measured performance, simulated S11 at SW = 111 without unilateralization feedback, and simulated k-factor.

The calculated  $h_{12(Core)}$  has a real part of 0.2 approximately, which is dominant over the imaginary part. For a transformer turn ratio  $n_1 = 1$ , the magnetic coupling coefficient  $k_1$  is then decided 0.2 in order to satisfy the unilateralization criterion. The LNA second-stage input also employs a customized inductor for low-noise impedance matching since the transmission line (TL) is optimized for its characteristic impedance, and therefore, the quality factor is relatively low [50], [51]. The inductors  $L_{D1}$  and  $L_{D2}$  are magnetically coupled for enhancing the inductance and saving the area. The input transformer is modeled using EM simulation; the transformer is simulated with certain diameter and width deviations to ensure reliability under possible process variation. The remaining stages use TLs in the matching blocks. An identical standalone LNA circuit is fabricated for characterization. Fig. 7 shows that the three-stage LNA has a measured peak gain of 17.7 dB with a controllable gain range of 9.0 dB and a 3-dB BW of 7.6 GHz. The minimum NF is measured 2.1 dB in the high-gain mode and 7.0 dB in the low-gain mode. The LNA input reflection coefficient S11 is below -10 dB with the first-stage attenuation switch turned off over 17-21 GHz. By using the unilateralization coupling network, the LNA maximum S11 is degraded by 2 dB when the switch is turned on. By contrast, the simulated S11 at SW = 111 without unilateralization feedback is also shown in Fig. 7(a), and S11 is degraded to worse than -10 dB. The simulated

Fig. 8. Circuit schematic of the RX RF-VGA and double-balanced mixer.

Fig. 9. (a) Circuit schematic of RX baseband LPF. (b) RX LPF simulated gain and frequency characteristics.

stability k-factor [see Fig. 7(b)] shows that the LNA is in stable condition. Since the transformer unilateralization feedback is passive and implemented in the top thick metal layers with metal width wider than 4  $\mu$ m, the transformer feedback is relatively insensitive to process variation.

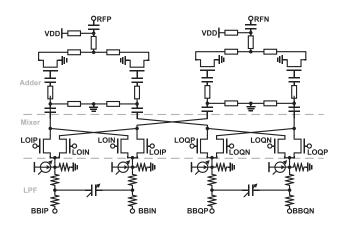

The single-ended RF signal after LNA is converted to differential through a Balun, as shown in Fig. 8. The differential RF signal is then divided into I-path and Q-path for down-converting to baseband frequency. A differential RF-VGA with the switched gain mode is employed for the additional RX variable gain range. By enabling cross-connection with anti-phase signal in the differential RF-VGA output, the RF-VGA can provide 12-dB variable gain in simulation. The down-conversion mixer employs passive double-balanced architecture for suppressing potential LO and RF leakage to the baseband.

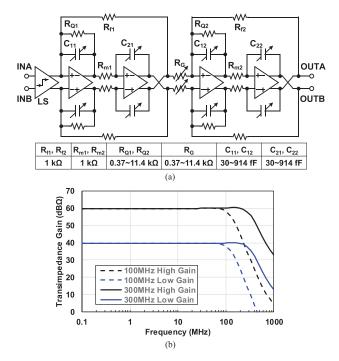

Fig. 9 shows the detailed circuit schematics of the LPF in RX analog baseband. The active LPF is composed of two-stage second-order LPFs with their total roll-off rate of -24 dB/octave. Due to the limited voltage headroom in the deep sub-micrometer CMOS process, the LPF has a current input and behaves as a transimpedance filter. Since the active

Fig. 10. (a) Circuit schematic of RX baseband VGA. (b) RX baseband VGA simulated gain and frequency characteristics.

LPF has a common-mode voltage on half VDD, and the mixer terminal needs to keep a low potential for conducting the transistor, a level shifter (LS) is, therefore, used to shift the low voltage at the mixer to half VDD at the LPF. The two-stage transimpedance LPF has a simulated gain of 60 dB $\Omega$ . The LPF employs Åkerberg-Mossberg topology in order to control quality factor (Q) and pole frequency independently. The quality factor and pole frequency can be expressed as

$$Q = \sqrt{\frac{C_1 R_Q^2}{C_2 R_f R_m}}$$

$$f_p = \frac{1}{\sqrt{C_1 C_2 R_f R_m}}$$

(8)

$$f_p = \frac{1}{\sqrt{C_1 C_2 R_f R_m}} \tag{9}$$

respectively. The variable gain in LPF is realized through changing its second-stage input resistance  $R_G$ . The variable quality-factor, bandwidth, and gain are digitally controlled with a 5-bit resistor bank and capacitor bank.

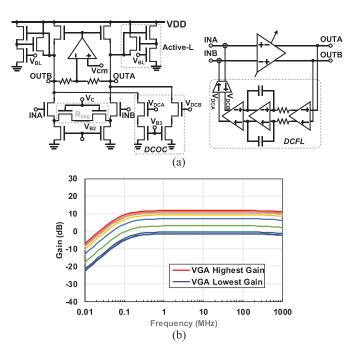

The LPF is followed by a baseband VGA, as shown in Fig. 10. The VGA source degeneration resistance  $R_{\text{deg}}$  can be tuned to realize variable transconductance and, therefore, the variable gain. It realizes a simulated gain tuning range from -2 to 12 dB. Active inductances are used to cancel the output capacitance and enhance the bandwidth of VGA. The active inductances employ Gyrator realization with transistor parasitic capacitance. The dc offset cancellation (DCOC) in the VGA is added to eliminate the dc offset amplification. The dc feedback loop (DCFL) contains an integrator and two gain stages. The VGA with DCFL closed loop shows a high-pass characteristic, which can prevent the dc offset from saturating subsequent circuits.

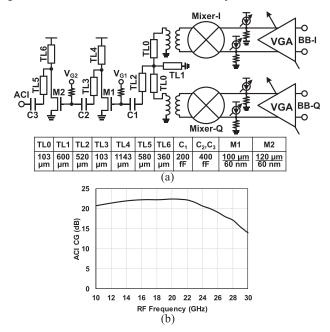

The ACI cancellation block shown in Fig. 11 is used in the RX frequency multiplexing mode. An anti-phase cancellation signal is generated in case the high-level channel-1 signal

Fig. 11. ACI cancellation scheme in the FDMA operation mode.

Fig. 12. (a) Circuit schematic of the RX ACI cancellation block. (b) Simulated conversion gain of the ACI cancellation block.

becomes an adjacent interference of the low-level channel-2 signal. The channel-1 received baseband signal is filtered and up-converted with anti-phase LO. The ACI RF signal is amplified by a two-stage RF-amplifier, as shown in Fig. 12(a). The ACI cancellation block provides a 22-dB gain with a 17-dB variable gain range and a 7-GHz RF bandwidth, as shown in Fig. 12(b). Since the receiving antenna polarizations are the same in the frequency multiplexing mode, the RX two channels can be switched by sensing output power, and the ACI is, therefore, implemented in one channel. The ACI signal is tapped on RX1 by T-junction TL. By adding the ACI path, the RX NF and gain are degraded. From the simulation, when the ACI is enabled, the RX2 NF is 0.53 dB increased, and the gain is 1.2 dB decreased.

## B. Transmitter

As shown in Fig. 13, the SATCOM direct-conversion TX baseband input is connected to mixers through an RC passive

Fig. 13. Circuit schematic of the LPF, mixer, and RF adder in SATCOM TX.

Fig. 14. Circuit schematic of the PA in SATCOM TX.

LPF with variable passband controlled by selecting capacitor bank. The LPF cutoff frequency can be tuned from 50 to 400 MHz with 6-bit binary control. The mixer is passive and with double-balanced topology; the mixer RF port dc offset is tunable in order to cancel the LO feedthrough (LOFT) caused by potential transistor mismatch [52]–[54]. The up-converted RF IQ signal is added to two differential paths RFP and RFN through an RF adder with a 7-dB RF gain, as shown in Fig. 13.

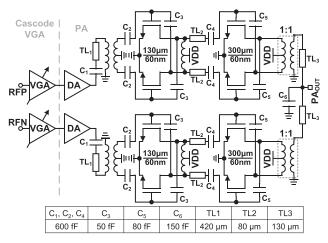

The RF adder differential output RFP and RFN is connected to a differential PA through an RF VGA, as shown in Fig. 14. The RF VGA is based on current steering cascode topology [55], the current steering transistor is controlled by a 10-bit DAC, and the VGA realized a variable gain of 10 dB. The differential PA has three stages. The first stage contains two parallel single-ended DA. The SATCOM TX is designed for achieving high linearity due to the requirement of output power and drive ability. In the CMOS process, over 10-dBm OP1dB output power PA has been demonstrated [56]-[61]; however, it is not high enough to drive the 3-dBW external amplifier. Further increasing the PA output power, larger devices and transformer-based power combining techniques can be used. Therefore, in this TX, the differential path unit PA final two stages are divided to differential again with four paths power combining in total, as shown in Fig. 14. Power matching is used in the PA load network to achieve high output power

Fig. 15. (a) PA matching network illustrated Smith chart. (b) PA matching network with transformer 3-D view. (c) PA measured small-signal performance. (d) PA measured large-signal performance.

and linearity. Fig. 15(a) shows the load–pull result of the PA transistor pair, and the higher output power leads to a low output impedance. In the current-type power-combining load network, the load impedance seen by the two identical paths will be twice of  $R_L$ . Since a transformer-based balun is required for converting differential to single-ended, the matching network can be easily realized by the combined network of a balun, a series TL, and a shunt capacitor. The realized matching network is shown in Fig. 15(b), and a high-quality-factor transformer is carefully designed for low-loss power matching. The transformer has a 1:1 turn ratio and vertically stacked structure for achieving high-quality factor and high coupling coefficient at millimeter-wave frequency [56], [61]. To improve the simulation and EM modeling accuracy, the standalone transformer is fabricated and measured to establish a semi-empirical model by fitting the EM-based model with the measured performance. The simulated PA transformer-based output network has a 2.5% impedance mismatch and a 0.7° phase mismatch seen by the transistor pairs, and the mismatch will not degrade the in-phase current-type power combining performance. For a reliable design, the PA is located at the corner of the chip with a strong power supply and ground, and it is also close to the decoupling capacitors to enhance the power integrity and PA stability. The PA transistor pair core utilizes a cross-coupled capacitive neutralization technique to enhance reverse isolation and to improve the power gain. Since the PA large power capability can be degraded by the hot-carrier-injection (HCI) effect, further consideration of the HCI healing technique can be useful for enhancing the PA reliability [62]. A standalone PA is fabricated, including the final two power stages and one DA stage. The standalone PA is measured with a peak gain of 23.7 dB with a 3-dB BW of 12 GHz. The standalone PA small-signal measurement result is shown in Fig. 15(c). The large-signal measurement result of the standalone PA is shown

| TX       |      |  |  |  |

|----------|------|--|--|--|

| LO 0.1   |      |  |  |  |

| Adder    | 0.05 |  |  |  |

| VGA      | 0.06 |  |  |  |

| DA       | 0.04 |  |  |  |

| PA       | 0.37 |  |  |  |

| RX (1ch) |      |  |  |  |

| LNA+RFA  | 0.12 |  |  |  |

| RFVGA    | 0.06 |  |  |  |

| LO       | 0.1  |  |  |  |

| BBVGA    | 0.02 |  |  |  |

| BBLPF    | 0.13 |  |  |  |

| ACI      | 0.07 |  |  |  |

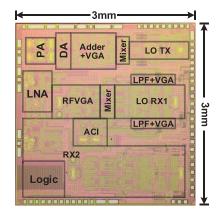

Fig. 16. Die micrograph and power breakdown table.

in Fig. 15(d); at class-A bias condition, the PA has a saturated output ( $P_{SAT}$ ) of 20.7 dBm and a 1-dB compression point ( $P_{1dB}$ ) of 15.9 dBm at 29 GHz.

### IV. MEASUREMENT RESULTS

The Ka-band SATCOM transceiver is fabricated in a standard 65-nm CMOS process with nine metal layer stacks, including one thick metal layer and one ultra-thick metal layer. The chip micrograph is shown in Fig. 16. The transceiver occupies a chip area of 3 mm × 3 mm. The VDD routing and the RF signal are mainly in the ultra-thick metal layer, the analog and digital circuits are designed in the thin metal layers for a compact area, and the GND routing uses all the metal layers. The TX is located at the top side, the dual-channel RX is located at the lower side, and the RF input/output ports and the LO ports are located at the left- and right-hand sides, respectively. The transceiver power breakdown is also shown in Fig. 16, the TX consumes 0.62 W, and the dual-channel RX consumes 0.93 W in total, including the ACI cancellation block. The RF blocks use a 1.05-V supply, and the analog baseband uses a 1.2-V supply. An evaluation PCB board is implemented with Megtron 6 material, and the chip is mounted using wire bonding. In the future CMOS III-V hybrid system integration, the ICs can be placed in the same cavity for a low wire bonding loss, and the thermally conductive adhesive glue can be used to attach the ICs with good thermal performance.

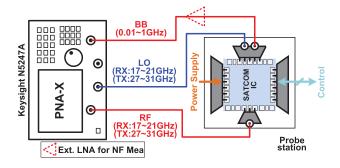

The SATCOM transceiver's small-signal performance is first evaluated on a probe station using a vector network analyzer (Keysight N5247A). Fig. 17 illustrates the general setup for evaluating both TX and RX using N5247A, two of the ports are connected to the input/output of the TX or RX on-chip through RF probes, and the external LO signal is also generated and controlled by N5247A with a typical phase noise of -97 dBc/Hz at a 1-MHz offset at the Ka-band. The external LO power is 3 dBm for both TX and RX. The RF and LO frequency offsets are set to 100 MHz. The digital control and power supply are connected using eye-pass probes on the other two sides of the chip. An external LNA is used at the baseband output to keep high enough gain in RX NF measurement. For setup simplicity, the double-sideband (DSB) noise is measured only. The measurement setup is calibrated to the probe tips of signal input and output. Fig. 18(a) shows that the measured

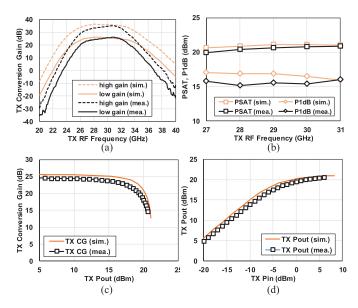

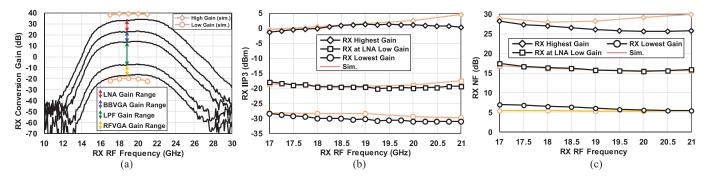

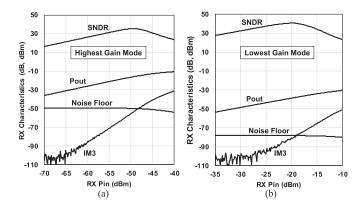

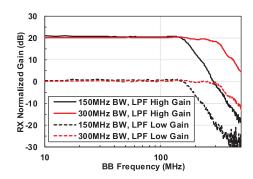

Fig. 17. Measurement setup using a vector network analyzer.

peak conversion gains of the TX are 26.1 and 35.1 dB on low- and high-gain modes, respectively. The TX 3-dB bandwidth on the low-gain mode is from 26.9 to 32.6 GHz and 27.0 to 32.4 GHz on the high-gain mode. The TX large-signal characteristic is evaluated using a power meter (Keysight E4417A). Fig. 18(b) shows the measured TX  $P_{SAT}$  and  $P_{1dB}$ over the operation frequency from 27 to 31 GHz.  $P_{\rm SAT}$  and  $P_{1\,\mathrm{dB}}$  are measured higher than 20 and 15 dBm, respectively. Fig. 19(a) shows that the RX measured peak conversion gain on the high-gain mode is 34.3 dB, and the 3-dB bandwidth is from 16.9 to 22.5 GHz. The measured total variable gain range is 50 dB. Fig. 19(b) and (c) shows the RX measured input third-order intercept point (IIP3) and NF on different gain conditions. On the high-gain mode, the RX achieves an IIP3 of -30 dBm and an NF of 6 dB at 19 GHz. In the 17–21-GHz operation band, the IIP3 varies from -28.3 to -31.1 dBm, and the NF is between 5.4 and 7.0 dB. The signal-to-noise and distortion ratio (SNDR) of the RX can be calculated from the measured RX gain, intermodulation distortion (IM3), and NF. Fig. 20 shows the RX achieves a peak SNDR of 35.3 dB at a -48.5-dBm input power on the high-gain mode and 40.1 dB at a -20.0-dBm input on the low-gain mode with a 300-MHz signal bandwidth. Fig. 21 shows the measured RX analog filter gain and frequency characteristics normalized to the lowest gain mode; it has a variable gain of 20 dB and is capable of variable bandwidth up to 300 MHz. For the digital-to-RF system integration, a 10-dBm full-scale-input differential ADC with a sampling rate higher than 600 MS/s can be used in the RX, considers a 30-dB signal SNR for demodulation, a 20-dB power range, a 6-dB quantization noise margin, and a 6-dB signal PAPR margin, and the required ADC ENOB is estimated of 10 bit. The ADC ENOB requirement can be relaxed by a variable gain driver preceding the ADC, and the required driver OIP3 is estimated at 30 dBm.

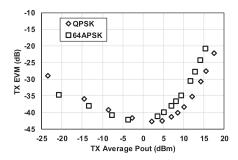

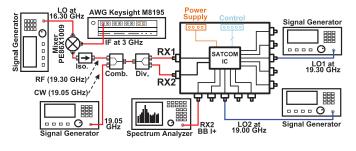

The SATCOM transceiver is also evaluated using modulated signals of QPSK, 32APSK, 64APSK, and 256APSK. Modulation schemes regulated in SATCOM standard DVB-S2X are included in the measurement. In the TX measurement, the baseband IQ differential signals are generated by an arbitrary waveform generator (AWG) (Keysight M8195A) with a symbol rate of 150 MBaud and a roll-off factor of 0.1, the 29-GHz RF output signal is down-converted to a 3-GHz IF frequency using an external mixer and evaluated by an oscilloscope (Keysight DSO90804A), and the output average power is measured by a power meter directly at the RF port. The

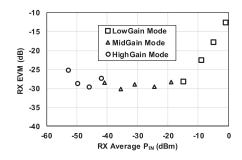

Fig. 18. Measured and simulated (a) TX conversion gain, (b) TX  $P_{\rm SAT}$  and  $P_{\rm 1\,dB}$ , (c) TX conversion gain compression, and (d) power compression.

external LO in the EVM measurement uses Keysight E8257D with a typical phase noise of -130 dBc/Hz at a 1-MHz offset at the Ka-band. The external LO power is 3 dBm for both TX and RX. Fig. 22 shows the TX measured EVM at different average output power in both QPSK and 64APSK modulation schemes, and the power level is tuned by adjusting AWG signal level and external attenuators at the baseband input. The measured average output power is 17.5 dBm with EVM of -22.1 dB in QPSK and 15.3 dBm with EVM of -20.7 dB in 64APSK. Fig. 23 shows the summary of the TX measured the best constellation, EVM, average output power, and ACPR in modulation schemes of QPSK, 16APSK, 64APSK, and 256APSK. The measured TX EVMs achieve lower than -42 dB with ACPR around 45 dB. To achieve the target EVM in the digital-to-RF system integration, consider a 40-dB signal SNR, a 15-dB power range, and a 6-dB signal PAPR margin, and the corresponding DAC bit for TX is 10 bit. In the RX measurement, the 19-GHz modulated RF signals are generated by up-converting AWG (Keysight M8195A) baseband signal to 19 GHz using a vector-signal generator (VSG) (Keysight M8267D), the symbol rate is 150 MBaud, and the roll-off factor is 0.1. The baseband output signal is evaluated by an oscilloscope (Keysight DSO90804A). The RF power is attenuated using external attenuators, and the input average power is measured by a power meter directly at the RF port. Fig. 24 shows the RX measured EVM at different average input powers, the power level is tuned by adjusting VSG signal level and external attenuators at the RF input, and the RX gain is also tuned to maintain the best EVM performance with different input power levels. The 64APSK modulation is used in the high- and medium-gain modes, and the QPSK modulation is used in the low-gain mode. The measured average input power is -53 dBm with EVM of -25.1 dB in 64APSK; the dynamic range is more than 35 dB with EVM under -25 dBm. The RX is also capable of high-power input; it achieves EVM of -12.6 dB at a -1-dBm

Fig. 19. RX measured and simulated (a) conversion gain, (b) IIP3, and (c) NF.

Fig. 20. RX measured SNDR in (a) high-gain mode and (b) low-gain mode.

Fig. 21. RX measured baseband frequency characteristics and gain control.

Fig. 22. TX measured EVM as a function of the average output power.

average input power in QPSK modulation. Fig. 25 shows the summary of the RX measured the best constellation, EVM, and average input power in different modes. The measured RX EVMs achieve lower than -25 dB with the variable gain setting.

| Carrier Freq.            | 29 GHz   | 29 GHz   | 29 GHz   | 29 GHz   |  |

|--------------------------|----------|----------|----------|----------|--|

| 64APSK<br>Constellation  | 0        |          |          |          |  |

| Modulation               | 256 APSK | 64 APSK  | 16 APSK  | QPSK     |  |

| Data Rate                | 1.2 Gbps | 0.9 Gbps | 0.6 Gbps | 0.3 Gbps |  |

| EVM                      | -42.3 dB | -42.1 dB | -42.3 dB | -42.7 dB |  |

| Average P <sub>OUT</sub> | -3.3 dBm | -3.7 dBm | -2.2 dBm | 2.1 dBm  |  |

| ACPR                     | 44.3 dB  | 44.5 dB  | 43.5 dB  | 45.7 dB  |  |

| Roll-off factor          | 0.1      | 0.1      | 0.1      | 0.1      |  |

Fig. 23. TX measured constellation summary.

Fig. 24. RX measured EVM as a function of the average input power.

| Carrier Freq.           | 19 GHz    | 19 GHz    | 19 GHz    | 19 GHz   |  |

|-------------------------|-----------|-----------|-----------|----------|--|

| Constellation           |           |           |           | * *      |  |

| Modulation              | 64 APSK   | 64 APSK   | 64 APSK   | QPSK     |  |

| Data Rate               | 0.9 Gbps  | 0.9 Gbps  | 0.9 Gbps  | 0.3 Gbps |  |

| EVM                     | -25.1 dB  | -30.1 dB  | -29.6 dB  | -17.9 dB |  |

| Average P <sub>IN</sub> | -53 dBm   | -35.5 dBm | -24.5 dBm | -5 dBm   |  |

| Mode                    | High Gain | Mid Gain  | Mid Gain  | Low Gain |  |

| Roll-off factor         | 0.1       | 0.1       | 0.1       | 0.1      |  |

Fig. 25. RX measured constellation summary.

The dual-channel RX ACI cancellation is measured with two signal sources, as shown in Fig. 26: one is a 19.05-GHz continuous-wave (CW) generated by the signal generator, and another is the modulated RF signal at 19.3 GHz. The dual-channel RX operates in the FDMA mode, the modulated RF signal will be demodulated in RX1, and the CW signal is

|                        | 1                        |                                |                      |                      |                      |                         |               |

|------------------------|--------------------------|--------------------------------|----------------------|----------------------|----------------------|-------------------------|---------------|

|                        | This work                | JSSC19 [5]                     | TMTT18[6]            | JSSC17[25]           | JSSC18 [24]          | ISSCC18 [30]            | JSSC20 [23]   |

|                        | This work                | Northrop Grumman               | Ulm U.               | IBM                  | LG                   | Qualcomm                | TokyoTech     |

| Process                | 65nm CMOS                | 45nm CMOS<br>SOI               | 250nm SiGe<br>BiCMOS | 130nm SiGe<br>BiCMOS | 28nm CMOS            | 28nm CMOS               | 65nm CMOS     |

| Application            | SATCOM                   | SATCOM                         | SATCOM               | 5G                   | 5G                   | 5G                      | 5G            |

| Architecture           | Direct Conversion        | Super Heterodyne<br>Digital IF | RF                   | Super<br>Heterodyne  | Direct<br>Conversion | Super<br>Heterodyne     | RF            |

| Integration Level      | RF+BB                    | RF+BB                          | RF                   | RF+IF                | RF+BB                | RF+IF                   | RF            |

| Elements               | 1TX+2RX                  | 1TX+1RX                        | 4TX+2RX              | 32TX+32RX            | 8TX+8RX              | 24TX+24RX               | 8TX+8RX       |

| Operating Band         | TX: 27- 31               | TX: 42- 47                     | TX: 29.5- 30.8       | TX: 27- 29           | TX: 25.8- 28.0       | TX:25.0- 31.0           | TX:26.5- 29.5 |

| (GHz)                  | RX: 17- 21               | RX:20- 22                      | RX:19.7- 21          | RX: 27.5- 29         | RX: 25.8- 28.0       | RX:26.5- 29.5           | RX:26.5- 29.5 |

| Roll-off factor        | 0.1                      | N/A                            | N/A                  | N/A                  | N/A                  | N/A                     | 0.35          |

| Ch. Bandwidth(GHz)     | 0.6                      | 0.6                            | N/A                  | N/A                  | 0.5                  | 0.4                     | N/A           |

| RX Gain Range (dB)     | 50 (-16 to 34)           | 14 (3 to 17) *                 | 0                    | 30                   | 39 (30 to 69)        | 24 (10 to 34)           | 0             |

| RX NF (dB)             | 5.4                      | 8.0 *                          | 5                    | 3.7                  | 6.7                  | 4.7                     | 4.2           |

| RX IIP3 (dBm)          | -30                      | N/A                            | -24.3                | -11.9                | -25.8                | N/A                     | -18.4         |

| ACI Cancellation (dB)  | 7.9<br>(@100MHz BW)      | N/A                            | N/A                  | N/A                  | N/A                  | N/A                     | N/A           |

| TX Psat (dBm)          | 20.5                     | >23                            | 6.19                 | 16.6                 | 10.5                 | 14                      | 15.1          |

| TX P1dB (dBm)          | 15.4                     | N/A                            | 4.19                 | 14.1                 | 9.5                  | 12                      | 11.3          |

| TX Pout@2%EVM<br>(dBm) | 12@QPSK<br>9.5@64APSK    | N/A                            | N/A                  | N/A                  | -18**                | 6.7@QPSK*<br>5.3@64QAM* | 7.0@64QAM     |

| TX ACPR@2%EVM<br>(dB)  | 37.6@QPSK<br>40.3@64APSK | N/A                            | N/A                  | N/A                  | 31.6                 | N/A                     | N/A           |

| Supply Voltage (V)     | 1.05 / 1.2               | 1 / 1.8 / 3                    | 2.5 / 3.3            | 2.7                  | 1.05                 | 1                       | 1             |

| PD C (U)               | TX: 0.62                 |                                | TX: 0.34             | TX: 4.6              | TX: 0.7              | TX: 2.16                | TX: 2         |

| PDC (W)                | RX: 0.93                 | 2.82                           | RX: 0.24             | RX: 3.3              | RX: 0.4              | RX: 1.0                 | RX: 0.9       |

| Area (mm²)             | 9                        | 28.4                           | 11.6                 | 166                  | 7.28                 | 27.8                    | 12            |

TABLE II

PERFORMANCE COMPARISON OF Ka-BAND MILLIMETER-WAVE TRANSCEIVERS FOR SATCOM, 5G, AND BEYOND

<sup>\*</sup> Estimated in figure \*\*Calculated from TX EIRP

Fig. 26. ACI cancellation measurement setup.

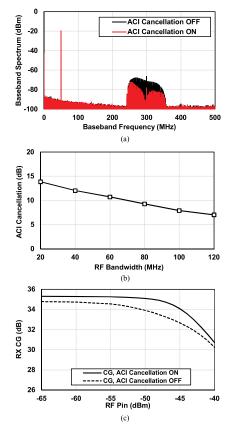

meant to be down-converted by RX2. The two signal sources are combined and connected to both RX1 and RX2 input ports. In this setup, the 19.05-GHz CW down-converted baseband is the desired output, and the 19.3-GHz modulated RF signal is the interference signal located in the adjacent channel. The RX2 baseband output is observed using a Spectrum Analyzer without external LO phase control. To keep the same true time delay between the ACI path and the RX2 path, the RF cable from the divider feed to RX2 is adjusted slightly longer than to RX1. Fig. 27(a) shows the measured spectrum in RX2 baseband output; when the ACI cancellation is enabled, the adjacent channel signal down-converted spectrum

at 300 MHz is canceled to a lower power level. The cancellation reduces the total input power including, the undesired ACI signal; the linearity for signal in the desired channel is, therefore, improved. Fig. 27(b) shows the effective cancellation results against ACI signal RF bandwidth. For ACI signal bandwidth of 100 MHz, the effective cancellation is 7.9 dB. The effective cancellation is more than 10 dB for ACI signal bandwidth of 60 MHz. The channel power is measured by the Spectrum Analyzer. Fig. 27(c) shows the ACI cancellation scheme improves the RX input 1-dB gain compression point by 4 dB.

The performance comparison of *Ka*-band millimeter-wave transceivers for SATCOM and 5G is listed in Table II. The SATCOM RX demonstrates low NF and high linearity characteristics with a minimum NF of 5.4 dB and an IIP3 of –30 dBm on the high-gain mode over 17–21 GHz. The RX achieves a 50-dB variable gain range and wide dynamic range. The dual-channel RX realizes 7.9-dB ACI cancellation with a signal bandwidth of 100 MHz; the cancellation scheme further enhances the RX linearity in the FDMA multiplexing mode. The SATCOM TX shows highly linear characteristics by achieving 12-dBm average output power using QPSK and 9.5-dBm output power using 64APSK with EVM below 2%.

Fig. 27. ACI cancellation measurement results. (a) Measured baseband spectrum. (b) ACI cancellation with different RF bandwidth. (c) RX linearity improvement with ACI cancellation.

# V. CONCLUSION

This article first presents a Ka-band CMOS transceiver for SATCOM. The transceiver consists of a highly linear TX and dual-channel wide-dynamic-range RX. To increase RX dynamic range, the RF stages and baseband stages can offer a variable gain of 50 dB in total. A dual-coupling transformer is used in LNA for a low-noise and wideband design; it also mitigates the loading effect from switched attenuators. An additional ACI cancellation scheme is implemented to further enhance the RX linearity in the frequency multiplexing mode. The SATCOM TX employs four-way power combining and a high-quality-factor transformer to maintain highly linear RF output. The transceiver achieves a P<sub>SAT</sub> of 20.5 dBm and an average output power of 12 dBm with an EVM of below 2%. The dual-channel RX achieves an NF of 5.4 dB and an IIP3 of -30 dBm on the high-gain mode; the ACI cancellation is measured of 7.9 dB with a 100-MHz signal bandwidth.

### REFERENCES

- [1] G. Maral, M. Bousquet, and Z. Sun, Satellite Communications Systems: Systems, Techniques and Technology. Hoboken, NJ, USA: Wiley, 2020.

- [2] H. Peyravi, "Medium access control protocols performance in satellite communications," *IEEE Commun. Mag.*, vol. 37, no. 3, pp. 62–71, Mar. 1999.

- [3] M. de Sanctis, E. Cianca, G. Araniti, I. Bisio, and R. Prasad, "Satellite communications supporting internet of remote things," *IEEE Internet Things J.*, vol. 3, no. 1, pp. 113–123, Feb. 2016.

- [4] G. M. Rebeiz and L. M. Paulsen, "Advances in SATCOM phased arrays using silicon technologies," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2017, pp. 1877–1879.

- [5] T. R. LaRocca et al., "Secure satellite communication digital IF CMOS Q-band transmitter and K-band receiver," IEEE J. Solid-State Circuits, vol. 54, no. 5, pp. 1329–1338, May 2019.

- [6] F. Tabarani, L. Boccia, T. Purtova, A. Shamsafar, H. Schumacher, and G. Amendola, "0.25-μm BiCMOS system-on-chip for K-/Ka-band satellite communication transmit–receive active phased arrays," *IEEE Trans. Microw. Theory Techn.*, vol. 66, no. 5, pp. 2325–2339, May 2018.

- [7] K. K. W. Low, S. Zihir, T. Kanar, and G. M. Rebeiz, "A scalable switchable dual-polarized 256-element Ka-band SATCOM transmit phasedarray with embedded RF driver and ±70° beam scanning," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Aug. 2020, pp. 821–824.

- [8] W. M. Abdel-Wahab et al., "A modular architecture for wide scan angle phased array antenna for K/Ka mobile SATCOM," in *IEEE MTT-S Int.* Microw. Symp. Dig., Jun. 2019, pp. 1076–1079.

- [9] G. Gultepe, S. Zihir, T. Kanar, and G. M. Rebeiz, "A dual-polarized 1024-element Ku-band SATCOM transmit phased-array with ±70° Scan and 43.5 dBW EIRP," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Aug. 2020, pp. 837–840.

- [10] C. Marcu et al., "A 90 nm CMOS low-power 60 GHz transceiver with integrated baseband circuitry," *IEEE J. Solid-State Circuits*, vol. 44, no. 12, pp. 3434–3447, Dec. 2009.

- [11] A. Binaie *et al.*, "A scalable 60 GHz 4-element MIMO transmitter with a frequency-domain-multiplexing single-wire interface and harmonic-rejection-based de-multiplexing," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Aug. 2020, pp. 1–4.

- [12] B. Razavi et al., "A low-power 60-GHz CMOS transceiver for WiGig applications," in Proc. Symp. VLSI Circuits, Jun. 2013, pp. C300–C301.

- [13] K. Okada et al., "A full 4-channel 6.3 Gb/s 60 GHz direct-conversion transceiver with low-power analog and digital baseband circuitry," in Proc. IEEE Int. Solid-State Circuits Conf., Feb. 2012, pp. 218–220.

- [14] V. Vidojkovic et al., "A low-power radio chipset in 40 nm LP CMOS with beamforming for 60 GHz high-data-rate wireless communication," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2013, pp. 236–237.

- [15] Y. Wang et al., "A 100 mW 3.0 Gb/s spectrum efficient 60 GHz biphase OOK CMOS transceiver," in Proc. Symp. VLSI Circuits, Jun. 2017, pp. C298–C299.

- [16] K. Dasgupta et al., "A 60-GHz transceiver and baseband with polarization MIMO in 28-nm CMOS," IEEE J. Solid-State Circuits, vol. 53, no. 12, pp. 3613–3627, Dec. 2018.

- [17] T. Sowlatiet et al., "A 60-GHz 144-element phased-array transceiver for backhaul application," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3640–3659, Dec. 2018.

- [18] B. Sadhu et al., "A 250-mW 60-GHz CMOS transceiver SoC integrated with a four-element AiP providing broad angular link coverage," *IEEE J. Solid-State Circuits*, vol. 55, no. 6, pp. 1516–1529, Jun. 2020.

- [19] M. Boers et al., "A 16TX/16RX 60 GHz 802.11ad chipset with single coaxial interface and polarization diversity," *IEEE J. Solid-State Circuits*, vol. 49, no. 12, pp. 3031–3045, Dec. 2014.

- [20] W. Deng et al., "An energy-efficient 10-Gb/s CMOS millimeter-wave transceiver with direct-modulation digital transmitter and I/Q phasecoupled frequency synthesizer," IEEE J. Solid-State Circuits, vol. 55, no. 8, pp. 2027–2042, Aug. 2020.

- [21] K. Kibaroglu, M. Sayginer, and G. M. Rebeiz, "A low-cost scalable 32-element 28-GHz phased array transceiver for 5G communication links based on a 2 × 2 beamformer flip-chip unit cell," *IEEE J. Solid-State Circuits*, vol. 53, no. 5, pp. 1260–1274, May 2018.

- [22] L. Wu, H. F. Leung, A. Li, Z. Hong, Y. Qin, and H. C. Luong, "A 4-element 60-GHz CMOS phased-array receiver with transformer-based hybrid-mode mixing and closed-loop beam-forming calibration," in *Proc. Symp. VLSI Circuits*, Jun. 2013, pp. C296–C297.

- [23] J. Pang et al., "A 28-GHz CMOS phased-array beamformer utilizing neutralized bi-directional technique supporting dual-polarized MIMO for 5G NR," IEEE J. Solid-State Circuits, vol. 55, no. 9, pp. 2371–2386, Sep. 2020.

- [24] H. Kim et al., "A 28-GHz CMOS direct conversion transceiver with packaged 2 × 4 antenna array for 5G cellular system," *IEEE J. Solid-State Circuits*, vol. 53, no. 5, pp. 1245–1259, May 2018.

- [25] B. Sadhu et al., "A 28-GHz 32-element TRX phased-array IC with concurrent dual-polarized operation and orthogonal phase and gain control for 5G communications," *IEEE J. Solid-State Circuits*, vol. 52, no. 12, pp. 3373–3391, Dec. 2017.

- [26] J.-L. Kuo et al., "60-GHz four-element phased-array transmit/receive system-in-package using phase compensation techniques in 65-nm flipchip CMOS process," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 3, pp. 743–756, Mar. 2012.

- [27] H. Krishnaswamy and H. Hashemi, "A fully integrated 24 GHz 4-channel phased-array transceiver in 0.13 μm CMOS based on a variable-phase ring oscillator and PLL architecture," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2007, pp. 124–591.

- [28] T.-S. Chu and H. Hashemi, "True-time-delay-based multi-beam arrays," IEEE Trans. Microw. Theory Techn., vol. 61, no. 8, pp. 3072–3082, Aug. 2013.

- [29] K. Khalaf et al., "A 60-GHz 8-way phased-array front-end with T/R switching and calibration-free beamsteering in 28-nm CMOS," IEEE J. Solid-State Circuits, vol. 53, no. 7, pp. 2001–2011, Jul. 2018.

- [30] J. D. Dunworth et al., "A 28 GHz bulk-CMOS dual-polarization phasedarray transceiver with 24 channels for 5G user and basestation equipment," in Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2018, pp. 70–72.

- [31] A. Natarajan, A. Komijani, X. Guan, A. Babakhani, and A. Hajimiri, "A 77-GHz phased-array transceiver with on-chip antennas in silicon: Transmitter and local LO-path phase shifting," *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 2807–2819, Dec. 2006.

- [32] J. Pang et al., "A 28-GHz CMOS phased-array transceiver based on LO phase-shifting architecture with gain invariant phase tuning for 5G new radio," *IEEE J. Solid-State Circuits*, vol. 54, no. 5, pp. 1228–1242, Mar. 2019.

- [33] A. G. Roy et al., "A 37-40 GHz phased array front-end with dual polarization for 5G MIMO beamforming applications," in Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC), Jun. 2019, pp. 251–254.

- [34] Y. Wang et al., "A 39 GHz 64-element phased-array CMOS transceiver with built-in calibration for large-array 5G NR," in Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC), Jun. 2019, pp. 279–282.

- [35] M. Johnson et al., "Code-domain multiplexing for shared IF/LO interfaces in millimeter-wave MIMO arrays," IEEE J. Solid-State Circuits, vol. 55, no. 5, pp. 1270–1281, May 2020.

- [36] M.-Y. Huang and H. Wang, "A mm-Wave Wideband MIMO RX with instinctual array-based blocker/signal management for ultralow-latency communication," *IEEE J. Solid-State Circuits*, vol. 54, no. 12, pp. 3553–3564, Dec. 2019.

- [37] N. S. Mannem, M.-Y. Huang, T.-Y. Huang, and H. Wang, "A reconfigurable hybrid series/parallel Doherty power amplifier with antenna VSWR resilient performance for MIMO arrays," *IEEE J. Solid-State Circuits*, vol. 55, no. 12, pp. 3335–3348, Dec. 2020.

- [38] M. Kalantari, H. Shirinabadi, A. Fotowat-Ahmadi, and C. P. Yue, "4.7 A single-antenna W-band FMCW radar front-end utilizing adaptive leakage cancellation," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2020, pp. 88–90.

- [39] H. Jia et al., "A 77 GHz frequency doubling two-path phased-array FMCW transceiver for automotive radar," *IEEE J. Solid-State Circuits*, vol. 51, no. 10, pp. 2299–2311, Oct. 2016.

- [40] D. Guermandi et al., "A 79-GHz 2 × 2 MIMO PMCW radar SoC in 28-nm CMOS," IEEE J. Solid-State Circuits, vol. 52, no. 10, pp. 2613–2626, Oct. 2017.

- [41] A. Townley et al., "A 94-GHz 4TX-4RX phased-array FMCW radar transceiver with antenna-in-package," IEEE J. Solid-State Circuits, vol. 52, no. 5, pp. 1245–1259, May 2017.

- [42] T. Ma et al., "A CMOS 76–81-GHz 2-TX 3-RX FMCW radar transceiver based on mixed-mode PLL chirp generator," IEEE J. Solid-State Circuits, vol. 55, no. 2, pp. 233–248, Feb. 2020.

- [43] Y. Wang et al., "A CMOS Ka-band SATCOM transceiver with ACI-cancellation enhanced dual-channel low-NF wide-dynamic-range RX and high-linearity TX," in Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC), Aug. 2020, pp. 355–358.

- [44] S. Peik, Satellite Communication Lecture Notes ASC. Bremen, Germany: Hochschule Bremen, 2013.

- [45] ETSI. (2021). ETSI TR 102 376-2 V1.2.1. [Online]. Available: https:// dvb.org/specifications/

- [46] Qorvo. (2021). Power Amplifiers. [Online]. Available: https://www. qorvo.com/products/amplifiers/power-amplifiers

- [47] Analog Devices. (2021). Low Noise Amplifiers. [Online]. Available: https://www.analog.com/en/products/amplifiers/rf-amplifiers/low-noise-amplifiers

- [48] M. P. van der Heijden, L. C. N. D. Vreede, and J. N. Burghartz, "On the design of unilateral dual-loop feedback low-noise amplifiers with simultaneous noise, impedance, and IIP3 match," *IEEE J. Solid-State Circuits*, vol. 39, no. 10, pp. 1727–1736, Oct. 2004.

- [49] P. R. Gray, P. Hurst, R. G. Meyer, and S. Lewis, Analysis and Design of Analog Integrated Circuits. Hoboken, NJ, USA: Wiley, 2001.

- [50] K. Okada et al., "A 60-GHz 16QAM/8PSK/QPSK/BPSK direct-conversion transceiver for IEEE802.15.3c," IEEE J. Solid-State Circuits, vol. 46, no. 12, pp. 2988–3004, Dec. 2011.

- [51] N. Li, K. Matsushita, N. Takayama, S. Ito, K. Okada, and A. Matsuzawa, "Evaluation of a multi-line de-embedding technique up to 110 GHz for millimeter-wave CMOS circuit design," *IEICE Trans. Fundamentals Electron., Commun. Comput. Sci.*, vol. E93-A, no. 2, pp. 431–439, Feb. 2010.

- [52] R. Wu et al., "64-QAM 60-GHz CMOS transceivers for IEEE 802.11ad/ay," IEEE J. Solid-State Circuits, vol. 52, no. 11, pp. 2871–2891, Nov. 2017.

- [53] Y. Wang et al., "A 60-GHz 3.0-Gb/s spectrum efficient BPOOK transceiver for low-power short-range wireless in 65-nm CMOS," IEEE J. Solid-State Circuits, vol. 54, no. 5, pp. 1363–1374, May 2019.

- [54] J. Pang et al., "A 50.1-Gb/s 60-GHz CMOS transceiver for IEEE 802.11ay with calibration of LO feedthrough and I/Q imbalance," IEEE J. Solid-State Circuits, vol. 54, no. 5, pp. 1375–1390, May 2019.

- [55] C.-C. Kuo, Z.-M. Tsai, J.-H. Tsai, and H. Wang, "71-76 GHz CMOS variable gain amplifier using current steering technique," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Jun. 2008, pp. 609–612.

- [56] F. Wang and H. Wang, "24.1 A 24-to-30 GHz watt-level broadband linear Doherty power amplifier with multi-primary distributed-activetransformer power-combining supporting 5G NR FR2 64-QAM with >19 dBm average pout and >19% average PAE," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2020, pp. 362–364.

- [57] S. Hu, F. Wang, and H. Wang, "A 28-/37-/39-GHz linear Doherty power amplifier in silicon for 5G applications," *IEEE J. Solid-State Circuits*, vol. 54, no. 6, pp. 1586–1599, Jun. 2019.

- [58] H. T. Nguyen and H. Wang, "A coupler-based differential mm-wave Doherty power amplifier with impedance inverting and scaling baluns," *IEEE J. Solid-State Circuits*, vol. 55, no. 5, pp. 1212–1223, May 2020.

- [59] M. Vigilante and P. Reynaert, "A wideband class-AB power amplifier with 29–57-GHz AM–PM compensation in 0.9-V 28-nm bulk CMOS," *IEEE J. Solid-State Circuits*, vol. 53, no. 5, pp. 1288–1301, May 2018.

- [60] D. Zhao and P. Reynaert, "A 40 nm CMOS E-band transmitter with compact and symmetrical layout floor-plans," *IEEE J. Solid-State Circuits*, vol. 50, no. 11, pp. 2560–2571, Nov. 2015.

- [61] Q. J. Gu, Z. Xu, and M. F. Chang, "Two-way current-combining W-band power amplifier in 65-nm CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 5, pp. 1365–1374, May 2012.

- [62] R. Wu et al., "19.5 An HCI-healing 60 GHz CMOS transceiver," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2015, pp. 1–3.

Yun Wang (Member, IEEE) received the B.S. and M.S. degrees from the University of Electronic Science and Technology of China, Chengdu, China, in 2011 and 2014, respectively, and the Ph.D. degree in physical electronics from the Tokyo Institute of Technology, Tokyo, Japan, in 2019.

He was an Intern with the Pohang University of Science and Technology, Pohang, South Korea, in 2013, and Device Technology Laboratories, NTT Corporation, Atsugi, Japan, in 2016. He is currently a Post-Doctoral Researcher with the Tokyo Insti-

tute of Technology. His research interests include CMOS radio frequency (RF)/millimeter-wave wireless systems, 5G phased-array mobile systems, and satellite communication.

Dr. Wang was a recipient of the IEICE Best Paper Award in 2018, the Best Student Paper Award (First Place) at the 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), and the Seiichi Tejima Research Award in 2021. He also serves as a Reviewer for IEEE JOURNAL OF SOLID-STATE CIRCUITS, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I, and the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES.

Dongwon You (Student Member, IEEE) received the B.S degree in electrical and computer engineering from Ajou University, Suwon, South Korea, in 2017, and the M.S degree in electrical and electronic engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 2019, where he is currently pursuing the Ph.D. degree in the electrical and electronic engineering.

His current research interests include CMOS analog/RF/millimeter-wave transceiver systems, multiple-input multiple-output (MIMO), mixed

signals, wireless communication, satellite communication, and device modeling.

**Xi Fu** (Graduate Student Member, IEEE) received the B.E. degree (Hons.) from the Dalian University of Technology, Dalian, China, in 2017, and the M.S. degree from the Department of Physical Electronics, Tokyo Institute of Technology, Tokyo, Japan, in 2019, where he is currently pursuing the Ph.D. degree in the electrical and electronic engineering.

His research interests include CMOS radio frequency (RF)/millimeter-wave transceiver systems, 5G mobile systems, satellite communication, and phased-array transceiver.

Mr. Fu was a recipient of the Japanese Government (MEXT) Scholarship.

**Takeshi Nakamura** received the B.E. and M.S. degrees from the Department of Electrical and Electronic Engineering, Tokyo Institute of Technology, Tokyo, Japan, in 2018 and 2021, respectively.

From 2019 to 2020, he was an Intern with imec, Leuven, Belgium.

Ashbir Aviat Fadila received the B.S. degree in electrical engineering from the Institut Teknologi Bandung, Bandung, Indonesia, in 2015, and the M.S. degree from the Department of Physical Electronics, Tokyo Institute of Technology, Tokyo, Japan, in 2020, where he is currently pursuing the Ph.D. degree.

From 2015 to 2016, he was a Standard Cells Mask Layout Engineer with Marvell Technology Indonesia, Jakarta, Indonesia. From 2016 to 2017, he was a Research Assistant with Institut Teknologi

Bandung, where he researched system on chip (SoC) for IoT applications. His current research interests include analog–mixed signals, data converter, and synthesizable analog circuits.

**Teruki Someya** (Member, IEEE) received the B.S., M.S., and Ph.D. degrees in electrical and electronic engineering from The University of Tokyo, Tokyo, Japan, in 2013, 2015, and 2018, respectively.

From 2018 to 2019, he was with the Department of Electrical and Electronic Engineering, Tokyo Institute of Technology, Tokyo, as a Post-Doctoral Researcher. He is currently a Post-Doctoral Researcher with Electronic Instrumentation Laboratory, Delft University of Technology (TU Delft), Delft, The Netherlands. His research interest

includes energy-efficient ultralow-power circuits for IoT applications.

**Atsuhiro Kawaguchi** received the B.S. degree from the Tokyo Institute of Technology, Tokyo, Japan, in 2019, where he is currently pursuing the M.S. degree in electrical and electronic engineering.

Junjun Qiu (Graduate Student Member, IEEE) received the B.Sc. degree in electrical and electronic engineering from the East China University of Science and Technology, Shanghai, China, in 2016, and the M.E. degree in electrical and electronic engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 2018, where she is currently pursuing the Ph.D. degree in electrical and electronic engineering.

She was focusing on fully synthesizable digital baseband circuit design for sub-GHz wireless

transceiver systems. Her current research interests include high-performance phase-locked loop design and mixed-signal wireless communication system design for Bluetooth low energy.

Ms. Qiu was a recipient of the IEEE SSCS Student Travel Grant Award in 2020

**Jian Pang** (Member, IEEE) received the bachelor's and master's degrees from Southeast University, Nanjing, China, in 2012 and 2014, respectively, and the Ph.D. degree from the Department of Physical Electronics, Tokyo Institute of Technology, Tokyo, Japan, in 2019.

From 2019 to 2020, he was a Post-Doctoral Researcher with the Tokyo Institute of Technology. He is currently a Special Appointed Assistant Professor with the Tokyo Institute of Technology, focusing on 5G millimeter-wave systems. His current

research interests include high-data-rate area-efficient millimeter-wave transceivers, power-efficient power amplifiers for 5G mobile systems, multiple-input multiple-output (MIMO), and mixed-signal systems.

Dr. Pang was a recipient of the IEEE SSCS Student Travel Grant Award in 2016, the IEEE SSCS Predoctoral Achievement Award for 2018–2019, and the Seiichi Tejima International Student Research Award in 2020. He also serves as a Reviewer for the IEEE JOURNAL OF SOLID-STATE CIRCUITS, IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I and II, and IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS.

**Kiyoshi Yanagisawa** received the B.E. and M.E. degrees in information science from Tohoku University, Sendai, Japan, in 1998 and 2000, respectively.

From 2013 to 2019, he was with Rohde & Schwarz, Tokyo, Japan, where he was engaged in the test and measurement of wireless systems. From 2019 to 2020, he was a Researcher with the Department of Electrical and Electronic Engineering, Tokyo Institute of Technology, Tokyo. His research interests include new technology in wireless systems and devices.

Mr. Yanagisawa is also a member of the Institute of Electronics, Information and Communication Engineers (IEICE).

Bangan Liu (Member, IEEE) received the B.Eng. degree from Northwestern Polytechnical University, Xi'an, China, in 2011, the M.S. degree from the University of Science and Technology of China, Hefei, China, in 2014, and the Ph.D. degree from the Tokyo Institute of Technology, Tokyo, Japan, in 2019.

He was an Intern with Apple Japan Design Center, Tokyo, in 2019. He is currently with Qualcomm Inc., San Diego, CA, USA, where he is involved in the development of high-performance cellular commu-

nication systems. His research interests include high-performance frequency synthesizers, fully synthesizable analog/RF circuits, high-performance wireless transceivers, and digital intensive/digitally assisted mixed-signal systems.

Yuncheng Zhang (Graduate Student Member, IEEE) received the B.S. and M.E. degrees in electrical engineering from the University of Science and Technology of China (USTC), Hefei, China, in 2013 and 2016, respectively. He is currently pursuing the Ph.D. degree with the Tokyo Institute of Technology, Tokyo, Japan.

His research interests include power-efficient wireless transceivers, all-digital phase-locked loops, and analog-to-digital converters.

Haosheng Zhang (Member, IEEE) was born in Jinhua, Zhejiang, China. He received the B.E. degree from Fudan University, Shanghai, China, in 2014, and the M.S. and Ph.D. degrees from the Tokyo Institute of Technology, Tokyo, Japan, in 2016 and 2019, respectively.

He is currently a Mixed-Signal Designer with SiTime Corporation, Tokyo, developing high-performance clocking circuits and architectures for micro-electromechanical systems (MEMS)-based timing reference. His research interests

include low-noise power-efficient CMOS oscillator architecture, low-power high-resolution phase-locked loop (PLL), and physics-and-IC interface, such as an atomic clock.

Dr. Zhang was a fellow of the Japanese-Government Scholarship (MEXT). He was a recipient or a co-recipient of the IEEE SSCS Japan Chapter Academic Research Award, the Best Student Paper of Radio Frequency Integrated Circuits Symposium (RFIC 2019), and the IEEE SSCS Predoctoral Achievement Award.

**Rui Wu** (Member, IEEE) received the B.S. and M.S. degrees from the University of Electronic Science and Technology of China, Chengdu, China, in 2006 and 2009, respectively, and the Ph.D. degree from the Tokyo Institute of Technology, Tokyo, Japan, in 2015.

From 2015 to 2018, he was a Post-Doctoral Researcher with the Tokyo Institute of Technology. Since 2018, he has been a Full Professor with the National Key Laboratory of Microwave Imaging Technology, Aerospace Information Research Insti-

tute, Chinese Academy of Sciences, Beijing, China. His current research interests include RF/millimeter-wave transceivers for radar and high data rate wireless communications.

Shunichiro Masaki was born in Hokkaido, Japan, in 1975. He received the B.S. and M.S. degrees in information science from Tohoku University, Sendai, Japan, in 1998 and 2000.

From 2000 to 2015, he was with Fujitsu Laboratories Ltd., Kanagawa, Japan, where he was engaged in the research and development of high-speed IOs (HSIOs). He is currently with Socionext Inc., Yokohama, Japan, where he is researching the technology of embedding HSIOs and RFs in the system on chip (SoC).

**Daisuke Yamazaki** received the master's degree from the Tokyo Institute of Technology, Tokyo, Japan, in 1994.

From 1994 to 2015, he was with Fujitsu Laboratories, Kawasaki, Japan, where he had researched and developed high-speed IOs (HSIOs) and radiofrequency integrated circuits (RFICs). He is currently with Socionext Inc., Yokohama, Japan, where he is researching and developing the technology of embedding HSIOs and RFs in the system on chip (SoC).

Mr. Yamazaki was a Speaker at the Design Solution Forum in 2018, presenting the system verification using the RF behavior model of SystemVerilog.

**Atsushi Shirane** (Member, IEEE) received the B.E. degree in electrical and electronic engineering and the M.E. and Ph.D. degrees in electronics and applied physics from the Tokyo Institute of Technology, Tokyo, Japan, in 2010, 2012, and 2015, respectively.

From 2015 to 2017, he was with Toshiba Corporation, Kawasaki, Japan, where he developed an 802.11ax wireless LAN RF transceiver. From 2017 to 2018, he was with Nidec Corporation, Kawasaki, Japan, where he researched intelligent

motors with wireless communication. He is currently an Assistant Professor with the Department of Electrical and Electronic Engineering, Tokyo Institute of Technology. His current research interests include RF CMOS transceiver for IoT, 5G, and satellite communication.

Dr. Shirane is also a member of the IEEE Solid-State Circuits Society and the Institute of Electronics, Information and Communication Engineers (IEICE).

**Kenichi Okada** (Senior Member, IEEE) received the B.E., M.E., and Ph.D. degrees in communications and computer engineering from Kyoto University, Kyoto, Japan, in 1998, 2000, and 2003, respectively.

From 2000 to 2003, he was a Research Fellow of the Japan Society for the Promotion of Science at Kyoto University. In 2003, he joined the Tokyo Institute of Technology, Tokyo, Japan, as an Assistant Professor. He is currently a Professor of electrical and electronic engineering with the Tokyo Institute

of Technology. He has authored or coauthored more than 400 journal articles and conference papers. His current research interests include millimeter-wave CMOS wireless transceivers for 20/28/39/60/77/79/100/300 GHz for 5G, WiGig, satellite and future wireless systems, digital phase-locked loop (PLL), synthesizable PLL, atomic clock, ultralow-power wireless transceivers for Bluetooth low energy, and sub-GHz applications.

Prof. Okada is/was a member of the Technical Program Committees of the IEEE International Solid-State Circuits Conference (ISSCC), the VLSI Circuits Symposium, European Solid-State Circuits Conference (ESSCIRC), and the Radio Frequency Integrated Circuits Symposium (RFIC). He is also a member of the Institute of Electrical and Electronics Engineers (IEEE), the Institute of Electronics, Information and Communication Engineers (IEICE), the Information Processing Society of Japan (IPSJ), and the Japan Society of Applied Physics (JSAP). He was a recipient or a co-recipient of the Ericsson Young Scientist Award in 2004, the A-SSCC Outstanding Design Awards in 2006 and 2011, the ASP-DAC Special Feature Award in 2011, the Best Design Awards in 2014 and 2015, the MEXT Young Scientists' Prize in 2011, the JSPS Prize in 2014, the Suematsu Yasuharu Award in 2015, the MEXT Prizes for Science and Technology in 2017, the RFIT Best Paper Award in 2017, the IEICE Best Paper Award in 2018, the RFIC Symposium Best Student Paper Award in 2019, the IEICE Achievement Award in 2019, the DOCOMO Mobile Science Award in 2019, the IEEE/ACM ASP-DAC, the Prolific Author Award in 2020, the Kenjiro Takayanagi Achievement Award in 2020, the KDDI Foundation Award in 2020, the IEEE Custom Integrated Circuits Conference (CICC), the Best Paper Award in 2020, and more than 50 other international and domestic awards. He is/was also Guest Editor and an Associate Editor of IEEE JOURNAL OF SOLID-STATE CIR-CUITS (JSSC), an Associate Editor of IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES (T-MTT), and a Distinguished Lecturer of the IEEE Solid-State Circuits Society (SSCS).