# A Quadrature Digital Power Amplifier With Hybrid Doherty and Impedance Boosting for Complex Domain Power Back-Off Efficiency Enhancement

Huizhen Jenny Qian<sup>®</sup>, Member, IEEE, Bingzheng Yang<sup>®</sup>, Graduate Student Member, IEEE, Jie Zhou<sup>®</sup>, Student Member, IEEE, Hongtao Xu<sup>®</sup>, Senior Member, IEEE, and Xun Luo<sup>®</sup>, Senior Member, IEEE

Abstract-A quadrature digital power amplifier (PA) with hybrid Doherty and impedance boosting (HDIB) technique is presented for deep power back-off (PBO) efficiency enhancement in the complex domain. Less power-combining ways and dc power supplies are required for proposed PA comparing to previously reported works with deep PBO efficiency enhancement. A reconfigurable matching network (RMN) based on a novel reconfigurable transformer is proposed with more freedom to achieve a flexible load impedance tuning range of the sub-PAs. The characteristics of the reconfigurable transformer based on tunable inductors are analyzed. Efficiency enhancement is achieved at 3-/6-/9-/12-/15-dB PBOs without any supply switching or PA short-switches. The PA is fabricated in 40-nm CMOS technology with a core size of 0.83 mm<sup>2</sup>. Operating at 2.3–3.4 GHz, it introduces 24.2-dBm peak  $P_{\text{out}}$ with 38.5% peak drain efficiency (DE) at 2.8 GHz. It achieves 38.5%/29.6%/18.4% at 2.8 GHz and 34.7%/26.6%/17.8% DE at 3.3 GHz for 0-/6-/12-dB PBO, 39.3%/29.5%/14.9% at 2.8 GHz, and 35.3%/27.9%/15.9% DE at 3.3 GHz for 3-/9-/15-dB PBO, respectively. For 10-MHz 256-QAM modulation signal, it delivers 16.22-/15.50-dBm average  $P_{\text{out}}$  with EVM of -32.3/-33.0 dB, average DE of 24.6%/22.7%, and ACLR of -33.20/-31.54 dBc at 2.8/3.3 GHz, respectively. For 20-MHz 64 QAM modulation signal, it exhibits 16.42-/15.52-dBm average  $P_{\text{out}}$  with EVM of -29.1/-29.3 dB, average DE of 24.9%/22.78%, and ACLR of -30.78/-30.74 dBc at 2.8/3.3 GHz, respectively.

*Index Terms*—Doherty, impedance boosting, power back-off (PBO), quadrature digital power amplifier (PA), reconfigurable transformer.

Manuscript received October 5, 2020; revised December 13, 2020 and February 1, 2021; accepted February 9, 2021. Date of publication February 24, 2021; date of current version April 23, 2021. This article was approved by Associate Editor Mohyee Mikhemar. This work was supported in part by the National Natural Science Foundation of China under Grant 61904025 and Grant 61934001. (Corresponding author: Xun Luo.)

Huizhen Jenny Qian, Bingzheng Yang, Jie Zhou, and Xun Luo are with the State Key Laboratory of Electronic Thin Films and Integrated Devices, University of Electronic Science and Technology of China, Chengdu 611731, China (e-mail: xun-luo@ieee.org).

Hongtao Xu is with the State Key Laboratory of ASIC and System, Fudan University, Shanghai 201203, China.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSSC.2021.3059113.

Digital Object Identifier 10.1109/JSSC.2021.3059113

#### I. INTRODUCTION

THE increasing data throughput of wireless communication systems favors spectral-efficiency modulation signals with high peak-to-average-power ratios (PAPRs). Therefore, the efficiency at the power back-off (PBO) region of the power amplifiers (PAs) or transmitters (TXs) is critical to decrease the power consumption of the RF front end. To cover multiple communication standards (e.g., LTE, 5G, Bluetooth, and Wi-Fi) with low cost and compact size, wideband PAs with high average efficiency are demanded.

Many techniques are developed to enhance the PA efficiency at PBO levels, such as envelope-tracking [1]-[4], Doherty [5]–[12], Class-G [13]–[15], and load modulation [16]–[21]. The supply modulator in envelope-tracking PA changes the supply voltage, which tracks the envelope of modulation signal to improve PBO efficiency. However, large bandwidth and dynamic ranges of the supply modulator become the performance bottleneck. Doherty PA achieves efficiency peak at PBO by cooperated main/auxiliary PAs and active load modulation. Class-G PA provides additional efficiency peaks at PBOs with switched supply voltages, although the efficiency discontinuity caused by supply switching degrades the efficiency enhancement compared to Doherty PA. Load modulation usually employs a large switch at the sub-PA's output to modulate the load impedance. However, the switch can cause bandwidth limitation, reliability issue, and degraded signal integrity from the dc current discontinuities.

To further improve the PA efficiency at deep PBO levels, several techniques are introduced. Multi-ways Doherty [22]–[25] achieves multiple efficiency peaks at PBOs with a relatively larger size. Power-controlled outphasing architecture [26]–[28] adopts two efficient PAs amplifying modulation signals with a constant envelope decomposed from the input signal. However, the efficiency enhancement at deep PBOs is degraded due to the increasing loss of power combiner and constant power consumption of driver circuits. Moreover, Class-G Doherty PA [29], [30] achieves efficiency peaks at 6- and 12-dB PBOs with extra hardware

overhead. Switched transformer PA [21] generates multiple efficiency peaks, while it requires extra hardware overhead including short switches in PA unit cells and multi-way power combining structure. Subharmonic switching (SHS) technique [31], [32] in combination with Class-G requires multiple power combined ways to achieve efficiency improvement. Moreover, the Class-G operation in these works needs supply switching to further improve the efficiency at PBO.

Meanwhile, digital polar architecture is often used in available techniques with PBO enhancement due to its flexibility with digital controlled output power and high energy efficiency. It adopts a complex coordinate rotation digital computer (CORDIC) for Cartesian-to-polar conversion and phase modulator (PM) compared to the quadrature digital PA. The spectrum expansion of Cartesian-to-polar conversion increases the necessary bandwidth of PM. The delay synchronization between the amplitude and phase paths should also be minimized to decrease the signal distortion. In contrast, digital quadrature PA [33]–[39] exhibits a simple structure without PM, CORDIC, and delay synchronization issues, which has a potential advantage for high data-rate transmission. However, it is still challenging for the efficiency enhancement at deep PBOs in the complex domain for existing techniques.

In this article, we propose a quadrature digital PA [40] with a hybrid Doherty and impedance boosting (HDIB) technique for deep PBO efficiency enhancement in the complex domain. It achieves efficiency peaks at 3-/6-/9-/12-/15-dB PBO over 2.3–3.4 GHz without supply switching or switches to short the sub-PA output. A reconfigurable matching network (RMN) with a reconfigurable transformer is introduced to realize the impedance boosting. This article is organized as follows. In Section II, the theoretical analysis of the quadrature digital PA with HDIB is discussed. The detailed circuit implementation is described in Section III. Section IV presents the measurement results and comparison with state-of-the-art works, and Section V concludes this article.

#### II. THEORY OF OPERATION

# A. Review of Multi-Way Doherty and Class-G Doherty PA

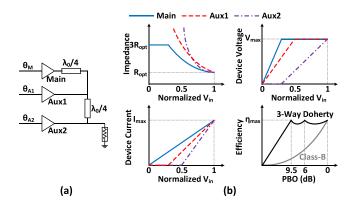

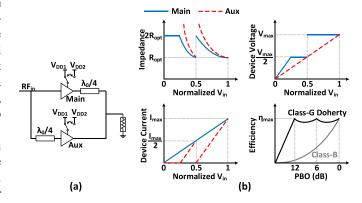

The Doherty PA exhibits efficiency enhancement at PBO and high average efficiency, which is demanded in modern wireless transmitter systems. To further improve the PBO efficiency, the multi-ways Doherty [22]-[25] and Class-G Doherty PAs [29], [30] are introduced with multiple efficiency peaks at PBO. Fig. 1 illustrates the schematic, load impedance, and voltage/current trajectories of a typical three-way Doherty PA. Two efficiency peaks are generated, which leads to the improved average efficiency of PA. It, nevertheless, employs complex power combining circuits, which is inefficient at deep PBO and challenging to achieve wideband operation. Moreover, as shown in Fig. 2, the typical Class-G Doherty PA [29], [30] achieves efficiency peaks at 6- and 12-dB PBOs. However, the supply switching in Class-G PAs introduces extra hardware overhead, possible linearity degradation from the supply discontinuity, and bandwidth challenges from the supply modulation effect.

Fig. 1. (a) Schematic and (b) load impedances, voltage/current trajectories for the main/auxiliary PAs, and efficiency of a three-way Doherty PA.

Fig. 2. (a) Schematic and (b) load impedances, voltage/current trajectories for the main/auxiliary PAs, and efficiency of a Class-G Doherty PA.

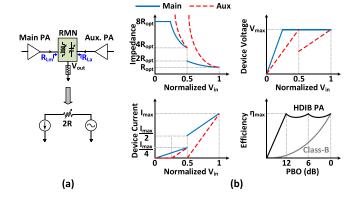

Fig. 3. (a) Schematic and (b) load impedances, voltage/current trajectories for the main/auxiliary PAs, and efficiency of the HDIB PA.

# B. Operation of HDIB PA

The simplified schematic of the HDIB PA is shown in Fig. 3(a). Conventional Doherty PA adopts active load modulation by cooperated main and auxiliary PAs with the fixed passive matching network [5]. In contrast, the proposed HDIB PA utilizes RMN for power combining of its main and auxiliary PAs to enhance the deep PBO efficiency. By changing the mode of RMN, the passive input impedance of the RMN is boosted from  $R_{\rm opt}$  (PBO from 0 to 6 dB) to  $4R_{\rm opt}$  (PBO  $\geq$  6 dB). This impedance boosting of RMN

|             |            | PBO (dB) | Main PA              |                      |                     |                   | Auxiliary PA         |                      |                      |                   |                                         |

|-------------|------------|----------|----------------------|----------------------|---------------------|-------------------|----------------------|----------------------|----------------------|-------------------|-----------------------------------------|

| RMN<br>Mode | State      |          | RF<br>Current<br>(I) | RF<br>Current<br>(Q) | Main RF<br>Current  | Load<br>Impedance | RF<br>Current<br>(I) | RF<br>Current<br>(Q) | Aux. RF<br>Current   | Load<br>Impedance | $P_{out}$                               |

| I           | (a)        | 0        | $I_{max}$            | $I_{max}$            | $\sqrt{2}I_{max}$   | $R_{opt}$         | $I_{max}$            | $I_{max}$            | $\sqrt{2}I_{max}$    | $R_{opt}$         | $4I_{\mathrm{max}}^2R_{\mathrm{opt}}$   |

| I           | <b>(b)</b> | 6        | $I_{max}/2$          | $I_{max}/2$          | $\sqrt{2}I_{max}/2$ | $2R_{opt}$        | 0                    | 0                    | 0                    | _                 | $I_{ m max}^2 R_{ m opt}$               |

| II          | ©          | 6        | $I_{max}/4$          | $I_{max}/4$          | $\sqrt{2}I_{max}/4$ | $4R_{opt}$        | $I_{max}$ /4         | $I_{max}$ /4         | $\sqrt{2}I_{max}$ /4 | $4R_{opt}$        | $I_{\mathrm{max}}^2 R_{\mathrm{opt}}$   |

| II          | <b>(d)</b> | 12       | $I_{max}/8$          | $I_{max}/8$          | $\sqrt{2}I_{max}/8$ | $8R_{opt}$        | 0                    | 0                    | 0                    | _                 | $I_{\mathrm{max}}^2 R_{\mathrm{opt}}/4$ |

| I           | e          | 3        | $I_{max}$            | 0                    | $I_{max}$           | $R_{opt}$         | $I_{max}$            | 0                    | $I_{max}$            | $R_{opt}$         | $2I_{\mathrm{max}}^2R_{\mathrm{opt}}$   |

| I           | <b>(f)</b> | 9        | $I_{max}/2$          | 0                    | $I_{max}/2$         | $2R_{opt}$        | 0                    | 0                    | 0                    | _                 | $I_{ m max}^2 R_{ m opt}/2$             |

| II          | g          | 9        | $I_{max}/4$          | 0                    | $I_{max}$ /4        | $4R_{opt}$        | $I_{max}$ /4         | 0                    | $I_{max}$ /4         | $4R_{opt}$        | $I_{\mathrm{max}}^2 R_{\mathrm{opt}}/2$ |

| II          | h          | 15       | $I_{max}/8$          | 0                    | $I_{max}/8$         | $8R_{opt}$        | 0                    | 0                    | 0                    |                   | $I_{\rm max}^2 R_{\rm opt}/8$           |

TABLE I

DETAILED OPERATION STATES IN DIFFERENT MODES OF PROPOSED PA

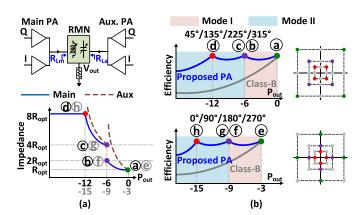

Fig. 4. (a) Simplified architecture and load impedance and (b) efficiency curves and constellation with corresponding operation states in complex domain of proposed quadrature digital quadrature PA with HDIB.

combined with the active load modulation of the Doherty operation produces the theoretical load impedance trajectories in Fig. 3(b). By manipulating the device's current of HDIB PA, the output voltage of the main PA is maintained constant at PBO ≤ 12 dB, which is similar behavior as the three-way Doherty PA in Fig. 1(b). Comparing to Class-G Doherty PA in Fig. 2(b) with discontinued output voltage, the HDIB PA has potentially better linearity. Meanwhile, only two-way power combining is required for HDIB PA, which is more compact comparing to the three-way Doherty PA. This method can be applied and extended to conventional analog PAs and digital PAs.

#### C. Operation of Quadrature Digital PA With HDIB

A digital quadrature PA with the aforementioned HDIB technique is proposed, as shown in Fig. 4(a). Both the main and auxiliary PAs are comprised of quadrature sub-PAs (I and Q sub-PAs) with the digitally controlled current. All the sub-PAs are assumed to be identical and combined by the RMN for quadrature vectors summation and active load modulation. There are two modes for the RMN. In mode I, the passive input impedance of RMN is low-state ( $R_{\rm opt}$ ). In mode II, the passive input impedance of RMN is high-state ( $R_{\rm opt}$ ). The load impedance of the main PA is doubled as the auxiliary PA turned off gradually. Both modes I and II

show the Doherty operation, as shown in Fig. 4(a). The load impedance of the main PA in modes I and II is varying from  $R_{\rm opt}$  to  $2R_{\rm opt}$  and  $4R_{\rm opt}$  to  $8R_{\rm opt}$ , respectively. At least six efficiency peaks are generated in the complex domain of the output vectors, as illustrated in Fig. 4(b). For example, efficiency peaks are produced at operation states ⓐ, ⓑ, ⓒ, and ⓓ for PA output vectors with phase-I  $(45^{\circ}/135^{\circ}/225^{\circ}/315^{\circ})$ ; efficiency peaks are produced at operation states ⓔ, ᠿ, ②, and 愉 for PA output vectors with phase-II  $(0^{\circ}/90^{\circ}/180^{\circ}/270^{\circ})$ . From 0- to 6-dB PBO with phase-I and 3- to 9-dB PBO with phase-II, the RMN is in mode I. For PBO > 6 dB with phase-I and PBO > 9 dB with phase-II, the RMN is in mode II.

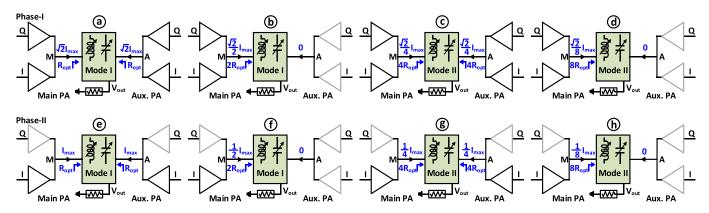

The detailed operation states ((a)–(h)) of the proposed digital quadrature PA with HDIB are depicted in Fig. 5 and Table I. At state (a) with maximum output power, both main and auxiliary PAs are fully on with output current of  $\sqrt{2}I_{\text{max}}$ . The RMN is at mode I providing both PAs' load impedance of  $R_{\text{opt}}$ . From 0- to 6-dB PBO in phase-I, the auxiliary PA is turned off gradually, while the current of the main PA is decreased to  $\sqrt{2}I_{\text{max}}/2$ . At state (b), the load impedance seen by the main PA is increased to  $2R_{\text{opt}}$  due to the load modulation of the Doherty operation. Therefore, the efficiency peak at 6-dB PBO is restored. At state ©, main and auxiliary PAs are equally on with quarter of their maximum current ( $\sqrt{2}I_{\text{max}}/4$ ). The load impedance is boosted to  $4R_{\rm opt}$  when the RMN is at mode II. The output power and output voltage at state © is the same as state (b). Hence, the efficiency is maintained 100% in an ideal case. Below 6-dB PBO in phase-I, the RMN is at mode II. From 6- to 12-dB PBO, the Doherty operation is performed again to restore the efficiency peak at 12-dB PBO (state @)), while the load impedance of main PA increases from  $4R_{\text{opt}}$ to  $8R_{\text{opt}}$ . For the operation states with phase-II (@, .f.), @, and (h)), the mechanism is similar as phase-I with dual-mode RMN. Note that, the in-phase or quad-phase sub-PAs of main and auxiliary PAs are fully off with 3 dB lower output power comparing to phase-I. Three efficiency peaks are achieved at 3-, 9-, and 15-dB PBOs at phase-II. Table II compares the existing and proposed techniques for PBO efficiency enhancement. Most of the existing techniques adopt multiple power-combined ways, which leads to relatively large circuit size. Class-G digital polar has no power combining with compact circuit size. However, it requires multiple power supplies, extra PM, and CORDIC. The proposed digital quadrature PA

Fig. 5. Typical operation states of the digital quadrature PA with HDIB.

TABLE II

COMPARISON OF EXISTING AND PROPOSED TECHNIQUES

FOR PBO EFFICIENCY ENHANCEMENT

|                                              | Power-<br>Combined<br>Ways | Power-<br>Combined<br>Techniques | η<br>Peaks | Supply<br>Number | Size  | Require<br>PM/<br>CORDIC |

|----------------------------------------------|----------------------------|----------------------------------|------------|------------------|-------|--------------------------|

| Class-G+<br>Digital Polar [15]               | 1                          | N/A                              | 2          | 2                | Good  | Yes                      |

| Multi-way<br>Doherty +<br>Digital Polar [25] | 3                          | 3 XFMRs<br>in Series             | 3          | 1                | Large | Yes                      |

| Class-G+<br>Doherty+<br>Digital Polar [29]   | 2                          | 2 XFMRs<br>in Parallel           | 3          | 2                | Large | Yes                      |

| Switched-<br>XFMR+<br>Digital Polar [21]     | 4                          | 1 XFMR<br>in Parallel            | 4          | 1                | Large | Yes                      |

| Class-G<br>Doherty<br>Quadrature [38]        | 2                          | 2 XFMRs<br>in Series             | 4          | 2                | Good  | No                       |

| Class-G+<br>SHS+<br>Digital Polar [31]       | 3                          | 3 XFMRs<br>in Series             | 5          | 3                | Large | Yes                      |

| Power Controlled Outphasing [26]             | 8                          | 8 XFMRs<br>in Series             | 5          | 1                | Large | Yes                      |

| Proposed<br>HDIB+Digital<br>Quadrature       | 2                          | 1 XFMR<br>Series                 | 6          | 1                | Good  | No                       |

with HDIB adopts only two power-combined ways to generate six efficiency peaks. The data rate is potentially larger without PM and CORDIC for the proposed architecture. Therefore, the proposed technique exhibits merits in deep PBO efficiency, circuit size, and data rate.

## III. CIRCUIT IMPLEMENTATION

### A. System Architecture

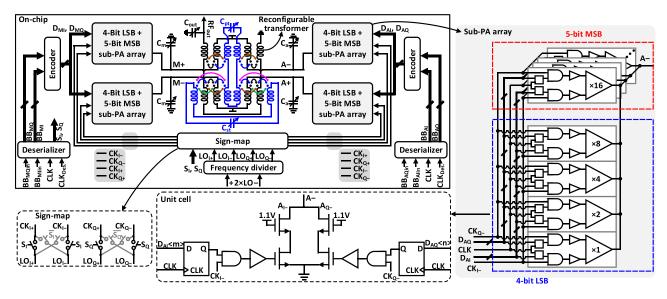

The simplified block diagram of the digital quadrature PA with HDIB is shown in Fig. 6. The main and auxiliary PAs are formed by the same sub-PA arrays, including differential in-phase/quad-phase sub-PAs. The sub-PA operates as the type of Class-E. The digital PA is controlled by  $4 \times 9$ -bit baseband I/Q code. To decrease the circuit complexity, each sub-PA is segmented into 5-bit unary-weighted MSB cells and

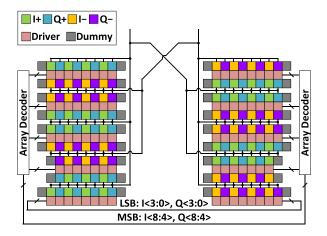

4-bit binary-weighted LSB cells. The PA unit cell is formed by switching cascade circuit in coordination with the signal from multiplied baseband data and LO. The transistors sizes for the MSB and LSB unit cells of the sub-PA array are  $50 \mu \text{m}/40 \text{ nm}, 25 \mu \text{m}/40 \text{ nm}, 12.5 \mu \text{m}/40 \text{ nm}, 6.25 \mu \text{m}/40 \text{ nm},$ and 3.125  $\mu$ m/40 nm, respectively. Fig. 7 shows the detailed floorplan of the proposed digital PA sub-array, including the unit cells, interconnection, dummy cells, and drivers. The baseband signal is re-sampled by the D flip-flop for better synchronization of parallel data. The RMN is composed of a reconfigurable transformer and switched capacitors. It combines the power from two-way differential sub-PA arrays and achieves the necessary impedance conversion from the 50- $\Omega$  output load. The impedance boosting is also realized by changing the mode of RMN to achieve HDIB operation. A frequency divider generates quadrature LOs with a 50% duty cycle from the differential 2 × LO RF inputs. The sign map can be used to determine the quadrant of the output signal [39], [41], [42]. In this work, the signs of the quadrature LOs can be switched by the sign-map circuit according to two sign bits (i.e.,  $S_I$  and  $S_O$ ). In each sub-PA, the two on-chip 1:10 deserializers are used to convert the serial I/Q BB signals to parallel I/Q BB signals, respectively. Each deserializer has one input port for input serial BB signal, two input ports for clocks, and ten output ports for parallel BB signals (including 9-bit I/Q BB codes for DPA control and 1-bit sign bit for sign-map control). The single supply of 1.1 V is adopted for the PA.

#### B. RMN With Reconfigurable Transformer

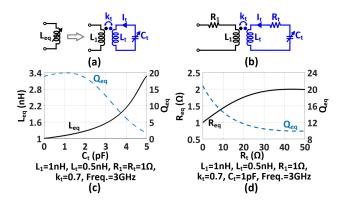

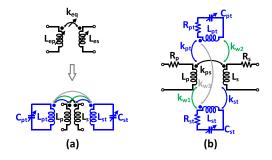

1) Tunable Inductor: To achieve at least four times impedance tuning range for the HDIB operation, the implementation of RMN is pivotal. We propose a reconfigurable transformer based on a tunable inductor. The simplified circuit model of the tunable inductor is exhibited in Fig. 8(a). The tunable inductor is composed of a main inductor  $L_1$ , an auxiliary inductor  $L_t$ , and a tunable capacitor  $C_t$ .  $L_1$  and  $L_t$  are magnetic coupled with the coupling factor of  $k_t$ .  $L_t$  is connected directly with the tunable capacitor  $C_t$ . The magnetic flux of the main inductor is manipulated by the induced current  $I_t$  through  $L_t$ , while  $I_t$  is related to  $L_t$ ,  $C_t$ , and  $k_t$ .

Fig. 6. Simplified block diagram of the proposed HDIB digital quadrature PA.

Fig. 7. Floorplan of the PA-sub array.

The equivalent inductance  $L_{\rm ep}$  is derived as

$$L_{\rm ep} = L_1 + \frac{\omega^2 L_t C_t}{1 - \omega^2 L_t C_t} k_t^2 L_1. \tag{1}$$

To analyze the quality factor of practical tunable inductor, the circuit model with parasitic resistance is used, as shown in Fig. 8(b).  $R_1$  is the parasitic resistance of  $L_1$ , and  $R_t$  is the total parasitic resistance of  $C_t$  and  $L_t$ . The equivalent inductance  $L_{\rm ep}$ , resistance  $R_{\rm ep}$ , and quality factor  $Q_{\rm ep}$  of the tunable inductor are derived as follows:

$$L_{\text{eq}} = L_1 + \frac{L_1 L_t C_t k_t^2 \omega^2 (1 - C_t L_t \omega^2)}{(C_t L_t \omega^2 - 1)^2 + R_t^2 C_t^2 \omega^2}$$

(2)

$$R_{\rm eq} = R_1 + \frac{C_t^2 L_t L_1 R_t k_t^2 \omega^4}{\left(C_t L_t \omega^2 - 1\right)^2 + R_t^2 C_t^2 \omega^2}.$$

(3)

Fig. 8. (a) Simplified circuit model of the tunable inductor. (b) Circuit model with parasitic resistance. (c) Equivalent inductance and quality factor versus  $C_t$ . (d) Equivalent resistance and quality factor versus  $R_t$ .

Fig. 8(c) shows calculated  $L_{\rm ep}$  and  $Q_{\rm ep}$  versus  $C_t$  under given components value as an example.  $L_{\rm ep}$  has large tuning range with various  $C_t$ . Meanwhile,  $Q_{\rm ep}$  is affected by  $C_t$  significantly, as exhibited in Fig. 8(c). Hence,  $C_t$  should be chosen considering both  $L_{\rm ep}$  and  $Q_{\rm ep}$ . Fig. 8(d) gives the calculated  $R_{\rm ep}$  and  $Q_{\rm ep}$  versus  $R_t$ . With  $R_t$  from 0 to 50  $\Omega$ ,  $R_{\rm ep}$  increases from 1 to 2  $\Omega$ , which is dominated by  $R_1$  (1  $\Omega$ ) and has low relativity to  $R_t$ . Thus, the switched capacitor can be easily implemented without significant degradation of  $Q_{\rm ep}$ .

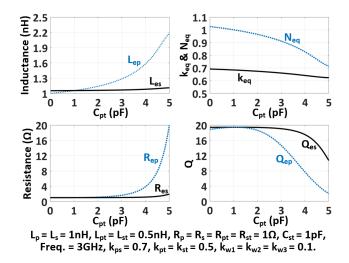

2) Reconfigurable Transformer: The reconfigurable transformer is formed by two tunable inductors, i.e., the primary inductor  $L_{\rm ep}$  and secondary inductor  $L_{\rm es}$  with the equivalent coupling factor  $k_{\rm ep}$ , as shown in Fig. 9(a).  $L_{\rm ep}$  is dominated by  $L_p$ ,  $L_{\rm pt}$ ,  $C_{\rm pt}$ , and coupling factor  $k_{\rm pt}$  between  $L_p$  and  $L_{\rm pt}$ .  $L_{\rm es}$  is dominated by  $L_s$ ,  $L_{\rm st}$ ,  $C_{\rm st}$ , and coupling factor  $k_{\rm st}$  between  $L_s$

$$Q_{\text{eq}} = \frac{\left(1 - C_t^2 L_t^2 (k_t^2 - 1)\omega^4 + C_t (R_t^2 C_t + L_t (k_t^2 - 2))\omega^2\right) \omega L_1}{C_t^2 L_t (L_1 R_t k_t^2 + R_1 L_t)\omega^4 + C_t R_1 (R_t^2 C_t - 2L_t)\omega^2 + R_1}$$

(4)

Fig. 9. (a) Simplified circuit model of the reconfigurable transformer. (b) Circuit model of the reconfigurable transformer with parasitic resistance.

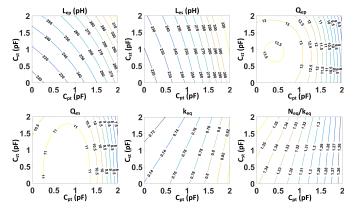

Fig. 10. Calculated transformer parameters versus  $C_{\rm pt}$ .

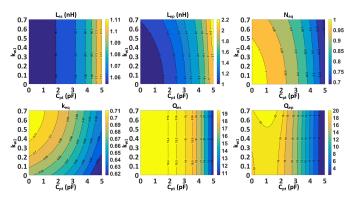

Fig. 11. Calculated  $L_{\rm es}$ ,  $L_{\rm ep}$ ,  $N_{\rm ep}$ ,  $k_{\rm ep}$ ,  $Q_{\rm es}$ , and  $Q_{\rm ep}$  versus  $C_{\rm pt}$  and  $k_{w2}$  ( $L_p=L_s=1$  nH,  $L_{\rm pt}=L_{\rm st}=0.5$  nH,  $R_p=R_s=R_{\rm pt}=R_{\rm st}=1$   $\Omega$ ,  $C_{\rm st}=1$  pF, Frequency = 3 GHz,  $k_{\rm ps}=0.7$ ,  $k_{\rm pt}=k_{\rm st}=0.5$ , and  $k_{w1}=k_{w3}=0.1$ ).

and  $L_{\rm st}$ . The detailed circuit model considering the parasitic resistance is shown in Fig. 9(b). Weak coupling also exists for  $L_p$  and  $L_{\rm st}$  with coupling factor  $k_{w1}$ ,  $L_s$ , and  $L_{\rm pt}$  with coupling factor  $k_{w2}$ ,  $L_{\rm st}$ , and  $L_{\rm pt}$  with coupling factor  $k_{w3}$ . Hence, the equivalent inductance  $L_{\rm ep}$  and  $L_{\rm es}$  and the coupling factor  $k_{\rm ep}$  are also affected by the unwanted EM coupling. The equivalent inductance  $L_{\rm ep}$  and  $L_{\rm es}$ , equivalent quality factor  $Q_{\rm ep}$  and  $Q_{\rm es}$ , and equivalent resistance  $R_{\rm ep}$  and  $R_{\rm es}$  are calculated, as shown in the Appendix. The calculated  $L_{\rm ep}$ ,  $L_{\rm es}$ ,  $k_{\rm ep}$ ,  $N_{\rm ep}$ ,  $R_{\rm ep}$ ,  $R_{\rm es}$ ,  $Q_{\rm ep}$ , and  $Q_{\rm es}$  versus  $C_{\rm pt}$  are shown

Fig. 12. Calculated  $L_{\rm es}$ ,  $L_{\rm ep}$ ,  $N_{\rm ep}$ ,  $k_{\rm ep}$ ,  $Q_{\rm es}$ , and  $Q_{\rm ep}$  versus  $C_{\rm pt}$  and  $k_{w3}$  ( $L_p = L_s = 1 \, {\rm nH}$ ,  $L_{\rm pt} = L_{\rm st} = 0.5 \, {\rm nH}$ ,  $R_p = R_s = R_{\rm pt} = R_{\rm st} = 1 \, \Omega$ ,  $C_{\rm st} = 1 \, {\rm pF}$ , Frequency = 3 GHz,  $k_{\rm ps} = 0.7$ ,  $k_{\rm pt} = k_{\rm st} = 0.5$ , and  $k_{w1} = k_{w2} = 0.1$ ).

Fig. 13. Calculated  $L_{\rm es}$ ,  $L_{\rm ep}$ ,  $N_{\rm ep}$ ,  $k_{\rm ep}$ ,  $Q_{\rm es}$ , and  $Q_{\rm ep}$  versus  $C_{\rm pt}$  and  $k_{w1}$  ( $L_p = L_s = 1 \, {\rm nH}$ ,  $L_{\rm pt} = L_{\rm st} = 0.5 \, {\rm nH}$ ,  $R_p = R_s = R_{\rm pt} = R_{\rm st} = 1 \, \Omega$ ,  $C_{\rm st} = 1 \, {\rm pF}$ , Frequency = 3 GHz,  $k_{\rm ps} = 0.7$ ,  $k_{\rm pt} = k_{\rm st} = 0.5$ , and  $k_{w2} = k_{w3} = 0.1$ ).

in Fig. 10.  $L_{\rm ep}$  is increased from 1 to 2.2 nH with larger  $C_{\rm pt}$ , while  $L_{\rm es}$  is changed slightly with larger  $C_{\rm pt}$ .  $N_{\rm ep}$  is tuned by  $C_{\rm pt}$  from 1.03 to 0.7, and  $k_{\rm ep}$  is decreased from 0.69 to 0.62.  $R_{\rm ep}$  is increased significantly with larger  $C_{\rm pt}$ , which leads to lower  $Q_{\rm ep}$ . The impact of  $C_{\rm pt}$  on  $R_{\rm es}$  and  $Q_{\rm es}$  is much smaller comparing to  $R_{\rm ep}$  and  $Q_{\rm ep}$  since  $k_{w2}$  (i.e., 0.1) is set to be much lower than  $k_{\rm ps}$  (i.e., 0.7) in Fig. 10.

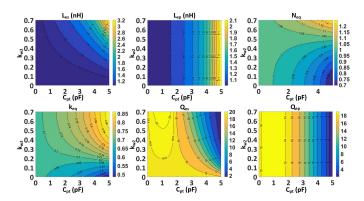

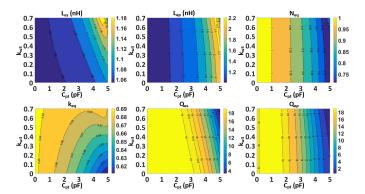

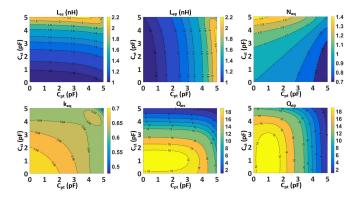

To evaluate the impact of  $k_{w2}$ , the calculated  $L_{es}$ ,  $L_{ep}$ ,  $N_{ep}$ ,  $k_{\rm ep}$ ,  $Q_{\rm es}$ , and  $Q_{\rm ep}$  versus  $C_{\rm pt}$  and  $k_{w2}$  are plotted in Fig. 11.  $L_{\rm es}$ varies from 1.05 to 3.4 nH as  $k_{w2}$  increasing from 0.1 to 0.7, while  $L_{ep}$  and  $Q_{ep}$  are the same with different  $k_{w2}$ .  $Q_{es}$  is deteriorated as  $k_{w2}$  increasing and  $C_{pt} > 2$  pF.  $N_{ep}$  and  $k_{ep}$  are also increased with larger  $k_{w2}$ . The impact of  $k_{w3}$  is weaker compared to  $k_{w2}$ , as exhibited in Fig. 12. The variation of  $L_{\text{es}}$ ,  $L_{\text{ep}}$ ,  $N_{\text{ep}}$ ,  $k_{\text{ep}}$ , and  $Q_{\text{ep}}$  across  $k_{w3}$  is relatively small. Nevertheless,  $Q_{es}$  is still deteriorated with larger  $C_{pt}$  and  $k_{w3}$ . The impact of  $k_{w1}$  is plotted in Fig. 13.  $L_{es}$  and  $Q_{es}$  are the same with different  $k_{w1}$ 's.  $L_{ep}$ ,  $Q_{ep}$ , and  $k_{ep}$  are increased slightly with larger  $k_{w1}$ , while  $N_{ep}$  is decreased with larger  $k_{w1}$ . The calculated  $L_{es}$ ,  $L_{ep}$ ,  $N_{ep}$ ,  $k_{ep}$ ,  $Q_{es}$ , and  $Q_{ep}$  versus  $C_{pt}$  and  $C_{\rm st}$  are illustrated in Fig. 14. The impact of  $C_{\rm st}$  on  $L_{\rm es}$  and  $Q_{\rm es}$  is similar as the impact of  $C_{\rm pt}$  on  $L_{\rm ep}$  and  $Q_{\rm ep}$ .  $L_{\rm es}$   $(L_{\rm ep})$ increases with larger  $C_{\rm st}$  ( $C_{\rm pt}$ ), and  $Q_{\rm es}$  ( $Q_{\rm ep}$ ) decreases with larger  $C_{\rm st}$  ( $C_{\rm pt}$ ).  $N_{\rm ep}$  increases with larger  $C_{\rm st}$  and decreases with larger  $C_{pt}$ .  $k_{ep}$  decreases with larger  $C_{pt}$  or  $C_{st}$ .

Fig. 14. Calculated  $L_{\rm es}$ ,  $L_{\rm ep}$ ,  $N_{\rm ep}$ ,  $k_{\rm ep}$ ,  $Q_{\rm es}$ , and  $Q_{\rm ep}$  versus  $C_{\rm pt}$  and  $C_{\rm st}$  ( $L_p=L_s=1$  nH,  $L_{\rm pt}=L_{\rm st}=0.5$  nH,  $R_p=R_s=R_{\rm pt}=R_{\rm st}=1$   $\Omega$ , Frequency = 3 GHz,  $k_{\rm ps}=0.7$ ,  $k_{\rm pt}=k_{\rm st}=0.5$ , and  $k_{w1}=k_{w2}=k_{w3}=0.1$ ).

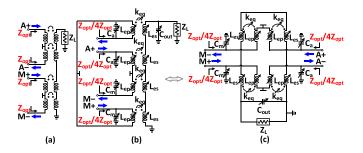

Fig. 15. Schematic of (a) conventional two-way differential PAs combined matching network, (b) proposed two-way differential PAs combined RMN in series, and (c) folded form of the two-way differential PAs combined RMN.

3) Design of RMN With Reconfigurable Transformer: The RMN is implemented using the reconfigurable transformer for the two-way differential power combining and impedance matching of HDIB PA. Comparing to the conventional two-way differential PAs combined matching network [see Fig. 15(a)] [16], [43], the proposed two-way differential PAs combined RMN is modified [see Fig. 15(b)] and folded [see Fig. 15(c)] to decrease the circuit size.

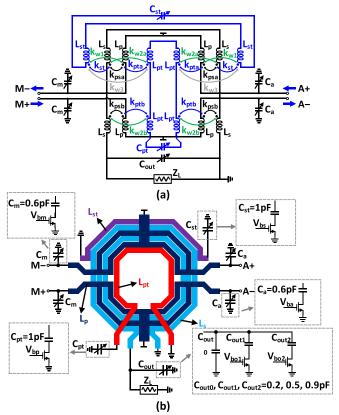

The reconfigurable transformer is finally implemented using a single-transformer footprint, as shown in Fig. 16. The primary windings of the transformer adopt main inductors  $L_p$  coupled with tuning inductors  $L_{\rm pt}$  located at the inner ring of the transformer. The secondary windings of the transformer adopt main inductors  $L_s$  coupled with tuning inductors  $L_{\rm st}$  located at the outer ring of the transformer. Parallel coils for the main inductors of both primary and secondary windings are used to improve Q.

The typical inductances of  $L_p$ ,  $L_s$ ,  $L_{\rm pt}$ , and  $L_{\rm st}$  are 216, 213, 236, and 226 pH. The typical coupling factors of  $k_{\rm psa}$ ,  $k_{\rm psb}$ ,  $k_{\rm pta}$ ,  $k_{\rm ptb}$ ,  $k_{\rm st}$ ,  $k_{w1}$ ,  $k_{w2}$ ,  $k_{w2b}$ , and  $k_{w3}$  are 0.83, 0.74, 0.63, 0.44, 0.61, 0.6, 0.63, 0.47, and 0.42. The EM simulated  $L_{\rm ep}$ ,  $L_{\rm ep}$ ,  $Q_{\rm ep}$ ,  $Q_{\rm es}$ ,  $k_{\rm ep}$ , and  $N_{\rm ep}/k_{\rm ep}$  of the reconfigurable transformer versus  $C_{\rm pt}$  and  $C_{\rm st}$  are shown in Fig. 17.  $L_{\rm ep}$  varies from 216 to 326 pH, while  $L_{\rm es}$  varies from 213 to 344 pH. Note that, to guarantee acceptable level of  $Q_{\rm ep}$  and  $Q_{\rm es}$ ,  $C_{\rm pt}$  and  $C_{\rm st}$  are limited to be lower than 2 pF.  $k_{\rm ep}$  is tuned by  $C_{\rm pt}$  and  $C_{\rm st}$  from 0.7 to 0.85, while  $N_{\rm ep}/k_{\rm ep}$  changes from 1.25 to 1.37. The quality factors of switched capacitors  $C_m$  (or  $C_a$ ),  $C_{\rm out1}$ ,  $C_{\rm out2}$ ,

Fig. 16. Detailed (a) lumped model circuits and (b) layout of the proposed two-way differential PAs combined RMN.

Fig. 17. EM simulated parameters across  $C_{\rm pt}$  and  $C_{\rm st}$  for the reconfigurable transformer.

$C_{\rm pt}$ , and  $C_{\rm st}$  are 171.05, 162.88, 130.63, 157.38, and 157.38 at 2.8 GHz, respectively. The stacked transistors could be used in the switch design to enhance the reliability of switch. The capacitor  $C_{\rm out}$  is located at the output of transformer.  $C_m$ ,  $C_a$ , and  $C_{\rm out}$  are used to optimize the matching network. The capacitor  $C_{\rm pt}$  is used to adjust the equivalent inductance of primary inductor, while the capacitor  $C_{\rm st}$  is used to adjust the equivalent inductance of secondary inductor.

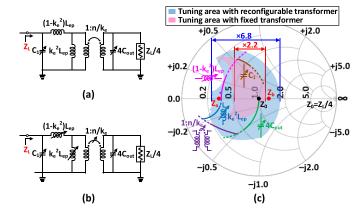

According to the parameters tuning range of the reconfigurable transformer in Fig. 17, the impedance tuning area can be estimated. The simplified equivalent single-end circuits

Fig. 18. (a) Simplified equivalent single-end circuit with fixed transformer. (b) Simplified equivalent single-end circuit with reconfigurable transformer. (c) Comparison of the impedance tuning range.

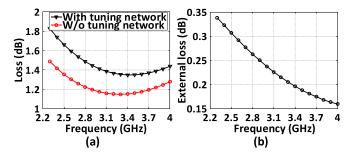

Fig. 19. (a) Simulated power loss of the transformer with/without the tuning network. (b) The simulated extra power loss of the transformer with the tuning network.

with fixed transformer [see Fig. 18(a)] and reconfigurable transformer [see Fig. 18(b)] are converted from the circuits in Fig. 15. Both tuning areas of the load impedance are compared in Fig. 18(c). About 6.8 times impedance tuning range is achieved with the proposed RMN, which is much larger than the 2.2 times impedance tuning range of the conventional circuit in Fig. 18(a). The two operation modes (mode I and mode II) of the RMN can be chosen with passive impedance of  $Z_a = Z_{\text{opt}}$  and  $Z_b = 4 Z_{\text{opt}}$  [see Fig. 18(c)]. Therefore, the proposed RMN exhibits an advantage to achieve impedance boosting for PA PBO efficiency enhancement with more freedom. Note that, as shown in Fig. 19(a), the proposed reconfigurable transformer introduces additional insertion loss due to the extra coupling to additional inductors and parasitics. The simulated extra power loss of the transformer with tuning network (i.e.,  $L_{pt}$ ,  $L_{st}$ ,  $C_{pt}$ , and  $C_{st}$ ) is shown in Fig. 19(b). It is seen that about 0.26- and 0.21-dB additional power losses could be introduced by the tuning network at 2.8 and 3.3 GHz, respectively.

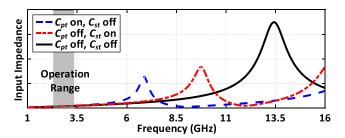

The simulated input impedances of the reconfigurable transformer with tuning network are shown in Fig. 20. This simulation did not include the matching capacitor  $C_a$ ,  $C_m$ , and  $C_{\text{out}}$  in Fig. 16(b). It can be seen that the related self-resonant frequencies are located at about 9.7 GHz (i.e.,  $C_{\text{pt}}$  off,  $C_{\text{st}}$  on) and 6.9 GHz (i.e.,  $C_{\text{pt}}$  on,  $C_{\text{st}}$  off), respectively, which are still far away from the operation frequency range (i.e., 2.3–3.4 GHz). Note that the self-resonant frequency of

Fig. 20. Simulated input impedance of the reconfigurable transformer.

${\it TABLE~III}$  Settings of Switched Capacitors in Various Operation Modes

|                          | Sett    | ing 1    | Sett     | ing 2    | Switch                     |  |  |

|--------------------------|---------|----------|----------|----------|----------------------------|--|--|

|                          | for low | ver band | for high | her band |                            |  |  |

|                          | 0-6dB   | 6-12dB   | 0-6dB    | 6-12dB   | Dimension                  |  |  |

|                          | PBO     | PBO      | PBO      | PBO      |                            |  |  |

| $C_m(1bit)$              | 0.6pF   | 0.6pF    | OFF      | OFF      | $2\times1152\mu$ m/40nm    |  |  |

| $C_a(1bit)$              | 0.6pF   | 0.6pF    | OFF      | OFF      | $2 \times 1152 \mu$ m/40nm |  |  |

| $C_{out}(2bit)$          | 1.1pF   | 1.6pF    | 0.2pF    | 0.7pF    | $2\times1152\mu$ m/40nm    |  |  |

| $C_{pt}(1 \mathrm{bit})$ | OFF     | 1pF      | OFF      | 1pF      | $2\times576\mu$ m/40nm     |  |  |

| $C_{st}(1bit)$           | 1pF     | OFF      | 1pF      | OFF      | $2\times576\mu$ m/40nm     |  |  |

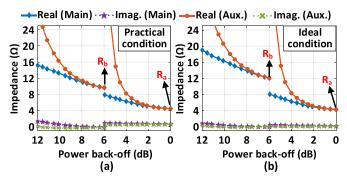

Fig. 21. Simulated load impedances of the proposed HDIB PA for (a) practical condition and (b) ideal condition.

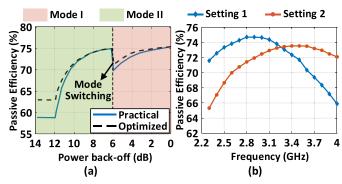

the proposed transformer could be adjusted by these capacitors (i.e.,  $C_{\rm pt}$  and  $C_{\rm st}$ ) to be away from the operated frequency band. Meanwhile, the switched capacitors in the PA matching network are reconfigured for lower and higher frequency bands to improve the performance. Table III shows the settings of the determined switched capacitors for different modes and frequency bands. For 0-6-dB PBO (mode I), Cpt is switched off, which leads to minimized  $L_{ep}$ .  $C_{st}$  is set to 1 pF to increase  $L_{\rm es}$ . A larger impedance transform ratio of the RMN is obtained with lower load impedance. For 6-12-dB PBO (mode II),  $C_{\rm st}$  is switched off to achieve minimized  $L_{\rm es}$ , while  $C_{\rm pt}$  is set to 1 pF to increase  $L_{\rm ep}$ . The simulated real part of the passive load impedance is boosted by the mode switching from  $R_a$  to  $R_b$  at 2.8 GHz [see Fig. 21(a)], while the imaginary part changes a little. Note that due to the impact of the parasitic inductance from the routings collecting the unit cells of sub-PA arrays, the impedance tuning range is deteriorated compared to the ideal case [see Fig. 21(b)]. In an ideal condition, the parasitics of routings and sub-PA are not considered.

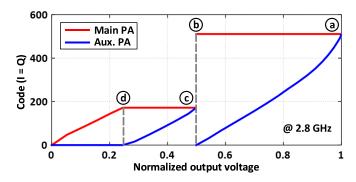

Fig. 22. Simulated code of main and auxiliary PAs (I=Q) versus normalized output voltage.

In practical implementation, due to the undesired parasitics, the ratio of  $R_b$  to  $R_a$  is not equal to the ideal case. Thus, the proposed DPA would have overlap or discontinuity in the power range for RMN modes I and II. To solve the problem, in practical measurement, the number of switched-on unit cells of main and auxiliary PAs of state © or @ should be finely adjusted to achieve the same output power. The adopted control codes for main and auxiliary PAs under two operation modes versus output voltage are illustrated in Fig. 22. From 0- to 6-dB PBO in mode I, the real part impedance of main PA increases gradually due to the decreased current from auxiliary PA, while the auxiliary PA turned off gradually with the real part impedance close to infinite at 6-dB PBO. The passive efficiency of the RMN decreases from 0- to 6-dB PBO [see Fig. 23(a)]. This is due to an increasing deviation of load impedance for main/auxiliary PAs. The simulated passive efficiency of the RMN with optimized impedances is compared in Fig. 23(a). In optimized conditions, the parasitics of routings and sub-PA are not considered. The tuning capacitors are adjusted to optimize the impedance for main and auxiliary PAs. Since both main and auxiliary PAs are fully on seeing boosted load impedance after mode switching at 6-dB PBO, the active load modulation is similar to the case at 0-dB PBO. The passive efficiency recovers to peak by the mode switching [see Fig. 23(a)]. From 6- to 12-dB PBO in mode II, the real part impedance of the main PA also increases due to the Doherty operation. The passive efficiency decreases again until 12-dB PBO with the auxiliary PA is fully off. Furthermore, with different settings of RMN (see Table III), the passive efficiency of the RMN can be improved at lower band and higher band, as illustrated in Fig. 23(b).

# IV. MEASUREMENT RESULTS

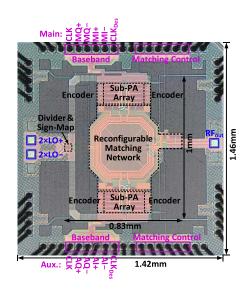

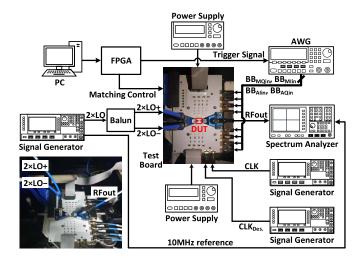

The proposed quadrature digital PA with HDIB is fabricated in 40-nm CMOS technology with a total size of  $1.42 \times 1.46 \text{ mm}^2$  (see Fig. 24). The chip core size is only  $0.83 \text{ mm}^2$ . The measurement setup is shown in Fig. 25. The chip is wire-bonded on a PCB. The  $2 \times$  LO signal is generated by a signal generator and converted to differential input signals by an off-chip balun. Input/output RF signals are fed/measured by GSSG/GSG probes. The arbitrary waveform generator (AWG) with four differential channels generates  $4 \times 9$ -bit-serial BB signals, including two differential I/Q signals of main PA and

Fig. 23. (a) Simulated passive efficiency of the RMN at 2.8 GHz. (b) Simulated passive efficiency of the RMN at 0-dB PBO versus frequency under different settings.

Fig. 24. Die micrograph.

Fig. 25. Measurement setup.

two differential I/Q signals of auxiliary PA. The matching control signals are programmed on a PC and up-loaded to an FPGA. The digital pre-distortion (DPD) algorithm on a PC is proposed to generate the baseband data and corresponding

Fig. 26. Measured DE versus Pout at 2.8 and 3.3 GHz.

Fig. 27. Measured system efficiency versus  $P_{\rm out}$  at 2.8 and 3.3 GHz.

matching control signals. Note that the baseband signals from the AWG and matching control signals from the FPGA should be synchronized in modulation measurement. Therefore, a trigger signal produced by the FPGA is used to synchronize the matching control signals with the baseband signal from AWG. The baseband sampling clock and the deserializer clock are produced by signal generators. A spectrum analyzer is used for the output signal measurement.

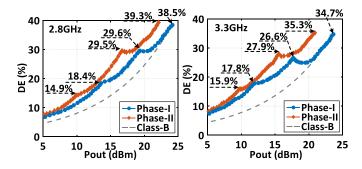

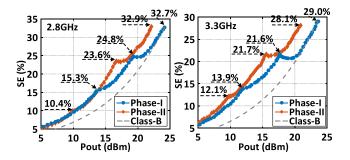

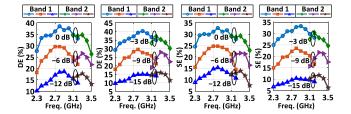

All the on-chip power consumptions (e.g. the PA array, encoders, deserializers, frequency divider, and sign map) are included for the system efficiency calculation. The continuous wave measurement is first taken. For CW measurement, the measured drain efficiency (DE) and versus  $P_{\text{out}}$ with phase-I ( $BB_{MI} = BB_{MQ}$ ,  $BB_{AI} = BB_{AQ}$ ) and phase-II  $(BB_{MO} = 0, BB_{AO} = 0)$  at 2.8 and 3.3 GHz is shown in Fig. 26. It achieves 38.5%/29.6%/18.4% DE at 2.8 GHz and 34.7%/26.6%/17.8% DE at 3.3 GHz for 0-/6-/12-dB PBO with phase-I, 39.3%/29.5%/14.9% at 2.8 GHz, and 35.3%/27.9%/15.9% DE at 3.3 GHz for 3-/9-/15-dB PBO with phase-II, respectively. The measured system efficiency (SE) versus  $P_{\text{out}}$  with phase-I (BB<sub>MI</sub> = BB<sub>MQ</sub>, and BB<sub>AI</sub> = BB<sub>AQ</sub>) and phase-II (BB<sub>MQ</sub> = 0, and BB<sub>AQ</sub> = 0) at 2.8 and 3.3 GHz is presented in Fig. 27. It achieves 32.7%/24.8%/15.3% SE at 2.8 GHz and 29%/21.6%/13.9% SE at 3.3 GHz for 0-/6-/ 12-dB PBO with phase-I, 32.9%/23.6%/10.4% SE at 2.8 GHz, and 28.1%/21.7%/12.1% SE at 3.3 GHz for 3-/9-/15-dB PBO with phase-II, respectively. For CW measurement, the power consumptions of the PA array and other circuits (including the encoders, de-serializers, and frequency divider) are 683.2 and 102.6 mW at 2.8 GHz and 660.2 and 108.6 mW at 3.3 GHz, respectively.

Fig. 28. Measured saturated Pout versus frequency.

Fig. 29. Measured system  $\eta$  (SE) and DE at various PBO levels versus frequency.

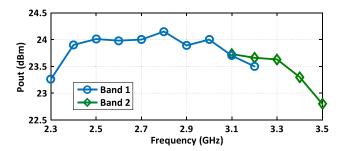

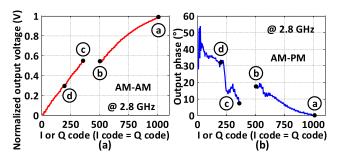

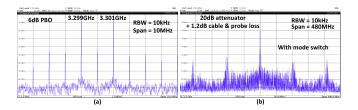

The RMN is reconfigured at different frequencies (band 1 and band 2) and PBO levels to enhance output power and efficiency. It delivers the maximum output power of 24.2 dBm, the peak system efficiency of 32.7%, and the peak DE of 38.5% at 2.8 GHz (see Figs. 28 and 29). The 1-dB bandwidth is from 2.3 to 3.4 GHz. The measured DE at various PBO levels versus frequency is also given in Fig. 29. The measured typical AM-AM and AM-PM distortions of phase-I at 2.8 GHz are shown in Fig. 30. Note that the I/Q code of state (c) is finely adjusted to guarantee the same output power with state (b). As depicted in Fig. 30(b), it shows about 10.85° phase jump at the mode switching. Then, 2-D memoryless DPD is performed to minimize all the code dependent AM-AM, AM-PM, and mode transition distortion around 6-dB PBO. First, I/Q codes for auxiliary PA are swept from zero to the maximum to obtain the AM-AM/AM-PM distortion of operation mode I, while all the unit cells of the main PA are switched on. Second, I/Q codes of main and auxiliary PAs are swept following the operation in mode II to obtain the AM-AM/AM-PM distortion of mode II. Third, the I/Q codes for the state (c) (i.e.,  $I_c/Q_c$ ) at 6-dB PBO should be determined, according to the measured data in previous steps to achieve the same output amplitude and phase as the state (b). The states with I/Q codes equal or greater than  $I_c/Q_c$  in mode II are not used to guarantee the monotonicity of the DPD algorithm. The discontinuity between modes I and II is eliminated. The single LUT is obtained with output signals in the complex domain constellation for the DPD.

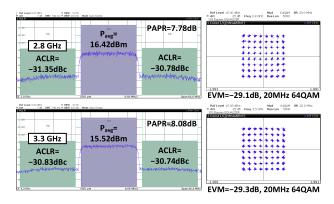

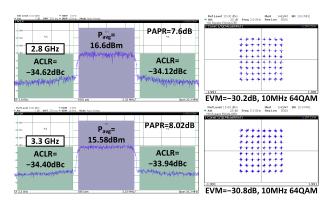

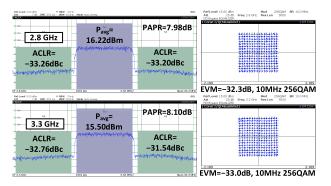

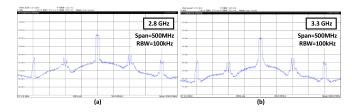

The real-time modulation measurements at 2.8/3.3 GHz for the 20-MHz 64 QAM, 10-MHz 64 QAM, and 10-MHz 256-QAM signals are shown in Figs. 31–33, respectively. For the 20-MHz 64 QAM modulation, the proposed PA transmits 16.42-/15.52-dBm average power with an average DE of 24.9%/22.78%, EVM of

Fig. 30. Measured (a) AM-AM and (b) AM-PM distortion (I = Q).

Fig. 31. Measured spectrum and constellation of the 20-MHz 64 QAM signal at 2.8 and 3.3 GHz.

Fig. 32. Measured spectrum and constellation of the 10-MHz 64 QAM signal at  $2.8~{\rm and}~3.3~{\rm GHz}.$

Fig. 33. Measured spectrum and constellation of the 10-MHz 256-QAM signal at 2.8 and 3.3 GHz.

-29.1/-29.3 dB, ACLR of -30.78/-30.74 dBc, and PAPR of 7.78/8.08 at 2.8/3.3 GHz, respectively. Meanwhile, for the 10-MHz 64 QAM modulation, it transmits

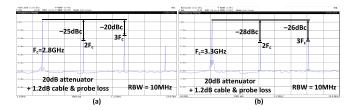

Fig. 34. Measured far-out spectrum of (a) 2.8- and (b) 3.3-GHz CW signals.

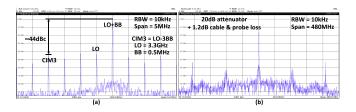

Fig. 35. Measured (a) close-in and (b) far-out output spectrum of single-sideband signal at full power.

Fig. 36. Measured (a) close-in and (b) far-out two-tone output spectrum with 2-MHz tone-spacing.

Fig. 37. Out-of-band spectrum of the 10-MHz 256-QAM signal at (a) 2.8 and (b) 3.3 GHz.

16.6-/15.58-dBm **EVM** of average power with -30.2/-30.8 dB, ACLR of -34.12/-33.94 dBc, and PAPR of 7.6/8.02 at 2.8/3.3 GHz, respectively. Moreover, for the 10-MHz, 256-QAM modulation, it transmits 16.22-/ 15.50-dBm average average power with an of 24.6%/22.7%, EVM of -32.3/-33.0 dB, ACLR of -33.2/-31.54 dBc, and PAPR of 7.98/8.10 at 2.8/3.3 GHz, respectively.

As shown in Fig. 34, the proposed DPA shows -25-/-28-dBc suppression for the second harmonic and -20-/-26-dBc suppression for the third harmonic at 2.8/3.3 GHz, respectively. Note that the inherent second harmonic of the PA is overlapped with the leakage of the  $2 \times LO$  input signal and the second harmonic of the frequency divider. The close-in and far-out spectrum of the single-sideband signal at full power are shown in Fig. 35. It shows about -44-dBc rejection of CIM3. Here, a 0.5-MHz single-tone signal is fed to the baseband. The measured close-in and far-out spectrum of a two-tone signal with 2-MHz tone-spacing

|                                           | This work                             |           |            |            | [33]                  | [35]             | [38]            | [39]            | [37]           | [36]       |  |

|-------------------------------------------|---------------------------------------|-----------|------------|------------|-----------------------|------------------|-----------------|-----------------|----------------|------------|--|

|                                           |                                       |           |            |            | JSSC2016              | ISSCC2017        | RFIC2019        | ISSCC2020       | JSSC2019       | JSSC2017   |  |

| A                                         | Hybrid-Doherty and impedance boosting |           |            |            | Class-G               | IQ sharing       | IQ sharing+     | IQ sharing+     | Class-G+       | IO alsoni  |  |

| Architecture                              |                                       |           |            |            |                       |                  | Class-G Doherty | Load modulation | IQ sharing     | IQ sharing |  |

| η Peaks in Yes                            |                                       |           |            | No         | No                    | N.A.             | Yes             | No              | Yes            |            |  |

| Complex Domain                            | Complex Domain                        |           |            |            | 110                   | 110              | 1 112 11        | 165             | 110            | 103        |  |

| $\eta$ Improvement at PBOs                |                                       | 3/6/9/1   | 12/15dB    |            | 6dB                   | 2.5/6/12dB       | 2.5/6/12dB      | 3/6dB           | 6dB            | N.A.       |  |

| Matching                                  | Matching 1 tran                       |           | sformer    |            | LC and off-chip balun | 1 power combiner | 2 transformers  | 1 transformer   | 2 transformers | Off chip   |  |

| Frequency (GHz)                           | 2.8                                   |           | 3          | .3         | 2                     | 2.5              | 2.2             | 0.85            | 2.2            | 0.8        |  |

| Peak Pout (dBm)                           | 24.2                                  |           | 23         | 23.6       |                       | 28.6             | 27.8            | 29.3            | 30.1           | 13.9       |  |

| Peak η (%)                                | 38.5/32.7 (DE/SE)                     |           | 34.7/29    | (DE/SE)    | 20 (PAE)              | 35 (PAE)         | 32.1 (SE)       | 43.1 (PAE)      | 37 (SE)        | 40.4 (SE)  |  |

| D 1 (2/6/0/                               | 39.3/29.6/ 35.3/26.6/                 |           |            | /26.6/     | N.A./14#/             | N.A./24#/        | N.A./23.0/      | 30#/35#/        | N.A./26.1/     |            |  |

| $\eta$ Peaks at 3/6/9/                    | 29.5/18.4/                            |           | 27.9/17.8/ |            | N.A./N.A./            | N.A./13.9/       | N.A./12.0/      | N.A./N.A./      | N.A./N.A./     | N.A.       |  |

| 12/15dB PBO (%)                           | 14.9 (DE)                             |           | 15.9 (DE)  |            | N.A. (PAE)            | N.A. (PAE)       | N.A. (SE)       | N.A. (PAE)      | N.A. (SE)      |            |  |

| Modulation Signal                         | 10MHz                                 | 20MHz     | 10MHz      | 20MHz      | 10MHz                 | LTE 10MHz        | 20MHz           | LTE 10MHz       | 20MHz          | LTE 10MHz  |  |

| Modulation Signal                         | 256QAM*                               | 64QAM*    | 256QAM*    | 64QAM*     | 64QAM                 | LIE IUMIIIZ      | 1024QAM         | 64QAM           | 256QAM         | 16QAM      |  |

| PAPR (dB)                                 | 7.98                                  | 7.78      | 8.1        | 8.08       | 6                     | 7.9              | 6.8             | 5.7             | 7.6            | 6.9        |  |

| Average $P_{out}$ (dBm)                   | 16.22                                 | 16.42     | 15.50      | 15.52      | 14.5                  | 20.7             | 21.0            | 23.6            | 22.5           | 7.0        |  |

| Average η (%)                             | 24.6 (DE)                             | 24.9 (DE) | 22.7 (DE)  | 22.78 (DE) | 12.2 (PAE)            | 14.6 (PAE)       | 18.4 (SE)       | 24.4 (PAE)      | 18.3 (SE)      | 29.1 (SE)  |  |

| Average II (70)                           | 18.9 (SE)                             | 19 (SE)   | 16.9 (SE)  | 17.0 (SE)  | 12.2 (IAL)            | 14.0 (1AL)       |                 |                 |                |            |  |

| EVM (dB)                                  | -32.3                                 | -29.1     | -33.0      | -29.3      | -28.9                 | -28.4            | -43.0           | -25.6           | -40.3          | -26.0      |  |

| Supply (V) 1.1                            |                                       |           |            | 2.4/1.2    | 1.1                   | 2.55/1.25        | 1.2/2.4         | 2.5/1.2         | 1.1            |            |  |

| Chip Size (mm <sup>2</sup> ) 2.1 (0.83**) |                                       |           |            | 1.75       | 1                     | 0.9**            | 1.2             | 3               | 0.23**         |            |  |

| CMOS Technology                           | 40nm                                  |           |            | 65nm       | 28nm                  | 65nm             | 55nm            | 65nm            | 28nm           |            |  |

TABLE IV

COMPARISON WITH STATE-OF-THE-ART QUADRATURE DIGITAL PAS

are shown in Fig. 36. The proposed mode switching affects the spectrum purity, which introduces about 6-dB worse spurious tones compared to the condition without mode switching.

The out-of-band spectrums for the 10-MHz 256-QAM signal are illustrated in Fig. 37. The spectrum replicas locate at integer times of baseband sampling frequency (i.e., 100 MHz),

Impared to the condition without mode switching. Integer times of baseband sampling frequency (i.e., 100 MHz),

$$L_{ep} = L_p - \frac{1}{A^2 + B^2} \Big( \Big( C_{pt} C_{st} \Big( L_{pt} M_{w1}^2 + L_{st} M_{pt}^2 - 2 M_{pt} M_{w1} M_{w3} \Big) \omega^2 - C_{pt} M_{pt}^2 - C_{st} M_{w1}^2 \Big)$$

$$\times \omega^2 A - B C_{pt} C_{st} \Big( M_{pt}^2 R_{st} + M_{w1}^2 R_{pt} \Big) \omega^3 \Big)$$

$$(5)$$

$$L_{es} = L_s - \frac{1}{A^2 + B^2} \Big( \omega^2 \Big( A C_{pt} C_{st} \Big( L_{pt} M_{st}^2 + L_{st} M_{w2}^2 - 2 M_{st} M_{w2} M_{w3} \Big) \omega^2 - B C_{pt} C_{st} \Big( M_{st}^2 R_{pt} + M_{w2}^2 R_{st} \Big) \omega - A \Big( C_{pt} M_{w2}^2 + C_{st} M_{st}^2 \Big) \Big) \Big) \Big)$$

$$- B C_{pt} C_{st} \Big( M_{pt}^2 R_{st} + M_{w1}^2 R_{pt} - 2 M_{pt} M_{w1} M_{w3} \Big) \omega^4 + B C_{pt} C_{st} \Big( M_{pt}^2 R_{st} + M_{w1}^2 R_{pt} \Big) \omega^3 + A \Big( C_{pt} M_{pt}^2 + C_{st} M_{w1}^2 \Big) \omega^2 + L_p (A^2 + B^2) \Big) \Big) \Big) \Big/ \Big( - B C_{pt} C_{st} \Big( L_{pt} M_{w1}^2 + L_{st} M_{pt}^2 - 2 M_{pt} M_{w1} M_{w3} \Big) \omega^5 - A C_{pt} C_{st} \Big( M_{pt}^2 R_{st} + M_{w1}^2 R_{pt} \Big) \omega^4 + B \Big( C_{pt} M_{pt}^2 + C_{st} M_{w1}^2 \Big) \omega^3 + R_p (A^2 + B^2) \Big) \Big)$$

$$Q_{es} = \Big( \Big( - A C_{pt} C_{st} \Big( L_{pt} M_{st}^2 + L_{st} M_{w2}^2 - 2 M_{st} M_{w2} M_{w3} \Big) \omega^4 + B C_{pt} C_{st} \Big( M_{st}^2 R_{pt} + M_{w2}^2 R_{st} \Big) \omega^3 + R_p (A^2 + B^2) \Big) \Big)$$

$$Q_{es} = \Big( \Big( - A C_{pt} C_{st} \Big( L_{pt} M_{st}^2 + L_{st} M_{w2}^2 - 2 M_{st} M_{w2} M_{w3} \Big) \omega^4 + B C_{pt} C_{st} \Big( M_{st}^2 R_{pt} + M_{w2}^2 R_{st} \Big) \omega^3 + R_p (A^2 + B^2) \Big) \Big)$$

$$Q_{es} = \Big( \Big( - A C_{pt} C_{st} \Big( M_{pt}^2 R_{st} + M_{w2}^2 R_{st} \Big) \omega^4 + B C_{pt} C_{st} \Big( M_{st}^2 R_{pt} + M_{w2}^2 R_{st} \Big) \omega^3 + R_p (A^2 + B^2) \Big) \Big)$$

$$Q_{es} = \Big( \Big( - A C_{pt} C_{st} \Big( M_{pt}^2 R_{st} + M_{w2}^2 R_{st} \Big) \omega^4 + B C_{pt} C_{st} \Big( M_{st}^2 R_{pt} + M_{w2}^2 R_{st} \Big) \omega^3 + R_p (A^2 + B^2) \Big)$$

$$+ A C_{pt} C_{st} \Big( M_{pt}^2 R_{st} + M_{w2}^2 R_{st} \Big) \omega^4 + B C_{pt} C_{st} \Big( M_{st}^2 R_{pt} + M_{w2}^2 R_{st} \Big) \omega^3 + R_p \Big( A^2 + B^2 \Big) \Big)$$

$$+ A C_{pt} C_{st} \Big( M_{pt}^2 R_{st} + M_{w2}^2 R_{st} \Big) \omega^4 + B C_{pt} C_{st} \Big( M_{st}^2 R_{st} + R_{st} \Big) \omega^2 + C_{st} M_{w$$

<sup>\*</sup>Bandwidth limited by the measurement setting. \*\*Core size. #Estimated from figures.

(19)

$$A = C_{\rm pt}C_{\rm st}L_{\rm pt}L_{\rm st}\omega^4 - C_{\rm st}M_{m3}^2\omega^4C_{\rm pt} - C_{\rm pt}C_{\rm st}R_{\rm pt}R_{\rm st}\omega^2 - C_{\rm pt}L_{\rm pt}\omega^2 - C_{\rm st}L_{\rm st}\omega^2 + 1$$

$$\tag{17}$$

$$B = -C_{pt}C_{st}L_{pt}R_{st}\omega^3 - C_{pt}C_{st}L_{st}R_{pt}\omega^3 + C_{pt}R_{pt}\omega + C_{st}R_{st}\omega.$$

(18)

$$M_{\text{eq}} = M_{\text{ps}} + \frac{1}{A^2 + B^2} \left( \omega^2 \left( C_{\text{st}} A C_{\text{pt}} \left( (-L_{\text{st}} M_{w2} + M_{\text{st}} M_{w3}) M_{\text{pt}} + M_{w1} \left( -L_{\text{pt}} M_{\text{st}} \right) + M_{w2} M_{w3} \right) \right) \omega^2 + B C_{\text{pt}} C_{\text{st}} \left( M_{\text{pt}} M_{w2} R_{\text{st}} + M_{\text{st}} M_{w1} R_{\text{pt}} \right) \omega + A \left( C_{\text{pt}} M_{\text{pt}} M_{w2} + C_{\text{st}} M_{\text{st}} M_{wl} \right) \right) \right)$$

which can be further improved with a larger sampling frequency. The performance of the proposed digital PA is summarized and compared with state-of-the-art quadrature digital PAs in Table IV. Broadband efficiency improvement at 3-/6-/9-/12-/15-dB PBO in the complex domain is achieved. It exhibits the maximum number of efficiency peaks comparing to previous quadrature digital PAs. The average efficiency is competitive with the highest operation frequency among the counterparts. It adopts a single supply without any supply switching and exhibits compact size using two-way combined RMN with a single-transformer footprint.

#### V. CONCLUSION

In this article, a prototype of quadrature digital PA with HDIB is proposed for PBO efficiency enhancement in the complex domain. A reconfigurable transformer is investigated to achieve impedance boosting for the RMN. Multiple efficiency peaks at deep PBOs are generated for significant efficiency improvement. Bandwidth extension of the Doherty operation is also realized by the RMN. The proposed technique is a promising candidate for portable devices with competitive performance.

#### APPENDIX

As for the reconfigurable transformer shown in Fig. 9, the equivalent inductance  $L_{\rm ep}$  and  $L_{\rm es}$ , equivalent quality factor  $Q_{\rm ep}$  and  $Q_{\rm es}$ , and equivalent resistance  $R_{\rm ep}$  and  $R_{\rm es}$  are derived as (5)–(10), shown at the bottom of the previous page. Note that  $M_{\rm ps}$ ,  $M_{\rm pt}$ ,  $M_{\rm st}$ ,  $M_{\rm w1}$ ,  $M_{\rm w2}$ ,  $M_{\rm w3}$ , A, and B [A and B shown at the top of the page] are defined as follows:

$$M_{\rm ps} = k_{\rm ps} \cdot \sqrt{L_p L_s} \tag{11}$$

$$M_{\rm pt} = k_{\rm pt} \cdot \sqrt{L_p L_{\rm pt}} \tag{12}$$

$$M_{\rm st} = k_{\rm st} \cdot \sqrt{L_{\rm s} L_{\rm st}} \tag{13}$$

$$M_{w1} = k_{w1} \cdot \sqrt{L_p L_{\text{st}}} \tag{14}$$

$$M_{w2} = k_{w2} \cdot \sqrt{L_s L_{\text{pt}}} \tag{15}$$

$$M_{w3} = k_{w3} \cdot \sqrt{L_{\rm pt} L_{\rm st}}.\tag{16}$$

The equivalent mutual inductance  $M_{\rm ep}$  [44] between  $L_{\rm ep}$  and  $L_{\rm es}$  is (19), as shown at the top of the page. The equivalent coupling factor  $k_{\rm ep}$  between  $L_{\rm ep}$  and  $L_{\rm es}$  is

$$k_{\rm eq} = \frac{M_{\rm eq}}{\sqrt{L_{\rm ep} \cdot L_{\rm es}}}.$$

(20)

The equivalent inductance ratio  $N_{\rm ep}$  of the reconfigurable transformer is

$$N_{\rm eq} = \sqrt{L_{\rm es}/L_{\rm ep}}. (21)$$

#### REFERENCES

- L. Kahn, "Single-sideband transmission by envelope elimination and restoration," *Proc. IRE*, vol. 40, no. 7, pp. 803–806, Jul. 1952.

- [2] D. K. Su and W. J. McFarland, "An IC for linearizing RF power amplifiers using envelope elimination and restoration," *IEEE J. Solid-State Circuits*, vol. 33, no. 12, pp. 2252–2258, Dec. 1998.

- [3] R. Wu, Y.-T. Liu, J. Lopez, C. Schecht, Y. Li, and D. Y. C. Lie, "High-efficiency silicon-based envelope-tracking power amplifier design with envelope shaping for broadband wireless applications," *IEEE J. Solid-State Circuits*, vol. 48, no. 9, pp. 2030–2040, Sep. 2013.

- [4] K. Oishi et al., "A 1.95 GHz fully integrated envelope elimination and restoration CMOS power amplifier using timing alignment technique for WCDMA and LTE," *IEEE J. Solid-State Circuits*, vol. 49, no. 12, pp. 2915–2924, Dec. 2014.

- [5] W. H. Doherty, "A new high efficiency power amplifier for modulated waves," *Proc. IRE*, vol. 24, no. 9, pp. 1163–1182, Sep. 1936.

- [6] F. Raab, "Efficiency of Doherty RF power-amplifier systems," IEEE Trans. Broadcast., vol. BC-33, no. 3, pp. 77–83, Sep. 1987.

- [7] W. M. Gaber, P. Wambacq, J. Craninckx, and M. Ingels, "A CMOS IQ digital Doherty transmitter using modulated tuning capacitors," in *Proc. IEEE Eur. Solid-State Circuits Conf.*, Sep. 2012, pp. 341–344.

- [8] E. Kaymaksut and P. Reynaert, "Transformer-based uneven Doherty power amplifier in 90 nm CMOS for WLAN applications," *IEEE J. Solid-State Circuits*, vol. 47, no. 7, pp. 1659–1671, Jul. 2012.

- [9] S. Hu, S. Kousai, J. S. Park, O. L. Chlieh, and H. Wang, "Design of a transformer-based reconfigurable digital polar Doherty power amplifier fully integrated in bulk CMOS," *IEEE J. Solid-State Circuits*, vol. 50, no. 5, pp. 1094–1106, May 2015.

- [10] V. Vorapipat, C. S. Levy, and P. M. Asbeck, "Voltage mode Doherty power amplifier," *IEEE J. Solid-State Circuits*, vol. 52, no. 5, pp. 1295–1304, May 2017.

- [11] S. Hu, F. Wang, and H. Wang, "A 28 GHz/37 GHz/39 GHz multiband linear Doherty power amplifier for 5G massive MIMO applications," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 32–33.

- [12] Y. Shen et al., "A fully-integrated digital-intensive polar Doherty transmitter," in Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC), Jun. 2017, pp. 196–199.

- [13] F. Raab, "Average efficiency of class-G power amplifiers," *IEEE Trans. Consum. Electron.*, vol. CE-32, no. 2, pp. 145–150, May 1986.

- [14] J. S. Walling, S. S. Taylor, and D. J. Allstot, "A class-G supply modulator and class-E PA in 130 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 44, no. 9, pp. 2339–2347, Sep. 2009.

- [15] S.-M. Yoo et al., "A class-G switched-capacitor RF power amplifier," IEEE J. Solid-State Circuits, vol. 48, no. 5, pp. 1212–1224, May 2013.

- [16] G. Liu, P. Haldi, T.-J.-K. Liu, and A. M. Niknejad, "Fully integrated CMOS power amplifier with efficiency enhancement at power back-off," *IEEE J. Solid-State Circuits*, vol. 43, no. 3, pp. 600–609, Mar. 2008.

- [17] Y. Lee and S. Hong, "A dual-power-mode output matching network for digitally modulated CMOS power amplifier," *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 4, pp. 1570–1579, Apr. 2013.

- [18] Y. Yoon et al., "A dual-mode CMOS RF power amplifier with integrated tunable matching network," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 1, pp. 77–88, Jan. 2012.

- [19] L. Ye, J. Chen, L. Kong, E. Alon, and A. M. Niknejad, "Design considerations for a direct digitally modulated WLAN transmitter with integrated phase path and dynamic impedance modulation," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3160–3177, Dec. 2013.

- [20] E. Kaymaksut and P. Reynaert, "Dual-mode CMOS Doherty LTE power amplifier with symmetric hybrid transformer," *IEEE J. Solid-State Circuits*, vol. 50, no. 9, pp. 1974–1987, Sep. 2015.

- [21] L. Xiong, T. Li, Y. Yin, H. Min, N. Yan, and H. Xu, "A broadband switched-transformer digital power amplifier for deep back-off efficiency enhancement," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2019, pp. 76–77.

- [22] Y. Yang, J. Cha, B. Shin, and B. Kim, "A fully matched N-way Doherty amplifier with optimized linearity," *IEEE Trans. Microw. Theory Techn.*, vol. 51, no. 3, pp. 986–993, Mar. 2003.

- [23] N. Srirattana, A. Raghavan, D. Heo, P. E. Allen, and J. Laskar, "Analysis and design of a high-efficiency multistage Doherty power amplifier for wireless communications," *IEEE Trans. Microw. Theory Techn.*, vol. 53, no. 3, pp. 852–860, Mar. 2005.

- [24] H. Golestaneh, F. A. Malekzadeh, and S. Boumaiza, "An extended-bandwidth three-way Doherty power amplifier," *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 9, pp. 3318–3328, Sep. 2013.

- [25] D. Jung, S. Li, J.-S. Park, T.-Y. Huang, H. Zhao, and H. Wang, "A CMOS 1.2-V hybrid current- and voltage-mode three-way digital Doherty PA with built-in phase nonlinearity compensation," *IEEE J. Solid-State Circuits*, vol. 55, no. 3, pp. 525–535, Mar. 2020.

- [26] W. Tai et al., "A transformer-combined 31.5 dBm outphasing power amplifier in 45 nm LP CMOS with dynamic power control for back-off power efficiency enhancement," *IEEE J. Solid-State Circuits*, vol. 47, no. 7, pp. 1646–1658, Jul. 2012.

- [27] P. A. Godoy, S. Chung, T. W. Barton, D. J. Perreault, and J. L. Dawson, "A 2.4-GHz, 27-dBm asymmetric multilevel outphasing power amplifier in 65-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 47, no. 10, pp. 2372–2384, Oct. 2012.

- [28] Z. Hu, L. C. N. D. Vreede, M. S. Alavi, D. A. Calvillo-Cortes, R. B. Staszewski, and S. He, "A 5.9 GHz RFDAC-based outphasing power amplifier in 40-nm CMOS with 49.2% efficiency and 22.2 dBm power," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, May 2016, pp. 206–209.

- [29] S. Hu, S. Kousai, and H. Wang, "A broadband CMOS digital power amplifier with hybrid class-G Doherty efficiency enhancement," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2015, pp. 44–45.

- [30] V. Vorapipat, C. Levy, and P. Asbeck, "A class-G voltage-mode Doherty power amplifier," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 46–47.

- [31] A. Zhang and M. S.-W. Chen, "A watt-level phase-interleaved multisubharmonic switching digital power amplifier," *IEEE J. Solid-State Circuits*, vol. 54, no. 12, pp. 3452–3456, Dec. 2019.

- [32] A. Zhang and M. S.-W. Chen, "A subharmonic switching digital power amplifier for power back-off efficiency enhancement," *IEEE J. Solid-State Circuits*, vol. 54, no. 4, pp. 1017–1028, Apr. 2019.

- [33] W. Yuan, V. Aparin, J. Dunworth, L. Seward, and J. S. Walling, "A quadrature switched-capacitor power amplifier," *IEEE J. Solid-State Circuits*, vol. 51, no. 5, pp. 1200–1209, May 2016.

- [34] R. Bhat, J. Zhou, and H. Krishnaswamy, "Wideband mixed-domain multi-tap finite-impulse response filtering of out-of-band noise floor in watt-class digital transmitters," *IEEE J. Solid-State Circuits*, vol. 52, no. 12, pp. 3405–3420, Dec. 2017.

- [35] A. Passamani, D. Ponton, E. Thaller, G. Knoblinger, A. Neviani, and A. Bevilacqua, "A 1.1 V 28.6 dBm fully integrated digital power amplifier for mobile and wireless applications in 28nm CMOS technology with 35% PAE," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 232–233.

- [36] H. Jin, D. Kim, and B. Kim, "Efficient digital quadrature transmitter based on IQ cell sharing," *IEEE J. Solid-State Circuits*, vol. 52, no. 5, pp. 1345–1357, May 2017.

- [37] S.-W. Yoo, S.-C. Hung, and S.-M. Yoo, "A watt-level quadrature class-G switched-capacitor power amplifier with linearization techniques," *IEEE J. Solid-State Circuits*, vol. 54, no. 5, pp. 1274–1287, May 2019.

- [38] S.-C. Hung, S.-W. Yoo, and S.-M. Yoo, "A quadrature class-G complex-domain Doherty digital power amplifier," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2019, pp. 291–294.

- [39] D. Zheng et al., "A 15b quadrature digital power amplifier with transformer-based complex-domain power-efficiency enhancement," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2020, pp. 370–371.

- [40] H. J. Qian, B. Yang, J. Zhou, H. Xu, and X. Luo, "A quadrature digital power amplifier with hybrid Doherty and impedance boosting for efficiency enhancement in complex domain," in *Proc. IEEE Radio* Freq. Integr. Circuits Symp. (RFIC), Aug. 2020, pp. 127–130.

- [41] M. S. Alavi, R. B. Stasewski, L. C. N. D. Vreede, A. Visweswaran, and J. R. Long, "All-digital RF I/Q modulator," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 11, pp. 3513–3526, Nov. 2012.

- [42] H. J. Qian, Y. Shu, J. Zhou, and X. Luo, "A 20–32-GHz quadrature digital transmitter using synthesized impedance variation compensation," *IEEE J. Solid-State Circuits*, vol. 55, no. 5, pp. 1297–1309, May 2020.

- [43] I. Aoki, S. D. Kee, D. B. Rutledge, and A. Hajimiri, "Distributed active transformer—A new power-combining and impedance-transformation technique," *IEEE Trans. Microw. Theory Techn.*, vol. 50, no. 1, pp. 316–331, Jan. 2002.

- [44] J. R. Long, "Monolithic transformers for silicon RF IC design," IEEE J. Solid-State Circuits, vol. 35, no. 9, pp. 1368–1382, Sep. 2000.

Huizhen Jenny Qian (Member, IEEE) received the B.E., master's, and Ph.D. degrees in electronic engineering from the University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2008, 2011, and 2018, respectively.

Since 2019, she has been a Faculty Member with the Center for Integrated Circuits, UESTC, where she is currently an Associate Professor. Her research interests include the wideband microwave/millimeter-wave transceiver, reconfigurable passive circuits, and on-chip array systems.

Dr. Qian was a recipient/co-recipient of the 2018 IEEE Microwave Theory and Techniques (MTT)-Society Graduate Fellowship Award, the IEEE International Wireless Symposium (IWS) Best Student Paper Awards in 2015 and 2018, the IEEE International Microwave Symposium (IMS) Student Design Competition Awards in 2017 and 2018, and the IEEE International Symposium on Radio-Frequency Integration Technology (RFIT) Best Student Paper Awards in 2016 and 2019.

Bingzheng Yang (Graduate Student Member, IEEE) received the B.E. degree in microelectronics from the University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2016, where he is currently pursuing the Ph.D. degree in microelectronics and solid-state electronics.

His research interest includes digital-assisted RF/microwave/millimeter-wave transmitter.

Mr. Yang was a recipient of the 2021 IEEE Microwave Theory and Techniques (MTT)-Society Graduate Fellowship Award.

**Jie Zhou** (Student Member, IEEE) received the B.E. degree in microelectronics from the University of Electronic Science and Technology of China, Chengdu, China, in 2016, where he is currently pursuing the Ph.D. degree in microelectronics and solid-state electronics.

His current research interest includes reconfigurable transmitter and receiver.

Mr. Zhou was a recipient of the 2017 IEEE Microwave Theory and Techniques (MTT)-Society Undergraduate/Pre-Graduate Scholarship Award.

**Hongtao Xu** (Senior Member, IEEE) received the B.S. degree in electronic engineering from Fudan University, Shanghai, China, in 1997, and the M.A. degree in economics and the Ph.D. degree in electrical and computer engineering from the University of California at Santa Barbara, Santa Barbara, CA, USA, in 2003 and 2005, respectively.

He was with Intel Labs, Hillsboro, OR, USA. In 2015, he joined the School of Microelectronics, Fudan University, as a Full Professor. He has authored or coauthored more than 50 journal and

conference papers. He holds 12 U.S. patents in the areas of RF transceiver and front-end module. His technical research interests include innovative analog/RF/millimeter-wave circuits and wireless systems for communication and sensing.

Dr. Xu is currently a Steering Committee Member and/or a Technical Program Committee Member of the IEEE International Solid-State Circuits Conference (ISSCC), the IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, and the IEEE International Wireless Symposium (IWS). He serves as an Associate Editor for IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS.

**Xun Luo** (Senior Member, IEEE) received the B.E. and Ph.D. degrees in electronic engineering from the University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2005 and 2011, respectively.

From 2010 to 2013, he was with Huawei Technologies Company Ltd., Shenzhen, China, as the Project Manager to guide research and development projects of multi-band microwave/millimeterwave (mm-wave) integrated systems for backhaul and wireless communication. Before joining UESTC,

he was an Assistant Professor with the Department of Microelectronics, Delft University of Technology, Delft, The Netherlands. Since 2015, he has been with UESTC as a Full Professor, where he has been appointed as the Executive Director of the Center for Integrated Circuits. Since 2020, he has been the Head of the Center for Advanced Semiconductor and Integrated Micro-System, UESTC. He has authored or coauthored more than 100 journal and conference papers. He holds 35 patents. His research interests include the RF/microwave/mm-wave integrated circuits, multiple-resonance terahertz (THz) modules, multi-bands backhaul/wireless systems, reconfigurable passive circuits, smart antenna, and system in package.

Dr. Luo is a Technical Program Committee Member of the IEEE International Microwave Symposium (IMS), the IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, and the IEEE International Wireless Symposium (IWS). He is also a Technical Committee Member of the Microwave Theory and Techniques Society MTT-4 on Microwave Passive Components and Transmission Line Structures, the MTT-5 on Filters, and the MTT-23 on Wireless Communications. He is also the Vice-Chair of the IEEE MTT-Society Chengdu Chapter. He was bestowed by China as the China Overseas Chinese Contribution Award in 2016. He received the UESTC 2016-2020 Outstanding Scientific Researcher Award. He received the UESTC Distinguished Innovation and Teaching Award in 2018 and the UESTC Outstanding Undergraduate Teaching Promotion Award in 2016. His Research Group BEAM X-Laboratory received multiple best paper awards and best design competition awards, including the IEEE IWS Best Student Paper Award in 2015 and 2018, the IEEE IMS Best Student Design Competition Award from 2017 to 2019, the IEEE IMS Sixty-Second Presentation Competition Award in 2019, and multiple best paper award finalists at the IEEE conferences. He is also the TPC Co-Chair of the IEEE IWS in 2018 and the IEEE International Symposium on Radio-Frequency Integration Technology (RFIT) in 2019. He serves as a Track Editor for IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS and an Associate Editor for IET Microwaves, Antennas and Propagation.