# A 15-Channel Orthogonal Code Chopping Instrumentation Amplifier for Area-Efficient, Low-Mismatch Bio-Signal Acquisition

Jeong Hoan Park, *Member, IEEE*, Tao Tang, *Member, IEEE*, Lian Zhang, *Student Member, IEEE*, Kian Ann Ng, *Senior Member, IEEE*, Gil Gerald Lasam Gammad<sup>®</sup>, Shih-Cheng Yen<sup>®</sup>, and Jerald Yoo<sup>®</sup>, *Senior Member, IEEE*

Abstract—This article presents a 15-channel orthogonal code chopping instrumentation amplifier (OCCIA) for an areaefficient and low gain-mismatch multi-channel bio-signal acquisition. Orthogonal codes directly modulate each channel and merge into a single signal for sharing IA, while performing dynamic offset compensation with low power consumption. Digitization-before-demodulation (DBD) transmits the combined modulated data directly, which alleviates ripple noise, and completely removes the demodulation and TX encoding overhead from the ASIC. The proposed OCCIA in 0.18-μm 1P6M CMOS, when compared with the recent multi-channel instrumentation amplifiers (IAs), shows the smallest area (0.019 mm²/Ch.), low gain mismatch (0.43%), with the lowest power consumption (1.97 μW/Ch.) and low crosstalk (< -51.5 dB) at 490-Hz bandwidth.

*Index Terms*—Bio-signal acquisition, demodulation-before-digitization (DBD), instrumentation amplifier (IA), low mismatch, orthogonal code chopping (OCC).

## I. Introduction

S the life span of people increases and lifestyle is changed, there is a rapid increase in patients who suffer from heart diseases and brain diseases such as epilepsy and dementia. Compared with the 1900s, 19 million patients died from heart disease in 2010, which is a 40% increase. The 2.7 million patients passed away with Alzheimer's diseases, which were ranked in the top 10 diseases in 2010 [1]. Many researchers have studied to find the precursor to mitigate such diseases, and electrical bio-signal acquisitions, such

Manuscript received January 23, 2020; revised March 27, 2020; accepted April 14, 2020. Date of publication May 15, 2020; date of current version September 24, 2020. This article was approved by Guest Editor Po-Hung Chen. This work was supported in part by A\*STAR AME Nanosystems through the Edge Program under Grant A18A4b0055 and in part by the National University of Singapore through the Hybrid Flexible Electronic Systems Program under Grant R-263-501-011-133/731. (Corresponding author: Jerald Yoo.)

Jeong Hoan Park, Tao Tang, and Lian Zhang are with the Department of Electrical and Computer Engineering, National University of Singapore, Singapore 117583 (e-mail: jhpark@nus.edu.sg).

Kian Ann Ng and Jerald Yoo are with the Department of Electrical and Computer Engineering, National University of Singapore, Singapore 117583, and also with the N.1 Institute for Health, National University of Singapore, Singapore 117585 (e-mail: jyoo@nus.edu.sg).

Gil Gerald Lasam Gammad and Shih-Cheng Yen are with the N.1 Institute for Health, National University of Singapore, Singapore 117585.

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2020.2991542

3. Filtering & Demodulation Overhead to the Off-Chip

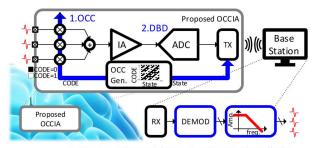

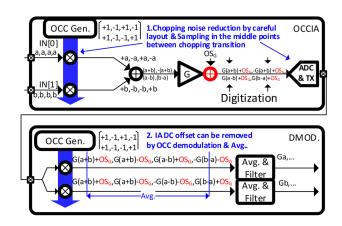

Fig. 1. Proposed OCCIA architecture.

as the electrocardiogram (ECG) and electroencephalogram (EEG), are widely chosen due to its convenience and non-invasiveness [2]–[4]. Their low temporal and spatial resolution, however, cannot offer fully sufficient information about patients' status for the delicate study and accurate monitoring [5]. The brain–machine interface also needs high temporal and spatial resolution bio-signal to send specific commands to the machine [6]. As the demands of more accurate monitoring and machine control are required, the implantable multi-channel bio-signal acquisition system-on-chip (SoC) has been widely developed to achieve higher temporal and spatial resolution [7]–[12]. With increased channel count, the SoC requires aggressive area and power reduction strategies, and especially for power-constrained implantable applications, low-power data encoding and transmission is a must [7]–[12].

To meet the aforementioned requirements, this article proposes an orthogonal code chopping instrumentation amplifier (OCCIA) with digitization-before-demodulation (DBD) scheme (Fig. 1). It exploits the orthogonal codes set that directly modulates and merges the multi-channel input data simultaneously for sharing a single instrumentation amplifier (IA), while reducing dynamic offset noise, power consumption, and inter-channel crosstalk at once. Sharing only a single IA among all channels will fundamentally reduce the gain mismatch while achieving power and area efficiency. DBD performs digitization prior to demodulation between chopping transitions, which leads to intrinsically ripple-free as compared to conventional chopping. As the merged signal is digitized

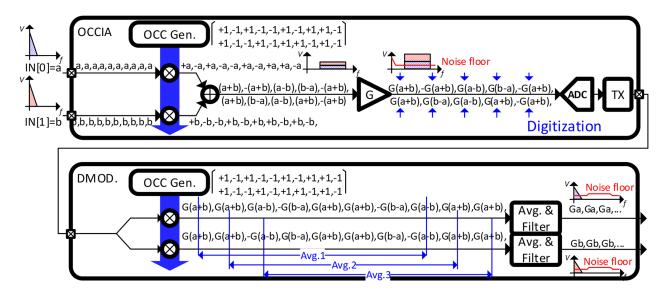

Fig. 2. Orthogonal Code Chopping (OCC) methodology.

and directly transmitted outside, DBD can relieve demodulation and TX encoding overhead from the power-constrained SoC. Such strategies are especially practical to reduce the power and area of multi-channel implanted devices that are suitable in the resource-constrained implantable environment.

This article is organized as follows. Section II illustrates the concepts of the orthogonal code chopping (OCC) and DBD and their benefits compared with other frequency modulations. Section III shows the circuit details in order to implement the proposed concepts. Measurement results and discussions are described in Sections IV and V, respectively. Finally, Section VI provides the conclusion.

# II. ORTHOGONAL CODE CHOPPING AND DIGITIZATION BEFORE DEMODULATION

## A. Orthogonal Code Chopping (OCC)

Fig. 2 illustrates the operating principle of the proposed OCC method [13]. Orthogonal codes set from the OCC generator (OCC Gen.), used as a chopping input, modulates all inputs into one spread spectrum in the higher frequency range. As the orthogonal codes keep the orthogonality of the modulated input spectrums, all the input signals are merged and capable of sharing a single amplifier. The orthogonal codes set also have the same benefit as chopping stabilizations, as the amplified signal frequency is higher than low-frequency noise such as flicker noise. Moreover, the spread signal is much more immune to frequency-specific interference.

After amplification, ADC digitizes the modulated signal, DBD, and TX transmits the digitized signal to the off-chip demodulator (DMOD) via a single communication channel. As the OCC already merges all the inputs, there are no needs of the additional modulator or serializer, which results in power and area saving. The separation of OCCIA with DMOD has another benefit regarding power reduction in the transmitting node that has more constraint of power and area; this is especially the case for multi-channel implantable sensors. The transmitted signal is multiplied with the orthogonal

codes set and averaged with further noise reduction. The signal orthogonality enables the signals to demodulate back into their respective original signals.

# B. Comparison of the OCC With Other Multi-Channel Chopping in Instrumentation Amplifiers (IAs)

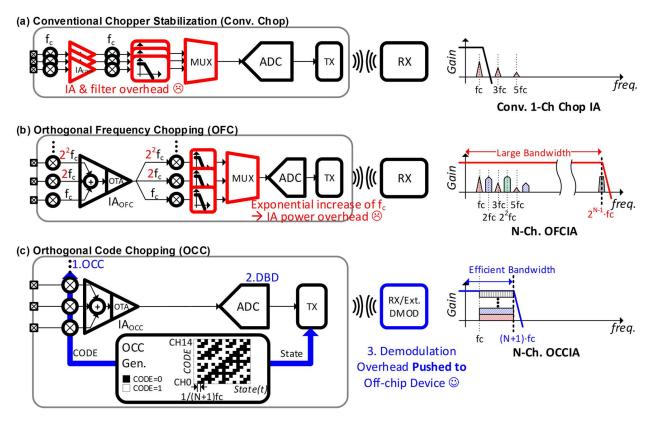

To further analyze the advantages of the OCC, Fig. 3 shows the quantitative analysis of the OCC compared with the conventional chopper-stabilization (Conv. Chop) [14]–[16] and the orthogonal frequency chopping (OFC) [17].

In multi-channel (# of Ch =  $N_{\rm Ch}$ ) Conv. Chop [14]–[16], IA and filter area ( $A_{\rm IA+Filter}$ ) overheads increase proportionally to  $N_{\rm Ch}$  as

$$A_{\text{IA+Filter}} = N_{\text{Ch}} \cdot (A_{\text{OTA}} + A_{C'\text{IN}} + A_{\text{Filter}}). \tag{1}$$

If the  $g_M/I_D$  ratio and gain are similar, IA power consumption is proportional to bandwidth (BW) as follows:

$$BW = g_M / (A \cdot C_L) \tag{2}$$

where BW is the bandwidth,  $g_M$  is the total transconductance of OTA, A is the voltage gain, and  $C_L$  is the load capacitance [7]. Assuming that total drain current of OTA  $(I_D)$  is proportional to  $g_M$ , (2) can be replaced by

$$BW = k \cdot I_D / (A \cdot C_L). \tag{3}$$

Even though OFC shares single IA by using orthogonal frequency modulation to reduce area overhead, the IA BW should cover the fastest chopping frequency as

$$f_{\text{chopping,fast,OFCIA}} = 2^{N_{\text{Ch}} - 1} \cdot f_c$$

(4)

where  $f_c$  is the slowest (base) chopping frequency [17] and  $N_{\rm ch}$  is the number of channels. Equation (3) shows that chopping frequency increases exponentially with  $N_{\rm Ch}$  to avoid harmonic distortion. In contrast, the BW of the OCCIA needs to cover

$$f_{\text{chopping,fast,OCCIA}} = (N_{\text{Ch}} + 1) \cdot f_c$$

(5)

Fig. 3. Comparison between (a) conventional chopping stabilization (Conv. Chop), (b) OFC, and (c) OCC.

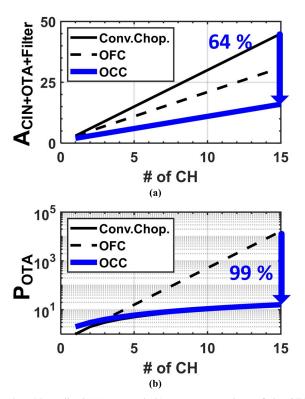

Fig. 4. Normalized (a) area and (b) power comparison of the OTA as increasing the number of channels.

that increases linearly with  $N_{\rm Ch}$ , as OCC modulates and spreads the input spectrum while maintaining the orthogonality and dimming harmonic crosstalk. This leads OCC to take only the advantages of the OFC (superior area and gain

TABLE I

SUMMARIZED EQUATIONS OF CONV. CHOP, OFC, AND OCC

|                                     | Conventional Chop.                     | OFC                                                       | OCC                            |

|-------------------------------------|----------------------------------------|-----------------------------------------------------------|--------------------------------|

| <sup>a</sup> A <sub>IA+Filter</sub> | Nch (Aota+Acin+Afilter)                | N <sub>Ch</sub> ·(A <sub>CIN</sub> +A <sub>Filter</sub> ) | Nch (Acin)                     |

|                                     |                                        | $+A_{OTA}$                                                | $+A_{OTA}$                     |

| $^{b}\mathbf{P}_{\mathrm{OTA}}$     | N <sub>Ch</sub> ·P <sub>OTA,CONV</sub> | 2(NCh-1) · POTA,CONV                                      | $(N_{Ch}+1)\cdot P_{OTA,CONV}$ |

| . 4 . 4                             | . 4 =1.1.1                             |                                                           |                                |

a: Acin:Aota:AFilter=1:1:1.

b: Pota,conv is minimum OTA power of Conv. Chop to cover fe.

mismatch) and the conventional IA (low power consumption compared to OFC at high  $N_{\rm Ch}$ ). Carefully considering an input range of the peak amplitude of the brain cortex  $(0.31 \pm 0.07 \ {\rm mV})$  and low concurrent activation between different regions [18], we choose  $N_{\rm Ch} = 15$ . Table I summarizes the relationship between power and area of the conventional chopper, OFC, and OCC, assuming that the area ratio of IA, filter, and input capacitor is 1:1:1 and that the most of the power consumption occurs in the IA. As shown in Fig. 4, at  $N_{\rm Ch} = 15$ , the OCCIA achieves 64% area ( $A_{\rm CIN+OTA+Filter}$ ) reduction than the conventional chopping, as well as a 99% reduction in OTA power compared to OFC.

# C. Number of Channels ( $N_{Ch}$ ) and Its Design Considerations

We also analyze the maximum number of channels allowed by: 1) the dynamic range and sampling rate required from the ADC; 2) TX power/ $N_{\rm Ch}$ ; and 3) OCC generator (OCC Gen.) area/ $N_{\rm Ch}$ , to find the theoretical maximum number of channels for a given BW in OCC. First is the relationship between the number of channels ( $N_{\rm Ch}$ ) and the ADC bit widths ( $B_{\rm ADC}$ ). Considering the ADC minimal dynamic range of 45 dB to

127

255

511

1023

2047

4095

| RELATIONSHIP DETWEEN INCh, DADC, JS,ADC, I / INCh, AND A/INCh |               |              |                         |                                                 |  |  |  |  |  |  |

|---------------------------------------------------------------|---------------|--------------|-------------------------|-------------------------------------------------|--|--|--|--|--|--|

| ADC Required                                                  |               |              | Ideal SAR ADC           |                                                 |  |  |  |  |  |  |

| $N_{Ch}$                                                      | $B_{ADC,min}$ | fs,ADC (kHz) | $^{a}P/N_{Ch}$ (nW/Ch.) | $^{b}A/N_{Ch}(10^{-3}\text{mm}^{2}/\text{Ch.})$ |  |  |  |  |  |  |

| 1                                                             | 7.97          | 1            | 25.1                    | 0.2383                                          |  |  |  |  |  |  |

| 3                                                             | 8.47          | 2            | 23.6                    | 0.1123                                          |  |  |  |  |  |  |

| 7                                                             | 8.97          | 4            | 28.7                    | 0.0681                                          |  |  |  |  |  |  |

| 15                                                            | 9.47          | 8            | 37.8                    | 0.0449                                          |  |  |  |  |  |  |

| 31                                                            | 9.97          | 16           | 51.8                    | 0.0307                                          |  |  |  |  |  |  |

| 63                                                            | 10.47         | 32           | 72.0                    | 0.0214                                          |  |  |  |  |  |  |

101.1

142.4

201.0

283.9

401.4

567.5

0.0150

0.0106

0.0075

0.0053

0.0037

0.0026

TABLE II RELATIONSHIP BETWEEN  $N_{Ch}$ ,  $B_{ADC}$ ,  $f_{SADC}$ ,  $P/N_{Ch}$ , AND  $A/N_{Cl}$

13.47 FOM is 100 fJ/Conv.

10.97

11.47

11.97

12.47

$C_{UNIT}$  is 0.5 fF with 9.5 ×10<sup>-7</sup>mm<sup>2</sup> at the 180 nm CMOS process. [26]

64

128

256

512

1024

2048

cover bio-signals [16], the minimum  $B_{\rm ADC}$  should be 7.47. In OCCIA, the minimum ADC bit widths  $(B_{ADC.min})$  is expressed as follows [19]:

$$B_{\text{ADC,min}} = 7.47 + \log_2 \sqrt{N_{\text{Ch}}}.$$

(6)

The sampling rate of the ADC  $(f_{S,ADC})$  is determined by the code length (CL) that is determined by  $N_{\rm Ch}$  as shown in the following equation:

$$f_{S,ADC} = f_{Nyquist} \cdot CL \approx f_{SAMPLE} \cdot N_{Ch}$$

(7)

where  $f_{\text{Nyquist}}$  is the Nyquist sampling rate of the bio-signalof-interest. Using (7), we can induce the ideal ADC FOM (FOM<sub>ADC,Ideal</sub>) expressed as [20]

$$FOM_{ADC,Ideal} = P/(f_{S,ADC} \cdot 2^{ENOB}).$$

(8)

For the area analysis, an SAR ADC can be classified into a unit capacitor in the DAC ( $C_{\text{UNIT}}$ ), a comparator, and a digital controller. Here, the digital controller size linearly increases with  $N_{\rm Ch}$ , and the comparator size is negligible. The total area of  $C_{\text{UNIT}}$  ( $\Sigma C_{\text{UNIT}}$ ) can be expressed as

$$\sum C_{\text{UNIT}} \propto 2^{\text{ENOB}}.$$

(9)

From (9), most of the area comes from  $C_{\text{UNIT}}$ . Table II summarizes the relation between  $N_{\rm Ch}$ ,  $N_{\rm ADC,min}$ , and  $f_{\rm S,ADC}$ using (6) and (7), which corresponds to the power and  $C_{\text{UNIT}}$ area per channel of the ideal SAR ADC using (8) and (9), respectively. From Table II, we can find that  $P/N_{\rm Ch}$  becomes significant at  $N_{\rm Ch} > 127$ .

Data transmission overhead affects the choice of  $N_{\rm Ch}$ . The latest high data rate of bio-medical communication is 12 Mb/s [21], which can cover up to 1023 channels [ $f_{S,ADC}$  $(512 \text{ kHz}) \times [\text{Code state } (10 \text{ b}) + B_{\text{ADC}} (13 \text{ b})] = 11.8 \text{ Mb/s}].$ As a result, the maximum channel can be 1023, and the optimal number is 15-31 in terms of digitization and data transmission.

The orthogonal code set is stored in the lookup table (LUT) in OCC Gen., and the LUT size in OCC Gen. also becomes a significant overhead when it comes to higher  $N_{\rm Ch}$ . The area of LUT/ $N_{\rm Ch}$  is linearly proportional to  $N_{\rm Ch}$ . Considering the area of D flip-flop cell area of 75  $\mu$ m<sup>2</sup> in 0.18- $\mu$ m CMOS process,

Fig. 5. DC offset (OS) analysis of OCCIA.

$N_{\rm Ch}$  should be less than 26 to occupy 10% of 0.02 mm<sup>2</sup>, which is the state-of-the-art bio-signal SoC area/ $N_{Ch}$ .

Second, we analyze mismatch and the crosstalk depending on  $N_{\rm Ch}$ . Fig. 5 shows the OCCIA operation with chopping noise, the mismatch of the chopping switch, and the IA DC offset  $(OS_G)$ . The common centroid layout and  $1.5 \times$  larger than minimum sized chopping switch can minimize process mismatch. The digital sampling in the middle phase between the chopping transition can alleviate the chopping ripple noise; the DC offset from the IA  $(OS_G)$  will be reduced by the demodulation and average.

The IA output swing margin also contributes to the crosstalk; if the margin is too small, the output G(a + b)will be distorted, which results in crosstalk. Thus, a sufficient output swing margin should be set up considering  $OS_G$  on the top of the output signal G(a + b). From the analyses, we can conclude that  $N_{\rm Ch}$  of 15–31 is the optimal value, and we chose 15 in this design.

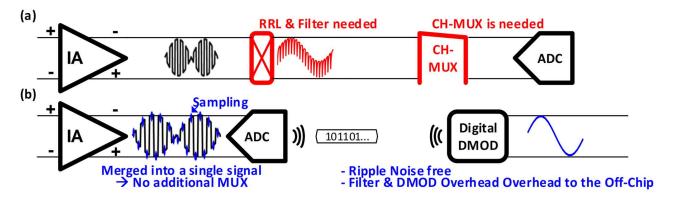

## D. Digitization Before Demodulation (DBD)

In terms of data communication, most bio-medical devices are preferred to have a single data communication channel via RF telemetry, inductive link, or ultrasound due to its area and power restriction [9], [22]-[24]. In order to use single-channel data communication, Conv. Chop and OFC demand channel multiplexer (CH-MUX) or signal encoder, which leads to additional power consumption and the increased chip area. Besides, the additional filter and the ripple reduction loop (RRL) are necessary to reduce ripple and glitch from the chopper that can distort the amplified signal. For example, Fan et al. [15] use RRL circuits that have two OTAs and several capacitors that need additional power and area. Chandrakumar and Markovic [16] have passive DC-blocking with 10-pF capacitor for ripple rejection, which results in the increasing area. The proposed DBD is applicable to solve such problems for low-power and area-efficient implantable applications; in conventional signal acquisition chain, digitization of the output signal is done after the analog demodulator and multiplexer for serialization as shown in Fig. 6. In contrast, OCCIA DBD scheme directly digitizes the amplified outputs prior to demodulation, thereby eliminating any need for analog

Fig. 6. Illustrations of (a) conventional demodulation system and (b) proposed DBD system.

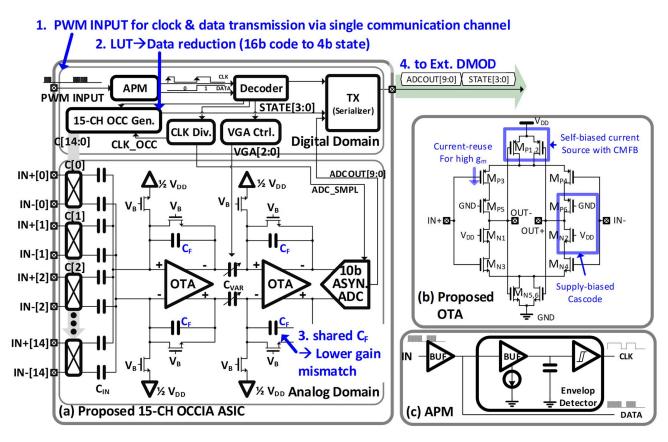

Fig. 7. (a) System block diagram. (b) Schematic of the self-biased fully differential OTA with current-reuse cascode. (c) Schematic of APM.

demodulators nor multiplexers. The ADC samples the outputs between chopping transitions, which significantly reduces the effect of chopping ripples. The direct merged data transmission to external demodulator relieves filter and demodulation overhead inside the chip, which results in power and area reduction.

#### III. CIRCUIT IMPLEMENTATIONS

Fig. 7 shows the overall system block diagram. As many implantable devices prefer to use a single communication channel such as an inductive link or an ultrasound (see [9], [22]–[24]), the proposed chip extracts the clock and the system parameters from the single incoming pulsewidth

modulated (PWM) programming data. The Decoder recognizes the number of pulses in 16 carrier clocks period to be DATA0, DATA1 as a parameter setting, and end-of-frame (EOF) as a protocol terminator; the distinct range of the number of pulses between DATA0, DATA1, and EOF can alleviate the communication error. PWM encoding has another benefit that it does not need additional clock synchronization circuitry consuming power. The amplifier programming module (APM) extracts the synchronized clock from the first rising edge of every pulse bursts. The current-controlled buffer and the Schmitt trigger enlarge the available carrier frequency by controlling charging speed, as shown in Fig. 7(c).

The orthogonal code generator generates one set of the OCC sequence (Walsh/Hadamard code) for each of the input

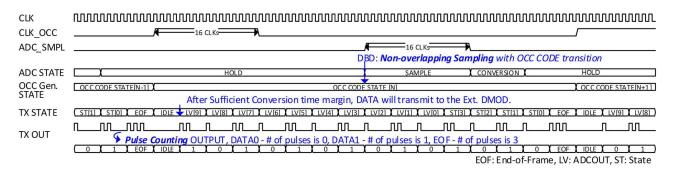

Fig. 8. Time waveform of the OCC Gen., ADC, and TX operations.

chopper switches via C[14:0]. LUT structure, synthesized by the automatically generated HDL, enables to send orthogonal 4-bit code state, instead of the entire 15-Ch. code itself.

The shared capacitive IA drastically reduces gain mismatch by sharing small feedback capacitor ( $C_F$  < 100 fF) that contributes to the gain due to PVT variation and layout. Depending on the bio-signal range, VGA uses a digitally controlled capacitor array to tune the gain delicately. Fig. 7(b) shows the self-biased fully differential OTA with currentreuse cascode, which achieves high gain and transconductance efficiency. Considering  $V_{\text{TH}}$  in 0.18- $\mu$ m process, the lower  $V_{\rm DD}$  of 1.2 V leads the proposed OTA to exploit the supplybias itself, hence do not need any additional bias circuitry. As a result, the proposed design achieves 10% reduction in area and power consumption [25]. The output swing margin becomes smaller with the power-and-area aggressive design. Considering the input voltage range [18], the proposed OTA is acceptable. Single NMOS pseudo-resistor with a bias voltage of  $V_B$  is used for control of cut-frequency and fast setup of bias voltage. The thermal input noise of the proposed IA  $(V_{N,\text{in}}^2)$  is expressed as

$$\overline{V_{N,\text{in}}^2} = 8KT\gamma/(g_{\text{MN3}} + g_{\text{MP3}})$$

(10)

where K is Boltzmann's constant, T is the temperature,  $\gamma$  is the coefficient, and  $g_{\text{MN3}}, g_{\text{MP3}}$  are the conductances of MN3 and MP3, respectively. From (3) and (5), integrated input noise ( $V_{N,\text{in,total}}$ ) can be calculated as

$$V_{N,\text{in,total}} = \sqrt{8KT\gamma/(g_{\text{MN3}} + g_{\text{MP3}}) \cdot \pi/2 \cdot \text{BW}}.$$

(11)

As multiplication of BW and  $g_{\rm MN3}+g_{\rm MP3}$  is constant, optimal power consumption and  $V_{N,\rm in,total}$  between Conv. Chop. IA and OCCIA would be similar.

The asynchronous ADC modified in [26] samples and digitizes the shared OTA output between chopping clock transitions (DBD) for ripple suppression. The asynchronous scheme does not need a system clock, which can help to reduce power consumption. Also, monotonic digitization is used for efficient power consumption [27]. The TX (serializer) merges the orthogonal 4-bit code state of each channel and the associated ADC output.

Fig. 8 shows the timing waveform of the OCC Gen., ADC, and TX operations. Clock divider (CLK Div.) generates  $64 \times$  slower the CLK\_OCC and ADC\_SMPL signals with the

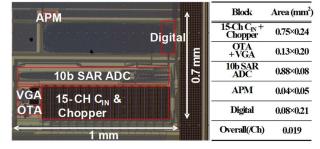

Fig. 9. Chip microphotograph.

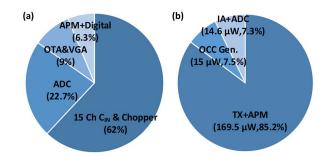

Fig. 10. (a) Area and (b) power breakdown.

synchronous CLK by the external device. OCC Gen. transits the code chopping set in the rising edge of CLK\_OCC. After 32 CLKs, ADC starts to sample the output of the IA. This gives a chance that IA has enough time to amplify the signal for the robust DBD. TX output uses pulse counting for the immune of phase noise. Since the external clock is much faster than the TX output, the TX output can be converted with a low error rate.

#### IV. MEASUREMENT RESULTS

The proposed 15-Ch. OCCIA was fabricated in a 1P6M 0.18- $\mu$ m CMOS, as shown in Fig. 9. As expected in Section II, 1-Ch.  $C_{\rm IN}$ , OTA occupy a similar area of 0.012 and 0.013 mm<sup>2</sup>, respectively [Fig. 10(a)]. Thanks to sharing an IA, VGA, and ADC among all 15 channels, the OCCIA occupies only 0.019 mm<sup>2</sup>/Ch. OCC Gen., IA, and ADC combined consume 29.6  $\mu$ W, which translates to 1.97  $\mu$ W/Ch. [Fig. 10(b)].

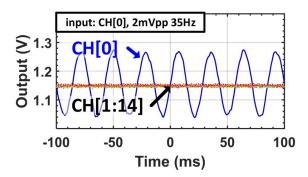

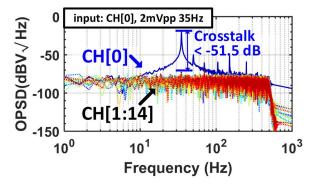

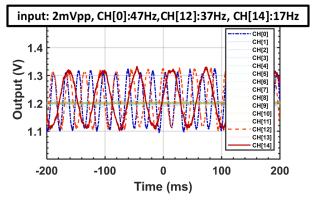

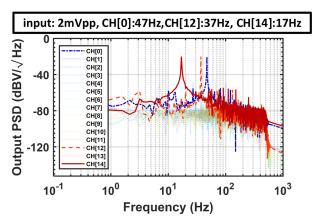

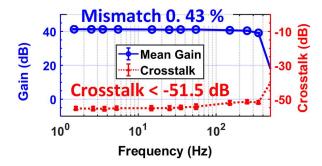

The demodulated output with a single-channel input (CH [0]) can be seen in Fig. 11 and Fig. 12. Crosstalk of 51.5 dB was measured when CH [0] inputs sinusoidal signal

Fig. 11. Transient response of output amplitude.

Fig. 12. Output power spectrum density (crosstalk < -51.5 dB).

Fig. 13. Transient response of output amplitude with response to 3-Ch inputs.

with a frequency of 35 Hz. To see the crosstalk, the demodulated output was measured with 3-Ch. input, as shown in Figs. 13 and 14. The spectrum shows that no harmonics interference was observed in OCC due to the spread effect. Fig. 15 summarizes the mean amplitude and signal crosstalk of all the channels with each same input stimuli. The GBP curve shows the BW of 490 Hz and its low mismatch (0.43%) with 8th IIR low-pass filter; while the power-aggressive design of the OCCIA with finite linearity leads to limited crosstalk of -51.5 dB, this still satisfies the crosstalk criteria [10] with a sufficient margin at 15 Ch. As the demodulation can be operated in the digital domain, the output noise floor is estimated from the demodulated signals containing ADC and demodulation noise, instead of using the conventional method (e.g., dynamic signal analyzer).

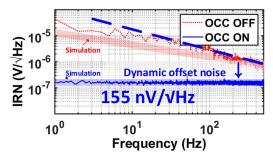

Fig. 16 shows the measured input noise density with ADC and demodulation dynamic offset noise when OCC is

Fig. 14. Output spectrums of 3-Ch inputs.

Fig. 15. Mean gain and crosstalk variance of all channels.

Fig. 16. Input referred noise curve with OCC ON/OFF.

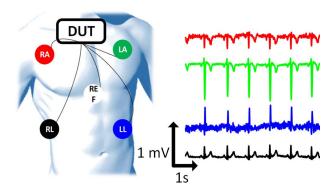

Fig. 17. Multi-channel ECG measurements.

activated. The dynamic offset noise in the low frequency is significantly reduced with the OCC activation. Measured input noise density is 155 nV/ $\sqrt{Hz}$ , including ADC and the off-chip OCC demodulator noise. Multi-channel ECG is also measured with OCCIA for an example of bio-signal

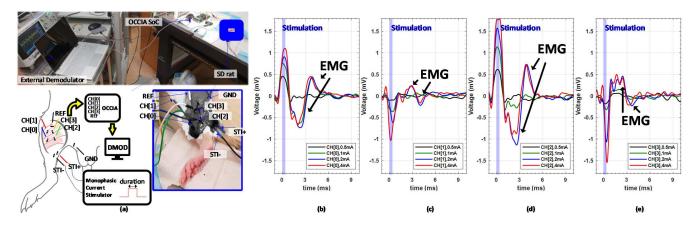

Fig. 18. Multi-channel EMG measurement. (a) Test configuration, and its results depending on the stimulus amplitude of (b) CH [0], (c) CH [1], (d) CH [2], and (e) CH [3].

TABLE III

PERFORMANCE COMPARISON

|                           | This<br>Work                 | Q. Fan<br>JSSC'11 [15] | Y. Tsai,<br>ISSCC'15 [17] | F. Michel,<br>ISSCC'12 [30] | R. Muller,<br>JSSC'15[9] | C. Lopez,<br>JSSC'14 [8]   | V.Majidzadeh,<br>TBCAS'11 [10] |

|---------------------------|------------------------------|------------------------|---------------------------|-----------------------------|--------------------------|----------------------------|--------------------------------|

| Methodology               | осс                          | Conv.<br>Chop.         | OFC                       | R-trim<br>feedback          | ChopΔΣ<br>rawData        | ACT Electrode<br>AC-couple | Ref.<br>Shared                 |

| Area /Ch. (mm²)           | $0.019^{A}$                  | $0.1^{B}$              | $0.031^{B}$               | $0.465^{B}$                 | 0.025 <sup>C</sup>       | $0.022^{\rm D}$            | $0.063^{B}$                    |

| Power/Ch. (µW)            | 1.97 <sup>A</sup>            | $1.8^{B}$              | $40.5^{B}$                | $25.2^{B}$                  | $2.29^{\circ}$           | $7.02^{\circ}$             | $7.92^{B}$                     |

| Max. gain<br>mismatch (%) | 0.43(15-Ch.) <sup>E</sup>    | -                      | 0.55(2-Ch.)               | 0.70                        | 15.0                     | -                          | -                              |

| N. of Ch.                 | 15                           | 1                      | 2                         | 1                           | 64                       | 455                        | 4                              |

| Crosstalk (dB)            | -51.5                        | -                      | -83.2                     | -                           | -85.0                    | -44.8                      | -43.5                          |

| Supply (V)                | 1.2(analog)<br>/1.5(digital) | 1                      | 3                         | 1.2                         | 0.5                      | 1.8                        | 1.8                            |

| Ch gain (dB)              | 40-56                        | 40                     | 40                        | 20-60                       | 30                       | 29.5-72                    | 39.4                           |

| Bandwidth (BW)            | 490                          | 0.1-500                | 1k                        | 1k-100k                     | 500                      | 0.2,6k                     | 7.2k                           |

| Noise density<br>(nV/√Hz) | 155 <sup>F</sup>             | 60                     | 26.0B                     | 40.0                        | 58.0                     | $41.3^{G}$                 | $39.4^{G}$                     |

| NEF                       | $7.25^{\rm F}$               | $3.3^{\mathrm{B}}$     | $3.74^{\mathrm{B}}$       | $7.50^{B}$                  | 4.76 <sup>C</sup>        | $3.08^{\mathrm{B}}$        | $3.35^{B}$                     |

| Process (nm)              | 180                          | 65                     | 350                       | 130                         | 65                       | 180                        | 180                            |

- A. IA+ADC+OCC Gen.

- B. IA

- C. IA+ADC

- D. Estimated by merging of IA and Electrode

- F. Noise of IA+ADC+Demodulator, current from IA+ADC+OCC Gen.

- E. Mismatch includes ADC + Demodulation error.

- G. Estimated from IRN and BW with assumption of constant noise density.

acquisition, as shown in Fig. 17. Depending on the electrodes' position, 4-Ch. ECG shows the proper amplitude and its plus and minus sign. Fig. 18 shows the multi-channel electrically evoked subcutaneous EMG measurement from anesthetic SD rat's left leg using isoflurane. Depending on the electrodes' position Fig. 18(a), each channel shows the EMG within 5 ms after an artifact that is proportional to monophasic stimulus current amplitude with a duration of 200  $\mu$ s [Fig. 18(b)–(e)]. Chip performances are summarized in Table III, which shows that OCC achieves the smallest area, lowest power, and low gain mismatch among recent multi-channel chopping IAs.

#### V. DISCUSSION

The measurement results verify the proposed OCC scheme principle. By combining orthogonal code modulator [19] and multi-frequency chopping stabilizations [14], the proposed OCC successfully achieves: 1) low-frequency noise reduction; 2) small area, and low-power consumption by sharing an IA and an ADC; and 3) eliminates the demodulator for data transmission.

The proposed OCCIA modulates 15-Ch. inputs into a single channel, where the output voltage swing margin in the IA must be carefully considered. Hence, Ouh and Johnston [29] propose a current-based CDMA encoding scheme in the optical application to use CDM benefits without the output voltage swing margin issue. However, this results in excessive power consumption as the number of channels increases (to keep the same noise contribution of IA). On the contrary, the OCCIA uses a voltage-based amplifier that has strength in terms of noise and power trade-off. The output voltage swing margin issue is negligible due to the small input bio-signals below 5 mV and the concurrent activation. The VGA solves the output voltage swing margin issue by changing the gain. Also, the VGA compensates for the additional dynamic range loss of  $\log_2 \sqrt{N}$  [19] with a combination of the over-sampling and average schemes of the demodulator.

Area of the OCCIA, including IA, OCC Gen., and ADC, is 0.019 mm<sup>2</sup>/Ch., which is the smallest among recent works shown in Table III. The power consumption is 1.97  $\mu$ W/Ch., which is the lowest as well. Also, it shows the lowest gain mismatch of 0.43% among 15 channels, which is superior over

other IA schemes thanks to the shared  $C_F$  and the single IA. Capacitive feedback structure enables IA to have flat gain in the OCC operating range, which reduces the gain mismatch from frequency-variant modulation.

#### VI. CONCLUSION

The proposed OCCIA with DBD shares an IA and an ADC among all the channels with competitive chopping speed, and it also pushes the demodulator overhead from the chip, which further reduces power, area, and noise. This is especially helpful in multi-channel implantable applications. The proposed OCCIA in 1P6M  $0.18-\mu m$  CMOS, when compared with the recent multi-channel IAs, successfully verifies one of the smallest area (0.019 mm²/Ch.) and power consumption (1.97  $\mu$ W/Ch.), with a low gain mismatch (0.43%) and the crosstalk (< -51.5 dB) at 490-Hz BW.

#### REFERENCES

- [1] D. S. Jones, S. H. Podolsky, and J. A. Greene, "The burden of disease and the changing task of medicine," *New England J. Med.*, vol. 366, no. 25, pp. 2333–2338, Jun. 2012.

- [2] M. Nei et al., "EEG and ECG in sudden unexplained death in epilepsy," Epilepsia, vol. 45, no. 4, pp. 338–345, Apr. 2004.

- [3] K. van der Hiele et al., "EEG markers of future cognitive performance in the elderly," J. Clin. Neurophysiol., vol. 25, no. 2, pp. 83–89, Apr. 2008.

- [4] M. A. Bin Altaf, C. Zhang, and J. Yoo, "A 16-channel patient-specific seizure onset and termination detection SoC with impedance-adaptive transcranial electrical stimulator," *IEEE J. Solid-State Circuits*, vol. 50, no. 11, pp. 2728–2740, Nov. 2015.

- [5] J.-P. Lachaux, N. Axmacher, F. Mormann, E. Halgren, and N. E. Crone, "High-frequency neural activity and human cognition: Past, present and possible future of intracranial EEG research," *Prog. Neurobiol.*, vol. 98, no. 3, pp. 279–301, Sep. 2012.

- [6] M. A. Lebedev and M. A. L. Nicolelis, "Brain-machine interfaces: Past, present and future," *Trends Neurosci.*, vol. 29, no. 9, pp. 536–546, Sep. 2006.

- [7] R. R. Harrison and C. Charles, "A low-power low-noise CMOS amplifier for neural recording applications," *IEEE J. Solid-State Circuits*, vol. 38, no. 6, pp. 958–965, Jun. 2003.

- [8] C. M. Lopez et al., "An implantable 455-Active-Electrode 52-channel CMOS neural probe," *IEEE J. Solid-State Circuits*, vol. 49, no. 1, pp. 248–261, Jan. 2014.

- [9] R. Muller *et al.*, "A minimally invasive 64-channel wireless μECoG implant," *IEEE J. Solid-State Circuits*, vol. 50, no. 1, pp. 344–359, Jan. 2015.

- [10] V. Majidzadeh, A. Schmid, and Y. Leblebici, "Energy efficient low-noise neural recording amplifier with enhanced noise efficiency factor," *IEEE Trans. Biomed. Circuits Syst.*, vol. 5, no. 3, pp. 262–271, Jun. 2011.

- [11] A. Zhou *et al.*, "A wireless and artefact-free 128-channel neuromodulation device for closed-loop stimulation and recording in non-human primates," *Nature Biomed. Eng.*, vol. 3, pp. 15–26, Dec. 2019.

- [12] W. Biederman et al., "A 4.78 mm 2 fully-integrated neuromodulation SoC combining 64 acquisition channels with digital compression and simultaneous dual stimulation," *IEEE J. Solid-State Circuits*, vol. 50, no. 4, pp. 1038–1047, Apr. 2015.

- [13] J. H. Park, T. Tang, L. Zhang, K. A. Ng, and J. Yoo, "A 15-Ch. 0.019 mm<sup>2</sup>/Ch. 0.43% gain mismatch orthogonal code chopping instrumentation amplifier SoC for bio-signal acquisition," in *Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC)*, Nov. 2019, pp. 295–296.

- [14] C. C. Enz and G. C. Temes, "Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization," *Proc. IEEE*, vol. 84, no. 11, pp. 1584–1614, Nov. 1996.

- [15] Q. Fan, F. Sebastiano, J. H. Huijsing, and K. A. A. Makinwa, "A 1.8 μW 60 nV/√ Hz capacitively-coupled chopper instrumentation amplifier in 65 nm CMOS for wireless sensor nodes," *IEEE J. Solid-State Circuits*, vol. 46, no. 7, pp. 1534–1543, Jul. 2011.

- [16] H. Chandrakumar and D. Markovic, "A high dynamic-range neural recording chopper amplifier for simultaneous neural recording and stimulation," *IEEE J. Solid-State Circuits*, vol. 52, no. 3, pp. 645–656, Mar. 2017.

- [17] Y. Tsai, F. Lee, T. Chen, and T. Lin, "A 2-Channel-83.2dB crosstalk 0.061 mm2 CCIA with an orthogonal frequency chopping technique," in *IEEE ISSCC Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 2015, pp. 92–94.

- [18] H. Toda, T. Suzuki, H. Sawahata, K. Majima, Y. Kamitani, and I. Hasegawa, "Simultaneous recording of ECoG and intracortical neuronal activity using a flexible multichannel electrode-mesh in visual cortex," *NeuroImage*, vol. 54, no. 1, pp. 203–212, Jan. 2011.

- [19] V. Majidzadeh, A. Schmid, and Y. Leblebici, "A 16-channel, 359 μW, parallel neural recording system using Walsh-Hadamard coding," in *Proc. IEEE Custom Integr. Circuits Conf.*, Sep. 2013, vol. 2, no. 4, pp. 3–6.

- [20] B. Murmann. ADC Performance Survey 1997-2019. [Online]. Available: http://web.stanford.edu/~murmann/adcsurvey.html

- [21] E. Y. Chow, A. Kahn, and P. P. Irazoqui, "High data-rate 6.7 GHz wireless ASIC transmitter for neural prostheses," in *Proc. 29th Annu. Int. Conf. IEEE Eng. Med. Biol. Soc.*, Aug. 2007, pp. 6581–6584.

- [22] R. R. Harrison et al., "Wireless neural recording with single low-power integrated circuit," *IEEE Trans. Neural Syst. Rehabil. Eng.*, vol. 17, no. 4, pp. 322–329, Aug. 2009.

- [23] D. Jiang, D. Cirmirakis, M. Schormans, T. A. Perkins, N. Donaldson, and A. Demosthenous, "An integrated passive phase-shift keying modulator for biomedical implants with power telemetry over a single inductive link," *IEEE Trans. Biomed. Circuits Syst.*, vol. 11, no. 1, pp. 64–77, Feb. 2017.

- [24] M. M. Ghanbari et al., "A 0.8 mm<sup>3</sup> ultrasonic implantable wireless neural recording system with linear AM backscattering," in *IEEE ISSCC Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 2019, pp. 284–286.

- [25] J. M. Lee et al., "A 29 nW bandgap reference circuit," in IEEE ISSCC Dig. Tech. Papers, San Francisco, CA, USA, Feb. 2015, pp. 100–101.

- [26] P. J. A. Harpe et al., "A 26 μW 8 bit 10 MSPS asynchronous SAR ADC for low energy radios," *IEEE J. Solid-State Circuits*, vol. 46, no. 7, pp. 1585–1595, Jul. 2011.

- [27] C.-C. Liu, S.-J. Chang, G.-Y. Huang, and Y.-Z. Lin, "A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure," *IEEE J. Solid-State Circuits*, vol. 45, no. 4, pp. 731–740, Apr. 2010.

- [28] S. Kwan An et al., "Design for a simplified cochlear implant system," IEEE Trans. Biomed. Eng., vol. 54, no. 6, pp. 973–982, Jun. 2007.

- [29] H. Ouh and M. L. Johnston, "Code-division multiplex encoding analog front end for current-mode sensor arrays," *IEEE Solid-State Circuits Lett.*, vol. 1, no. 5, pp. 118–121, May 2018.

- [30] F. Michel and M. Steyaert, "On-chip gain reconfigurable 1.2V 24μW chopping instrumentation amplifier with automatic resistor matching in 0.13μm CMOS," in *IEEE ISSCC Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 2012, pp. 372–373.

**Jeong Hoan Park** (Member, IEEE) received the B.S. and Ph.D. degrees from the School of Electrical Engineering and Computer Science, Seoul National University, Seoul, South Korea, in 2011 and 2017, respectively.

He is currently a Research Fellow with the Department of Electrical and Computer Engineering, National University of Singapore, Singapore. His main research topic is the development of low-power and low-noise multi-channel bio-signal acquisition and the neural prosthesis with neuromorphic processing System-on-Chip (SoC).

Tao Tang (Member, IEEE) received the B.S. degree in electrical engineering from Wuhan University, Wuhan, China, in 2012, the M.S. and Ph.D. degrees in electrical engineering from Nanyang Technological University, Singapore, in 2013 and 2018, respectively.

From 2012 to 2017, he was an Attached Research Student with the Institute of Microelectronics (IME), Agency for Science, Technology and Research (A\*STAR), Singapore. He has been a Research Fellow with the National University of Singapore

since 2017. His research interests include low-noise, high performance readout circuit and system for bio-medical applications, and brain-machine interfaces.

Lian Zhang (Student Member, IEEE) received the B.E. degree from the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore, in 2016. She is currently pursuing the Ph.D. degree with the Department of Electrical and Computer Engineering, National University of Singapore, Singapore.

Her research focuses on low power and low noise analog instrumentation, area efficient data conversion, and mixed signal system implementation for bio-medical applications.

Kian Ann Ng (Senior Member, IEEE) received the B.E. degree in electrical and electronic engineering and the M.E. degree in IC design from Nanyang Technological University, Singapore, in 2000 and 2005, respectively, and the Ph.D. degree from the National University of Singapore, Singapore, in 2015

From 2000 to 2009, he has held senior technical positions with the following companies: STMicroelectronics, Chartered Semiconductor Manufacturing, and Oxford Semiconductors. He has designed

EEG/ECG mixed-signal front ends, switched-capacitor circuits, RF identification circuits, image sensors, ESD/IO circuits, USB(1.0–3.0) SERDES, and Firewire SERDES. He is currently a Research Fellow with the National University of Singapore. He has authored or coauthored over 30 technical articles and holds 5 U.S. patents. His main research focuses on analog IC and system design, implantable neural recording systems and peripheral nerve prosthesis.

Dr. Ng is an Active Committee Member of the IEEE Solid-State circuits Society (Singapore Chapter).

Gil Gerald Lasam Gammad received the Doctor of Veterinary Medicine (DVM) degree from the University of the Philippines, Los Baños (UPLB), Philippines.

From 2009 to 2015, he had extensive work experience in the field of laboratory animals with Maccine Pte Ltd and Innoheart Pte Ltd. He is currently a Laboratory Technologist with the National University of Singapore (NUS). The assigned duties include surgeries involving device implantation in rodent and Non-human primates, providing surgical training to

research staff, assisting Principal Investigator in submission and amendment of research protocol, and ensuring regulatory compliance.

**Shih-Cheng Yen** received the B.S.E., M.S.E., and Ph.D. degrees from the Department of Bioengineering, University of Pennsylvania, Philadelphia, PA, USA, in 1993 and 1998, respectively.

For his Ph.D., he worked on neural network models of the primary visual cortex. He then spent several years performing single-neuron recordings in the primary visual cortex of both anesthetized cats and awake, behaving non-human primates, first at the University of California, Davis, CA, USA, and subsequently at Montana State University, Bozeman,

MT, USA. He is currently with the Innovation and Design Programme, Faculty of Engineering, N.1 Institute for Health, National University of Singapore (NUS), Singapore. His research interests are in neural coding and neuroprosthetics.

**Jerald Yoo** (Senior Member, IEEE) received the B.S., M.S., and Ph.D. degrees from the Department of Electrical Engineering, Korea Advanced Institute of Science and Technology (KAIST), Daejeon, South Korea, in 2002, 2007, and 2010, respectively.

From 2010 to 2016, he was with the Department of Electrical Engineering and Computer Science, Masdar Institute, Abu Dhabi, United Arab Emirates, where he was an Associate Professor. From 2010 to 2011, he was a Visiting Scholar with Microsystems Technology Laboratories (MTL),

Massachusetts Institute of Technology (MIT), Cambridge, MA, USA. Since 2017, he has been with the Department of Electrical and Computer Engineering, National University of Singapore, Singapore, where he is currently an Associate Professor. He has pioneered researches on low-energy body-area-network (BAN) for communication/powering and wearable body sensor networks using the planar-fashionable circuit board for a continuous health monitoring system. He authored book chapters in the *Bio-Medical CMOS ICs* (Springer, 2010), the *Enabling the Internet of Things—From Circuits to Networks* (Springer, 2017), and *The IoT Physical Layer* (Springer, 2019). His current research interests include low-energy circuit technology for wearable bio-signal sensors, flexible circuit board platform, BAN communication and powering, ASIC for piezoelectric micromachined ultrasonic transducers (pMUT), and system-on-chip (SoC) design to system realization for wearable healthcare applications.

Dr. Yoo is a Distinguished Lecturer of the IEEE Circuits and Systems Society (CASS) (2019-2020). He also served as the Distinguished Lecturer for the IEEE Solid-State Circuits Society (SSCS) (2017–2018). He was a recipient or a co-recipient of several awards: the IEEE International Symposium on Circuits and Systems (ISCAS) 2015 Best Paper Award (BioCAS Track), the ISCAS 2015 Runner-Up Best Student Paper Award, the Masdar Institute Best Research Award in 2015, and the IEEE Asian Solid-State Circuits Conference (A-SSCC) Outstanding Design Award (2005). He was a Vice-Chair of the IEEE SSCS United Arab Emirates (UAE) Chapter. He currently serves as a Technical Program Committee Member for the IEEE International Solid-State Circuits Conference (ISSCC), ISSCC Student Research Preview (Co-Chair), IEEE Custom Integrated Circuits Conference (CICC, Emerging Technologies Subcommittee Chair), and IEEE Asian Solid-State Circuits Conference (A-SSCC, Emerging Technologies and Applications Subcommittee Chair). He is also an Analog Signal Processing Technical Committee Member of the IEEE Circuits and Systems Society.