# In<sub>0.52</sub>Al<sub>0.48</sub>As Based Single Photon Avalanche Diodes With Stepped E-Field in Multiplication Layers and High Efficiency Beyond 60%

Yi-Shan Lee , Yan-Min Liao, Ping-Li Wu, Chi-En Chen, Yu-Jie Teng, Yu-Ying Hung, and Jin-Wei Shi , Senior Member, IEEE

Abstract—We carry out an In<sub>0.53</sub>Ga<sub>0.47</sub>As/In<sub>0.52</sub>Al<sub>0.48</sub>As single photon avalanche diode which exhibits a single photon detection efficiency exceeding 60% at 1310 nm and neat temporal characteristic of 65 ps. A novel concept of dual multiplication layer is incorporated to avoid the tradeoff between dark count rate, afterpulsing and timing jitter, paving the possibility to improve the overall performance of a single photon detector. Based on this elevated device structure, we further optimize the detection efficiency and timing jitter by employing a delicate mesa structure to better confine the electric field distribution within the central multiplication region. For our detector operated under gated mode, a shorten gate width together with an increase of excess bias percentage leads to a significant improvement in the detection performance. We eventually achieve a single photon detection efficiency of 61.4% without the involvement of afterpulsing at the gating frequency of 10 kHz for 200 K.

Index Terms—Single photon avalanche diode, photon detection efficiency, timing jitter.

## I. INTRODUCTION

INCE single photon detector (SPD) offers the ultimate sensitivity, it facilitates the fast development of quantum information technologies [1]. Variety of applications such as light detection and ranging (LiDAR) and time-resolved single molecule spectroscopy also benefits from the supreme sensitivity and picosecond temporal response of SPD [2], [3]. Single photon avalanche diode (SPAD) stands out among other SPDs thanks to the advantages of their compactness, cryogenic-free operation and low cost. Extending the spectral range to shortwave infrared (SWIR) region provide the compatibility of SPAD with fiber-based applications and also permit higher optical

Manuscript received June 2, 2021; revised September 6, 2021; accepted September 17, 2021. Date of publication September 21, 2021; date of current version October 6, 2021. This work was supported in part by the Ministry of Science and Technology, Taiwan (MOST) under Grants 109-2622-E-008-010-CC2, 109-2627-M-008-001, 109-2221-E-008-025, and 110-2221-E-008-098. (Corresponding authors: Jin-Wei Shi; Yi-Shan Lee.)

Yi-Shan Lee, Yan-Min Liao, Ping-Li Wu, Chi-En Chen, Yu-Jie Teng, and Jin-Wei Shi are with the Department of Electrical Engineering, National Central University, Taoyuan 320, Taiwan (e-mail: queenalee@ee.ncu.edu. tw; 108521014@cc.ncu.edu.tw; 105501509@cc.ncu.edu.tw; 107501539@ cc.ncu.edu.tw: 107501504@cc.ncu.edu.tw: jwshi@ee.ncu.edu.tw).

Yu-Ying Hung is with the College of Science Joint Science Program, National Central University, Taoyuan 320, Taiwan (e-mail: 107208501@cc.ncu.edu.tw). Color versions of one or more figures in this article are available at

Digital Object Identifier 10.1109/JSTQE.2021.3114130

https://doi.org/10.1109/JSTQE.2021.3114130.

power at eye-safety threshold for the LiDAR applications. The single photon detection performance of SPAD is characterized by several figure of merits, dark count rate (DCR), single photon detection efficiency (SPDE), maximum count rate, afterpulsing probability and timing jitter. SPADs of high SPDE and low DCR are especially favored in numbers of applications such as quantum key distribution and a range of time-correlated single photon counting (TCSPC) measurements. In the SWIR region, compared with In<sub>0.53</sub>Ga<sub>0.47</sub>As/In<sub>0.52</sub>Al<sub>0.48</sub>As SPADs, the In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP SPADs have received more research interests over the past decade due to the improved epitaxy and fabrication techniques [4–9]. However, In<sub>0.52</sub>Al<sub>0.48</sub>As-based APDs are increasingly being studied instead of InP-based APDs as they exhibit superior performance due to the large difference between the electron and hole ionization coefficients which contributes to a low excess noise, high gain-bandwidth product and better sensitivity upon In<sub>0.52</sub>Al<sub>0.48</sub>As-based APD. Moreover, in light of larger bandgap, high-electron mobility and less temperature dependence of ionization coefficient ratio, the detection performance of In<sub>0.53</sub>Ga<sub>0.47</sub>As/In<sub>0.52</sub>Al<sub>0.48</sub>As SPAD can be improved in terms of breakdown, temporal and temperature characteristics, which appears to be the next choice for the upcoming decade of solid-state SPD development [10–13].

The first In<sub>0.53</sub>Ga<sub>0.47</sub>As/In<sub>0.52</sub>Al<sub>0.48</sub>As SPAD was reported by Karve et al. [14]. They have demonstrated a SPAD with SPDE of 16% at 130 K. Nakata et al. further improved the overall performance with SPDE of 10% at 213 K [15]. In addition, Zhao et al. has designed an In<sub>0.53</sub>Ga<sub>0.47</sub>As/In<sub>0.52</sub>Al<sub>0.48</sub>As SPAD with SPDE of 6% and 14% at respective 240 K and 120 K based on the self-quenching and self-recovering mechanism [16]. More recently, Meng et al. demonstrated a mesa-type  $In_{0.53}Ga_{0.47}As/In_{0.52}Al_{0.48}As$  SPAD with SPDE of 21% at 260 K [17]. By further increasing the thickness of absorption and multiplication layer to the respective thickness of 1700 nm and 1000 nm, they achieved SPDE of 26% and DCR of 100 MHz at 210 K [18]. Very recently, Zhang et al. incorporated a triple mesa structure to suppress the surface leakage current, achieving SPDE of 35% and DCR of 33 MHz at 240 K [19]. However, for the above reported In<sub>0.52</sub>Al<sub>0.48</sub>As -based SPADs, the DCRs remain several orders higher compared with the InP-based SPADs. It is the tunneling current from the In<sub>0.52</sub>Al<sub>0.48</sub>As multiplication layer that hinders the efficient DCR suppression during cooling. In order to reduce the tunneling current, the thickness of multiplication layer should be increased to avoid the direct-tunneling generation. However, with thicker multiplication layer, the accompanying issues of broadened temporal distribution and afterpulsing effect emerge.

By incorporating a unique structure design, our previous report on In<sub>0.53</sub>Ga<sub>0.47</sub>As/In<sub>0.52</sub>Al<sub>0.48</sub>As SPAD, which consists of a dual multiplication layer with an overall thickness of 500 nm, have achieved the best SPDE of 32% and 26% respectively at 187.5 K and room temperature with a moderate DCR of 200 MHz and 5 MHz [20], though it still falls behind the superb SPDE exceeding 60% from recently reported InGaAs/InP SPADs [21–23]. In our previous work, the DCR originated from the high periphery electric field existing at the etched sidewall is the main obstacle to achieve higher SPDE. Therefore, in this work, we modify the mesa structure in order to reduce the periphery electric field and have stronger confinement of the high electric field within the center of active mesa. Meanwhile, we shorten the gate width to reduce the DCR and hence avoid the count rate saturation when the excess bias is further raised to boost the SPDE. By combining the above improvement in fabrication and gate operation, we achieve SPDE as high as 61.4%, which is, to our knowledge, the best among the reported In0.53Ga0.47As/In0.52Al0.48As SPADs at 1310 nm and comparable to the reported In0.53Ga0.47As/InP SPADs at 1550 nm for the same thickness of 2- $\mu$ m InGaAs absorption layer. Such high SPDE is obtained at the cost of relatively high DCR performance. Based on our current structure with high responsivity (larger than 1 A/W), the applications using time-gated strategy is ambitiously envisioned for that the synchronization of the gated signal of SPAD with incoming single-photon data stream can mitigate the problem of high DCR in our device [24].

### II. STRUCTURE DESIGN AND EXPERIMENTAL DETAILS

The avalanche triggering probability highly depends on the multiplication region width, electric field, excess bias and temperature. Thicker multiplication region can increase the avalanche triggering probability and reduce the DCR, but at the cost of poor temporal and speed performance. When the thickness of multiplication layer is reduced to improve the temporal characteristic and operation speed of SPAD, the tunneling effect and dead space effect become more pronounced [9]. The avalanche triggering probability increases faster with excess bias ratio when the dead space occupies a larger fraction of the multiplication region width [25], however, the tunneling generation also begins to dominate the bulk current prior to the avalanche breakdown, imposing an upper limit on the bias voltage range for the SPAD with thin multiplication layer [10].

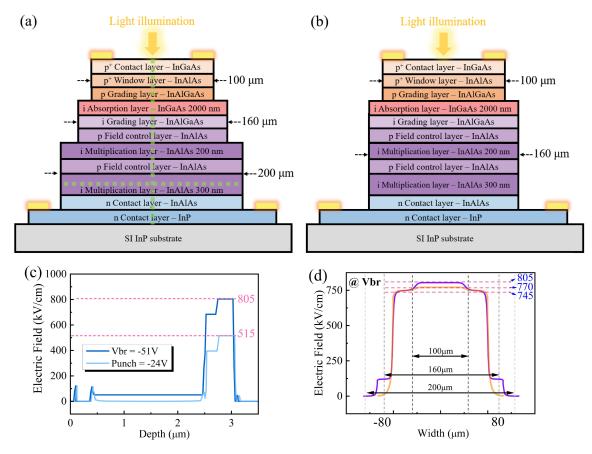

Our design concept aims at circumventing the trade-off between DCR induced by tunneling generation, afterpulsing (maximum count rate) and timing jitter. Therefore, we propose a SPAD structure with a relatively thin multiplication layer as compared to a normal SPAD structure which usually consists of at least 1000-nm-thick multiplication layer. The layer structure of our SPAD device is detailed in Fig. 1(a). The wafer was grown by molecular beam epitaxy (MBE) on a semi-insulating InP substrate. A 2000-nm-thick absorption layer is

designed for increasing the photon absorption efficiency. Two grading layers are used to reduce the carrier accumulation at the abrupt In<sub>0.53</sub>Ga<sub>0.47</sub>As/In<sub>0.52</sub>Al<sub>0.48</sub>As heterojunctions. The doping concentration of top field control layer is properly chosen to ensure a low but high enough electric field strength in the absorption layer for drifting the photogenerated carriers to the multiplication layer. With inserting an additional bottom field control layer, a 500-nm-thick multiplication layer in a conventional separate absorption, grading, charge and multiplication (SAGCM) structure is partitioned into a 200-nm-thick top multiplication layer and a 300-nm-thick bottom multiplication layer. A stepwise electric field distribution in the growth direction is thus formed in the multiplication layer as shown in Fig. 1(b), where the electric field distribution is calculated by using the Silvaco Technology Computer Aided Design (TCAD) tools. The electric field strength in the top multiplication layer with the thickness of 200 nm, which has not reached the threshold of impact ionization, will energize and accelerate the carriers to the bottom multiplication layer. The carriers entering the bottom multiplication layer with the thickness of 300 nm will trigger subsequent impact ionizations, creating a self-sustaining avalanche. The top multiplication layer in our design can act to build up the initial energy of all the carriers and align them at the same starting point, which in principle can minimize the dead space effect and maintain the applied bias voltage range while reducing the thickness of multiplication layer.

Based on our previous work, this design has been proven to provide an excellent timing performance with considerable improvement in the DCR as compared with other reported In<sub>0.52</sub>Al<sub>0.48</sub>As SPADs [20]. We continue to put effort on the optimization of SPAD performance from the aspect of fabrication processes. As mentioned previously, since the avalanche triggering probability depends on the electric field distribution, we incorporate a quadruple mesa configuration to better confine the high electric field within the central active multiplication region. The etching profile for the quadruple and triple mesa is illustrated respectively by Fig. 1(a) and (b). The photo-active area with the diameter of 60  $\mu m$  is defined by the first mesa with the diameter of 100  $\mu$ m and surrounded by the second and third mesa with the diameter of respective 160  $\mu$ m and 200  $\mu$ m. The lateral electric field distribution of bottom multiplication region for the quadruple and triple mesa is calculated and shown in Fig. 1(c). As can be seen, the additional second mesa in quadruple mesa device, which is etched through the first field control (charge) layer and stops at first multiplication layer, can more effectively constrain the E-field below it [26], [27]. We can clearly see from Fig. 1(d), as expected, that the electric field reduces from 750 to 90 kV/cm at the sidewall of the second multiplication layer in the quadruple mesa device. The much smaller electric field strength in the edge of multiplication region than that of the triple mesa one can prevent the edge breakdown by well-concentrating the high field region below the first active

The mesa etching was performed by using plasma dry etching, which is composed of  $CH_4$  and  $O_2$  gas. Since the aluminum based alloy has slower etching rate, the etching depth can be precisely controlled, which ensures a perfect etching stop at first M-layer.

Fig. 1. Illustration of layer structure and etching profile for InGaAs/InAlAs SPAD with (a) quadruple mesa structure and (b) triple mesa structure. (c) Electric field profile at punch through and breakdown voltage along the vertical growth direction as indicated by the longitudinal green dashed line in (a). (d) Lateral electric field profile at the second (bottom) multiplication layer (along the transverse green dashed line in (a)) for triple (orange) and quadruple (purple) mesa structures.

After mesa etching, the surface sidewall was treated with ammonium sulfide and followed by a polyimide passivation. Ni-Ge-Au and Ti-Au were used as the Ohmic contact metal for n<sup>+</sup>-InP and p<sup>+</sup>-InGaAs layer. The contacts were deposited by e-beam evaporation and alloyed by rapid thermal annealing. In order to optimize the quantum efficiency, a final antireflection coating targeted at 1310 nm was deposited on the top of the active window.

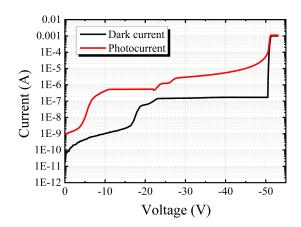

The dark and illuminated current-voltage characteristics of our  $In_{0.53}Ga_{0.47}As/In_{0.52}Al_{0.48}As$  SPAD with specific design are shown in Fig. 2. The punch-through and breakdown voltages are obtained to be respectively 24 V and 51 V, where the breakdown voltage is defined at a dark current of 10  $\mu$ A. A lensed fiber laser with spot size of 2.6  $\mu$ m and the wavelength of 1550 nm is used to illuminate the SPAD device. Under the pump power of 1  $\mu$ W, a maximum responsivity of 1.12 A/W at unity gain is achieved, corresponding to an external quantum efficiency (EQE) exceeding 100%, which suggests that all the absorbed photons are detected. Therefore, under the estimated EQE and optimized conditions, we can anticipate that the maximum achievable SPDE approaches 100%. The temperature dependency of the breakdown voltage is 51 mV / K, about half of that obtained from  $In_{0.53}Ga_{0.47}As/InP$  SPADs [22].

The SPAD is operated under a gated mode with a passive quenching circuit. The applied voltage is composed of a dc component and a gated electrical pulse. The constant dc voltage

Fig. 2. Dark and illuminated current-voltage characteristics of mesa-type InGaAs/InAlAs SPAD. The SPAD was illuminated with an optical power of  $1\mu W$ .

is set below the breakdown voltage. The gate frequency of the electrical pulses for subsequent characterization is 10 kHz. The main gate width of 1.5 ns is used for most characterizations. The SPDE measurements adopting both the gate width of 1.5 ns and 5 ns for showing the significant increase of SPDE due to an increased excess bias percentage. All the characterizations are carried out in a LN2 open-cycle cryostat (Optistat CF, Oxford Instruments) which can cool the device down to 77K. The electrical

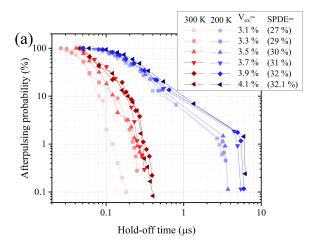

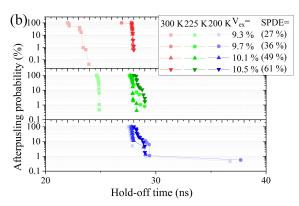

Fig. 3. Afterpulsing probability versus the hold-off time at various temperatures and excess biases for the gate width of (a) 5 ns and (b) 1.5 ns. Different excess bias is applied according to the color scale. The SPDE value measured at 200 K is shown in the parenthesis.

signals can be applied and taken from the electrical feedthrough of the cryostat. The excess amount of bias voltage shown in percentage in this article is the ratio of excess bias voltage versus breakdown voltage. The excess electric field are guaranteed to be consistent for different temperature by the recalculation of exact dc voltage and gated pulse according to the breakdown voltage measured at every temperature. For illuminated experiments, we use a 1310 nm laser with pulse width of 50 ps at a repetition rate of 10 kHz synchronized with the gate frequency. The laser pulses are attenuated to about 0.17 photons per pulse. The timing jitter is determined by a time-correlated single photon counting module (TCSPC) with a timing resolution of 4 ps.

## III. RESULTS AND DISCUSSIONS

The maximum operation speed limited by the afterpulsing effect is characterized via the double pulse method [28]. A laser pulse was synchronized with the first gate, triggering an avalanche event, and the second "dark" gate is applied with an adjustable hold-off time for measuring the correlated avalanche events. We vary the operating temperature at the gate width of 5 ns and 1.5 ns and measure the afterpulsing probability at several selected SPDEs. Fig. 3(a) shows the afterpulsing probability as a function of hold-off time for the gate width of 5 ns. Under this gate condition, the hold-off time required to reduce the

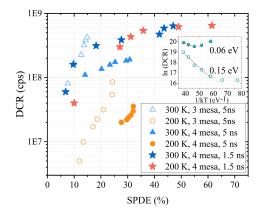

Fig. 4. DCR versus SPDE for triple and quadruple mesa devices at different gate width operations and the temperature of 200 K and 300 K. The inset shows the Arrhenius plot of DCR for the gate width of 1.5 ns (solid symbol) and 5 ns (open symbol). The activation energy can be calculated from the slope of the Arrhenius plot.

afterpulsing probability below 1% is 5  $\mu$ s and 0.3  $\mu$ s respectively at 200 K and 300 K, corresponding to the operation speed of 200 kHz and 3.3 MHz. Furthermore, the afterpulsing probability increases slightly with higher excess bias or with higher SPDE, where the value of SPDE behind the excess bias percentage in the legend is the data measured at 200 K. When the pulse width is reduced to 1.5 ns, the narrower pulse decreases the amounts of carriers generated during an avalanche breakdown event, leading to less pronounced afterpulsing effect. As shown in Fig. 3(b), the afterpulsing probability is greatly decreased as compared to that measured under the gate width of 5 ns. The hold-off time required for minimal afterpulsing probability (1%) is between 0.02  $\mu$ s and 0.03  $\mu$ s when the temperature is changed from 300 K to 200 K, corresponding to the maximum operation speed between 50 MHz and 33 MHz. At 200 K, with the increase of SPDE, the afterpulsing probability exhibits no significant increase. For T = 225 K and 300 K, the afterpulsing probability increases slightly for the excess bias increasing from 9.3% to 10.5% (SPDE from 27% to 61%). Again, the SPDE in the legend is referred to the data measured at 200 K. Reducing the gate width avoids the afterpulsing effect but also decreases the amplitude of avalanche signal, which makes more difficult to distinguish the avalanche signal from the capacitively-coupled spurious signal. As a result, the level of applied excess bias is elevated and ranges between 7.5% to 11% for the narrower gate operation, where the DCR saturation sets the upper limit on the excess bias.

We characterize the DCR and SPDE at the temperature of 200 K and 300 K and at a fixed gate frequency of 10 kHz where the afterpulsing effect can be disregarded through the above examination on the afterpulsing performance. Fig. 4 shows the SPDE versus DCR density (normalized to the area of active window) for triple and quadruple mesa devices at the gate width of 5 ns and 1.5 ns. For the triple mesa device measured at the longer gate width of 5 ns, the highest achieved SPDE for 200 K and 300 K is respectively 24% and 15%. The SPDE is notably improved to 32% and 31% respectively for 200 K and 300 K due to the enhanced avalanche triggering probability by incorporating a quadruple mesa structure. In particular, for 300 K, a more

|                           | Material      | Diameter<br>(μm) | V <sub>ex</sub> /V <sub>BD</sub> (%) | Peak<br>SPDE<br>(%) | DCR<br>density<br>(cps/µm²) | Jitter<br>(ps) | Diffusion<br>tail (ps) | Temperature<br>(K) |

|---------------------------|---------------|------------------|--------------------------------------|---------------------|-----------------------------|----------------|------------------------|--------------------|

| Tosi [9]                  | InGaAs/InP    | 25               | 15                                   | 37                  | 24                          | 87             | 360                    | 225                |

| Liu [5]                   | InGaAs/InP    | 40               | 6                                    | 45                  | 7.5                         | 140            | 400                    | 200                |

| Comandar[22]              | InGaAs/InP    |                  | 14                                   | 55                  |                             | 91             |                        | 293                |

| Fang [23]                 | InGaAs/InP    | 25               | 27                                   | 60                  | 5.4×10 <sup>2</sup>         |                |                        | 300                |

| Zhang [19]                | InGaAs/InAlAs | 25               | 3                                    | 35                  | 5.3×10 <sup>4</sup>         |                |                        | 240                |

| Our previous<br>work [20] | InGaAs/InAlAs | 240              | 8                                    | 32.3                | 87                          | 61             | N/A                    | 187.5              |

| This work                 | InGaAs/InAlAs | 60               | 8.3                                  | 61.4                | 1.8×10 <sup>5</sup>         | 65             | N/A                    | 200                |

TABLE I FIGURE OF MERITS OF OUR AND OTHER SPADS

significant increment of SPDE is observed. For the quadruple mesa devices, SPDE has less temperature dependence, which implies that more uniform and well concentrated electric field distribution can offset carrier cooling subjected to the increased phonon scattering at high temperatures. To operate SPAD at room temperature is very attractive since it reduces not only the complexity of cooling systems but also avoid the afterpulsing effect. In addition to the SPDE, the DCR density for quadruple mesa device is several times lower compared to the triple mesa device at the same SPDE.

The highest SPDEs are obtained by reducing the gate width to 1.5 ns in conjunction with higher excess bias. As shown in Fig. 4, the maximum achievable SPDE reaches 61.4% with  $180 \text{ kcps/}\mu\text{m}^2$  DCR at 200 K and even reaches 47% with  $177 \text{ kcps/}\mu\text{m}^2 DCR$  at 300 K. Here, the achieved SPDEs (61.4%) at 200 K and 47% at 300 K) is the highest ever reported in InP and  $In_{0.52}Al_{0.48}As$  based SPADs [19], [23]. In order to study the possible origins of dark counts, we probe the DCR at various temperatures. The activation energy can be obtained by fitting the ln(DCR) versus 1/kT characteristics, as shown in the inset of Fig. 4. For the longer gate width with lower excess bias, the activation energy is 0.15 eV at the linear fitting range between 200 K and 300K. With a shorten gate width and higher excess bias, the activation energy of 0.06 eV is deduced from the data between 250 K and 300 K. The activation energy far less than the half of energy bandgap of InGaAs layer for both operation conditions suggests that the dark counts is dominantly originated from the tunneling-related generation in the multiplication layer instead of the Shockley-Read-Hall generation in the absorption layer. For the operation with the gate width of 1.5 ns, the tunneling-related generation gets more serious due to the application of higher excess bias. Therefore, for future advanced structure design, the tunneling generation remains the most concerning issue.

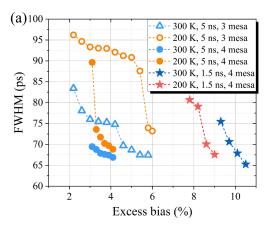

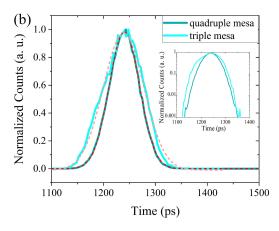

The temporal response of our SPAD perfectly follows a Gaussian distribution function and is almost free from the slow diffusion tail [20]. The full-width of half-maximum of Gaussian function, known as the timing jitter, is recorded as a function of excess bias at different operation conditions respectively for the temperature of 200 K and 300 K. Fig. 5(a) shows the changes

Fig. 5. (a) Timing jitter versus excess bias for quadruple and triple mesa devices at different gate width operations and the temperature of 200 K and 300 K. (b) Gaussian-like temporal responses measured at  $V_{\rm ex}=4.1\%$ , 5ns gate width and T=200 K for quadruple and triple mesa devices. The red and pink dashed line are the Gaussian fit curves for quadruple and triple mesa devices, respectively. The inset shows the semilog plot of temporal response distributions.

of the jitter with excess bias. For all operation conditions, the timing jitter universally decreases with increasing the excess bias. In addition, as shown by the data obtained at the gate width of 5 ns, the timing jitter can be greatly improved under the same excess bias by incorporating a quadruple mesa structure.

Fig. 5(b) shows the near-Gaussian temporal responses measured at the excess bias of 4.1%, the gate width of 5ns and  $T=200~\rm K$  respectively for quadruple and triple mesa device. With reducing the gate width and higher excess bias, the timing jitter is no further decreased due to the limitation of instrument response.

The recent achievement of InGaAs based SPAD has been summarized into Table I which lists several figure of merits of SPAD. All the figure of merits are recorded under which the peak SPDE is obtained. The SPDE reported in this work is better than the recent published results of InGaAs/InP SPAD [22], [23] and InGaAs/InAlAs SPAD [19], however, at the cost of relatively high DCR. Further improvement in the device DCR performance can be expected by only slightly increasing the thickness of multiplication layer to reduce the tunneling generation.

#### IV. CONCLUSION

We have demonstrated an  $In_{0.53}Ga_{0.47}As/In_{0.52}Al_{0.48}As$  SPAD with high SPDE beyond 60% at 1310 nm. By introducing a distinct design of dual multiplication layer, we overcome the trade-off barrier that exists between the DCR, afterpulsing effect and the timing jitter. The highest EQE of over 100% was achieved based on the optimization of vertical electric field. The lateral electric field distribution is more uniform and well concentrated by incorporating a quadruple mesa structure. The advanced device structure in conjunction with a shorten gate width, the SPDE, an important figure of merit for SPADs, reaches 61.4% with 180 kcps/ $\mu$ m<sup>2</sup> DCR at 200 K without the involvement of afterpulsing effect. Our detector featuring a high efficiency detection of near-IR photons and low jitter is desired especially for the outdoor direct time-of-flight LiDAR and enables the extension from short- to long-range.

#### REFERENCES

- R. H. Hadfield, "Single-photon detectors for optical quantum information applications," *Nat. Photon.*, vol. 3, pp. 696–705, Dec 2009, doi: 10.1038/nphoton.2009.230.

- [2] A. McCarthy et al., "Kilometer-range depth imaging at 1550 nm wavelength using an InGaAs/InP single-photon avalanche diode detector." Opt. Exp., vol. 21, pp. 22098–22113, Sep. 2013.

- [3] E. B. van Munster and T. W. J. Gadella, "Fluorescence lifetime imaging microscopy (FLIM)," Adv. Biochem. Eng. Biotechnol., vol. 95, pp. 143–175, May 2005, doi: 10.1007/b102213.

- [4] S. Pellegrini et al., "Design and performance of an InGaAs-InP single-photon avalanche diode detector," *IEEE J. Quantum Electron.*, vol. 42, no. 4, pp. 397–403, Apr. 2006, doi: 10.1109/JQE.2006.871067.

- [5] M. Liu et al., "High-performance InGaAs-InP single-photon avalanche photodiode," IEEE J. Sel. Topics Quantum Electron., vol. 13, no. 4, pp. 887–894, Jul./Aug. 2007, doi: 10.1109/JSTQE.2007.903855.

- [6] M. A. Itlzer et al., "Advances in ingaasp-based avalanche diode single photon detectors," J. Modern Opt., vol. 58 no. 3–4, pp. 173–200, Jan 2011, doi: 10.1080/09500340.2010.547262.

- [7] Y. Liang et al., "Room-temperature single-photon detector based on InGaAs/InP avalanche photodiode with multichannel counting ability," *IEEE Photon. Technol. Lett.*, vol. 23, no. 2, pp. 115–117, Jan. 2011, doi: 10.1109/LPT.2010.2092756.

- [8] A. Tosi, F. Acerbi, M. Anti, and F. Zappa, "InGaAs/InP single-photon avalanche diode with reduced afterpulsing and sharp timing response with 30ps tail," *IEEE J. Quantum Electron.*, vol. 48, no. 9, pp. 1227–1232, Sep. 2012, doi: 10.1109/JQE.2012.2208097.

- [9] A. Tosi, N. Calandri, M. Sanzaro, and F. Acerbi, "Low-noise, low-jitter, high detection efficiency InGaAs/InP single-photon avalanche diode," *IEEE J. Sel. Top. Quantum Electron.*, vol. 20, no. 6, Nov./Dec. 2014, Art no. 3803406, doi: 10.1109/JSTQE.2014.2328440.

- [10] Y. L. Goh et al., "Avalanche multiplication in InAlAs," IEEE Trans. Electron Devices, vol. 54, no. 1, pp. 11–16, Jan. 2007, doi: 10.1109/TED.2006.887229.

- [11] S. C. L. T. Mun et al., "A theoretical comparison of the breakdown behavior of In<sub>0.52</sub>Al<sub>0.48</sub>As and InP near-infrared single-photon avalanche photodiodes," *IEEE J. Quantum Electron.*, vol. 45, no. 5, pp. 566–571, May 2009, doi: 10.1109/JQE.2009.2013094.

- [12] S. L. Tan, D. S. Ong, and H. K. Yow, "Theoretical analysis of breakdown probabilities and jitter in single-photon avalanche diodes," *J. Appl. Phys.*, vol. 102, Aug. 2007, Art no. 044506, https://doi.org/10.1063/1.2772531.

- [13] M. Nada, Y. Muramoto, H. Yokiyama, N. Ishibashi, and S. Kodama, "Inverted inalas/ingaas avalanche photodiode with low-high-low electric field profile," *Jpn. J. Appl. Phys.*, vol. 51, no. 2, Feb. 2012, Art. no. 02BG03.

- [14] G. Karve et al., "Geiger mode operation of an In<sub>0.53</sub>Ga<sub>0.47</sub>As-In<sub>0.52</sub>Al<sub>0.48</sub>As avalanche photodiode," *IEEE J. Quantum Electron.*, vol. 39, no. 10, pp. 1281–1286, Oct. 2003, doi: 10.1109/JQE.2003.817244.

- [15] T. Nakata et al., "InAlAs avalanche photodiodes for gated Geiger mode single photon counting," in Proc. OECC Tech. Dig., 2010, pp. 822–823.

- [16] K. Zhao, S. You, J. Cheng, and Y. H. Lo, "Self-quenching and self-recovering InGaAs/InAlAs single photon avalanche detector," *Appl. Phys. Lett.*, vol. 93, no. 15, pp. 153504–1–153504–3, Jun. 2008.

- [17] X. Meng, C. H. Tan, S. Dimler, J. P. R. David, and J. S. Ng, "1550nm InGaAs/InAlAs single photon avalanche diode at room temperature," *Opt. Exp.*, vol. 22, pp. 22608–22615, Sep. 2014, doi: 10.1364/OE.22.022608.

- [18] X. Meng et al., "InGaAs/InAlAs single photon avalanche diode for 1550nm photons," Roy. Soc. Open Sci., vol. 3, no. 3, Mar. 2016, Art. no. 150584, doi: 10.1098/rsos.150584.

- [19] J. Zhang et al., "High-performance InGaAs/InAlAs single-photon avalanche diode with a triple-mesa structure for near-infrared photon detection," Opt. Lett., vol. 46, pp. 2670–2673, Jun. 2021, doi:10.1364/OL.424606.

- [20] Y. S. Lee, P. L. W. Naseem, Y. J. Chen, and J. W. Shi, "Neat temporal performance of InGaAs/InAlAs single photon avalanche diode with stepwise electric field in multiplication layers," *IEEE Access*, vol. 9, pp. 32979–32985, 2021, doi: 10.1109/ACCESS.2021.3060824.

- [21] J. C. Campbell, W. Sun, Z. Lu, M. A. Itzler, and X. Jiang, "Common-mode cancellation in sinusoidal gating with balanced InGaAs/InP single photon avalanche diodes," *IEEE J. Quantum Electron.*, vol. 48, no. 12, pp. 1505–1511, Dec. 2012, doi: 10.1109/JQE.2012.2223200.

- [22] L. C. Comandar et al., "Gigahertz-gated InGaAs/InP single-photon detector with detection efficiency exceeding 55% at 1550 nm," J. App. Phys., vol. 117, Feb. 2015, Art. no. 083109, https://doi.org/10.1063/1.4913527.

- [23] Y. Q. Fang et al., "InGaAs/InP single-photon detectors with 60% detection efficiency at 1550 nm," Rev. Sci. Instruments, vol. 91, Aug. 2020, Art. no. 083102, doi: 10.1063/5.0014123.

- [24] I. Vornicu, R. Carmona-Galan, and A. Rodriguez-Vazquez, "On-chip timeof-flight estimation in standard CMOS technology," SPIE Newsroom, pp. 3, Feb. 2015, doi: 10.1117/2.1201501.005721.

- [25] J. S. Ng, C. H. Tan, G. J. Rees, and J. P. R. David, "Effects of dead space on breakdown probability in geiger mode avalanche photodiode," *J. Modern Opt.*, vol. 54, no. 2-3, pp. 353–360, doi: 10.1080/09500340600753814.

- [26] Y.-H. Chen et al., "Top-Illuminated In<sub>0.52</sub>Al<sub>0.48</sub>As-based avalanche photodiode with dual charge layers for high-speed and low dark current performances," *IEEE J. Sel. Topics Quantum Electron.*, vol. 24, no. 2, Mar./Apr. 2018, Art. no. 3800208.

- [27] H.-Y. Zhao et al., "High-speed avalanche photodiodes with wide dynamic range performance," J. Lightw. Technol., vol. 37, no. 23, pp. 5945–5952, Dec. 2019.

- [28] K. E. Jensen et al., "Afterpulsing in Geiger-mode avalanche photodiodes for 1.06 μm wavelength," Appl. Phys. Lett., vol. 88, no. 13, Mar. 2006, Art. no. 133503, doi: 10.1063/1.2189187.

Yi-Shan Lee received the Ph.D. degree in electronics engineering from the National Chiao Tung University, Taiwan, in 2015. Since 2015, she has been an Assistant Professor with the Department of Electrical Engineering, National Central University, Taoyuan, Taiwan. Her work focuses specifically on the cavity quantum electrodynamics, single photon source, entangled photon pairs and single photon avalanche diodes. Her recent publications can be found in Optics Letter, IEEE Photonics Technology Letters, Physical Review Letters, and IEEE ACCESS.

Yan-Min Liao was born in Taoyuan, Taiwan, on Feb. 24, 1997. He received the B.S. degree from the Department of Electronics, Chung Yuan Christian Chung University, Taoyuan, in 2019. He is currently working toward the M.S. degree with the Department of Electrical Engineering, National Central University, Taoyuan. His current research interests include single-photon avalanche diode and avalanche photodiode.

**Yu-Jie Teng** was born in Taichung, Taiwan, in 2000. She is currently an Undergraduate Student with the Department of Electrical Engineering, National Central University, Taoyuan, Taiwan. She is studied in conduction under Prof. Yi-Shan Lee. Her independent study focuses on single photon avalanche diode for single photon applications.

Ping-Li Wu was born in Tainan, Taiwan, in 1997. He received the B.S. degree from the Department of Electrical Engineering, National Central University, Taoyuan, Taiwan, in 2020. He is currently a Research Assistant with Quantum Optoelectronics Laboratory, National Central University, under the leadership of Prof. Yi-Shan Lee. His research interests include the measurement and characterization of the near-infrared single-photon avalanche diodes.

**Yu-Ying Hung** is currently an Undergraduate Student with the College of Science Joint Science Program, National Central University, Taoyuan, Taiwan. She is studied in conduction under Prof. Yi-Shan Lee. Her independent study focuses on single photon avalanche diode for single photon applications.

Chi-En Chen was born in Kaohsiung, Taiwan, in 2000. He is currently an Undergraduate Student with the Department of Electrical Engineering, National Central University, Taoyuan, Taiwan. He is studied in conduction under Prof. Yi-Shan Lee. His independent study focuses on single photon avalanche diode for single photon applications.

Jin-Wei Shi (Senior Member, IEEE) was born in Kaohsiung, Taiwan, on January 22, 1976. In 2003, he joined the Department of Electrical Engineering, National Central University, Taoyuan, Taiwan, where he has been a Professor since 2011. During 2011–2012 and during 2016–2017, he joined the ECE Dept. of UCSB, as a Visiting Professor. He has authored or coauthored more than 4 book chapters, 160 Journal papers, 200 conference papers and holds 30 patents. His current research interests include ultrahigh speed/power photodetectors, electro-absorption

modulators, THz photonic transmitters, single-photon and high-speed avalanche photodiodes and VCSELs. In 2010, he was the recipient of the Da-You Wu Memorial Award.