# A Back-Illuminated SPAD Fabricated With 40 nm CMOS Image Sensor Technology Achieving Near 40% PDP at 940 nm

Eunsung Park, Won-Yong Ha, Hyo-Sung Park, Doyoon Eom, Hyun-Seung Choi, Dae-Hwan Ahn, Woo-Young Choi, *Member, IEEE*, and Myung-Jae Lee, *Member, IEEE*

Abstract—This article introduces a back-illuminated (BI) single-photon avalanche diode (SPAD) based on 40 nm CMOS image sensor (CIS) technology which is the most advanced technology node for the fabrication of a SPAD up to date. It's based on a P-well (PW) and deep N-well (DNW) junction, and the DNW is deeply implanted to form a wide absorption region resulting in very high and wide photon detection probability (PDP). Thanks to the retrograde DNW, the premature edge breakdown phenomenon is completely prevented and the whole area of the planar junction becomes a high-efficient avalanche multiplication region. In addition, an anti-reflection coating on the backside of the SPAD and a metal reflector at the bottom reduce the reflection of incoming photons and improve the efficiency at long wavelengths, respectively. With the most advanced CIS technology for BI SPADs, the presented SPAD accomplishes a dark count rate (DCR) of 70 cps/\mu<sup>2</sup>, peak PDP of 81% at 675 nm, and PDP of 39% at 940 nm. The timing jitter is 79 ps full width at half-maximum width (FWHM), which is the best timing jitter performance among BI SPADs reported so far. All the values are obtained with the excess bias voltage of 6 V.

Index Terms—Avalanche photodiode (APD), back-illuminated single-photon avalanche diode (SPAD), CMOS image sensor (CIS) technology, detector, diode, Geiger-mode avalanche photodiode (G-APD), high-volume manufacturing, integrated optics device, integrated optoelectronics, integration of photonics in standard CMOS technology, light detection and ranging (LiDAR), near infrared (NIR), optical sensing, optical sensor, photodetector, photodiode, photomultiplier, RGB-D sensor, semiconductor device, sensor, silicon, wafer-scale integration.

Manuscript received February 3, 2023; revised April 11, 2023; accepted April 28, 2023. Date of publication; date of current version. This work was supported by the Korea Institute of Science and Technology (KIST) Institution Program (Grant No. 2E32242), National Research Foundation of Korea (NRF) (Grant No. 2021M3D1A2046731), and Korea Evaluation Institute of Industrial Technology (KEIT) grant funded by the Ministry of Trade, Industry and Energy (MOTIE, Korea) (20008757). (Corresponding author: Woo-Young Choi and Myung-Jae Lee.)

E. Park, H.-S. Park, D. Eom, H.-S. Choi, D.-H. Ahn, and M.-J. Lee are with the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology (KIST), Seoul 02792, South Korea (e-mail: mj.lee@kist.re.kr).

W.-Y. Ha is with the Institute of Electrical and Micro Engineering, École Polytechnique Fédérale de Lausanne, Rue de la Maladière 71 B.

E. Park, H.-S. Park, D. Eom, H.-S. Choi and W.-Y. Choi are with the Department of Electrical and Electronic Engineering, Yonsei University, Seoul 03722, South Korea.

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier

### I. Introduction

S single-photon avalanche diode (SPAD) based sensors have proven their feasibility in various scientific and industrial applications which require high sensitivity, they have been getting a lot of attention [1]-[4]. In addition, the development of SPADs in deep-submicron CMOS technologies enables the capability of monolithic integration with on-chip electronics that perform the functions of time-resolved measurement and histogram process required for time-correlated single-photon counting (TCSPC) and consequently large arrays, while reducing production costs. As a result, the CMOS-based SPAD sensor solutions are being applied to various applications requiring time-resolved imaging, such as light detection and ranging (LiDAR) to control and navigate autonomous vehicles [3]-[6], airborne laser mine detection system (ALMDS) to identify a target in military applications [7], service drones [8], machine vision [9], security, and biomedical imaging including fluorescence lifetime imaging (FLIM) [10], positron emission tomography (PET) [11], and near-infrared optical tomography (NIROT) that can diagnose the human brain and body [12]. One challenge of the CMOS-based approach is that the on-chip electronics occupy a considerable area and it becomes more severe as more functionalities like counting, timestamping, processing, and compression are required, which results in a small area to implement the SPAD, i.e., low fill factor (FF) [13], [14]. Such a trade-off not only limits the spatial resolution of a SPAD sensor but also increases the chip size and cost. In order to overcome the trade-off, a possible solution is using a more advanced CMOS technology. A SPAD in a deeper-submicron CMOS technology has a comparative advantage in terms of power consumption as well as FF, but it still suffers from the space problem with the onchip electronics. Furthermore, as the doping concentrations increase as the technology node decreases, the available depletion regions become narrower, resulting in a high tunneling noise and low and narrow photon detection probability (PDP). Another critical issue with the CMOSbased SPAD sensor solutions is that the PDP in the nearinfrared (NIR) range is low, and unlike the fill-factor problem it cannot be dramatically improved even if an advanced CMOS technology is utilized [15], [16]. The reason is that the

TABLE I

PERFORMANCE COMPARISON OF STATE-OF-THE-ART

FI AND BI SPADS

| TITAL BISTIES                |                  |                  |                     |                      |

|------------------------------|------------------|------------------|---------------------|----------------------|

|                              | [15]             | [16]             | [23]                | [24]                 |

| Туре                         | FI               | FI               | BI                  | BI                   |

| $V_B[V]$                     | 22               | 31.5             | 30                  | 22                   |

| $V_E\left[\mathbf{V}\right]$ | 6                | 7                | 2.5                 | 3                    |

| Peak PDP<br>[%]              | 55<br>(@ 480 nm) | 62<br>(@ 530 nm) | 69.4*<br>(@ 510 nm) | 50.5**<br>(@ 800 nm) |

| PDP @ 940 nm [%]             | 3.2              | 4.2              | 24.4*               | 20.5**               |

PDE with \*microlens and pyramid surface or \*\*microlens and light trapping.

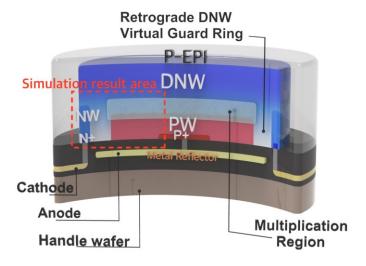

Fig. 1. Cross-section of the proposed BI SPAD.

PN junctions are usually formed within  $1\sim3~\mu m$  under the surface while the penetration depth of NIR in Si is much deeper than the junctions.

A recent paradigm shift in CMOS SPADs is the development of back-illuminated (BI) SPADs in CMOS image sensor (CIS) technology compatible with three-dimensional stacking technology. The stacking technology places the CMOS circuitry under the SPAD array so that significantly improves the FF while enabling higher functionality, lower power consumption, and larger array production. In addition, since it is possible to select and utilize a more appropriate CMOS technology for the top-tier and bottom-tier chip, respectively, the SPAD can avoid the negative effects caused by high doping concentrations, and as a result, dark count rate (DCR) and PDP can be significantly improved. Furthermore, as the top-tier chip is fabricated a BI CIS technology, the junction of the SPAD is formed at a deeper position compared to that of the front-illuminated (FI) case, and thus higher PDP can be achieved in the NIR wavelength range. To date, there have been several attempts on the BI 3D-stacked SPADs and various results have been reported [17]-[24]. Table I shows the performance comparison between FI and BI SPADs reported lately, and it clearly shows that the SPAD PDP at 940nm can be greatly increased with the BI approach.

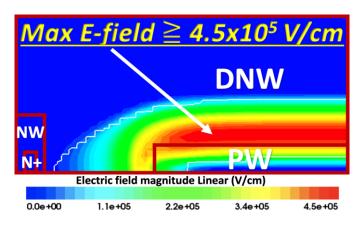

**Fig. 2.** TCAD simulation result for the BI SPAD: E-field profile at  $V_E = 1$  V.

Although these attempts report substantial performance improvement, especially in NIR efficiency, it can be increased further, and particularly the timing jitter performance should be improved to achieve a better depth resolution of SPAD-based sensors.

In this paper, we present and fully characterize a single BI SPAD fabricated in 40 nm CIS technology which is the most advanced CIS technology for SPAD fabrications. Thanks to the wide absorption region, high E-field at the planar junction enabling efficient avalanche multiplication, optimized backside etching/thinning, and the use of a metal reflector and anti-reflection coating (ARC), the proposed SPAD achieves an excellent peak PDP of 81% at the wavelength of 675 nm along with high PDP in the NIR wavelength range. In addition, it achieves the best timing jitter, 79 ps at the full width at half maximum (FWHM) among the BI SPADs reported so far. This article is organized as follows. In Section II, the SPAD structure and its TCAD simulation result are explained. Section III presents the full characteristics of the SPAD including a demonstration of the active area, I-V characteristics, noise, temperature dependence, sensitivity, and timing performance. Section IV concludes this paper.

### II. SPAD Structure and TCAD Simulation

Fig. 1 shows the cross-section of the proposed BI SPAD fabricated in SK hynix 40 nm CIS technology. The SPAD is based on a P-well (PW) and deep N-well (DNW) junction, and a virtual guard ring (GR) based on the retrograde DNW surrounds the junction to prevent the premature breakdown at the edge of the junction. The SPAD is implemented in a round shape with a 5  $\mu$ m diameter active area, 2  $\mu$ m GR, and 0.5  $\mu$ m cathode, resulting in a FF of 25%. The GR and cathode sizes were chosen as conservative design parameters, and therefore the FF can be improved in future generations with optimized parameters and the use of microlens. In addition, it can be further improved by sharing the cathode between SPADs. The thickness of the Si epi layer remained after the backside etching/thinning process is optimized considering the absorption coefficient in silicon and the depth of DNW.

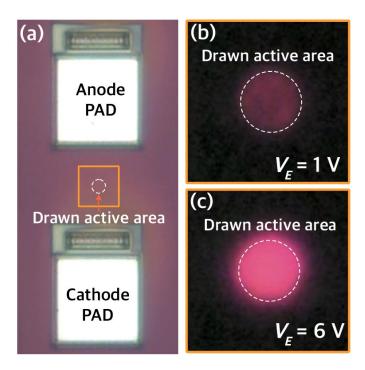

**Fig. 3.** (a) Micrograph of the BI SPAD and light-emission-test results at  $V_E =$  (b) 1 V and (c) 6 V.

Through this process, the BI SPAD is able to achieve a wide spectral range as well as high efficiency. In addition, thanks to the metal reflector that covers the active area completely and the ARC formed on the top of the SPAD backside, the detection efficiency can be further improved.

In order to demonstrate the depletion region and E-field profile, TCAD simulation was performed at the excess bias voltage,  $V_E$ , of 1 V. The simulation area in Fig. 2 corresponds to the red-dashed square in Fig. 1. Thanks to deep and retrograded DNW, the virtual GR prevents the premature edge breakdown completely so that a wide avalanche multiplication region is uniformly formed at the planar PW/DNW junction, which contributes to achieving a high and wide efficiency along with the wide depletion region over 1  $\mu$ m and broad absorption region based on the lightly-doped deep DNW.

### III. EXPERIMENTAL RESULTS

Fig. 3(a) shows the micrograph of the BI SPAD having an anode and cathode pad which is used for experiments in this paper. Figs. 3(b) and (c) show light-emission-test results at  $V_E$  = 1 V and 6 V, respectively. The area emitting light clearly indicates that the SPAD does not suffer from any premature edge breakdown and has a uniform and high E-field over the active area. In order to investigate more precisely the effective active region where a photon-generated carrier can trigger an avalanche multiplication, a measurement with a laser-scanning microscope was performed. The laser beam passes through the optical system and reaches the scanning equipment consisting of a single Galvo mirror that can scan the X-Y axis. When the single Galvo mirror scans over the SPAD, the number of

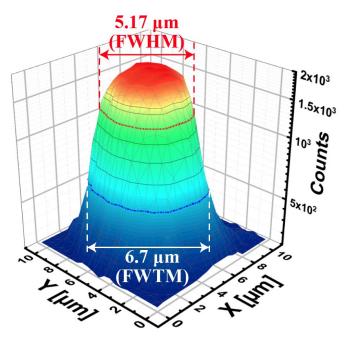

**Fig. 4.** Laser-scanning-microscope result of the BI SPAD: 3D-plot at  $V_E = 4$  V.

**Fig. 5.** I-V characteristics of the BI SPAD without and with illumination at room temperature.

SPAD output pulses varies depending on the location of the laser, and the number of the pulses is measured with an oscilloscope in real-time. The result is shown in Fig. 4 at  $V_E$  = 4 V with a 637 nm continuous laser. It clearly demonstrates that the avalanche multiplication occurs over the whole active area and the FWHM is about 5.2  $\mu$ m. This result proves again that the proposed SPAD does not suffer from premature edge breakdown, matching well with the TCAD-simulation and the light-emission-test results shown in Figs. 2 and 3, respectively. The full width at tenth maximum (FWTM) is about 6.7  $\mu$ m, which means that some of the photon-generated carriers at the GR region contribute to the avalanche multiplication.

Fig. 6. Output waveforms of the device at three different bias conditions.

**Fig. 7.** DCR and normalized DCR of the BI SPAD versus  $V_E$  at room temperature.

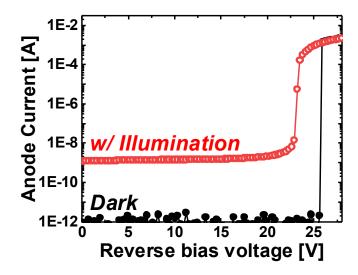

The I-V characteristics of the SPAD in Fig. 5 show that the breakdown voltage is about 23.2 V and the SPAD has very low dark currents below 1 pA, which is the minimum limit of the measurement setup at room temperature. The breakdown in the dark condition occurs at a larger reverse bias voltage than under illumination, and it indicates that the number of dark carriers is low, which should result in a low DCR performance.

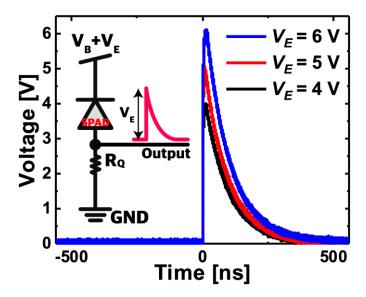

The inset of Fig. 6 shows a simple schematic for measuring the proposed SPAD. An external passive quenching resistor of 200 k $\Omega$  was used to measure the output voltage pulses, and a reverse bias voltage was applied to the cathode. The measurements were performed with a high-performance digital oscilloscope. Although the measured pulse widths are a

**Fig. 8.** Temperature-dependent-measurement results: (a) breakdown voltage variation versus temperature and (b) normalized DCR versus  $V_E$  at four different temperatures.

little wide due to the external capacitance components, it can be seen that the height of each output pulse matches well with the applied  $V_E$ .

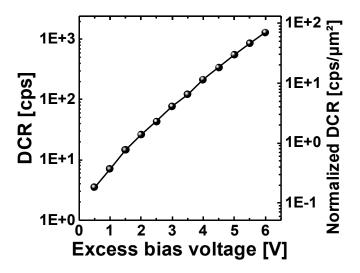

DCR measurement was performed at room temperature as a function of  $V_E$ , from 0.5 V up to 6 V, and the result is shown in Fig. 7. The SPAD exhibits a low DCR, about 0.2 cps/ $\mu$ m<sup>2</sup> at  $V_E = 0.5$  V, and therefore  $V_E$  can be increased to enhance the PDP performance. At  $V_E = 6$  V, it still shows below 100 cps/ $\mu$ m<sup>2</sup> DCR. One of the factors increasing DCR in the BI SPAD is the dangling bonds on the Si epi surface after the backside etching/thinning process. However, thanks to the structural advantage of the proposed SPAD, i.e., isolating the SPAD active region from the P-epi using DNW, the SPAD is not exposed to the dangling-bond defects so that it can achieve a low DCR even at the high excess bias condition.

Fig. 9. Arrhenius plot with extracted activation energy and the coefficient for the curve fit at  $V_E = 6$  V.

**Fig. 10.** PDP spectra of the BI SPAD at three different  $V_E$ .

**Fig. 11.** Timing jitter of the BI SPAD at  $V_E = 6$  V when using a 940 nm picosecond pulsed laser.

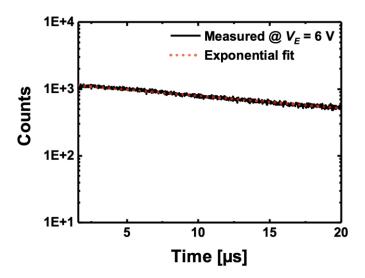

Fig. 12. Inter-avalanche time histogram measured at  $V_E = 6 \text{ V}$  along with a fitted exponential curve.

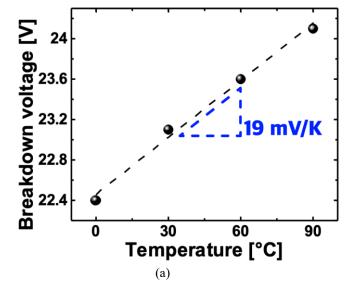

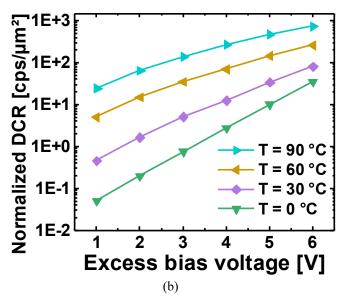

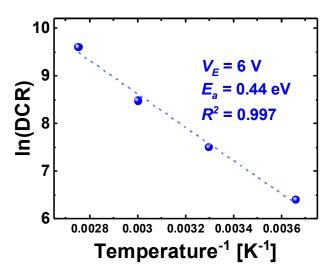

The temperature dependence of the breakdown voltage was investigated from 0 to 90 °C with a temperature chamber, and the results are shown in Fig. 8(a). The temperature coefficient of the breakdown voltage is about 19 mV/K. The DCR was also characterized at different temperatures, from 0 to 90 °C, and the device shows acceptable DCR, below 1 kcps/ $\mu$ m², even at 90 °C as can be seen in Fig. 8(b). The measurement results indicate the main contributor to its DCR is the trapassisted thermal generation, and this can be confirmed by the activation energy,  $E_a$ , extracted from the Arrhenius plot depicted in Fig. 9. The extracted value is 0.44 eV at  $V_E = 6$  V, and it implies that the traps can be generated by the implantation of phosphorus [25].

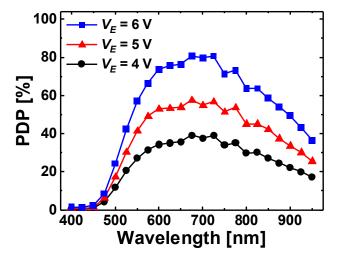

Fig. 10 shows the PDP spectra of the BI SPAD for  $V_E$  from 4 to 6 V. The SPAD achieves a peak PDP of 81% at 675 nm and PDP of about 39.2% at 940 nm at  $V_E = 6$  V. It is notable that the cut-off wavelength in PDP appears at around 450 nm, and it corresponds to the penetration depth of about 400 nm in silicon. It means that the remaining P-epi thickness above the deep DNW after the backside etching/thinning process is just about 400 nm, which was done by considering the photon absorption coefficient and the deeply formed DNW. Therefore, the SPAD can collect most of the photon-generated carriers, achieving a wide spectral range and very high PDP. Such performance will play a key role in many applications that require high PDP.

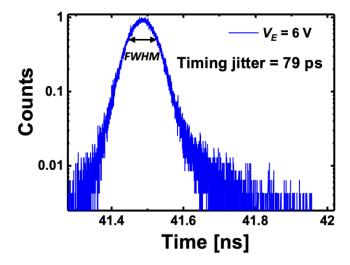

The timing-jitter measurements were performed at room temperature. A 940 nm picosecond pulsed laser was used as the laser source and a high-performance oscilloscope providing TCSPC function was used to measure the time difference between the laser triggering pulse and the SPAD output pulse. Fig. 11 shows the result of normalized histogram values on a log scale. The result shows the FWHM value at  $V_E$  = 6 V and the result is 79 ps. The excellent timing jitter of this SPAD is achieved thanks to the wide and high E-field at the junction and the DNW blocking diffused carriers from the P-epi.

Fig. 12 shows the inter-avalanche time histogram of the SPAD at  $V_E = 6$  V. Although the dead time is relatively large, about 1.6  $\mu$ s, because the measurement was conducted by using an external passive quenching resistor, it can be greatly improved with an integrated active recharge circuit. As the measured histogram is well matched with the exponential curve, which indicates the Poissonian nature of the SPAD output pulses, it suggests that the afterpulsing probability is negligible with a dead time longer than 1.6  $\mu$ s.

### IV. CONCLUSION

We demonstrate a high-performance BI SPAD fabricated in 40 nm CIS technology. Through the TCAD simulation, lightemission test, and laser-scanning microscope, the avalanche multiplication area is clearly demonstrated, and the device is fully characterized, including temperature-dependent noise characteristics. The thickness of the Si epi selected in considering both the depth of avalanche multiplication region and photon absorption coefficient enabled wide-spectral PDP and best timing jitter. Thanks to the wide absorption region, high and wide E-field at the planar junction, optimized backside process, metal reflector, and ARC, the proposed SPAD achieves a DCR of 70 cps/µm<sup>2</sup>, peak PDP of 81%, PDP of 39.2% at 940 nm, and timing jitter of 79 ps at  $V_E = 6$  V. The SPAD achieves, to the best of our knowledge, the highest PDP and the lowest timing jitter among reported BI SPADs so far. We expect that this SPAD can play a key role in various applications.

### ACKNOWLEDGMENT

The authors are grateful to SK hynix collaborators, especially Hyuk An, Suhyun Yi, Kyung-Do Kim, Jongchae Kim, Kwang June Sohn, Kwangjun Cho, Ji-Hoon Cho, Minseok Shin, Hoon-Sang Oh, and Kangbong Seo, for their help and support.

# REFERENCES

- [1] B. F. Aull A. H. Loomis, D. J. Young, R. M. Heinrichs, B. J. Felton, P. J. Daniels, and D. J. Lanseres, "Geiger-mode avalanche photodiodes for three-dimensional imaging," *Lincoln Lab. J.*, vol. 13, no. 2, pp. 335-350, 2002.

- [2] C. Niclass, A. Rochas, P.-A. Besse, and E. Charbon, "Design and characterization of a CMOS 3-D image sensor based on single photon avalanche diodes," *IEEE J. Solid-State Circuits*, vol. 40, no. 9, pp. 1847-1854, Sep. 2005.

- [3] C. Niclass, M. Gersbach, R. Henderson, L. Grant, and E. Charbon, "A single photon avalanche diode implemented in 130-nm CMOS technology," *IEEE J. Sel. Topics Quantum Electron.*, vol. 13, no. 4, pp. 863-869, Jul./Aug. 2007.

- [4] F. Villa, R. Lussana, D. Bronzi, S. Tisa, A. Tosi, F. Zappa, A. D. Mora, D. Contini, D. Durini, S. Weyers, and W. Brockherde, "CMOS imager with 1024 SPADs and TDCs for single-photon timing and 3-D time-of-flight," *IEEE. J. Sel. Topics Quantum Electron.*, vol. 20, no. 6, Nov./Dec. 2014, Art. No. 3804810.

- [5] C. Bruschini, H. Homulle, and E. Charbon, "Ten years of biophotonics single-photon SPAD imager applications – retrospective and Outlook," *Proc. SPIE*, vol. 10069, Feb. 2017, Art. No. 100691S.

- [6] C. Bruschini, H. Homulle, I. M. Antolovic, S. Burri, and E. Charbon, "Single-photon avalanche diode imagers in biophotonics: review and outlook," *Light. Sci. Appl.* 8, 87, Sep. 2019.

- [7] X. Li, C. Liu, Z. Wang, X. Xie, D. Li, and L. Xu, "Airborne LiDAR: state-of-the-art of system design, technology and application," *Meas. Sci. Technol.*, vol. 32, no. 3, Dec. 2020.

- [8] G. Nash, and V. Devrelis, "Flash LiDAR imaging and classification of vehicles," in *Proc. IEEE Sensors*, Oct. 2020, pp. 1-4.

- [9] S. Afshar, T. J. Hamilton, L. Davis, A. Schaik, and D. Delic, "Event-based processing of single photon avalanche diode sensors," *IEEE Sensors Journal*, vol. 20, no. 14, Jul. 2020.

- [10] M. Vitali, D. Bronzi, A. J. Krmpot, S. N. Nikolic, F.-J. Schmitt, C. Junghans, S. Tisa, T. Friedrich, V. Vukojevic, L. Terenius, F. Zappa, and R. Rigler, "A single-photon avalanche camera for fluorescence lifetime imaging microscopy and correlation spectroscopy," *IEEE J. Sel. Topics Quantum Electron.*, vol. 20, no. 6, Nov./Dec. 2014.

- [11] C. Veerappan, C. Bruschini, and E. Charbon, "Sensor network architecture for a fully digital and scalable SPAD based PET system," *IEEE Nucl. Sci. Symp. Med. Imag. Conf. Rec. (NSS/MIC)*, Oct./Nov. 2012, pp. 1115-1118.

- [12] J. Jiang, A. D. C. Mata, S. Lindner, E. Charbon, M. Wolf, and A. Kalyanov, "Dynamic time domain near-infrared optical tomography based on a SPAD camera," *Biomed. Opt. Express*, vol. 11, no. 10, Oct. 2020.

- [13] J. Richardson, R. Walker, L. Grant, D. Stoppa, F. Borghetti, E. Charbon, M. Gersbach, and R. K. Henderson, "A 32 × 32 50 ps resolution 10 bit time to digital converter array in 130 nm CMOS for time correlated imaging," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Sep. 2009, pp. 77-80.

- [14] D. Bronzi, F. Villa, S. Tisa, A. Tosi, F. Zappa, D. Durini, S. Weyers, and W. Brockherde, "100 000 frames/s 64 × 32 single-photon detector array for 2-D imaging and 3-D ranging," *IEEE J. Sel. Topics Quantum Electron.*, vol. 20, no. 6, pp. 1-10, Nov./Dec. 2014.

- [15] F. Gramuglia, M.-L. Wu, C. Bruschini, M.-J. Lee, and E. Charbon, "A low-noise CMOS SPAD pixel with 12.1 ps SPTR and 3 ns dead time," *IEEE J. Sel. Topics Quantum Electron.*, vol. 28, no. 2, Mar./Apr. 2022, Art. No. 3800809.

- [16] F. Gramuglia, P. Keshavarzian, E. Kizilkan, C. Bruchini, S. S. Tan, M. Tng, E. Quek, M.-J. Lee, E. Charbon, "Engineering breakdown probability profile for PDP and DCR optimization in a SPAD fabricated in a standard 55 nm BCD process," *IEEE J. Sel. Topics Quantum Electron.*, vol. 28, no. 2, Mar./Apr. 2022, Art. No. 3802410.

- [17] E. Charbon, M. Scandini, J. Mata Pavia, and M. wolf, "A dual backsideilluminated 800-cell multi-channel digital SiPM with 100 TDCs in 130 nm 3D IC technology," in *Proc. IEEE Nucl. Sci. Symp. Med. Imag. Conf.*, Nov. 2014.

- [18] J. M. Pavia, M. Scandini, S. Lindner, M. Wolf, and E. Charbon, "A 1 × 400 backside-illuminated SPAD sensor with 49.7 ps resolution, 30 pJ/sample TDCs fabricated in 3D CMOS technology for near-infrared optical tomography," *IEEE J. Solid-State Circuits*, vol. 50, no. 10, pp. 2406-2418, Oct. 2015.

- [19] T. Al Abbas, N. A. W. Dutton, O. Almer, S. Pellegrini, Y. Henrion, and R. K. Henderson, "Backside illuminated SPAD image sensor with 7.83µm pitch in 3D-stacked CMOS technology," *International Electron Devices Meeting*, Dec. 2016.

- [20] S. Lindner, S. Pellegrini, Y. Henrion, B. Rae, M. Wolf, and E. Charbon, "A high-PDE, backside-illuminated SPAD in 65/40-nm 3D IC CMOS pixel with cascaded passive quenching and active recharge," *IEEE Electron Device Lett.*, Nov. 2017.

- [21] M.-J. Lee, A. R. Ximenes, P. Padmanabhan, T.-J. Wang, K.-C. Huang, Y. Yamashita, D.-N. Yaung, and E. Charbon, "High-performance back-illuminated three-dimensional stacked single-photon avalanche diode implemented in 45-nm CMOS technology", IEEE J. Sel. Topics Quantum Electron., vol. 24, no. 6, Nov./Dec. 2018.

- [22] M.-J. Lee, P. Sun, G. Pandraud, C. Bruschini, and E. Charbon, "First near-ultraviolet- and blue-enhanced backside-illuminated single-photon avalanche diode based on standard SOI CMOS technology," *IEEE J. Sel. Topics Quantum Electron.*, vol. 25, no. 5, Oct. 2019.

- [23] K. Morimoto, J. Iwata, M. Shinohara, H. Sekine, A. Abdelghafar, H. Tsuchiya, Y. Kuroda, K. Tojima, W. Endo, Y. Maehashi, Y. Ota, T. Sasago, S. Maekawa, S. Hikosaka, T. Kanou, A. Kato, T. Tezuka, S. Yoshizaki, T. Ogawa, K. Uehira, A. Ehara, F. Inui, Y. Matsuno, K. Sakurai, and T. Ichikawa, "3.2 megapixel 3D-stacked charge focusing SPAD for low-light imaging and depth sensing," *International Electron Devices Meeting*, Dec. 2021.

- [24] S. Shimada, Y. Otake, S. Yoshida, S. Endo, R. Nakamura, H. Tsugawa, T. Ogita, T. Ogasahara, K. Yokochi, Y. Inoue, K. Takabayashi, H.

Maeda, K. Yamamoto, M. Ono, S. Matsumoto, H. Hiyama, and T. Wakano, "A back illuminated 6μm SPAD pixel array with high PDE and timing jitter performance," *International Electron Devices Meeting*, Dec. 2021

[25] E. A. G. Webster, R. L. Nicol, L. Grant, and D. Renshaw, "Per-pixel dark current spectroscopy measurement and analysis in CMOS image sensors," *IEEE Trans. Electron Devices*, vol. 57, no. 9, pp. 2176-2182, Sep. 2010.

Eunsung Park received the B.S. degree in electronic engineering from Gachon University, Gyeonggi-do, South Korea, in 2019. He is currently working toward the M.S. and Ph.D. degrees at the Yonsei University. Since 2019, he has been a Student Researcher with the Post-Silicon Semiconductor Institute, Korea Institute

of Science and Technology (KIST), Seoul, South Korea. His research interests include single-photon detector/sensors, Si-SPADs in CMOS, and CIS technologies.

Won-Yong Ha received the B.S. and M.S. degrees in electrical and electronic engineering from Yonsei University and Yonsei University - Korea Institute of Science and Technology (KIST) association course, Seoul, South Korea in 2020 and 2022, respectively. Since 2022, he has been the Ph.D. Student with Advanced Ouantum Architecture

Laboratory (AQUA) Laboratory, École Polytechnique Fédérale de Lausanne, Neuchâtel, Switzerland. His current research interests include the design and modeling of deep submicron Si-SPAD and SPAD-based detector fabricated in CMOS and BCD technologies.

Hyo-Sung Park received the B.S. degree in Semiconductor Science & Technology from Jeonbuk National University, Jeonju, South Korea, in 2020. Since 2020, he has been working toward the M.S. and Ph.D. degrees at the Yonsei University and Korea Institute of Science and Technology (KIST), Seoul, South Korea. His research interests include single-

photon avalanche diodes, pixel circuits for CMOS SPADs, and LiDAR/D-ToF sensors and applications.

**Doyoon Eom** received the B.S. degree in electrical and electronic engineering from Yonsei University, Seoul, South Korea, in 2020. Since 2021, he has been working toward the M.S. degree at the Yonsei University and Korea Institute of Science and Technology (KIST), Seoul, South Korea. His research interests include single-photon avalanche diodes, LiDAR

sensors and applications, CMOS-compatible photodetectors, and avalanche-mode light emitting diodes.

Hyun-Seung Choi received the B.S. degree in electrical and electronic engineering from Chung-Ang University, Seoul, South Korea, in 2021. Since 2021, he has been working toward the M.S. and Ph.D. degrees at the Yonsei University and Korea Institute of Science and Technology (KIST), Seoul, South Korea. His research interests include single-

photon avalanche diodes, LiDAR sensors and applications, and equivalent circuit modeling for CMOS SPADs.

Dae-Hwan Ahn was born in Jeollabuk-do, Korea, on June 8, 1989. He received the B.S degree in electric and electronic engineering from the University of Toyama, Toyama, Japan in 2014, and M.S. and Ph.D. degrees in electronic engineering from the University of Tokyo, Tokyo, Japan, in 2016 and 2019, respectively. He currently holds a post-

doctoral position with the Center for Opto-Electronic Materials and Devices, Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology (KIST). His recent interests focus on the technologies of advanced CMOS devices.

Woo-Young Choi (M'92) received the B.S., M.S., and Ph.D. degrees in electrical engineering and computer science from the Massachusetts Institute of Technology, Cambridge, MA, USA, in 1986, 1988, and 1994, respectively. His doctoral dissertation concerned the investigation of molecular-beam epitaxygrown InGaAlAs laser diodes for

fiber-optic applications. From 1994 to 1995, he was a Postdoctoral Research Fellow at NTT Opto-Electronics Laboratories, where he worked on femtosecond all-optical switching devices based on low-temperature grown InGaAlAs quantum wells. In 1995, he joined the Department of

Electrical and Electronic Engineering, Yonsei University, Seoul, South Korea, where he is currently a professor. His research interests include high-speed circuits and systems that include high-speed electronic circuits, silicon photonics, and Si image sensors.

Myung-Jae Lee (S'08–M'13) received the B.S., M.S., and Ph.D. degrees in electrical and electronic engineering from Yonsei University, Seoul, South Korea, in 2006, 2008, and 2013, respectively. His doctoral dissertation concerned silicon avalanche photodetectors fabricated with standard CMOS/BiCMOS technology.

From 2013 to 2017, he was a Postdoctoral Researcher with the faculty of electrical engineering, Delft University of Technology (TU Delft), Delft, The Netherlands, where he worked on single-photon sensors and applications based on single-photon avalanche diodes. In 2017, he joined the school of engineering, École Polytechnique Fédérale de Lausanne (EPFL), Neuchâtel, Switzerland, as a Scientist, working on advanced single-photon sensors/applications coordinating/managing several research projects as a Co-Principal Investigator. Since 2019, he has been a Principal Investigator/Principal Research Scientist with the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology (KIST), Seoul, South Korea, where he has led the research and development of next-generation single-photon detectors and sensors for various applications. His research interests have spanned from photodiodes/photodetectors to single-photon detectors/sensors, concentrating since 2006 on CMOS-compatible avalanche photodetectors and singlephoton avalanche diodes and applications thereof (e.g., LiDAR, ToF, 3D vision, biophotonics, quantum photonics, space, security, silicon photonics, optical interconnects, etc.).