# Doping Engineering for PDP Optimization in SPADs Implemented in 55-nm BCD Process

Feng Liu<sup>®</sup>, *Member, IEEE*, Claudio Bruschini<sup>®</sup>, *Senior Member, IEEE*, Eng-Huat Toh<sup>®</sup>, *Member, IEEE*, Ping Zheng<sup>®</sup>, Yongshun Sun, Vinit Dhulla, Elgin Quek<sup>®</sup>, *Member, IEEE*, Myung-Jae Lee<sup>®</sup>, *Member, IEEE*, and Edoardo Charbon<sup>®</sup>, *Fellow, IEEE*

Abstract—We introduce a new family of single-photon avalanche diodes (SPADs) with enhanced depletion regions in a 55-nm Bipolar-CMOS-DMOS (BCD) technology. We demonstrate how to systematically engineer doping profiles in the main junction and in deep p-well layers to achieve high sensitivity and low timing jitter. A family of sub 10  $\mu$ m SPADs was designed and fully characterized. With the increase of the well-defined depletion region, the breakdown voltages of three variants are 17.1, 20.6, and 23.0 V, respectively, the peak PDP wavelengths are 450 nm, 540 nm, and 640 nm, respectively. The timing jitter below 50 ps (FWHM) at 5 V excess bias voltage are achieved in SPAD1 and SPAD2. SPAD3 shows a high PDP over a wide spectral range, with a peak PDP of 41.3% at 640 nm, and 22.3% at 850 nm, and the timing jitter 96 ps at 3 V excess bias voltage. The proposed SPADs are suitable to low-pitch, large-format image sensors for high-speed, time-resolved applications and quantum imaging.

*Index Terms*—Single-photon avalanche diode (SPAD), Bipolar-CMOS-DMOS (BCD), doping engineering, single-photon imaging, quantum imaging.

#### I. INTRODUCTION

S INGLE-PHOTON avalanche diodes (SPADs) in monolithic CMOS technology [1] have been receiving great attention in recent years for scientific, industrial, and consumer applications, such as time-of-flight (TOF) sensing [2], [3], [4], low-light photon counting and imaging [5], [6], biomedical imaging [7], [8], quantum random number generation (QRNG) [9]. However, CMOS SPADs using advanced technology nodes, below 180 nm, tend to have limited photon detection probability (PDP) in a small range of wavelengths and generally low sensitivity in

Manuscript received 10 May 2023; revised 23 October 2023 and 5 January 2024; accepted 6 January 2024. Date of publication 9 January 2024; date of current version 23 January 2024. (Corresponding author: Feng Liu; Myung-Jae Lee; Edoardo Charbon.)

This work did not involve human subjects or animals in its research.

Feng Liu, Claudio Bruschini, and Edoardo Charbon are with the Advanced Quantum Architecture Laboratory (AQUA), École Polytechnique Fédérale de Lausanne (EPFL), 2000 Neuchâtel, Switzerland (e-mail: feng.liu@epfl.ch; claudio.bruschini@epfl.ch; edoardo.charbon@epfl.ch).

Eng-Huat Toh, Ping Zheng, Yongshun Sun, Vinit Dhulla, and Elgin Quek are with the GlobalFoundries Singapore Pte., Ltd., Singapore 738406 (e-mail: enghuat.toh@globalfoundries.com; ping.zheng@globalfoundries.com; yongshun.sun@globalfoundries.com; vinit.dhulla@globalfoundries.com; elgin.quek@globalfoundries.com).

Myung-Jae Lee is with the Post-Silicon Semiconductor Institute (PSI), Korea Institute of Science and Technology (KIST), Seoul 02792, South Korea (e-mail: mj.lee@kist.re.kr).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSTQE.2024.3351676.

Digital Object Identifier 10.1109/JSTQE.2024.3351676

near-infrared (NIR) spectral range, due to narrow depletion regions available in these technologies [10].

Significant improvements in NIR and an overall wide spectral range has recently been achieved in submicron CMOS technologies [10], [11], [12], [13], [14] and the use of electrical microlensing [15], also known as charge focusing [16], has been shown to be useful to improve PDP. Electrical microlensing consists of forcing photo-generated carriers to drift towards the multiplication region by gradual doping profiles or non-vertical electric fields. However, wide and deep depletion regions appear to be the most effective means to improve NIR PDP. For instance, Webster et al. have achieved over 40% PDP from 410 nm to 760 nm at high excess bias by burying the multiplication region in 130 nm CMOS technology. Niclass et al. have used fully depleted SPAD structures in 180 nm CMOS technology achieved PDP of 64.8% and 24% at 610 nm and 850 nm, respectively at moderate excess bias.

Recently, advanced backside illuminated (BSI) 3D stacking technologies have emerged with high fill factor, making high NIR PDP SPAD sensors possible. A BSI charge-focusing SPAD achieved a PDE (photon detection efficiency) of 24.4% at the wavelength of 940 nm with optical microlenses and a dedicated light trapping technique [6]. Another work reported a PDE of 21.8% for only 2.5  $\mu m$  pitch with an optimized gapless microlens and pyramid surface for diffraction (PSD) [17]. The PDE of 36.5% at 940 nm, the world's highest value so far, was achieved by combining dual diffraction and 2  $\times$  2 on-chip lens [18]. However, the BSI technology typically is high cost, and requires long delivery time.

In this paper, we report on a new family of frontside-illuminated (FSI) SPADs with a pitch of 8.5  $\mu$ m characterized by fully depleted main junction and 3 different depletion DPW layers, with the potential of being miniaturized further. We first demonstrate how to systematically engineer the doping profile of the main junction and of the deep p-well layers, and then fully characterize the impact of doping engineering in small SPADs. The proposed structures are called SPAD1, SPAD2, and SPAD3, where SPAD1 and SPAD2 are optimized for timing jitter, with less than 50 ps (FWHM) at 5 V excess bias voltage, while SPAD3 was red and NIR enhanced, with a comparably low timing jitter.

#### II. SPAD STRUCTURE AND SIMULATION

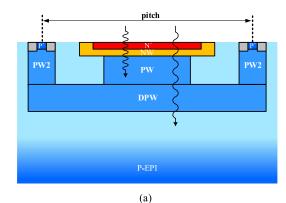

Fig. 1(a) shows the cross-section of the FSI SPAD family in 55 nm BCD process. The SPAD is based on a shallow N-well

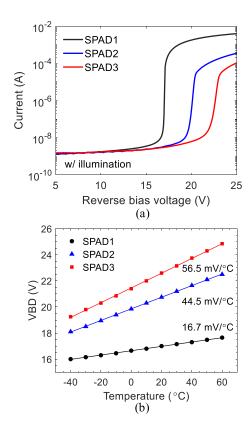

Fig. 1. (a) Simplified cross-section of the proposed SPAD. The structure is based on shallow NW and PW layers. Three different DPW layers are also implemented. All 3 SPADs have the same drawn avalanche area and pitch. (b) The simplified doping profile versus depth below silicon surface. Layers DPW1-3 are used in SPAD1-3, respectively.

(NW) and P-well (PW) junction. The pitch is 8.5  $\mu$ m. All the SPADs presented in this study were designed and realized in a round shape with an avalanche diameter of 4.4  $\mu$ m, achieving a fill factor of 21%. Based on the achieved results, a parameter optimization can be performed to achieve a higher fill factor in future generations. Fig. 1(b) shows the doping profile versus depth below surface. The substrate features a gradient of p-type doping in the epitaxial layer, and the SPAD incorporates three different deep P-well (DPW) layers below the junction.

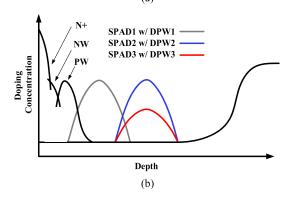

Doping engineering is employed in both the main junction and deep p-well layers. Fig. 2 shows simulations of the relative electric field, as well as the depletion layer boundaries. For the main junction, the avalanching junction is engineered through shallow NW and PW layers and optimized to achieve a high avalanche gain and wide depletion region. Significant efforts are dedicated to fine-tuning the fully depleted PW layer to achieve a higher breakdown probability. For the different DPW layers, the depletion region can be well defined in depth, while photo-generated carriers in the depletion region can quickly drift towards the avalanching junction.

## III. RESULTS AND DISCUSSION

# A. I-V Characteristics

The static current/voltage curves of the proposed SPADs were measured using a semiconductor analyzer, revealing extremely

Fig. 2. Simulation results depicting the electric field as well as the depletion layer boundaries for SPAD1 (a), SPAD2 (b), and SPAD3 (c) at 3V excess bias voltage. The junction is engineered to achieve a wide depletion region.

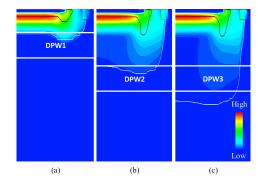

Fig. 3. (a) SPADs current as a function of reverse bias voltage with illumination. (b) Breakdown voltage as a function of temperature for 3 different SPADs.

low dark current levels in the pA range for all three variants. The current-voltage curves with illumination are shown in Fig. 3(a).

With different DPW layers, the corresponding breakdown voltages are 17.1, 20.6, and 23.0 V, respectively. This means that the breakdown voltage is related to both the main junction and the DPW layers for miniaturized fully depleted SPAD. Besides, it is clearly shown that SPAD2 and SPAD3 achieve lower photo-current above the breakdown voltage. Fig. 3(b) shows the breakdown voltage as a function of temperature from  $-40\,^{\circ}$ C to 60 °C. The extracted temperature coefficients are 16.7, 44.5, and 56.5 mV/°C, respectively. With a thicker depletion region, the temperature coefficients grow larger [19].

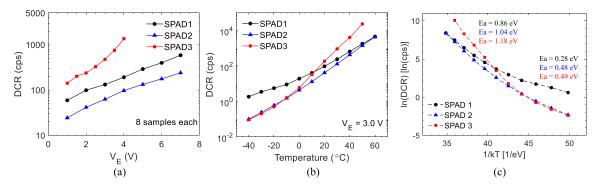

Fig. 4. (a) Median DCR at room temperature. The data is obtained by measuring 8 dies. (b) Temperature dependence of DCR for 3 different SPADs. Measurements were taken from one SPAD sample each from -40 °C to 60 °C. (c) Arrhenius plot of the DCR for 3 different SPADs at the excess bias voltage of 3 V.

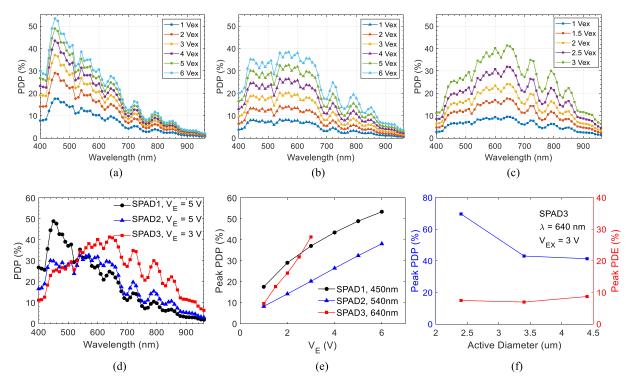

Fig. 5. Measured PDP as a function of wavelength for SPAD1 (a), SPAD2 (b), and SPAD3 (c) from 400 nm to 960 nm with the step of 10 nm. (d) PDP comparison as a function of wavelength for 3 different SPADs. (e) PDP as a function of excess bias voltage at the peak wavelength for 3 different SPADs. (f) Peak PDP and PDE as a function of draw active diameter of SPAD3. The guard ring width is same during the scaling. The PDP is calculated based on the draw active area.

## B. Dark Count Rate

The dark count rates (DCRs) of 8 samples for each SPADs were measured at room temperature. Fig. 4(a) shows the median DCR as a function of the excess bias voltage. The median DCR of SPAD1 is 132 cps and 290 cps at 3 V and 5 V excess bias voltage, respectively. This can be further reduced through optimizing the guard ring to decrease the electitric field in the junction edge. It is clear that SPAD2 shows the best DCR performance, with the median DCR of 62.3 cps and 132.2 cps at 3 V and 5 V excess bias voltage, respectively. The median DCR of SPAD3 is 474.2 cps at 3 V excess bias voltage. SPAD3 shows the worst DCR performance, due to deep-level traps in the wide depletion region. The temperature dependence of DCR at 3 V excess bias voltage is shown in Fig. 4(b), whereas SPAD2 and SPAD3 show a strong temperature dependence. As the thermal generation is

the main source of dark count rate, activation energies can be extracted from the temperature dependence [20]. The Arrhenius plot for 3 different SPADs is shown in Fig. 4(c). At high temperature, where SRH (Shockley-Read-Hall) effect is the dominant, the corresponding activation energies of the SPAD family is 0.86, 1.04, 1.18 eV, respectively. With the temperature cooling down, the tunneling mechanism becomes more important. The the corresponding activation energies of the SPAD family is 0.28, 0.48, 0.49 eV, respectively

## C. Photon Detection Probability

PDP measurement was taken at room temperature with 10 nm interval using the continuous light technique [21]. The calculated PDP is based on the draw avalanche area. Fig. 5 shows the measured PDP results from 400 nm to 960 nm with the step of

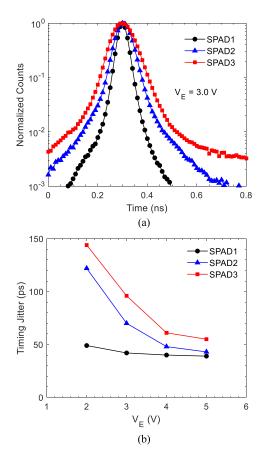

Fig. 6. (a) Timing jitter response for an 850 nm laser at 3 V excess bias voltage. The jitter of the laser is 32 ps. (b) Timing jitter (FWHM) as a function of excess bias voltage.

10 nm for all the SPADs. With the different DPW layers, it is clearly shown that the peak PDP wavelengths are observed to be 450 nm, 540 nm, and 640 nm, respectively. SPAD1 achieves peak PDP of 48.9% at 450 nm, 6.7% at 850 nm, and 2.4% at 940 nm at 5 V excess bias voltage. SPAD2 achieves peak PDP of 32.4% at 540 nm, 10.7% at 850 nm, and 3.7% at 940 nm at 5 V excess bias voltage. Thanks to the wider depletion region, SPAD3 shows a high PDP over a wide spectral range, with peak PDP of 41.3% at 640 nm, 22.3% at 850 nm, and 8.3% at 940 nm at 3 V excess bias voltage. This broad spectral response from visible to NIR holds great potential for a diverse applications. The peak PDP as a function of excess bias voltage is shown in Fig. 5(e). The peak PDP of SPAD3 shows the strongest dependence on excess bias voltage. The miniaturization of SPAD plays a crucial role in the development of large-format image sensors. During the pitch scaling down, same guard ring width is maintained. However, the reduction in SPAD pitch presents challenges in accurately evaluating the avalanche area through light emission test, and the process mismatch can have a higher impact. Fig. 5(f) shows the peak PDP and PDE of SPAD3 as a function of draw active diameter. The minimum active diameter is 2.4  $\mu$ m, the corresponding pitch is 6.5  $\mu$ m. We can see that the peak PDE decreases only a bit during the pitch scaling from 8.5  $\mu$ m to  $6.5 \mu m$ . The lateral charge collection by drift-diffusion can help enhance the sensitivity thanks to the fully depleted structure.

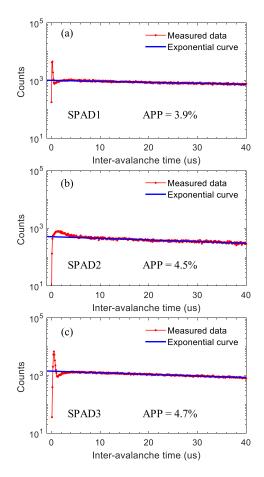

Fig. 7. Afterpulsing probability: measured inter-avalanche time histogram at room temperature. (a)–(b) SPAD1 and SPAD2 at 5 V excess bias voltage. (c) SPAD3 at 3 V excess bias voltage. The dead time of each SPAD was 100 ns.

## D. Timing Jitter

A dedicated printed circuit board equipped with a fast comparator was utilized to evaluate the timing jitter. A low threshold voltag, which was close to the baseline of the output pulse, was applied to detect the SPAD signal at the onset of the avalanche phenomenon. Fig. 6(a) shows the timing jitter at 3 V excess bias voltage with an 850-nm laser source (NKT Photonics PiL085X). The jitter of the laser is 32 ps. The evolution of jitter as a function of the excess bias voltage is shown in Fig. 6(b). A timing jitter of 42, 70, and 96 ps (FWHM) is achieved at 3 V excess bias voltage, respectively. The timing jitter at same excess voltage increases clearly with the expansion of the depletion region, because the timing fluctuation of the photo-generated carriers upward towards the avalanching area will be dominant.

## E. Afterpulsing Probability

Under constant low light condition, the distribution of interavalanche time follows poisson statistics. An afterpulse can be triggered by trapped carriers during recharging. The measured afterpulsing probability (APP) is shown in Fig. 7. A high threshold voltage of the comparator, which was close to the peak of the output pulse, was applied to detect the output pulse. The dead time is about 100 ns. The afterpulsing probability of SPAD1 and

| Parameter                    | This work<br>(SPAD1) | This work<br>(SPAD2) | This work<br>(SPAD3) | [10]             | [11]           | [12]                         | [13]            | [14]          |

|------------------------------|----------------------|----------------------|----------------------|------------------|----------------|------------------------------|-----------------|---------------|

| Structure                    | Shallow<br>NW/PW     | Shallow<br>NW/PW     | Shallow<br>NW/PW     | N+/PW            | Deep<br>NW/epi | Deep<br>NW/epi               | Deep<br>NW/PW   | Deep<br>NW/PW |

| Technology (nm)              | 55                   | 55                   | 55                   | 180              | 90             | 130                          | 180             | 180           |

| Pitch (µm)                   | 8.5                  | 8.5                  | 8.5                  | N/A              | N/A            | N/A                          | 25              | N/A           |

| Avalanche area (µm²)         | 15.2                 | 15.2                 | 15.2                 | 78.5             | 32.1           | 50.2                         | 206.9           | 220           |

| Fill Factor (%)              | 21                   | 21                   | 21                   | N/A              | N/A            | N/A                          | 33.1            | 35            |

| VBD (V)                      | 17.1                 | 20.6                 | 23.0                 | 19.7             | 14.9           | 20                           | 20.5            | 20.0          |

| VE (V)                       | 5                    | 5                    | 3                    | 4                | 2.4            | 6                            | 5               | 5             |

| DCR (cps/µm²)                | 19.1                 | 8.7                  | 31.2                 | 30               | ~4.6           | $0.36$ $(V_E = 2 \text{ V})$ | 0.6             | 1.7           |

| PDP Peak (%)                 | 48.9<br>@450 nm      | 32.4<br>@540 nm      | 41.3<br>@640 nm      | 36<br>@600 nm    | 44<br>@690 nm  | 45.2<br>@560 nm              | 64.8<br>@610 nm | 47<br>@570 nm |

| PDP (%)<br>@ 850 nm          | 6.7                  | 10.7                 | 22.3                 | 16               | 21.4           | 15.8                         | 24              | 20            |

| PDP (%)<br>@ 940 nm          | 2.4                  | 3.7                  | 8.3                  | N/A              | 10.1           | 5.7                          | 8.8             | 9.7           |

| Afterpulsing probability (%) | 3.9ª                 | 4.5ª                 | 4.7ª                 | 50ª              | 0.38           | 0.98                         | 0.49            | N/A           |

| Dead time (ns)               | 100a                 | 100 <sup>a</sup>     | 100 <sup>a</sup>     | 750 <sup>a</sup> | 23             | 35                           | 24.9            | N/A           |

| Timing Jitter (ps)<br>FWHM   | 39<br>@850 nm        | 43<br>@850 nm        | 96<br>@850 nm        | 165<br>@790 nm   | 51<br>@470 nm  | 58<br>@654 nm                | 161<br>@635 nm  | N/A           |

TABLE I

PERFORMANCE SUMMARY AND COMPARISON WITH N-ON-P FRONT-SIDE ILLUMINATED SPADS IN CMOS TECHNOLOGY.

<sup>&</sup>lt;sup>a</sup> This value is significantly overestimated with huge parasitic capacitance due to the lack of integrated circuit.

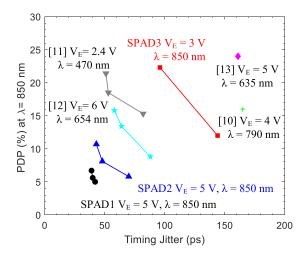

Fig. 8. Performance comparison of the N-on-P SPADs in monolithic CMOS technologies. PDP at 850 nm versus timing jitter at similar excess bias voltages is reported.

SPAD2 was measured to be 3.9%, and 4.5% at 5 V excess bias voltage. The measured afterpulsing probability of SPAD3 was 4.7%. Due to the lack of integrated quench and recharge circuits, a large number of carriers maybe trapped after an avalanche. Thus, the measured afterpulsing probability was significantly overestimated.

## IV. STATE-OF-THE-ART COMPARISON

Fig. 8 shows the PDP and timing jitter comparison of the proposed SPADs with the previously reported N-on-P type SPADs in CMOS technology. The proposed SPAD1 and SPAD2 show less than 50 ps timing jitter at 5 V excess bias voltage. The proposed SPAD3 shows a high PDP at 850 nm, while keeping a low timing jitter at 3 V excess bias voltage. Table I shows the

overall performance of the developed SPADs and comparison with the state-of-the-art SPADs.

#### V. CONCLUSION

We demonstrate the role of doping engineering to widen the depletion region in small SPADs with a pitch of 6.5  $\mu$ m to 8.5  $\mu$ m implemented in a 55-nm BCD process. To demonstrate it practically, a family of SPADs was designed, realized, and fully characterized in this technology. The doping profiles of the avalanching junction layers were optimized to achieve redand NIR-enhanced sensitivity. Experimental evaluation of the proposed SPADs revealed that the PDP peak wavelength can be improved with a wider and deeper depletion region, thereby achieving a high PDP over a wide spectral range, with a peak PDP of 41.3% at 640 nm, and 22.3% at 850 nm, and the timing jitter 96 ps at 3 V excess bias voltage. The technique is suitable for small-pitch SPADs and large-format image sensors, with multi-megapixel resolution, both operating in frontside- and backside-illuminated modes.

#### ACKNOWLEDGMENT

The authors would like to thank GlobalFoundries for fabricating the devices in 55-nm BCD technology.

#### REFERENCES

- E. Charbon, "Single-photon imaging in complementary metal oxide semiconductor processes," *Philos. Trans. Roy. Soc. A*, vol. 372, no. 2012, 2014, Art. no. 20130100.

- [2] C. Niclass, M. Soga, H. Matsubara, M. Ogawa, and M. Kagami, "A 0.18-m CMOS SoC for a 100-m-range 10-frame/s 200× 96-pixel time-of-flight depth sensor," *IEEE J. Solid-State Circuits*, vol. 49, no. 1, pp. 315–330, Jan. 2014.

- [3] S. W. Hutchings et al., "A reconfigurable 3-D-stacked SPAD imager with in-pixel histogramming for flash LIDAR or high-speed time-of-flight imaging," *IEEE J. Solid-State Circuits*, vol. 54, no. 11, pp. 2947–2956, Nov. 2019.

- [4] D. Stoppa et al., "A reconfigurable QVGA/Q3VGA direct time-of-flight 3D imaging system with on-chip depth-map computation in 45/40nm 3Dstacked BSI SPAD CMOS," in *Proc. Int. Image Sensor Workshop*, 2021, pp. 53–56.

- [5] J. Ogi et al., "A 124-dB dynamic-range SPAD photon-counting image sensor using subframe sampling and extrapolating photon count," *IEEE J. Solid-State Circuits*, vol. 56, no. 11, pp. 3220–3227, Nov. 2021.

- [6] K. Morimoto et al., "3.2 megapixel 3D-stacked charge focusing SPAD for low-light imaging and depth sensing," in *Proc. Int. Electron Devices Meeting*, 2021, pp. 20.2.1–20.2.4.

- [7] C. Bruschini, H. Homulle, I. M. Antolovic, S. Burri, and E. Charbon, "Single-photon avalanche diode imagers in biophotonics: Review and outlook," *Light: Sci. Appl.*, vol. 8, no. 1, 2019, Art. no. 87.

- [8] B. Park et al., "5.6 A 400 × 600 fps 117.7 dB-DR SPAD X-Ray detector with seamless global shutter and time-encoded extrapolation counter," in Proc. IEEE Int. Solid-State Circuits Conf., 2023, pp. 100–102.

- [9] N. Massari et al., "A monolithic SPAD-based random number generator for cryptographic application," in *Proc. IEEE 48th Eur. Solid State Circuits Conf.*, 2022, pp. 73–76.

- [10] S. Mandai, M. W. Fishburn, Y. Maruyama, and E. Charbon, "A wide spectral range single-photon avalanche diode fabricated in an advanced 180 nm CMOS technology," *Opt. Exp.*, vol. 20, no. 6, pp. 5849–5857, 2012.

- [11] E. A. Webster, J. A. Richardson, L. A. Grant, D. Renshaw, and R. K. Henderson, "A single-photon avalanche diode in 90-nm CMOS imaging technology with 44% photon detection efficiency at 690 nm," *IEEE Electron Device Lett.*, vol. 33, no. 5, pp. 694–696, May 2012.

- [12] E. A. Webster, L. A. Grant, and R. K. Henderson, "A high-performance single-photon avalanche diode in 130-nm CMOS imaging technology," *IEEE Electron Device Lett.*, vol. 33, no. 11, pp. 1589–1591, Nov. 2012.

- [13] C. Niclass et al., "A NIR-sensitivity-enhanced single-photon avalanche diode in 0.18 μm CMOS," in *Proc. Int. Image Sensor Workshop*, 2015, pp. 8–11.

- [14] A. Katz, T. Blank, A. Fenigstein, T. Leitner, and Y. Nemirovsky, "Active-reset for the N + P single-ended SPAD used in the NIR LiDAR receivers," IEEE Trans. Electron Devices, vol. 66, no. 12, pp. 5191–5195, Dec. 2019.

- [15] C. Veerappan, Y. Maruyama, and E. Charbon, "Silicon integrated electrical micro-lens for CMOS SPADs based on avalanche propagation phenomenon," in *Proc. Int. Image Sensor Workshop*, 2013.

- [16] K. Morimoto, "Charge-focusing SPAD image sensors for low light imaging applications," in *Proc. Int. SPAD Sensor Workshop*, 2020.

- [17] S. Shimada et al., "A SPAD depth sensor robust against ambient light: The importance of pixel scaling and demonstration of a 2.5μm pixel with 21.8% PDE at 940nm," in *Proc. Int. Electron Devices Meeting*, 2022, pp. 37.3.1–37.3.4.

- [18] Y. Fujisaki et al., "A back-illuminated 6 μm SPAD depth sensor with PDE 36.5% at 940 nm via combination of dual diffraction structure and 2× 2 on-chip lens," in *Proc. IEEE Symp. VLSI Technol. Circuits*, 2023, pp. 1–2.

- [19] A. Gulinatti, F. Ceccarelli, M. Ghioni, and I. Rech, "Custom silicon technology for SPAD-arrays with red-enhanced sensitivity and low timing jitter," *Opt. Exp.*, vol. 29, no. 3, pp. 4559–4581, 2021.

- [20] M. Liu et al., "High-performance INGAAS/INP single-photon avalanche photodiode," *IEEE J. Sel. Topics Quantum Electron.*, vol. 13, no. 4, pp. 887–894, Jul./Aug. 2007.

- [21] F. Gramuglia et al., "Engineering breakdown probability profile for PDP and DCR optimization in a SPAD fabricated in a standard 55 nm BCD process," *IEEE J. Sel. Topics Quantum Electron.*, vol. 28, no. 2, Mar./Apr. 2022, Art. no. 3802410.

Claudio Bruschini (Senior Member, IEEE) received the Laurea degree in physics from the University of Genova, Genova, Italy, in 1992, and the Ph.D. degree in applied sciences from Vrije Universiteit Brussel, Brussels, Belgium, in 2002. He is currently a Scientist and Lab Deputy with EPFL's Advanced Quantum Architecture Laboratory. He has authored or coauthored more than 170 articles and conference proceedings and one book. His scientific interests include high energy physics and parallel computing in the early days, to challenging sensor applications in

humanitarian demining, concentrating since 2003 on quantum photonic devices, high-speed and time-resolved 2D/3D optical sensing, and applications thereof (biophotonics, nuclear medicine, basic sciences, security, ranging). He was the co-recipient of the 2012 European Photonics Innovation Award and of the Image Sensors Europe 2019 Award in the category "Best Academic Research Team", and Swiss Medtech Award 2016 finalist. He is an SPIE Senior Member and co-founder of a start-up commercialising selected AQUA lab SPAD designs.

Eng-Huat Toh (Member, IEEE) received the B.Eng. (Hons.) and Ph.D. degrees in electrical and computer engineering from the National University of Singapore, Singapore, in 2004 and 2008, respectively. He is currently a Principal Member of Technical Staff in technology development with GlobalFoundries, Singapore, and works on logic, non-volatile memory (NVM) technology, next generation memories, such as STT MRAM and RRAM, magnetic sensors, and optical sensors. He has authored or coauthored more than 70 journal articles and conference papers and

holds more than 170 patents in the field of semiconductor.

Ping Zheng received the master's degree in materials science from Shanghai University, Shanghai, China, in 2004. She is currently a Member of Technical Staff in technology development with GlobalFoundries, Singapore, and works on logic, high voltage devices, magnetic sensors, and optical sensors.

Yongshun Sun received the B. Eng. degree (with Hons.) in electrical and electronics engineering and the Ph.D. degree in electrical and electronics engineering from Nanyang Technological University, Singapore, in 2007 and 2012, respectively. Since 2014, he has been with Globalfoundries Singapore, Singapore, where he is currently a member of technical staff in technology development department.

Feng Liu (Member, IEEE) received the B.S. degree from the College of Physics, Sichuan University, Chengdu, China, in 2014, and the Ph.D. degree from the Department of Engineering Physics, Tsinghua University, Beijing, China, in 2020. Since 2020, he has been a Research Scientist with AQUA Laboratory, Ecole Polytechnique Fédérale de Lausanne (EPFL), Neuchâtel, Switzerland. From 2016 to 2017, he was a Visiting Scholar with Brookhaven National Laboratory (BNL), Upton, NY, USA. His research interests include CMOS SPAD device and image sensor devel-

opment, integrated circuit for radiation detection and imaging.

Vinit Dhulla received the Ph.D. degree in electrical engineering from Stony Brook University. He is the Deputy Director of Product Management with GLOBALFOUNDRIES (GF), focusing on imaging and sensing technologies for consumer, Auto and IoT end markets. Before GF, he spent more than 13 years with Voxtel-Inc in various roles, leading the development of LiDAR sensor technology, receiver products, and LiDAR demo systems. He also managed numerous Small Business Innovation Research programs as Principal Investigator and Program Man-

ager. Voxtel-Inc was acquired by Allegro Microsystems in 2020. At Allegro, he led a cross-functional engineering team developing lidar sensors and demo systems for automotive market, before joining GF in 2021.

Elgin Quek (Member, IEEE) received the B.Eng. degree (with first-class Hons.) in electrical engineering from the National University of Singapore, Singapore, and the M.S. degree in electrical engineering from Stanford University, Stanford, CA, USA. From 1988 to 2009, he was with Chartered Semiconductor, Singapore, where he worked on process integration, yield enhancement, device engineering, and SPICE modeling for CMOS and floating gate memories. Since 2009, he has been with GLOBALFOUNDRIES Singapore, where he is currently a GF Senior Fellow

in Technology Development responsible for device design for CMOS-based logic, SRAM, non-volatile memory, display-driver and sensor technologies. He has coauthored more than 40 technical papers and holds more than 150 U.S. patents.

Myung-Jae Lee (Member, IEEE) received the B.S., M.S., and Ph.D. degrees in electrical and electronic engineering from Yonsei University, Seoul, South Korea, in 2006, 2008, and 2013, respectively. His doctoral dissertation concerned silicon avalanche photodetectors fabricated with standard CMOS/BiCMOS technology. From 2013 to 2017, he was a Post-doctoral Researcher with the Faculty of Electrical Engineering, Delft University of Technology (TU Delft), Delft, The Netherlands, where he worked on single-photon sensors and applications based on

single-photon avalanche diodes. In 2017, he joined the School of Engineering, École Polytechnique Fédérale de Lausanne (EPFL), Neuchâtel, Switzerland, as a Scientist, working on advanced single-photon sensors/applications and coordinating/managing several research projects as a Co-Principal Investigator. Since 2019, he has been a Principal Investigator/Principal Research Scientist with the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology (KIST), Seoul, where he has led the research and development of next-generation single-photon detectors and sensors for various applications. His research interests include photodiodes/photodetectors to single-photon detectors/sensors, concentrating since 2006 on CMOS-compatible avalanche photodetectors and single-photon avalanche diodes and applications thereof (e.g., LiDAR, ToF, 3D vision, biophotonics, quantum photonics, space, security, silicon photonics, and optical interconnects).

Edoardo Charbon (Fellow, IEEE) received the Diploma from ETH Zurich, Zürich, Switzerland, in 1988, the M.S. degree from the University of California at San Diego, San Diego, CA, USA, in 1991, and the Ph.D. degree from the University of California at Berkeley, Berkeley, CA, USA, in 1995, all in electrical engineering and EECS. He has consulted with numerous organizations, including Bosch, X-Fab, Texas Instruments, Maxim, Sony, Agilent, and the Carlyle Group. From 1995 to 2000, he was with Cadence Design Systems, where he was the Architect of the

company's initiative on information hiding for intellectual property protection. In 2000, he joined as the Chief Architect with Canesta Inc., where he led the development of wireless 3-D CMOS image sensors. Since 2002, he has been a member of the Faculty of EPFL, where he is a Full Professor. From 2008 to 2016, he was with Delft University of Technology's as a Full Professor and Chair of VLSI design. He has been the driving force behind the creation of deep-submicron CMOS SPAD technology, which is mass-produced since 2015 and is present in telemeters, proximity sensors, and medical diagnostics tools. He has authored or coauthored more than 400 papers and two books, and he holds 24 patents. His research interests include 3-D vision, LiDAR, FLIM, FCS, NIROT to super-resolution microscopy, time-resolved Raman spectroscopy, and cryo-CMOS circuits and systems for quantum computing. Dr. Charbon is a distinguished Visiting Scholar of the W. M. Keck Institute for Space at Caltech, a Fellow of the Kavli Institute of Nanoscience Delft, and a distinguished Lecturer of the IEEE Photonics Society.