# SPAD Developed in 55 nm Bipolar-CMOS-DMOS Technology Achieving Near 90% Peak PDP

Won-Yong Ha, *Student Member, IEEE*, Eunsung Park , Doyoon Eom, Hyo-Sung Park, Francesco Gramuglia, *Member, IEEE*, Pouyan Keshavarzian, *Student Member, IEEE*, Ekin Kizilkan, *Student Member, IEEE*, Claudio Bruschini, *Senior Member, IEEE*, Daniel Chong, Shyue Seng Tan, Michelle Tng, Elgin Quek, *Member, IEEE*, Edoardo Charbon, *Fellow, IEEE*, Woo-Young Choi, *Member, IEEE*, and Myung-Jae Lee, *Member, IEEE*

Abstract—We present a single-photon avalanche diode (SPAD) developed in 55 nm bipolar-CMOS-DMOS (BCD) technology, which achieves high photon detection probability (PDP) while its breakdown voltage is lower than 20 V. To enhance the PDP performance, the SPAD junction is optimized with lightly-doped-drain and high-voltage-well layers which are provided in the BCD process. In addition, the dielectric layers over the SPAD are properly etched to reduce multilayer reflections so that the photon collection efficiency can be maximized. The SPAD achieves a peak PDP of 89.4% at 450 nm wavelength with the excess bias voltage of 7 V, while its breakdown voltage is 16.1 V. At the same bias condition, the device shows a dark count rate (DCR) of 38.2 cps/ $\mu$ m<sup>2</sup>. It also achieves a timing jitter of 55 ps at 940 nm with the 7 V excess bias. This new high-performance SPAD implemented in such an advanced node BCD technology operating at a low breakdown voltage is expected to have a major impact on several single-photon applications, especially biomedical sensing and imaging.

Manuscript received 1 April 2023; revised 28 June 2023; accepted 31 July 2023. Date of publication 9 August 2023; date of current version 15 December 2023. This work was supported by the Korea Institute of Science and Technology through Institutional Program under Grant 2E32242. (Corresponding authors: Edoardo Charbon; Woo-Young Choi; Myung-Jae Lee.)

Won-Yong Ha was with the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology, Seoul 02792, South Korea, and with the Department of Electrical and Electronic Engineering, Yonsei University, Seoul 03722, South Korea. He is now with the Institute of Electrical and Microengineering, École Polytechnique Fédérale de Lausanne, 2002 Neuchatel, Switzerland (e-mail: james62473414@gmail.com).

Eunsung Park, Doyoon Eom, and Hyo-Sung Park are with the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology, Seoul 02792, South Korea, and also with the Department of Electrical and Electronic Engineering, Yonsei University, Seoul 03722, South Korea (e-mail: es.park@kist.re.kr; dja1995@kist.re.kr; phs0817@kist.re.kr).

Francesco Gramuglia, Daniel Chong, Shyue Seng Tan, Michelle Tng, and Elgin Quek are with the GLOBALFOUNDRIES Singapore Pte. Ltd., Singapore 738406 (e-mail: francesco.gramuglia@epfl.ch; daniel.chong@globalfoundries.com; jason.tan@globalfoundries.com; jinghuamichelle.tng@globalfoundries.com; elgin.quek@globalfoundries.com).

Pouyan Keshavarzian, Ekin Kizilkan, Claudio Bruschini, and Edoardo Charbon are with the Institute of Electrical and Microengineering, École Polytechnique Fédérale de Lausanne, 2002 Neuchatel, Switzerland (e-mail: pouyan.keshavarzian@epfl.ch; ekin.kizilkan@epfl.ch; claudio.bruschini@epfl.ch; edoardo.charbon@epfl.ch).

Woo-Young Choi is with the Department of Electrical and Electronic Engineering, Yonsei University, Seoul 03722, South Korea (e-mail: wchoi@yonsei.ac.kr).

Myung-Jae Lee is with the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology, Seoul 02792, South Korea (e-mail: mj.lee@kist.re.kr).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSTQE.2023.3303678.

Digital Object Identifier 10.1109/JSTQE.2023.3303678

Index Terms—Avalanche photodiode (APD), bipolar-CMOS-DMOS (BCD) technology, detector, electronic photonic integration, fluorescence correlation spectroscopy (FCS), fluorescence lifetime imaging microscopy (FLIM), frontside illumination (FSI), Geiger-mode avalanche photodiode (G-APD), high-volume manufacturing, integrated optics device, integration of photonics in standard CMOS technology, optical sensing, optical sensor, photodetector, photodiode, photomultiplier, photon counting, photon timing, semiconductor, sensor, silicon, single-photon avalanche diode (SPAD), single-photon counting, single-photon imaging, standard CMOS technology.

#### I. INTRODUCTION

INGLE-PHOTON avalanche diodes (SPADs) are devices in high demand for various applications, especially in biomedical practices [1], [2]. They could replace photomultiplier tubes (PMTs) thanks to their compactness and high sensitivity in tomography applications such as near-infrared optical tomography (NIROT) [3] and time-of-flight positron emission tomography (ToF-PET) [4]. They also play a key role in fluorescence-lifetime imaging microscopy (FLIM) [5], fluorescence correlation spectroscopy (FCS) [6], and Raman spectroscopy [7], [8], [9], [10], [11].

SPADs fabricated in CMOS technology are of great interest due to such advantages as low-cost fabrication, mass production, and monolithic integration capability with circuitry. Furthermore, with the technology scaling down, the advantages of CMOS-SPADs are becoming more pronounced in terms of pixel resolution, footprint, and functionality. Many attempts have therefore been made to develop SPADs based on advanced CMOS technologies [12], [13]. As technology nodes scale, however, the doping concentrations of implants typically increase, which presents a challenge for the development of CMOS-SPADs as it narrows the width of the depletion region, resulting in a higher dark count rate (DCR) and lower photon detection probability (PDP) [13], [14].

To address this problem, Gramuglia et al. [15] and Keshavarzian et al. [16] reported a SPAD based on 55 nm bipolar-CMOS-DMOS (BCD) technology. The BCD technology provides deeper and/or lower-doped layers compared to CMOS technology, and this facilitates the implementation of SPADs with very low DCR and high PDP at higher excess bias voltages  $(V_E)$ . Also, the BCD technology makes high-voltage transistors

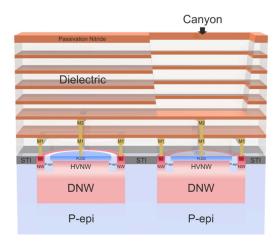

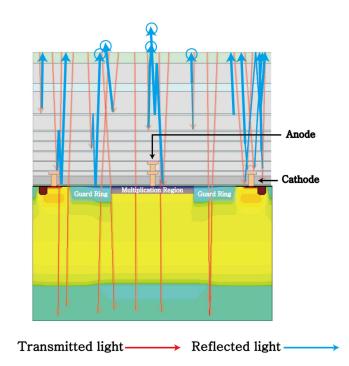

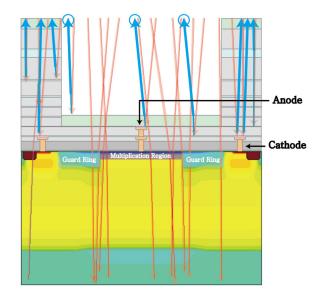

Fig. 1. Cross-sections of the BCD-SPADs.

available to designers, thus enabling pixels that allow for a high excess bias voltage [16]. One downside of the BCD-SPAD is the relatively high breakdown voltage ( $V_B$ ), typically over 30 V, which results in higher power consumption and limits its applicability range.

Another approach is to use backside-illuminated (BSI) CMOS image sensor (CIS) technology with 3D stacking. While the recent reports by Shimada et al. [17] and Morimoto et al. [18] demonstrated excellent SPAD performance based on 90 nm BSI CIS processes, the BSI 3D stacking approach may not be appropriate for cost-effective applications. Furthermore, until now, both of these approaches have been commonly unavailable from a foundry.

In this article, we present a SPAD fabricated in 55 nm BCD technology. In order to achieve high performance while maintaining the  $V_B$  less than 20 V, the junction is formed with P-type lightly-doped-drain (PLDD) and high-voltage N-well (HVNW) layers. In addition, the dielectric layers above the SPAD are properly etched away to reduce the multilayer reflection. The resulting SPAD achieves outstanding performance in terms of PDP, DCR, and timing jitter with a low breakdown voltage of 16.1 V.

#### II. DEVICE STRUCTURE AND SIMULATION

#### A. Device Structure

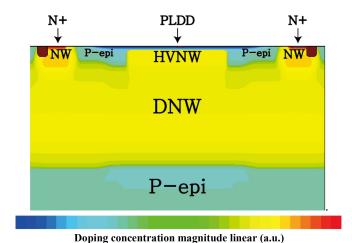

Fig. 1 shows cross-sections of two SPAD configurations Both SPADs have the identical device structure, where PLDD and HVNW layers form a 9  $\mu$ m diameter PN junction and a total diameter of 14.4  $\mu$ m as shown in Fig. 2. Both layers are standard in this technology, and the merits of using such layers are: (i) the PLDD generates less implantation-induced defects, enabling low-noise SPAD operation, and (ii) the HVNW provides a proper depletion region with the PLDD layer, which is wide enough to prevent band-to-band tunneling but, at the same time, not so wide as to significantly increase the breakdown voltage. To prevent premature edge breakdown, the SPADs are designed in a round shape and a P-epi guard ring with a width of 2  $\mu$ m is implemented at the edge of the junction. A lightly-doped deep

Fig. 2. Doping-concentration profile of the BCD-SPADs.

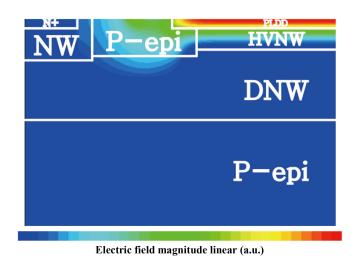

Fig. 3. E-field profile of the BCD-SPAD obtained with TCAD simulation.

N-well (DNW) is used for the cathode connection, and it also makes the absorption region larger and consequently increases the PDP. To maximize the SPAD detection efficiency further, a few of the SPAD's dielectric layers above the multiplication and guard-ring regions are etched away, thus forming a *canyon*. We implemented two SPADs with and without the canyon. By comparing their performance, the effect of the canyon can be clearly demonstrated.

# B. TCAD Simulation

In order to check the SPADs' E-field profile, TCAD simulation using Okuto's avalanche breakdown model was performed when the  $V_B$  and  $V_E$  were 16 V and 7 V, respectively [19]. As can be seen in Fig. 3, the E-field strength at the edge of the junction is reduced by the P-epi guard ring.

Therefore, we are able to avoid the premature edge breakdown phenomenon and form a high and uniform E-field at the planar PLDD/HVNW junction. In addition, the simulation to check the breakdown probability of the device was conducted using

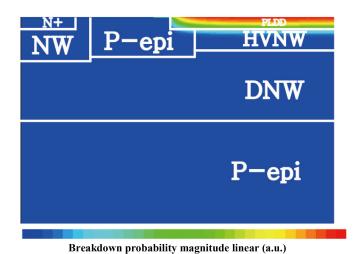

Fig. 4. Breakdown probability profile of the BCD-SPAD obtained with TCAD simulation.

Fig. 5. Simplified raytracing result of the BCD-SPAD without the canyon obtained with TCAD simulation.

the McIntyre model as shown in Fig. 4 [20]. With the shallow junction, it is expected that the proposed devices achieve high PDP at  $400{\sim}500$  nm which corresponds to about 0.1 to 1  $\mu$ m penetration depth of photons inside silicon. Finally, the effects of the canyon etch were investigated using ray-tracing simulations. In these simulations, the transmitted and reflected light is represented by the reddish and bluish arrows, respectively. The several dielectric layers on top of the non-canyon-etched SPAD result in many reflections as shown in Fig. 5. On the other hand, the light reflections are reduced in the SPAD with the canyon etch as can be seen in Fig. 6. The simulation results indicate

Fig. 6. Simplified raytracing result of the BCD-SPAD with the canyon obtained with TCAD simulation.

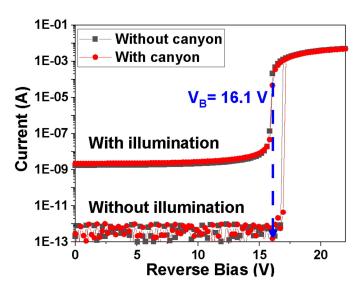

Fig. 7.  $\,$  I-V characteristics of the BCD-SPADs under dark and illumination conditions.

that more photons reach the active region with the canyon etch, thereby leading to a higher PDP.

# III. EXPERIMENT RESULTS

#### A. I-V Characteristics

Fig. 7 shows the I-V characteristics of the fabricated BCD-SPADs with and without illumination measured using a semi-conductor device analyzer at room temperature. As both SPADs are based on the same front-end-of-line (FEOL), they show similar results, small dark currents and high avalanche multiplication. Thanks to the high doping concentration of the PLDD,

Fig. 8. Results of light emission tests of BCD-SPADs: (a) SPAD without the canyon before  $V_B$ , (b) SPAD without the canyon at  $V_E=3$  V, (c) SPAD with the canyon before  $V_B$ , (d) SPAD with the canyon at  $V_E=3$  V.

both SPADs have a low  $V_B$  of about 16.1 V, matching well with our expectations from the TCAD simulation. In addition, the dark currents of both SPADs increase at a higher voltage than the  $V_B$  under illumination, which indicates the number of dark carriers is relatively low [4].

## B. Light Emission Test

Light emission tests of both SPADs are conducted to confirm the suppression of premature edge breakdown as shown in Fig. 8. The light-emitting area indicates the avalanche multiplication region when a higher excess bias than its  $V_B$  is applied. Therefore, the test results clearly demonstrate that a high E-field, over the critical E-field of silicon, is uniformly formed in the planar junction of both SPADs. Moreover, as the edge of the junction is not brighter than the center, the devices don't exhibit any premature edge breakdown, which was expected from TCAD simulation results shown in Figs. 3 and 4.

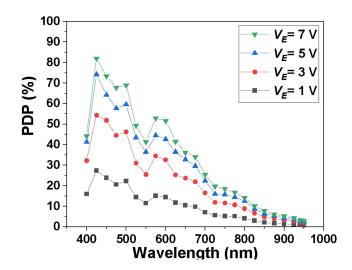

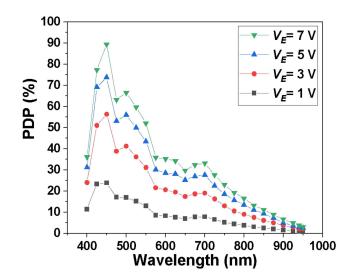

#### C. Photon Detection Probability

The PDP measurements were performed from 400 nm to 950 nm in 25 nm steps for the two SPADs at  $V_E=1,3,5,$  and 7 V as displayed in Figs. 9 and 10, respectively. The tests were based on the continuous light technique at room temperature [21]. In the setup for these measurements, coherent and uniform light was illuminated to the SPAD and a reference photodiode by using an integrating sphere and a monochromator. The optical intensity of the reference photodiode was then measured for calculating the number of photons impinging on the SPAD. The SPAD was quenched with an external passive quenching resistor of  $100 \, \mathrm{k}\Omega$  and the outputs were monitored by the oscilloscope. The dead time was about  $2.5 \, \mu \mathrm{s}$ , with which it was checked that the SPADs do not suffer from any afterpulsing.

Fig. 9. PDP of the BCD-SPAD without canyon as a function of the wavelength at four different excess bias voltages.

Fig. 10. PDP of the BCD-SPAD with canyon as a function of the wavelength at four different excess bias voltages.

As both SPADs are based on a shallow junction, they have a peak PDP at around 450 nm. Moreover, the presence of fewer dielectric layers allows more photons to reach the silicon with fewer reflections, as expected with the simulations in Fig. 5 and Fig. 6, and therefore near 90% peak PDP is achieved with canyon etching when  $V_E$  is 7 V, while the default structure shows about 82% peak PDP at the same bias condition.

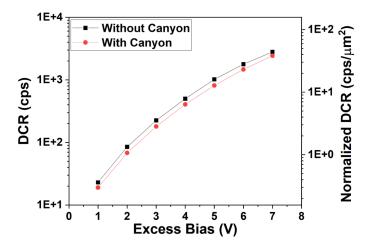

#### D. Dark Count Rate

DCR is comprised of primary and secondary pulses. Thermally generated carriers and tunneling are dominant components in primary pulses, while the secondary pulses, known as afterpulses, are avalanches caused by the release of trapped carriers [22]. That is to say, the DCR of a SPAD is mainly affected by the FEOL and should not be affected by the canyon implementation.

Fig. 11. DCR of the BCD-SPADs as a function of excess bias.

DCR measurements were conducted with a passive quenching resistor of  $100~\mathrm{k}\Omega$  and an oscilloscope. As can be seen in Fig. 11, the DCR difference between the SPADs with and without canyon etch is almost negligible, and therefore it can be concluded that the canyon etch process over the SPAD does not influence its noise performance. The SPADs show very low DCR, about 0.03 cps/ $\mu$ m², at  $V_E=1~\mathrm{V}$  so that it can be operable at a higher  $V_E$  to increase its PDP performance. When  $V_E$  is increased to 7 V, the DCR is about 40 cps/ $\mu$ m².

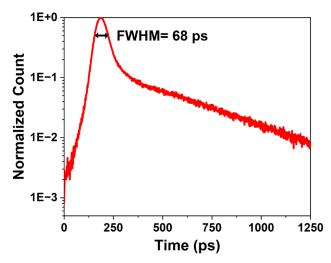

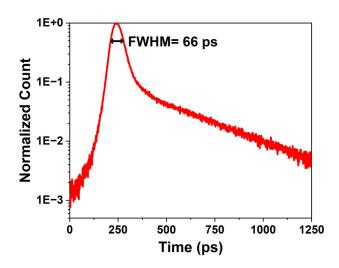

## E. Timing Jitter

The timing jitter performance is an important factor for biomedical applications that requires precise sensing such as ToF PET [23]. The timing jitter is the statistical fluctuation in time between the absorption of the photon and its corresponding avalanche breakdown [22]. It is dominated by carrier transit time, such as drift, diffusion, and avalanche multiplication time [24]. The timing jitter performance of the SPADs was measured using the time-correlated single-photon counting (TCSPC) technique at  $V_E = 7$  V with a 940 nm picosecond pulsed laser having a 30 kHz repetition rate. Both SPADs have excellent timing jitter performance, about 66 ps FWHM, including the jitter of the laser and laser driver as shown in Figs. 12 and 13. Both show almost identical jitter values because they share a common SPAD structure. The timing jitter could be decreased further with integrated circuitry as well as an optimized setup [25].

# IV. DISCUSSIONS

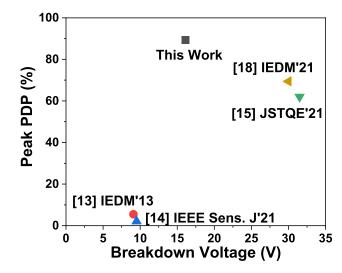

The proposed devices are compared with state-of-the-art SPADs fabricated in 90 nm processes and below in Figs. 14 and 15. The previously-reported SPADs that have lower  $V_B$  than the present SPAD reported in this article suffer from very low peak PDP as well as very high DCR [13], [14]. Compared to the SPADs which have higher  $V_B$ , our SPAD still exhibits higher peak PDP and lower or comparable timing jitter [15], [17], [18]. We further improve the detection efficiency of our SPAD without sacrificing other performance characteristics. Therefore,

Fig. 12. Timing jitter of the BCD-SPAD without canyon.

Fig. 13. Timing jitter of the BCD-SPAD with canyon.

Fig. 14. Peak PDP vs  $V_B$  comparisons of SPADs fabricated in 90 nm or more advanced processes.

|                                            | This work              |                          | [12]                      | £1.43                     | [15]                    | [17]                    | [10]                      |

|--------------------------------------------|------------------------|--------------------------|---------------------------|---------------------------|-------------------------|-------------------------|---------------------------|

|                                            | Without Canyon         | With Canyon              | <del>-</del> [13]         | [14]                      | [15]                    | [17]                    | [18]                      |

| Technology                                 | 55 nm FSI BCD          | 55 nm FSI BCD            | 65 nm FSI<br>CMOS         | 65 nm FSI<br>CMOS         | 55 nm FSI BCD           | 90 nm BSI CIS           | 90 nm BSI CIS             |

| Active Junction                            | PLDD/HVNW              | PLDD/HVNW                | N+/PW                     | N+/PW                     | DPW/BNW                 | n/a                     | n/a                       |

| Guard Ring                                 | P-epi GR               | P-epi GR                 | Modified NW               | NW                        | Virtual GR              | n/a                     | n/a                       |

| Active Area                                | 63.6 μm²               | 63.6 μm <sup>2</sup>     | 64 μm²                    | 100 μm²                   | 60.8 μm²                | n/a                     | n/a                       |

| $V_B$                                      | 16.1 V                 | 16.1 V                   | 9.1 V                     | 9.52 V                    | 31.5 V                  | 22 V                    | 30 V                      |

| $V_E$                                      | 7 V                    | 7 V                      | 0.4 V                     | 0.3 V                     | 7 V                     | 3 V                     | 2.5 V                     |

| Normalized DCR                             | 44 cps/μm <sup>2</sup> | 38.2 cps/μm <sup>2</sup> | 15.6 kcps/μm <sup>2</sup> | 138 kcps/μm <sup>2</sup>  | 2.6 cps/μm <sup>2</sup> | 19 cps/pix              | 0.044 cps/μm <sup>2</sup> |

| Peak PDP<br>@ wavelength                   | 82%<br>@ 425 nm        | 89.4%<br>@ 450 nm        | 5.5%<br>@ 425 nm          | 2.1%<br>@ 440 nm          | 62%<br>@ 530 nm         | n/a                     | 69.4%*<br>@ 510 nm        |

| PDP at 940nm<br>@ <i>V<sub>E</sub></i>     | 3.64%<br>@ 7 V         | 3.94%<br>@ 7 V           | 0.3%<br>@ 0.25 V          | 0.2%<br>@ 0.3 V           | 4.2%<br>@ 7 V           | 20.2%*<br>@ 3V          | 24.4%*<br>@ 2.5 V         |

| Timing Jitter $\bigcirc$ $\lambda$ . $V_E$ | 68 ps<br>@ 940 nm. 7 V | 66 ps<br>@ 940 nm. 7 V   | 235 ps<br>@ 637 nm. 0.4 V | 197 ps<br>@ 685 nm, 0.3 V | 52 ps<br>@ 780 nm. 3 V  | 137 ps<br>@ 940 nm, 3 V | 100 ps<br>@ 940 nm. 2.5 V |

40

TABLE I

PERFORMANCE SUMMARY AND COMPARISON WITH SPADS FABRICATED IN 90 NM OR MORE ADVANCED PROCESSES

<sup>\*</sup>PDE with microlens on the top of the SPAD

FLIM (400~750 nm) 30 **PDE** (%) PET (375~500 nm) 20 10 (400~850 nm) NIROT (650~950 nm) 1E+0 1E+1 1E+3 1E-1 1E+2 Normalized DCR (cps/μm²)

Fig. 15. Peak PDP vs timing jitter (FWHM) comparisons of SPADs fabricated in 90 nm or more advanced processes.

Fig. 16. Different biomedical applications and their requirements [26], [27], [28], [29], [30], [31].

the proposed SPAD achieves the highest peak PDP with excellent timing jitter performance in spite of the reduced  $V_B$ , while showing reasonable DCR performance. Table I lists the performance summary of the SPADs and shows the performance comparisons with the state-of-the-art SPADs.

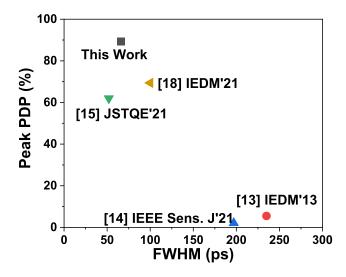

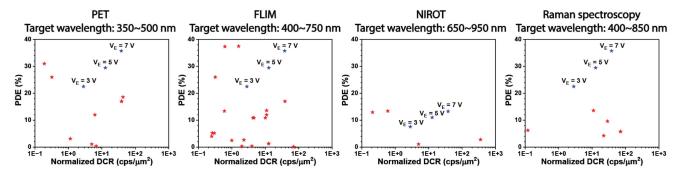

The demonstrated SPAD can be an excellent candidate for several biomedical applications, where high PDP, low timing jitter, and low  $V_B$  are required. For example, the high PDP of the proposed SPAD at around 450 nm is greatly beneficial to PET applications. In addition, the low timing jitter can substantially improve the sensitivity and resolution of ToF-PET systems. Other biomedical applications such as FLIM and time-domain

Raman spectroscopy also require such a high PDP in the visible wavelength range. Moreover, as the proposed device achieves reasonable NIR efficiency with the use of lightly-doped DNW, it's expected that the SPAD can be also utilized in NIROT applications. In addition, the low  $V_B$  offers an advantage to biomedical equipment in terms of power management and consumption, which is expected to play a major role in portable diagnostic and surgical systems.

Many multi-pixel SPAD sensors targeted at biomedical applications are actually co-integrated with the corresponding quench/recharge and data acquisition circuits. Therefore, the overall pixel efficiency, also called photon detection efficiency

Fig. 17. Peak performance and target wavelength of typical CMOS/BCD-based SPAD sensors for biomedical applications reported in [25], [26], [27], [28], [29], [30]. For the proposed SPAD we used different excess bias voltages and a fill factor of 40%, assuming no microlenses were used. (a) Reported PET applications vs SPAD at 450 nm, (b) Reported FLIM applications vs SPAD at 450 nm, (c) Reported NIROT applications vs SPAD at 700 nm, (d) Reported Raman spectroscopy applications vs SPAD at 450 nm.

(PDE), is defined as PDE = PDP  $\times$  fill factor (FF). Fig. 16 shows the PDE and normalized DCR range of typical CMOS/BCDbased SPAD sensors for biomedical applications [26], [27], [28], [29], [30], [31]. The fill factor of the SPAD is determined by the ratio of the active area of the SPAD to the total area of the device. With an active area diameter of 9  $\mu$ m and a total diameter of 14.4  $\mu$ m, the fill factor of the device is about 40%. Also, as shown in Fig. 17, the sensors in different biomedical applications are compared to the peak performance of the proposed SPAD at different excess bias voltages, taking into account a FF of 40%. Considering the various target wavelengths of each technology, the non-identical peak performance of the SPAD is used for the comparison. For PET, FLIM, and Raman spectroscopy, the SPAD's performance at 450 nm, where the device has the maximum efficiency in their target wavelengths, is compared to the SPAD sensors as can be seen in Fig. 17(a), (b), and (d). On the other hand, the performance at 700 nm is used to compare NIROT's sensors. Although an ideal sensor would be placed in the top left corner of the plot, the proposed SPAD can be optimized in terms of the PDP and DCR according to each application by adjusting its excess bias voltage. It should thus be able to satisfy the demanding requirements of most biomedical applications.

## V. CONCLUSION

We have demonstrated and characterized high-performance SPADs based on 55 nm BCD technology. With the use of layers available in BCD technology, the SPAD structure is optimized for low-noise and high-efficiency operation with a low  $V_B$ . In order to enhance its efficiency, we use canyon etch to reduce multilayer reflections. The resulting SPAD has a  $V_B$  of 16.1 V, peak PDP of 89.4% at 450 nm, DCR of 38.2 cps/ $\mu$ m<sup>2</sup>, and timing jitter of 66 ps at  $V_E = 7$  V. It's expected that the proposed SPAD has a great potential for several biomedical applications.

## REFERENCES

M.-J. Lee and E. Charbon, "Progress in single-photon avalanche diode image sensors in standard CMOS: From two-dimensional monolithic to three-dimensional-stacked technology," *Japanese J. Appl. Phys.*, vol. 57, no. 10, pp. 1–6, Sep. 2018.

- [2] M. Sanzaro, F. Signorelli, P. Gattari, A. Tosi, and F. Zappa, "0.16 μm–BCD silicon photomultipliers with sharp timing response and reduced correlated noise," Sensors, vol. 18, no. 11, pp. 1–9, Nov. 2018.

- [3] S. Lindner et al., "A novel 32 x 32, 224 mevents/s time resolved SPAD image sensor for near-infrared optical tomography," in *Proc. Biophoton. Congr.: Biomed. Opt. Congr.*, 2018, Paper JTh5A.6.

- [4] W.-Y. Ha et al., "Noise optimization of single-photon avalanche diodes fabricated in 110 nm CMOS image sensor technology," *Opt. Exp.*, vol. 30, no. 9, pp. 14958–14965, Apr. 2022.

- [5] A. C. Ulku et al., "A 512 × 512 SPAD image sensor with integrated gating for widefield FLIM," *IEEE J. Sel. Topics Quantum Electron.*, vol. 25, no. 1, Jan./Feb. 2019, Art. no. 6801212.

- [6] S. Mandai, M. W. Fishburn, Y. Maruyama, and E. Charbon, "A wide spectral range single-photon avalanche diode fabricated in an advanced 180 nm CMOS technology," *Opt. Exp.*, vol. 20, no. 6, pp. 5849–5857, Feb. 2012.

- [7] J. Holma, I. Nissinen, J. Nissinen, and J. Kostamovaara, "Characterization of the timing homogeneity in a CMOS SPAD array designed for timegated Raman spectroscopy," *IEEE Trans. Instrum. Meas.*, vol. 66, no. 7, pp. 1837–1844, Jul. 2017.

- [8] I. Nissinen, J. Nissinen, P. Keranen, D. Stoppa, and J. Kostamovaara, "A 16 × 256 SPAD line detector with a 50-ps, 3-bit, 256-channel time-todigital converter for Raman spectroscopy," *IEEE Sensors J.*, vol. 18, no. 9. pp. 3789–3798, May 2018.

- [9] J. Kostamovaara et al., "Fluorescence suppression in Raman spectroscopy using a time-gated CMOS SPAD," *Opt. Exp.*, vol. 21, no. 25, pp. 31632–31645, Dec. 2013.

- [10] Y. Maruyama, J. Blacksberg, and E. Charbon, "A 1024× 8, 700-ps time-gated SPAD line sensor for planetary surface exploration with laser Raman spectroscopy and LIBs," *IEEE J. Solid-State Circuits*, vol. 49, no. 1, pp. 179–189, Jan. 2014.

- [11] F. Madonini and F. Villa, "Single photon avalanche diode arrays for time-resolved Raman spectroscopy," *Sensors*, vol. 21, no. 13, Jun. 2021, Art. no. 4287.

- [12] S. Pellegrini and B. Rae, "Industrialised SPAD in 40 nm technology," in *Proc. IEEE Int. Electron Devices Meeting*, 2017, pp. 16.5.1–16.5.4.

- [13] E. Charbon, H. J. Yoon, and Y. Maruyama, "A Geiger mode APD fabricated in standard 65nm CMOS technology," in *Proc. IEEE Int. Electron Devices Meeting*, 2013, pp. 27.5.1–27.5.4.

- [14] W. Jiang, Y. Chalich, R. Scott, and M. J. Deen, "Time-gated and multijunction SPADs in standard 65 nm CMOS technology," *IEEE Sensors J.*, vol. 21, no. 10, pp. 12092–12103, May 2021.

- [15] F. Gramuglia et al., "Engineering breakdown probability profile for PDP and DCR optimization in a SPAD fabricated in a standard 55 nm BCD process," *IEEE J. Sel. Topics Quantum Electron.*, vol. 28, no. 2, Mar./Apr. 2022, Art. no. 3802410.

- [16] P. Keshavarzian et al., "Low-noise high-dynamic-range single-photon avalanche diodes with integrated PQAR circuit in a standard 55nm BCD process," in *Proc. SPIE*, vol. 12089, 2022, Art. no. 120890B.

- [17] S. Shimada et al., "A back illuminated 6 μm SPAD pixel array with high PDE and timing jitter performance," in *Proc. IEEE Int. Electron Devices Meeting*, 2021, pp. 20.1.1–20.1.4.

- [18] K. Morimoto et al., "3.2 Megapixel 3D-stacked charge focusing SPAD for low-light imaging and depth sensing," in *Proc. IEEE Int. Electron Devices Meeting*, 2021, pp. 20.2.1–20.2.4.

- [19] Y. Okuto and C. R. Crowell, "Threshold energy effect on avalanche breakdown voltage in semiconductor junctions," *Solid State Electron.*, vol. 18, no. 2. pp. 161–168, Sep. 1975.

- [20] R. J. Mcintyre, "On the avalanche initiation probability of avalanche diodes above the breakdown voltage," *IEEE Trans. Electron Devices*, vol. 20, no. 7, pp. 637–641, Jul. 1973.

- [21] G. Zappalà et al., "Set-up and methods for SiPM photo-detection efficiency measurements," J. Instrum., vol. 11, no. 8, pp. 1–18, Aug. 2016.

- [22] C. Veerappan, "Single-photon avalanche diodes for cancer diagnosis," Ph.D. dissertation, Delft Univ. Technol., Delft, The Netherlands, Mar 2016

- [23] V. C. Spanoudaki and C. S. Levin, "Photo-detectors for time of flight positron emission tomography (ToF-PET)," *Sensors*, vol. 10, no. 11, pp. 10484–10505, Nov. 2010.

- [24] R. Helleboid et al., "Modeling of SPAD avalanche breakdown probability and jitter tail with field lines," *Solid-State Electron.*, vol. 194, Mar. 2022, Art. no. 108376.

- [25] I. Cusini et al., "Historical perspectives, state of art and research trends of SPAD arrays and their applications (Part II: SPAD arrays)," Front. Phys., vol. 10, Jul. 2022, Art. no. 906671.

- [26] C. Bruschini, H. Homulle, I. M. Antolovic, S. Burri, and E. Charbon, "Single-photon avalanche diode imagers in biophotonics: Review and outlook," *Light: Sci. Appl.*, vol. 8, no. 1, Sep. 2019, Art. no. 87.

- [27] A. Chiuri and F. Angelini, "Fast gating for Raman spectroscopy," Sensors, vol. 21, no. 8, Apr. 2021, Art. no. 2579.

- [28] L. Zhang, A. Ameri, M. Anwar, and A. M. Niknejad, "A microwave-optical biosensor with 5.4 ppm label/reference-free long-term stability and single photon sensitivity in 28 nm bulk CMOS," in *Proc. IEEE Custom Integr. Circuits Conf.*, 2019, pp. 1–4.

- [29] M. Buttafava et al., "SPAD-based asynchronous-readout array detectors for image-scanning microscopy," *Optica*, vol. 7, no. 7, pp. 755–765, Jul 2020

- [30] D. R. Schaart, E. Charbon, T. Frach, and V. Schulz, "Advances in digital SiPMs and their application in biomedical imaging," *Nucl. Instrum. Methods Phys. Res. Sect. A: Accel., Spectrometers, Detect. Assoc. Equip.*, vol. 809, pp. 31–52, Feb. 2016.

- [31] F. Gramuglia, "High-performance CMOS SPAD-based sensors for timeof-flight PET applications," Ph.D. dissertation, École Polytechnique Fédérale de Lausanne, Lausanne, Switerland, 2022.

Won-Yong Ha (Student Member, IEEE) received the B.S. and M.S. degrees in electrical engineering from Yonsei University, Seoul, South Korea, in 2020 and 2022 respectively. Since 2022, he has been working toward the Ph.D. degree with the AQUA Laboratory, École Polytechnique Fédérale de Lausanne, Neuchâtel, Switzerland. His research interests include CMOS-SPAD structure, Si-SPADs-based circuits, and time-gated Raman spectroscopy

**Doyoon Eom** received the B.S. degree in electrical and electronic engineering from Yonsei University, Seoul, South Korea, in 2020. Since 2021, he has been working toward the M.S. degree with Yonsei University and Korea Institute of Science and Technology, Seoul, South Korea. His research interests include single-photon avalanche diodes, LiDAR sensors and applications, CMOS-compatible photodetectors, and avalanche-mode light-emitting diodes.

Hyo-Sung Park received the B.S. degree in semiconductor science & technology from Jeonbuk National University, Jeonju, South Korea, in 2020. He is currently working toward the M.S. and Ph.D. degrees with Yonsei University, Seoul, South Korea. Since 2020, he has been a Student Researcher with the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology, Seoul, South Korea. His research interests include single-photon avalanche diodes, pixel and array circuits for CMOS-SPADs, and LiDAR/D-ToF sensors and applications.

Francesco Gramuglia (Member IEEE) received the B.S. degree in biomedical engineering from the Politecnico di Milano, Milan, Italy, in 2013, the M.S. degree in electronics engineering from the Politecnico di Milano, Milan, Italy, in 2016, and the Ph.D. degree in microelectronics from the EPFL in the Advanced Quantum Architecture Laboratory in 2022. From 2015 to 2016, he was a Trainee with STORMlab, Vanderbilt University, Nashville, TN, USA, where he collaborated on the development of robotic endoscope platforms. His research interests include the

design of deep-submicron Si-SPAD and SPAD-based sensors in standard CMOS and BCD technologies, and system development for use in several applications based on single photon detection, e.g., Time-of-flight Positron emission tomography. In 2016, he was the recipient of the Best Application Prize and Overall Winner at Surgical Robot Challenge during the Hamlyn Symposium on Medical Robotics at Imperial College, London, 2016. In 2021, he was also the recipient of the First Place Nuclear Science Symposium (NSS) Student Paper Award. Since 2022, he has been a Senior Engineer with the Technology Development Device Department, Globalfoundries.

Eunsung Park received the B.S. degree in electronic engineering from Gachon University, Gyeonggi-do, South Korea, in 2019. He is currently working toward the M.S. and Ph.D. degrees with Yonsei University, Seoul, South Korea. Since 2019, he has been a Student Researcher with the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology, Seoul, South Korea. His research interests include single-photon detectors/sensors, Si-SPADs in CMOS, and CIS technologies.

Pouyan Keshavarzian (Student Member, IEEE) received the B.Sc. and M.Sc. degrees in electrical engineering from the University of Calgary, Calgary, AB, Canada, in 2015 and 2019, respectively, and the Ph.D. degree from the École Polytechnique Fédérale de Lausanne, Lausanne, Switzerland, in 2023. From 2013 to 2016, he had various roles in hardware engineering within Garmin Canada, Cochrane, AB, Canada, where he was involved in the design of low-power wireless sensors for sport and health monitoring applications. For his M.Sc. research, he focused

on developing microwave backscattering circuits and systems for radar applications. His research interests include the statistical modeling and development of circuits and detectors for SPAD-based sensors.

Ekin Kizilkan (Student Member, IEEE) received the B.S. degree in electrical and electronics engineering and in physics from Middle East Technical University, Ankara, Turkey, in 2016 and 2017, respectively, and the M.S. degree from the École Polytechnique Fédérale de Lausanne, Lausanne, Switzerland, in 2019. Since 2019, he has been working toward the Ph.D. degree with Advanced Quantum Architecture Laboratory. From 2016 to 2017, he was a Full-Time Research Assistant with Quantum Devices and Nanophotonics Research Laboratory on the design

and fabrication of SWIR Cameras based on III/V compound semiconductors. He has been conducting research on Single-Photon Avalanche Diodes (SPAD) based on various technologies (CMOS, Germanium on Silicon PIC, III/V) to enhance SPADs' performance in NIR wavelengths as part of his Ph.D. work.

Michelle Tng received the B.Eng. degree in electrical and electronic engineering from Nanyang Technological University, Singapore, in 2012. Since then, she has been with GLOBALFOUNDRIES, where she is a part of the Global TCAD team. Her research interests include semiconductor device modeling and single photon avalanche diodes.

Claudio Bruschini (SeniorMember, IEEE) received the Laurea degree in physics from the University of Genova, Genoa, Italy, in 1992, and the Ph.D. degree in applied sciences from Vrije Universiteit Brussel, Brussels, Belgium, in 2002. He is currently a Scientist and Lab Deputy with EPFL's Advanced Quantum Architecture Laboratory. He has authored or coauthored more than 130 articles and conference proceedings and one book. His scientific interests have spanned from high energy physics and parallel computing in the early days, to challenging sensor applications in

humanitarian demining, concentrating since 2003 on quantum photonic devices, high-speed and time-resolved 2D/3D optical sensing, and applications thereof (biophotonics, nuclear medicine, basic sciences, security, ranging). He was the recipient of the 2012 European Photonics Innovation Award, Image Sensors Europe 2019 Award in the category Best Academic Research Team, and Swiss Medtech Award 2016 finalist. He is a SPIE Senior Member and Co-Founder of a start-up commercialising selected AQUA lab SPAD designs.

Elgin Quek (Member, IEEE) received the B.Eng. degree (with First Class Hons.) in electrical engineering from the National University of Singapore, Singapore, and the M.S. degree in electrical engineering from Stanford University, Stanford, CA, USA. From 1988 to 2009, he was with Chartered Semiconductor, Singapore, where he worked on process integration, yield enhancement, device engineering and SPICE modeling for CMOS and floating gate memories. Since 2009, he has been with Globalfoundries Singapore, where he is also a GF Senior Fellow in

Technology Development responsible for device design for CMOS-based logic, SRAM, non-volatile memory, display-driver and sensor technologies. He has coauthored more than 40 technical papers and holds more than 150 U.S. patents.

**Daniel Chong** received the M.Eng. degree from the National University of Singapore Electrical Engineering Department in 2002. Since graduation, he have been with Globalfoundries Singapore Technology Development Department.

Shyue Seng Tan received the B.Eng. (with First-class Hons.) and the Ph.D. degrees in electrical & electronics engineering from Nanyang Technological University, Singapore, in 2001 and 2004, respectively. He is currently a PMTS (Deputy Director) with the Technology Development Department, Globalfoundries Singapore Private Limited, where he is leading a group of engineers working on the CMOS logic, HV, NVM, HBT device design and development. His research interests include semiconductor device physics and reliability physics and biosensor, CIS,

and SPAD development. He has authored or coauthored more than 30 journal and conference papers include one invited paper. He is the holder of 140 U.S. patents and more are in the progress of filing/searching. In addition, he was a Peer Reviewer of International Journal paper, IEEE TRANSACTION OF ELECTRON DEVICES, Electron Device Letters, Journal of Electrochemical Society, Applied Physics Letter, and Journal of Applied Physics.

Edoardo Charbon (Fellow, IEEE) received the Diploma in electrical engineering and EECS from ETH Zurich, the M.S. degree in electrical engineering and EECS from the University of California at San Diego, La Jolla, CA, USA, and the Ph.D. degree in electrical engineering and EECS from the University of California at Berkeley, Berkeley, CA, USA, in 1988, 1991, and 1995, respectively. He has consulted with numerous organizations, including Bosch, X-Fab, Texas Instruments, Maxim, Sony, Agilent, and Carlyle Group. He was with Cadence Design Systems

from 1995 to 2000, where he was the Architect of the company's initiative on information hiding for intellectual property protection. In 2000, he joined Canesta Inc., as the Chief Architect, where he led the development of wireless 3-D CMOS image sensors. Since 2002, he has been a Member of the Faculty of EPFL, where he has been a Full Professor since 2015. From 2008 to 2016, he was a Full Professor and the Chair of VLSI design with the Delft University of Technology, Delft, The Netherlands. He has been the driving force behind the creation of deep-submicron CMOS SPAD technology, which is mass-produced since 2015 and is present in telemeters, proximity sensors, and medical diagnostics tools. He has authored or coauthored more than 300 papers and two books, and he holds 20 patents. His research interests include 3-D vision, FLIM, FCS, NIROT to super-resolution microscopy, time-resolved Raman spectroscopy, and cryo-CMOS circuits and systems for quantum computing. Dr. Charbon is a Distinguished Visiting Scholar of the W. M. Keck Institute for Space at Caltech, Fellow of the Kavli Institute of Nanoscience Delft, and Distinguished Lecturer of the IEEE Photonics Society.

Woo-Young Choi (Member, IEEE) received the B.S., M.S., and Ph.D. degrees in electrical engineering and computer science from the Massachusetts Institute of Technology, Cambridge, MA, USA. For his Ph.D. thesis, he investigated MBE-grown InGaAlAs laser diodes for fiber optic applications. From 1994 to 1995, he was a Postdoctoral Research Fellow with NTT Opto-electronics Labs., where he worked on femto-second all-optical switching devices based on low-temperature-grown InGaAlAs quantum wells. In 1995, he joined the Department of Electrical and Elec-

tronic Engineering, Yonsei University, Seoul, South Korea, where he is currently a Professor. His current research interests include electronic, opto-electronic, and photonic devices and circuits for interconnect and sensing applications.

Myung-Jae Lee (Member, IEEE) received the B.S., M.S., and Ph.D. degrees in electrical and electronic engineering from Yonsei University, Seoul, South Korea, in 2006, 2008, and 2013, respectively. His doctoral dissertation concerned silicon avalanche photodetectors fabricated with standard CMOS/BiCMOS technology. From 2013 to 2017, he was a Post-doctoral Researcher with the Faculty of Electrical Engineering, Delft University of Technology, Delft, The Netherlands, where he worked on single-photon sensors and applications based on single-photon

avalanche diodes. In 2017, he joined the School of Engineering, École Polytechnique Fédérale de Lausanne, Neuchâtel, Switzerland, as a Scientist, working on advanced single-photon sensors/applications and coordinating/managing several research projects as a Co-Principal Investigator. Since 2019, he has been a Principal Investigator/Principal Research Scientist with the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology, Seoul, South Korea, where he has led the research and development of next-generation single-photon detectors and sensors for various applications. His research interests include photodiodes/photodetectors to single-photon detectors/sensors, concentrating since 2006 on CMOS-compatible avalanche photodetectors and single-photon avalanche diodes and applications thereof, e.g., LiDAR, ToF, 3D vision, biophotonics, quantum photonics, space, security, silicon photonics, and optical interconnects.