# Radiation-Induced Charge Trapping in Shallow Trench Isolations of FinFETs

Stefano Bonaldo<sup>®</sup>, Member, IEEE, Trace Wallace<sup>®</sup>, Member, IEEE, Hugh Barnaby<sup>®</sup>, Fellow, IEEE, Giulio Borghello<sup>®</sup>, Member, IEEE, Gennaro Termo<sup>®</sup>, Federico Faccio<sup>®</sup>, Member, IEEE, Daniel M. Fleetwood<sup>®</sup>, Life Fellow, IEEE, Serena Mattiazzo, Marta Bagatin<sup>®</sup>, Member, IEEE, Alessandro Paccagnella<sup>®</sup>, Senior Member, IEEE, and Simone Gerardin<sup>®</sup>, Member, IEEE

Abstract-We provide comprehensive experimental data and technology computer-aided design (TCAD) simulations to clarify total-ionizing-dose mechanisms in 16-nm Si FinFETs. In n-channel FinFETs irradiated to ultrahigh doses, the transconductance evolution rebounds (increase up to 3-10 Mrad followed by a decrease), while the drain-to-source leakage current steadily augments until reaching a plateau at very large doses. These effects result from positive charge trapping deep in the sidewalls of the shallow trench isolation (STI) and negative trapped charge accumulation localized in the upper STI corners. Larger sizes of inter-fin STI enhance the leakage current degradation of transistors with smaller numbers of fins. Hydrogen-induced border- and/or interface-trap generation at the Si/oxide interface at the STI corners leads to increased low-frequency noise (LFN) at doses > 10 Mrad(SiO<sub>2</sub>). These results show that the quality of oxides and interfaces in the upper region of the STI adjacent to the device channel is crucial for the tolerance to ultrahigh radiation of modern FinFET technologies.

*Index Terms*—16 nm, bias condition, charge trapping, FinFET, low-frequency noise, radiation effects, shallow trench isolation (STI), total ionizing dose (TID).

#### I. INTRODUCTION

THE scaling down of the metal-oxide-semiconductor (MOS) devices has generally resulted in increased tolerance to total ionizing dose (TID) [1], [2], [3]. The ultrathin gate oxide thickness of the gate-stack of Si-based field-effect transistors (FETs) has reduced densities of charge trapped in gate oxides and increased the likelihood of charge neutralization due to tunneling electrons [1], [4], [5]. However,

Manuscript received 21 July 2023; revised 15 September 2023 and 13 October 2023; accepted 18 October 2023. Date of publication 24 October 2023; date of current version 18 April 2024. This work was supported in part by the FinFET16v2 experiment through the National Institute for Nuclear Physics—Istituto Nazionale di Fisica Nucleare (INFN), Italy.

Stefano Bonaldo, Serena Mattiazzo, Marta Bagatin, Alessandro Paccagnella, and Simone Gerardin are with the Department of Information Engineering, University of Padova, 35131 Padua, Italy, and also with Istituto Nazionale di Fisica Nucleare (INFN), 35131 Padua, Italy (e-mail: stefano.bonaldo@dei.unipd.it).

Trace Wallace and Hugh Barnaby are with the School of Electrical, Computer and Energy Engineering, Arizona State University, Tempe, AZ 85281 USA.

Giulio Borghello and Federico Faccio are with CERN, 1211 Geneva, Switzerland.

Gennaro Termo is with CERN, 1211 Geneva, Switzerland, and also with the École Polytechnique Fédérale de Lausanne, 1015 Lausanne, Switzerland.

Daniel M. Fleetwood is with the Department of Electrical and Computer Engineering, Vanderbilt University, Nashville, TN 37235 USA.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TNS.2023.3326481.

Digital Object Identifier 10.1109/TNS.2023.3326481

the decrease in channel width and length has led to new TID-induced effects related to other critical insulators and modern production processes, e.g., shallow trench isolation (STI) oxides [6], [7], [8], [9], [10], spacer dielectrics [11], [12], [13], and halo implantation [14].

Several recent studies on MOSFET and FinFET technologies have identified the STI as the single most important issue for devices exposed to ionizing radiation, particularly at ultrahigh doses [15], [16], [17], [18], [19], [20], [21], [22]. In planar Si CMOS technologies, irradiation induces positive charge buildup in the STI, which is thicker and has higher defect densities than  $SiO_2$  gate oxides [6], [10]. Positive charge in the STI increases OFF-state leakage current in n-channel FETs due to the activation of lateral parasitic transistors [9], [19], [20] and induces parametric drifts in n- and p-channel FETs. The worst case degradation is found in narrow-channel transistors due to the radiation-induced narrow-channel effect (RINCE) [6], [9], [10]. For example, positive charge trapped in the STI of pFETs can lead to decreased densities of holes in regions of the device channel that are close to the STI, often leading to large shifts in the transconductance  $g_m$  and threshold voltage  $V_{\text{th}}$  of narrow pFETs [6], [9], [14], [17]. Similar width-dependent effects occur in n-channel MOSFETs: positive charge in STI enhances the number of carriers (electrons) in the regions close to the STI, significantly improving  $g_m$  of narrow nFETs [6], [9].

As technology nodes have advanced, TID effects have been widely explored in FinFETs [20], [21], [22], [23], [24], [25], [26], [27], [28], [29], [30], [31], [32]. Si-based FinFET technologies have exhibited TID-induced degradation with complex dependences on irradiation bias conditions [23], channel lengths [20], fin geometry [28], fin orientation [32], and fin/finger numbers [21]. Experiments at ultrahigh doses up to 1 Grad(SiO<sub>2</sub>) have been performed to analyze the transistor response and identify the critical TID mechanisms [20], [22]. In [20], 16-nm FinFETs irradiated in the ON-condition  $(V_{\rm gs} = V_{\rm dd})$  exhibited significant TID-induced degradation of  $g_m$  and  $I_{OFF}$ . pFinFETs showed monotonic  $g_m$  degradation with accumulated dose that depends on the number of fin/fingers due to the different dimensions of lateral and inter-fin STI [20], [21]. In contrast, nFinFETs showed increases in  $I_{OFF}$  and an interesting rebound of  $g_m$  with no  $V_{\text{th}}$  degradation [22]. Similar  $g_m$  rebound and  $I_{OFF}$  increases in nFinFETs are also observed at low doses, as < 1 Mrad(SiO<sub>2</sub>) [31], [32]. While these effects have been tentatively attributed to activation of

© 2023 The Authors. This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

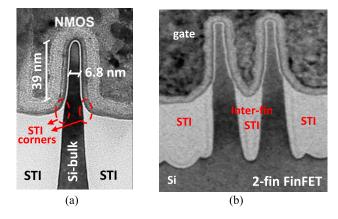

Fig. 1. (a) TEM images of single-channel fin fabricated in TSMC 16-nm FinFET technology. (b) TEM image of a commercial Intel 10-nm FinFET designed with two fins. After [33] and [34].

negatively charged traps outside the channel region [22], the underlying mechanisms remain unknown.

In this article, we present comprehensive experimental data and technology computer-aided design (TCAD) simulations that clarify the origin of these TID mechanisms in nFinFETs. Ultrahigh dose irradiation is used to magnify the degradation to help understand the underlying causes for the  $g_m$  rebound and increase in  $I_{\text{OFF}}$ . We find that these effects result from two mechanisms in different regions of the STI: 1) positive charge trapping in the deep STI sidewalls and 2) negative trapped charge in the upper STI corners. Buildup of negative charge depends strongly on the bias applied during irradiation, in contrast to the trapped positive charge, which is relatively insensitive to the applied bias. Low-frequency noise (LFN) measurements suggest that the negative trapped charge in the upper STI corner is most likely due to acceptor-like interface and/or border traps. TCAD simulations are presented that strongly support this interpretation of the experimental data.

# **II. DEVICES AND EXPERIMENTAL DETAILS**

# A. Devices

The FinFETs under test were core transistors fabricated in a commercial 16-nm bulk CMOS technology, rated to a nominal  $V_{dd}$  of 0.9 V. The devices were part of a custom array composed of several accessible transistors with channel length L = 72 or 240 nm. All tested transistors have the same fin width and fin height, sharing source and bulk contacts with separate drain and gate contacts.

For reference, Fig. 1(a) shows a TEM image of a single fin transistor fabricated from Taiwan Semiconductor Manufacturing Company (TSMC) 16-nm FinFET technology [33]. For the devices shown in Fig. 1(a), the channel width (W) is constant to ~85 nm, which is calculated as  $2*h_{\text{fin}} + w_{\text{fin}}$ , where  $h_{\text{fin}}$  is the height of the fin (~39 nm) and  $w_{\text{fin}}$  is the width of the fin is (~7 nm). The image highlights two upper sides of the STI, forming two triangular SiO<sub>2</sub> regions, which are distinctive structural characteristics of FinFET devices. These regions will be fundamental for the following discussions and are called "STI corners." Transistors with two, five, or ten fins were tested in this study to investigate the variation of TID-induced effects with fin number ( $n_{\text{fin}}$ ). As highlighted in Fig. 1(b) for 10-nm Intel FinFETs, the dimensions of the lateral delimiting STI oxides are larger than inter-fin STI, while the STI corners are identical regardless of delimiting or inter-fin STI [34].

# B. Exposure Conditions and Measurement Setup

The irradiation was conducted using a Seifert Model RP 149 X-ray irradiator at the University of Padova, Italy, at a dose rate of 4.5 Mrad(SiO<sub>2</sub>)/h [35]. All doses are expressed in SiO<sub>2</sub>. The total exposure time was ~9 days to reach 1 Grad. After the exposure, transistors were annealed at 100 °C for 24 h. Devices were biased in three different conditions during irradiation and annealing: "OFF" ( $V_{gs} = 0$  V and  $V_{ds} = 0$  V), "ON" ( $V_{gs} = 0.9$  V and  $V_{ds} = 0$  V), and "DIODE" ( $V_{gs} = 0.9$  V and  $V_{ds} = 0.9$  V). All other terminals were grounded.

DC static characteristics of transistors were measured at room temperature before exposure, after irradiation, and after high-temperature annealing. The threshold voltage  $V_{\text{th}}$  is calculated as  $V_{\text{gs-int}} - V_{\text{ds}}/2$ , where  $V_{\text{gs-int}}$  is extracted in the linear mode of device response ( $V_{\text{ds}} = 50 \text{ mV}$ ) as the gate-voltage axis intercept for a linear extrapolation of the  $I_d-V_{\text{gs}}$  curve at the point of maximum first derivative [36]. LFN was measured in a frequency span between 0.5 Hz and 1 kHz at  $V_{\text{ds}} = 50 \text{ mV}$ at several values of  $V_{\text{gt}} = V_{\text{gs}} - V_{\text{th}}$ .

The array structure of each tested die contained 12 nFinFET transistors fabricated with different channel lengths and fin numbers. Considering the high sensitivity of transistors to electrostatic discharge and the time required for performing an irradiation test at ultrahigh doses (~5 days for 500 Mrad or ~9 days for 1 Grad), at least three dies were tested in each bias condition, for a total of > 36 tested transistors per bias condition. Results in this article are presented for representative channel lengths and fin numbers, with at least two nominally identical devices evaluated for all experimental conditions. Nominally identical devices irradiated and annealed under similar conditions show parameter shifts that typically vary by less than  $\pm$  10%; dedicated tests to evaluate device-to-device variability were performed and analyzed in previous work [27].

#### **III. DC MEASUREMENTS**

# A. TID Tolerance at Different Bias Conditions

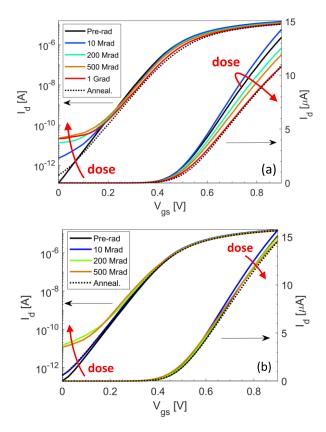

Fig. 2 shows the dc response for an nFinFET irradiated and annealed for 24 h at 100 °C in the ON- and OFF-bias conditions. The worst case degradation is observed when the devices are irradiated in the ON-condition, as the TID induces significant variation in the slope of the curves, i.e., the transconductance  $g_m$ . In both cases, the maximum drain current increases until 10 Mrad (blue curve) and then decreases at higher doses due to the  $g_m$  loss. The leakage current, defined as  $I_d$  at  $V_{gs} = 0$  V, increases with cumulative dose by  $\sim 100 \times$  during irradiation. Annealing at high-temperature induces an almost complete recovery of the leakage current (see the black dotted curve) with negligible effects on the transistor response at  $V_{gs} > V_{th}$ . The different behavior of the

Fig. 2. Radiation-induced degradation of  $I_d-V_{gs}$  curves in the linear regime ( $V_{ds} = 50 \text{ mV}$ ) for nFinFETs with L = 72 nm. The devices were irradiated and annealed at 100 °C for 24 h in (a) ON-bias and (b) OFF-bias conditions.

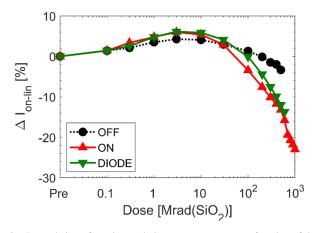

Fig. 3. Degradation of maximum drain current  $\Delta I_{\text{on-lin}}$  as a function of dose for nFinFETs with  $L = 72 \text{ nm. } I_{\text{on-lin}}$  is defined as the drain current at  $V_{\text{gs}} =$ 0.9 V with  $V_{\text{ds}} = 50 \text{ mV}$ . Devices were irradiated in different bias conditions: OFF ( $V_{\text{gs}} = 0 \text{ V}$  and  $V_{\text{ds}} = 0 \text{ V}$ ), ON ( $V_{\text{gs}} = 0.9 \text{ V}$  and  $V_{\text{ds}} = 0 \text{ V}$ ), and DIODE ( $V_{\text{gs}} = 0.9 \text{ V}$  and  $V_{\text{ds}} = 0.9 \text{ V}$ ).

leakage current and  $g_m$  suggests that effects originate from two different mechanisms.

The maximum drain current  $I_{\text{on-lin}}$  is plotted as a function of dose in Fig. 3 for OFF-, ON-, and DIODE-bias conditions. At 500 Mrad, the value  $\Delta I_{\text{on-lin}}$  of ON-biased devices decreases by 18% versus a 5% decrease for the OFF-biased. The curves of the ON-biased (red) and DIODE-biased (green) transistors almost overlap, suggesting an insensitivity of TID effects to the lateral drain-to-source electric field. However, the significant differences between the OFF-biased devices and ON- and DIODE-biased devices show that the results are still strongly influenced by the applied gate bias.

Increases in  $\Delta I_{\text{on-lin}}$  are observed at doses up to 10 Mrad, with a peak observed at ~3 Mrad. Similar effects are also observed in planar MOSFET technologies [6], [9] exposed at similar dose rates. At doses above 10 Mrad, the ON-current decreases constantly in all conditions in the explored dose range.

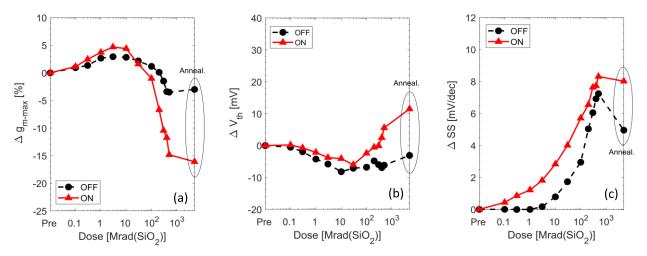

To help identify the cause of the  $I_{\rm ON}$  degradation, Fig. 4 shows the radiation-induced degradation in terms of (a) maximum transconductance  $\Delta g_{\rm m-MAX}$ , (b) threshold voltage  $\Delta V_{\rm th}$ , and (c) subthreshold swing  $\Delta$ SS. Three significant effects are apparent in Fig. 4.

1)  $g_m$  Rebound at 10 Mrad: Values of  $g_m$  clearly increase at doses < 10 Mrad and decrease at doses > 10 Mrad. Considering the worst case, ON-biased nFinFETs  $\Delta g_m$  is +5% at 10 Mrad and decreases to -15% at 500 Mrad. As the  $\Delta g_m$  trend is similar to  $\Delta I_{\text{on-lin}}$ , the dominant effect in the inversion regime is related to the degradation of the transconductance  $g_m$ .

2) Slight Degradation of  $V_{th}$  and SS: Values of  $V_{th}$  shift less than 15 mV, while SS increases by < 10 mV/dec after devices are irradiated to 500 Mrad. These shifts are relatively small and contribute little to the overall TID degradation. The modest  $\Delta V_{th}$  shifts indicate almost negligible charge trapping in the gate oxide and/or at its Si/SiO<sub>2</sub> interface [1], [2], [3], [4], [15], [16], [17], [18], [19], [20], [21], [22].

3) Influence of Irradiation Bias Condition on  $g_m$ : The ONbiased devices exhibit the highest  $\Delta g_m$ , meaning that the TID mechanism degrading  $g_m$  is strongly influenced by the intensity of the electric field applied to the oxides.

All these dependences will be important to the discussions of degradation mechanisms in Section IV.

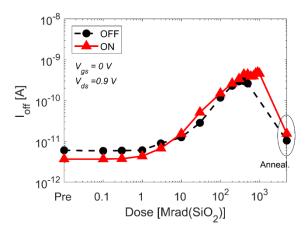

## B. Off-Leakage Current

Fig. 5 plots  $I_{\text{OFF}}$  as a function of accumulated dose, where  $I_{\text{OFF}}$  is calculated as  $I_d$  at  $V_{\text{gs}} = 0$  V with  $V_{\text{ds}} = 0.9$  V. In contrast to  $g_m$  and  $I_{\text{ON}}$ ,  $I_{\text{OFF}}$  shows monotonic degradation. The ON-irradiated transistors exhibit similar  $I_{\text{OFF}}$  degradation compared to OFF-irradiated devices, as both increase monotonically by ~100× at 500 Mrad. Inspection of all other terminals shows that leakage is flowing from drain to source. At doses > 100 Mrad,  $I_{\text{OFF}}$  reaches a plateau and settles at about  $5 \times 10^{-10}$  A, independently of the applied gate bias during irradiation. Annealing devices at 100 °C for 24 h restores  $I_{\text{OFF}}$ to pre-irradiation values.

$I_{\text{OFF}}$  increases indicate positive charge trapping in the STI that activates parasitic leakage paths close to the STI sidewall, similar to effects seen in irradiated planar nMOSFETs [6], [8], [17] and FinFETs [28], [31]. The  $I_{\text{OFF}}$  plateau at doses > 100 Mrad may be induced by the saturation of positive charges in STI sidewalls at ultrahigh doses or by the equilibrium of annealing (detrapping) and trapping occurring during long-time irradiations. More importantly, the insensitivity of  $I_{\text{OFF}}$  to applied gate bias suggests that the leakage most likely occurs in deeper regions of the STI sidewalls, where the electric field

Fig. 4. Degradation of (a) maximum transconductance  $\Delta g_{\text{m-MAX}}$ , (b) threshold voltage  $\Delta V_{\text{th}}$ , and (c) subthreshold swing  $\Delta SS$ , as functions of dose in nFinFETs with L = 72 nm. Transistors were irradiated and then annealed for 24 h at 100 °C in the OFF- and ON-bias conditions. Measurements are carried out at room temperature in the linear regime ( $V_{\text{ds}} = 50 \text{ mV}$ ).

Fig. 5. Increase of drain leakage current  $I_{OFF}$  at  $V_{ds} = 0.9$  V as a function of cumulative dose for nFinFETs with L = 72 nm. Transistors were irradiated and then annealed for 24 h at 100 °C in the OFF- and ON-bias conditions.

intensity, and thus charge yield, is not influenced by  $V_g$  [1], [4], [8], [15], [16], [18].

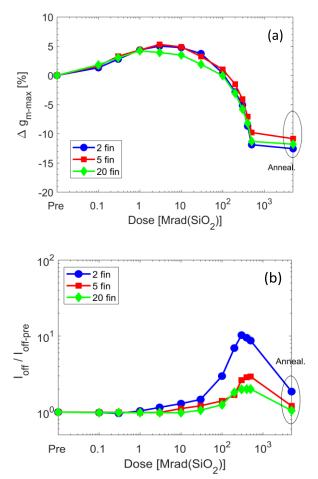

## C. TID Effects Dependence on Fin Number

We evaluated the dependence of the TID response on the number of fins by testing nFinFETs fabricated with different fin numbers and the same channel length (L = 240 nm). The devices were irradiated up to 500 Mrad in the ON-bias, i.e., worst case bias condition. Fig. 6(a) shows the  $g_m$  degradation of nFinFETs with 2, 5, and 20 fins. The curves nearly overlap, indicating practical insensitivity of  $\Delta g_m$  to the number of fins. At 500 Mrad, values of  $\Delta g_m$  are -12%, -10%, and -11% for 2-, 5-, and 20-fin transistors, respectively. As in Fig. 4(a), all devices exhibit positive  $g_m$  shifts at doses < 10 Mrad and turnaround at  $\sim 10$  Mrad, with  $g_m$  decreasing at ultrahigh doses.

In contrast,  $I_{OFF}$  degradation depends strongly on the fin number of the transistors. Fig. 6(b) shows  $I_{OFF}$  normalized by its initial value ( $I_{OFF}/I_{off-pre}$ ) for nFinFETs with 2, 5, and 20 fins. Worst case is found for transistors having two fins (blue curve). These show an  $I_{OFF}$  increase

Fig. 6. Influence of the number of fins on TID-induced effects as a function of dose (a)  $\Delta g_{m-\text{lin}}$  and (b)  $I_{\text{off}}/I_{\text{off-pre}}$ . nFinFETs with L = 240 nm were irradiated up to 500 Mrad(SiO<sub>2</sub>) and annealed at 100 °C for 24 h in the ON-bias condition.  $I_d - V_{\text{gs}}$  curves of unpassivated GaN-based HEMTs in the saturation regime ( $V_{\text{ds}} = 5$  V). The devices were irradiated up to 100 Mrad(SiO<sub>2</sub>) and then annealed at room temperature for 27 h in (a) "cut-off"-bias and (b) the "on"-bias.

of  $\sim 10 \times$  after 500 Mrad versus  $\sim 2.5 \times$  for the 20-fin devices (the increase of  $100 \times$  reported previously was for the shorter L = 72 nm transistors). In all cases, high-temperature

Fig. 7. LFN response for nFinFETs with L = 240 nm and  $n_{\rm fin} = 2$ . Devices were irradiated up to 500 Mrad(SiO<sub>2</sub>) and annealed at 100 °C for 24 h in (a) ON- and (b) OFF-bias conditions. The noise was measured at  $V_{\rm ds} = 50$  mV and  $V_{\rm et} = 0.2$  V at room temperature.

annealing induces an almost complete recovery of  $I_{\text{OFF}}$ , similar to the results in Fig. 5. The dependence of  $I_{\text{OFF}}$  is most likely induced by the higher volume oxides of lateral STI compared to intra-fin STI [see Fig. 1(b)], similar to the fin dependence found in p-channel FinFETs [21]. Enhanced positive charge densities in the lateral STI may induce higher  $I_{\text{OFF}}$  degradation in the first and last fins in sequences, compared with those in central positions. Consequently, transistors with low numbers of fins have relatively higher  $I_{\text{OFF}}$  degradation compared to transistors having higher numbers of fins.

The differing  $g_m$  and  $I_{OFF}$  dependences on numbers of fins highlight that significant TID degradation can occur in two different regions of STI. In particular,  $I_{OFF}$  is evidently induced by positive charges trapped in deep regions of the STI sidewalls, as suggested by its dependence on fin number and its relative independence of irradiation bias. On the other hand,  $g_m$  may be induced by negative trapped charge buildup in the upper corners of the STI, as suggested by its independence of fin number and its strong dependence on irradiation bias.

#### **IV. LOW-FREQUENCY NOISE RESPONSE**

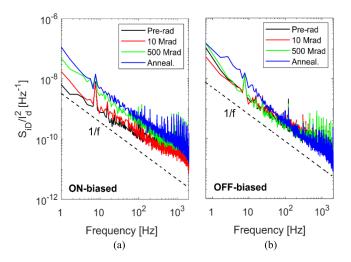

LFN was measured at several gate voltages to obtain insights into TID-induced defects [37], [38], [39], [40], [41], [42], [43], [44], [45], [46], [47], [48], [49], [50], [51]. The analysis shown here focuses on devices with long channels (L = 240 nm), as the noise response of short-channel transistors in the pre-rad condition is typically dominated by the Lorentzian noise generated by a single preexisting prominent defect, which dominates over the 1/f noise response, resulting in random telegraph noise [46], [47], [48], [49], [50].

Fig. 7(a) and (b) shows the LFN response of nFinFETs irradiated and annealed in the ON- and OFF-bias conditions, respectively. The FinFETs show 1/f noise with typical device-to-device variability [37], [38]. In ON-biased devices, the noise is approximately constant after 10 Mrad and increases at 500 Mrad. This LFN increase indicates activation of new traps, as the channel and newly generated defects localized in

Fig. 8. 1/f noise magnitudes at f = 10 Hz versus  $V_{gs} - V_{th}$  at  $V_{ds} = 50$  mV for nFinFETs with L = 240 nm. Devices were irradiated up to 500 Mrad(SiO<sub>2</sub>) and then annealed in the ON-bias condition.

the near-interfacial gate oxide can exchange charge through tunneling and/or thermally assisted processes, which allows for the capture/emission of electrons by border traps [37], [38], [44]. Recent revaluation of LFN also shows a potentially significant role for hydrogen-mediated defect activation and passivation in LFN for some devices, e.g., via the alternating defect activation and passivation of interface traps at the semiconductor/oxide interface [47], [51]. As a consequence, increases in LFN noise magnitudes at doses > 10 Mrad indicate the generation of border traps and/or increases in intensity of hydrogen-assisted defect activation and passivation processes at Si/oxide interfaces [37], [47], [51]. It is worth noting that the significant increase in magnitude of LFN does not occur until  $g_m$  begins to drop, after 10 Mrad [see Fig. 4(a)]. High-temperature annealing in Fig. 7 (blue curve) slightly increases the LFN, again in agreement with the slight changes in  $g_m$  after annealing. In contrast, OFF-biased FinFETs show stable LFN response, which is relatively insensitive to cumulative dose.

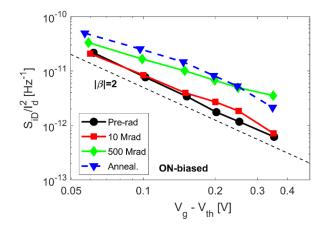

Fig. 8 plots the LFN magnitude at 10 Hz as a function of  $V_{\rm gt} = V_{\rm gs} - V_{\rm th}$  for nFinFETs irradiated in the ONbias condition. When the slope  $|\beta|$  of the noise versus  $V_{gt}$ curve is approximately equal to 2, the effective density of the traps is uniform in space and energy [37], [39], [40], [42]. In pristine and in devices irradiated to 10-Mrad,  $|\beta|$  is ~2, indicating an approximately uniform spatial and energetic trap distribution. At 500 Mrad, the noise increases significantly and  $|\beta|$  is ~1.6, indicating that the newly generated traps are less uniform in space and energy than the defects leading to the noise in the as-processed devices. For annealed devices, the  $S_{\rm Id}-V_{\rm gt}$  curve shows a slight increase in magnitude at low  $V_{\rm gt}$  with  $|\beta|$  of ~1.6, while  $|\beta|$  is ~2.1 for high  $V_{\rm gt}$ . Hence, there is not only an increase in effective defect density during irradiation and annealing but also a change in spatial and energy distribution [37], [38], [44].

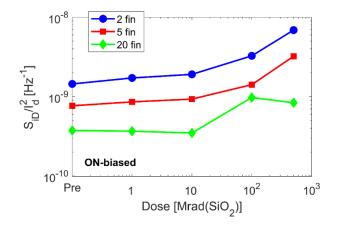

Fig. 9 shows the noise at 10 Hz as a function of dose for transistors of L = 240 nm with different fin numbers. The noise magnitude scales inversely with channel area, i.e., the number of fins, and increases with dose [37], [38], [48]. The LFN magnitude of all FinFETs increases substantially

Fig. 9. LFN magnitudes for nFinFETs with L = 240 nm and several fin numbers. Devices were irradiated and annealed in the ON-bias condition with noise measured at  $V_{ds} = 50$  mV and  $V_{gt} = 0.2$  V at room temperature. The out-of-trend increase of LFN of 20-fin device at 100 Mrad is most likely caused by higher-than-normal contact noise during this test.

after 100 Mrad(SiO<sub>2</sub>), similar to the  $g_m$  drop in Fig. 4(a). The increase of LFN is independent of the number of fins, as all FinFETs exhibit a 4× increase in the LFN magnitude.

We conclude that, in ON-biased transistors, the LFN measurements at doses > 10 Mrad and subsequent high-temperature annealing indicate the activation of border and/or interface defects, which are spatially and/or energetically nonuniform, and independent of fin number. These results all suggest that the increase in noise is most likely due to the trap activation processes related to the STI corners [38], [47], [52], [53], [54], which lead to the decrease in  $g_m$  for similar dose and annealing conditions.

#### V. MECHANISMS IDENTIFICATION AND DISCUSSION

Based on the above experimental results, we have proposed TID-induced mechanisms that could justify the evolution of  $g_m$  and  $I_{ON}$  at high doses in Figs. 3 and 4. Silvaco TCAD simulations are now presented to illustrate how these basic mechanisms influence the electrical response of the transistors. The results provide strongly supporting evidence for the following sequence.

1) First Mechanism: It is fast generation of positive charge, holes, and H<sup>+</sup>, in the SiO<sub>2</sub> of STI. This mechanism is responsible for the  $g_m$  increase at doses < 10 Mrad and for the continuous  $I_{\text{OFF}}$  increase.

2) Second Mechanism: It is slow activation of donor-like traps, capable of trapping negative charge in the upper corners of the STI [see Fig. 1(a)]. This mechanism is responsible for the  $g_m$  decrease at doses > 10 Mrad and the increase of the LFN magnitude.

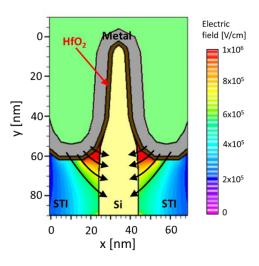

Charge trapping in the STI can contribute to the LFN of devices, as reported in [52], [53], and [54]. Fig. 10 shows a Silvaco TCAD model developed through the Devedit and Deckbuild tools, including the Atlas and Victory Process. The geometrical structure is based on TEM images shown in Fig. 1 with meshing optimized close to the material interfaces. The gate-stack is formed by  $\sim 2$  nm of HfO<sub>2</sub> (brown),  $\sim 6$  nm of Al (gray), and a thick layer of Ti (green). Doping

Fig. 10. TCAD simulation of the nFinFETs for  $V_{gs} = 0.9$  V. The color scale indicates the intensity of the electric field in the STI, while the black arrows show the direction of the electric field.

profiles in the Si channel have been retrieved from publicly available information and set to  $10^{16}$  cm<sup>-3</sup> of B in the channel region [26]. All the physics for modeling the semiconductor device are set to the default Silvaco parameter values. The color scale in Fig. 10 indicates the electric field intensity Ewhen  $V_{gs} = 0.9$  V. The FinFET layout introduces distinctive regions visible as triangular oxide regions in the upper STI corners, which are characterized by the highest values of electric fields. This agrees well with the strong influence of bias on  $\Delta g_m$  in Fig. 4(a). It is likely that the negative charge formation (mechanism #2) may be related to H<sup>+</sup> transport and dehydrogenation processes at the  $Si/SiO_2$  interface [12], [13], [55], [56], [57], [58], [59], [60], [61], leading to the accumulation of negatively charged interface traps in the STI corners. Interface-trap formation in the STI corner is enhanced under high electric fields as in the cases of ON- and DIODEbiases, as shown also by LFN measurements. This contrasts with results for OFF-bias, for which electric fields are small in the STI corners.

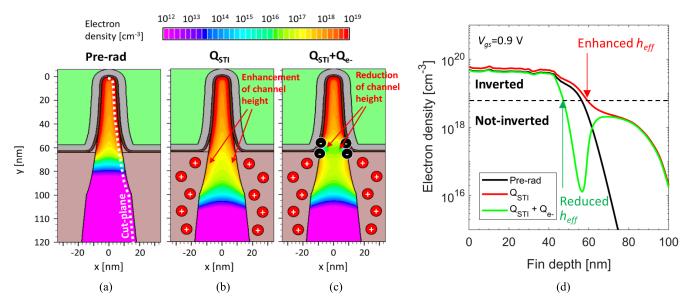

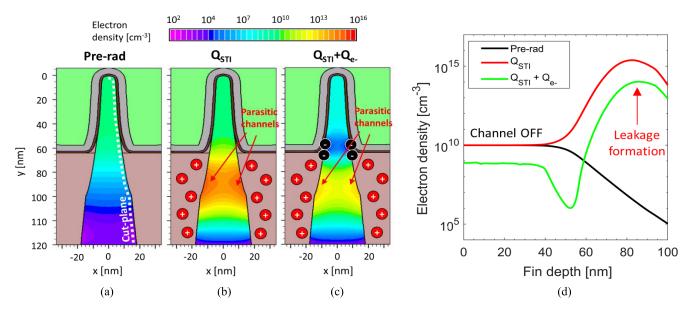

Fig. 11 shows the proposed TID-induced mechanisms degrading  $g_m$ . TCAD simulations are performed in nFinFETs at  $V_{gs} = 0.9$  V (channel ON). The color scale indicates the electron density in the Si channel fin. TID effects were simulated by adding fixed charges in specific regions of the STI oxide [15], [16], [18], [62]. Positive charge was added as fully ionized donor traps ( $Q_{STI}$ ), which are uniformly distributed throughout the STI, in agreement with the relatively small electric field reaching the STI sidewalls. Negative charge, accounting for mechanism #2, was added as fully ionized acceptor traps ( $Q_{e-}$ ) uniformly distributed at the Si/STI interface from the top STI corner down to a depth of 15 nm, represented by the red regions of Fig. 10 under the highest electric field.

In the pre-irradiation condition in Fig. 11(a), the channel region is inverted, and the fin is characterized by a high density of electrons. Fig. 11(b) simulates the condition at 10 Mrad, when positive charges are trapped in STI with

Fig. 11. TCAD simulation of nFinFETs when  $V_{gs} = 0.9$  V (channel ON). The images show TID-induced mechanisms degrading  $g_{m-max}$ . The color scale illustrates the electron density in the Si channel fin. (a) Pre-irradiation without trapped charges in the oxides. (b) At high doses with positive trapped charge in STI ( $Q_{STI} = 5 \times 10^{17}$  cm<sup>-3</sup>). (c) At ultrahigh doses with positive and negative trapped charge ( $Q_{STI} = 5 \times 10^{17}$  cm<sup>-3</sup> and  $Q_{e-} = 7.5 \times 10^{12}$  cm<sup>-2</sup>).  $Q_{STI}$ 's are uniformly distributed in the STI, while  $Q_{e-}$ 's are localized at the Si/SiO<sub>2</sub> interface close to the upper corners of the STI. (d) Plot shows the electron density in the Si fin as a function of fin depth [coordinate y in (a)], considering the cutline shown in (a), i.e., at 1 nm from the Si/SiO<sub>2</sub> interface, with  $Q_{STI} = 5 \times 10^{17}$  cm<sup>-3</sup> and  $Q_{e-} = 7.5 \times 10^{12}$  cm<sup>-2</sup>.

Fig. 12. TCAD simulations of nFinFETs when  $V_{\rm gs} = 0.9$  V (channel ON). The plots show electron density concentrations as functions of fin depth along the cutline in Fig. 11(a), showing the modulation of the effective channel height  $h_{\rm eff}$ . (a) Several densities of positive charge  $Q_{\rm STI}$  are shown, with  $Q_{e-} = 0$  cm<sup>-2</sup>. (b) Several densities of negative charges  $Q_{e-}$  are shown, with  $Q_{\rm STI} = 5 \times 10^{17}$  cm<sup>-3</sup>.

$Q_{\text{STI}} = 5 \times 10^{17} \text{ cm}^{-3}$ , in agreement with typical expected charge trapping in the STI [14], [63]. Positive charge enhances the effective height ( $h_{\text{eff}}$ ) of the device channel, which extends a little deeper into the fin substrate. Fig. 11(c) simulates

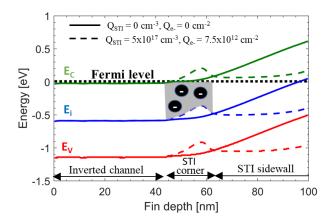

Fig. 13. Simulated band diagrams as a function of fin depth, considering the cutline shown in Fig. 11(a), i.e., at 1 nm from the Si/SiO<sub>2</sub> interface. The band diagram refers to an nFinFET biased with  $V_{\rm gs} = 0.9$  V. Continuous line refers to the pre-irradiation condition and dotted lines refer to  $Q_{\rm STI} = 5 \times 10^{17}$  cm<sup>-3</sup> and  $Q_{e-} = 7.5 \times 10^{12}$  cm<sup>-2</sup>. The plot shows that interface traps located in the STI corner are charged negatively, as the Fermi level is above the intrinsic level.

ultrahigh dose effects, considering the contribution of negative trapped charge in the STI corners at  $Q_{e-} = 7.5 \times 10^{12} \text{ cm}^{-2}$ , which is in the range of density of interface traps expected at STI corner/semiconductor interfaces [13], [19], [64]. This negative charge compensates for the effect of positive charge, depleting the Si channel region near the STI corners and thus reducing  $h_{\text{eff}}$ .

Variations in  $h_{\text{eff}}$  that occur as a result of radiation-induced charge trapping in the STI are highlighted in Fig. 11(d), which shows the electron density as a function of fin depth, evaluated at a cutline at 1 nm from the Si/SiO<sub>2</sub> interface. The depth of 0 nm corresponds to the top of the fin, with the increase in value moving down in the fin substrate. Depths

Fig. 14. TCAD simulation of nFinFETs when  $V_{gs} = 0$  V (channel OFF). The images show TID-induced mechanisms increasing the  $I_{OFF}$  current. The color scale shows the electron density in the Si channel fin. (a) Pre-irradiation without any trapped charge in the oxides. (b) At high doses with positive trapped charge in STI ( $Q_{STI} = 5 \times 10^{17}$  cm<sup>-3</sup>). (c) At ultrahigh doses with positive and negative trapped charge ( $Q_{STI} = 5 \times 10^{17}$  cm<sup>-3</sup> and  $Q_{e-} = 7.5 \times 10^{12}$  cm<sup>-2</sup>). Values of  $Q_{STI}$  are uniformly distributed in the STI, while the  $Q_{e-}$  values are localized at the Si/SiO<sub>2</sub> interface close to the upper corners of the STI. (d) Electron density in the Si fin as a function of fin height, considering the cutline shown in Fig. 11(a), i.e., at 1 nm from the Si/SiO<sub>2</sub> interface.

with high  $e^-$  densities [> 5 × 10<sup>18</sup> cm<sup>-3</sup>; see dotted line in Fig. 11(a)] identify  $h_{\rm eff}$ , corresponding to inverted Si regions. For example, before irradiation (black curve),  $h_{\rm eff}$  is ~55 nm. The value of  $h_{\rm eff}$  increases to ~59 nm when positive  $Q_{\rm STI} = 5 \times 10^{17}$  cm<sup>-3</sup> is added, and the value of  $h_{\rm eff}$  decreases to ~46 nm when negative  $Q_{e-} = 7.5 \times 10^{12}$  cm<sup>-2</sup> are added in addition to  $Q_{\rm STI}$ .

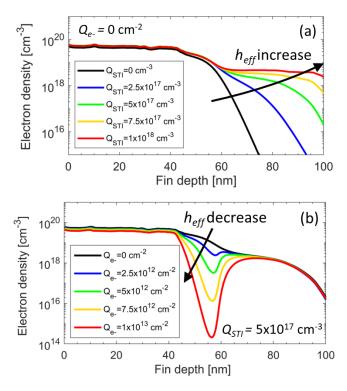

The initial increase of  $h_{\rm eff}$  in Fig. 11(b) and the associated reduction of  $h_{\rm eff}$  in Fig. 11(c) agree well with the turnaround of the experimental  $g_m$  visible in Fig. 4(a), as  $g_m$  is approximately proportional to the effective channel height  $h_{\rm eff}$ . Modulation of  $h_{\rm eff}$  may occur due to both positive charges in STI and negative charges in the STI corners. The simulation results in Fig. 12 highlight the  $h_{\rm eff}$  modulation effect induced by several densities of  $Q_{\text{STI}}$  and  $Q_{e-}$ . In Fig. 12(a), the electron concentration is plotted for different densities of  $Q_{STI}$ . Positive charges in the STI contribute to enhancement of the inversion layer close to the upper corner of the STI, thus increasing  $h_{\rm eff}$ . In Fig. 12(b), the effects of electron trapping in the STI corner are studied for different densities of  $Q_{e-}$  when positive charges are trapped in the STI ( $Q_{\text{STI}} = 5 \times 10^{17} \text{ cm}^{-3}$ ). The plot highlights the effects induced by negative charges on the  $h_{\rm eff}$ . The black curve refers to only positive trapped charge, representing the condition at 10 Mrad with the highest  $h_{\rm eff}$ . By increasing densities of compensating trapped negative charge in the STI corners,  $h_{\rm eff}$  decreases with slight changes in electrical response of the main channel, consistent with the constant  $V_{\text{th}}$  and SS in Fig. 4.

The slight increase of the SS and increase of the LFN at doses > 10 Mrad suggest that the nature of the negative charges of mechanism #2 is most likely interface traps, whose generation is typically slow, electric field driven, and temperature dependent [55], [57], [58], [59], [60], [61]. Moreover,

the amphoteric nature of interface traps [65], [66] fits with this explanation of both  $g_m$  and  $I_{OFF}$  degradation. As shown by the band diagram of Fig. 13, interface traps located at the STI corners are negatively charged when the channel is in inversion, causing a drop in  $g_m$ .

In contrast, these interface traps are partially filled when devices are in the subthreshold region, thus affecting much less  $I_{\text{OFF}}$ , for which the increase relies primarily on positive charges trapped in the STI sidewalls. The interface traps at the STI corners can be partially filled with positive or negative charges, depending on the position of the Fermi energy with respect to the intrinsic level of Si. The mechanism increasing the  $I_{OFF}$  current is shown in Fig. 14 through simulations at  $V_{\rm gs} = 0$  V (channel not inverted). The color scale indicates the electron density in the Si channel fin, as in Fig. 11. In Fig. 14(a), the p-substrate region is in accumulation, having an e<sup>-</sup> density of 10<sup>10</sup> cm<sup>-3</sup>. In Fig. 14(b), positive charge  $(Q_{\rm STI} = 5 \times 10^{17} {\rm cm}^{-3})$  is added in the STI, leading to an increase in e<sup>-</sup> density in the Si regions close to STI sidewalls. These Si regions with high e<sup>-</sup> density activate two parasitic leakage paths deep in the STI sidewalls, responsible for the increase of  $I_{\text{OFF}}$  [8], [15], [16], [18], [26]. Fig. 14(c) represents the case, in which the Fermi level is higher than the intrinsic level, thus the case with negative trapped charge. Even at relatively high  $Q_{e^-} = 7.5 \times 10^{12} \text{ cm}^{-2}$ , the parasitic transistors are still activated, in agreement with the continuous increase of the  $I_{OFF}$  of Fig. 5. This effect is highlighted in Fig. 14(d), which shows  $e^-$  density as a function of fin depth. The peak in e<sup>-</sup> density is found in the deep Si regions, before and after negative  $Q_{e^-}$  charge is added in the STI corners. The height of the e<sup>-</sup>density peak depends mainly on  $Q_{STI}$  but can still be slightly influenced by  $Q_{e-}$ . In conclusion, in the case of partially filled positive interface traps or in the case of partially filled negative interface traps, the parasitic transistors located in the deep Si regions are still conducting, leading to the  $I_{\text{OFF}}$  increase visible in Fig. 5.

# VI. CONCLUSION

The results of this work clarify the nature of TID mechanisms in n-channel FinFETs, identifying critical TID issues related to charge trapping in the upper corners of STI oxides. The 16-nm Si nFinFETs irradiated up to ultrahigh doses exhibit a turnaround in  $g_m$  above 3–10 Mrad and a continuous increase in drain leakage current at higher doses. Worst case degradation is found when positive bias is applied to the gate, with  $V_{\text{th}}$  and SS relatively insensitive to accumulated dose.

Experimental results, combined with TCAD simulations, identify two different dominating TID mechanisms that induce nonuniform charge trapping in the STI oxides. The first mechanism is related to positive charge trapping in the STI sidewalls. Positive charge causes a monotonic increase of the drain-to-source leakage current and improves  $g_m$  due to an increase in the effective channel height. The larger dimensions of the lateral STI oxides compared with the smaller dimensions of intra-fin STI enhance the relative  $I_{OFF}$  degradation of transistors with a smaller number of fins. On the other hand, a second slower mechanism appears at doses > 10 Mrad causing the formation of negative trapped charge in the upper corners of the STI. The negative charge compensates the effect of positive charges and degrades the transistors  $g_m$  due to the reduction of the effective channel height. The generation of border/interface traps and the activation of hydrogen-assisted processes at Si/oxide interface lead to significant increases in LFN at doses > 10 Mrad. These results resolve several puzzling issues from previous studies of FinFETs at ultrahigh radiation doses, and point to the need to continuously monitor and improve the channel/STI interfaces of advanced MOS technologies.

#### ACKNOWLEDGMENT

The authors would like to thank Andrea Baschirotto for providing the 16-nm FinFET devices in the framework of the FinFET16v2 project of the National Institute for Nuclear Physics—INFN, Italy.

#### REFERENCES

- J. R. Schwank et al., "Radiation effects in MOS oxides," *IEEE Trans. Nucl. Sci.*, vol. 55, no. 4, pp. 1833–1853, Aug. 2008.

- [2] H. J. Barnaby, "Total-ionizing-dose effects in modern CMOS technologies," *IEEE Trans. Nucl. Sci.*, vol. 53, no. 6, pp. 3103–3121, Dec. 2006.

- [3] D. M. Fleetwood, "Radiation effects in a post-Moore world," *IEEE Trans. Nucl. Sci.*, vol. 68, no. 5, pp. 509–545, May 2021.

- [4] T. R. Oldham and F. B. McLean, "Total ionizing dose effects in MOS oxides and devices," *IEEE Trans. Nucl. Sci.*, vol. 50, no. 3, pp. 483–499, Jun. 2003.

- [5] J. M. Benedetto, H. E. Boesch, F. B. McLean, and J. P. Mize, "Hole removal in thin-gate MOSFETs by tunneling," *IEEE Trans. Nucl. Sci.*, vol. NS-32, no. 6, pp. 3916–3920, Dec. 1985.

- [6] F. Faccio, S. Michelis, D. Cornale, A. Paccagnella, and S. Gerardin, "Radiation-induced short channel (RISCE) and narrow channel (RINCE) effects in 65 and 130 nm MOSFETs," *IEEE Trans. Nucl. Sci.*, vol. 62, no. 6, pp. 2933–2940, Dec. 2015.

- [7] L. Ding et al., "Radiation tolerance study of a commercial 65 nm CMOS technology for high energy physics applications," *Nucl. Instrum. Methods Phys. Res. A, Accel. Spectrom. Detect. Assoc. Equip.*, vol. 831, pp. 265–268, Sep. 2016.

- [8] C.-M. Zhang et al., "Characterization of GigaRad total ionizing dose and annealing effects on 28-nm bulk MOSFETs," *IEEE Trans. Nucl. Sci.*, vol. 64, no. 10, pp. 2639–2647, Oct. 2017.

- [9] S. Bonaldo et al., "Ionizing-radiation response and low-frequency noise of 28-nm MOSFETs at ultrahigh doses," *IEEE Trans. Nucl. Sci.*, vol. 67, no. 7, pp. 1302–1311, Jul. 2020.

- [10] M. Gaillardin, V. Goiffon, S. Girard, M. Martinez, P. Magnan, and P. Paillet, "Enhanced radiation-induced narrow channel effects in commercial 0.18 μm bulk technology," *IEEE Trans. Nucl. Sci.*, vol. 58, no. 6, pp. 2807–2815, Dec. 2011.

- [11] S. Gerardin et al., "Impact of 24-GeV proton irradiation on 0.13-μm CMOS devices," *IEEE Trans. Nucl. Sci.*, vol. 53, no. 4, pp. 1917–1922, Aug. 2006.

- [12] F. Faccio et al., "Influence of LDD spacers and H<sup>+</sup> transport on the total-ionizing-dose response of 65-nm MOSFETs irradiated to ultrahigh doses," *IEEE Trans. Nucl. Sci.*, vol. 65, no. 1, pp. 164–174, Jan. 2018.

- [13] S. Bonaldo et al., "Charge buildup and spatial distribution of interface traps in 65-nm pMOSFETs irradiated to ultrahigh doses," *IEEE Trans. Nucl. Sci.*, vol. 66, no. 7, pp. 1574–1583, Jul. 2019.

- [14] S. Bonaldo et al., "Influence of halo implantations on the total ionizing dose response of 28-nm pMOSFETs irradiated to ultrahigh doses," *IEEE Trans. Nucl. Sci.*, vol. 66, no. 1, pp. 82–90, Jan. 2019.

- [15] M. Turowski, A. Raman, and R. D. Schrimpf, "Nonuniform total-doseinduced charge distribution in shallow-trench isolation oxides," *IEEE Trans. Nucl. Sci.*, vol. 51, no. 6, pp. 3166–3171, Dec. 2004.

- [16] M. R. Shaneyfelt, P. E. Dodd, B. L. Draper, and R. S. Flores, "Challenges in hardening technologies using shallow-trench isolation," *IEEE Trans. Nucl. Sci.*, vol. 45, no. 6, pp. 2584–2592, Dec. 1998.

- [17] S. Mattiazzo et al., "Total ionizing dose effects on a 28 nm Hi-K metalgate CMOS technology up to 1 Grad," J. Instrum., vol. 12, no. 2, Feb. 2017, Art. no. C02003.

- [18] M. L. McLain, H. J. Barnaby, and G. Schlenvogt, "Effects of channel implant variation on radiation-induced edge leakage currents in n-channel MOSFETs," *IEEE Trans. Nucl. Sci.*, vol. 64, no. 8, pp. 2235–2241, Aug. 2017.

- [19] N. Rezzak et al., "The sensitivity of radiation-induced leakage to STI topology and sidewall doping," *Microelectron. Rel.*, vol. 51, no. 5, pp. 889–894, May 2011.

- [20] T. Ma et al., "TID degradation mechanisms in 16 nm bulk FinFETs irradiated to ultra-high doses," *IEEE Trans. Nucl. Sci.*, vol. 68, no. 8, pp. 1571–1578, Aug. 2021.

- [21] T. Ma et al., "Influence of fin and finger number on TID degradation of 16-nm bulk FinFETs irradiated to ultrahigh doses," *IEEE Trans. Nucl. Sci.*, vol. 69, no. 3, pp. 307–313, Mar. 2022.

- [22] S. Bonaldo et al., "DC response, low-frequency noise, and TID-induced mechanisms in 16-nm FinFETs for high-energy physics experiments," *Nucl. Instrum. Methods Phys. Res. A, Accel. Spectrom. Detect. Assoc. Equip.*, vol. 1033, Jun. 2022, Art. no. 166727.

- [23] I. Chatterjee et al., "Bias dependence of total ionizing dose response in bulk FinFETs," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 6, pp. 4476–4482, Dec. 2013.

- [24] M. Gaillardin et al., "Total ionizing dose response of multiple-gate nanowire field effect transistors," *IEEE Trans. Nucl. Sci.*, vol. 64, no. 8, pp. 2061–2068, Aug. 2017.

- [25] M. Gorchichko et al., "Total-ionizing-dose effects and low-frequency noise in 30-nm gate-length bulk and SOI FinFETs with SiO<sub>2</sub>/HfO<sub>2</sub> gate dielectrics," *IEEE Trans. Nucl. Sci.*, vol. 67, no. 1, pp. 245–252, Jan. 2020.

- [26] T. Wallace et al., "Layout dependence of total ionizing dose effects on 12-nm bulk FinFET core digital structures," *IEEE Trans. Nucl. Sci.*, vol. 70, no. 4, pp. 620–626, Apr. 2023.

- [27] T. Ma et al., "Increased device variability induced by total ionizing dose in 16-nm bulk nFinFETs," *IEEE Trans. Nucl. Sci.*, vol. 69, no. 7, pp. 1437–1443, Jul. 2022.

- [28] I. Chatterjee et al., "Geometry dependence of total-dose effects in bulk FinFETs," *IEEE Trans. Nucl. Sci.*, vol. 61, no. 6, pp. 2951–2958, Dec. 2014.

- [29] M. Gaillardin, P. Paillet, V. Ferlet-Cavrois, O. Faynot, C. Jahan, and S. Cristoloveanu, "Total ionizing dose effects on triple-gate FETs," *IEEE Trans. Nucl. Sci.*, vol. 53, no. 6, pp. 3158–3165, Dec. 2006.

- [30] E. Simoen et al., "Radiation effects in advanced multiple gate and silicon-on-insulator transistors," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 3, pp. 1970–1991, Jun. 2013.

- [31] M. P. King et al., "Analysis of TID process, geometry, and bias condition dependence in 14-nm FinFETs and implications for RF and SRAM performance," *IEEE Trans. Nucl. Sci.*, vol. 64, no. 1, pp. 285–292, Jan. 2017.

- [32] Z. Ren et al., "TID response of bulk Si PMOS FinFETs: Bias, fin width, and orientation dependence," *IEEE Trans. Nucl. Sci.*, vol. 67, no. 7, pp. 1320–1325, Jul. 2020.

- [33] D. James, "Moore's Law continues into the 1x-nm era," in *Proc. 27th Annu. SEMI Adv. Semiconductor Manuf. Conf. (ASMC)*, May 2016, pp. 324–329.

- [34] C. Auth et al., "A 10 nm high performance and low-power CMOS technology featuring 3<sup>rd</sup> generation FinFET transistors, self-aligned quad patterning, contact over active gate and cobalt local interconnects," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2017, pp. 673–676.

- [35] D. Bisello, A. Candelori, A. Kaminski, A. Litovchenko, E. Noah, and L. Stefanutti, "X-ray radiation source for total dose radiation studies," *Radiat. Phys. Chem.*, vol. 71, no. 3, pp. 713–715, 2004.

- [36] A. Ortiz-Conde, F. J. García-Sánchez, J. Muci, A. T. Barrios, J. J. Liou, and C.-S. Ho, "Revisiting MOSFET threshold voltage extraction methods," *Microelectron. Rel.*, vol. 53, no. 1, pp. 90–104, Jan. 2013.

- [37] D. M. Fleetwood, "1/f noise and defects in microelectronic materials and devices," *IEEE Trans. Nucl. Sci.*, vol. 62, no. 4, pp. 1462–1486, Aug. 2015.

- [38] D. M. Fleetwood, "Total-ionizing-dose effects, border traps, and 1/f noise in emerging MOS technologies," *IEEE Trans. Nucl. Sci.*, vol. 67, no. 7, pp. 1216–1240, Jul. 2020.

- [39] J. H. Scofield, T. P. Doerr, and D. M. Fleetwood, "Correlation of preirradiation 1/f noise and postirradiation threshold voltage shifts due to oxide-trapped charge in MOS transistors," *IEEE Trans. Nucl. Sci.*, vol. 36, no. 6, pp. 1946–1955, Dec. 1989.

- [40] S. A. Francis, A. Dasgupta, and D. M. Fleetwood, "Effects of total dose irradiation on the gate-voltage dependence of the 1/*f* noise of nMOS and pMOS transistors," *IEEE Trans. Electron Devices*, vol. 57, no. 2, pp. 503–510, Feb. 2010.

- [41] D. M. Fleetwood et al., "Unified model of hole trapping, 1/f noise, and thermally stimulated current in MOS devices," *IEEE Trans. Nucl. Sci.*, vol. 49, no. 6, pp. 2674–2683, Dec. 2002.

- [42] G. Ghibaudo, O. Roux, C. Nguyen-Duc, F. Balestra, and J. Brini, "Improved analysis of low frequency noise in field-effect MOS transistors," *Phys. Status Solidi A*, vol. 124, no. 2, pp. 571–581, Apr. 1991.

- [43] D. M. Fleetwood, "Total ionizing dose effects in MOS and low-doserate-sensitive linear-bipolar devices," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 3, pp. 1706–1730, Jun. 2013.

- [44] D. Fleetwood et al., "Effects of oxide traps, interface traps, and 'border traps' on metal-oxide-semiconductor devices," J. Appl. Phys., vol. 73, no. 10, pp. 5058–5074, 1993.

- [45] J. H. Scofield, N. Borland, and D. M. Fleetwood, "Reconciliation of different gate-voltage dependencies of 1/f noise in n-MOS and p-MOS transistors," *IEEE Trans. Electron Devices*, vol. 41, no. 11, pp. 1946–1952, Nov. 1994.

- [46] S. Bonaldo and D. M. Fleetwood, "Random telegraph noise in nanometer-scale CMOS transistors exposed to ionizing radiation," *Appl. Phys. Lett.*, vol. 122, no. 17, Apr. 2023, Art. no. 173508.

- [47] D. M. Fleetwood, "Interface traps, correlated mobility fluctuations, and low-frequency noise in metal-oxide-semiconductor transistors," *Appl. Phys. Lett.*, vol. 122, no. 17, Apr. 2023, Art. no. 173504.

- [48] M. Gorchichko et al., "Total-ionizing-dose response of highly scaled gate-all-around Si nanowire CMOS transistors," *IEEE Trans. Nucl. Sci.*, vol. 68, no. 5, pp. 687–696, May 2021.

- [49] S. Bonaldo et al., "TID effects in highly scaled gate-all-around Si nanowire CMOS transistors irradiated to ultrahigh doses," *IEEE Trans. Nucl. Sci.*, vol. 69, no. 7, pp. 1444–1452, Jul. 2022.

- [50] D. M. Fleetwood, "Low-frequency noise in nanowires," *Nanoscale*, vol. 15, no. 29, pp. 12175–12192, Jul. 2023.

- [51] D. M. Fleetwood, E. X. Zhang, R. D. Schrimpf, S. T. Pantelides, and S. Bonaldo, "Effects of interface traps and hydrogen on the lowfrequency noise of irradiated MOS devices," *IEEE Trans. Nucl. Sci.*, early access, Oct. 10, 2023, doi: 10.1109/TNS.2023.3323548.

- [52] V. Re, M. Manghisoni, L. Ratti, V. Speziali, and G. Traversi, "Impact of lateral isolation oxides on radiation-induced noise degradation in CMOS technologies in the 100-nm regime," *IEEE Trans. Nucl. Sci.*, vol. 54, no. 6, pp. 2218–2226, Dec. 2007.

- [53] L. Ratti, L. Gaioni, M. Manghisoni, G. Traversi, and D. Pantano, "Investigating degradation mechanisms in 130 nm and 90 nm commercial CMOS technologies under extreme radiation conditions," *IEEE Trans. Nucl. Sci.*, vol. 55, no. 4, pp. 1992–2000, Aug. 2008.

- [54] V. Re, L. Gaioni, M. Manghisoni, L. Ratti, and G. Traversi, "Comprehensive study of total ionizing dose damage mechanisms and their effects on noise sources in a 90 nm CMOS technology," *IEEE Trans. Nucl. Sci.*, vol. 55, no. 6, pp. 3272–3279, Dec. 2008.

- [55] P. S. Winokur, H. E. Boesch, J. M. McGarrity, and F. B. McLean, "Field- and time-dependent radiation effects at the SiO<sub>2</sub>/Si interface of hardened MOS capacitors," *IEEE Trans. Nucl. Sci.*, vol. NS-24, no. 6, pp. 2113–2118, Dec. 1977.

- [56] F. B. McLean, "A framework for understanding radiation-induced interface states in SiO<sub>2</sub> MOS structures," *IEEE Trans. Nucl. Sci.*, vol. NS-27, no. 6, pp. 1651–1657, Dec. 1980.

- [57] M. R. Shaneyfelt, J. R. Schwank, D. M. Fleetwood, P. S. Winokur, K. L. Hughes, and F. W. Sexton, "Field dependence of interface-trap buildup in polysilicon and metal gate MOS devices," *IEEE Trans. Nucl. Sci.*, vol. 37, no. 6, pp. 1632–1640, Dec. 1990.

- [58] N. S. Saks, R. B. Klein, and D. L. Griscom, "Formation of interface traps in MOSFETs during annealing following low temperature irradiation," *IEEE Trans. Nucl. Sci.*, vol. 35, no. 6, pp. 1234–1240, Dec. 1988.

- [59] S. N. Rashkeev, D. M. Fleetwood, R. D. Schrimpf, and S. T. Pantelides, "Proton-induced defect generation at the Si-SiO<sub>2</sub> interface," *IEEE Trans. Nucl. Sci.*, vol. 48, no. 6, pp. 2086–2092, Dec. 2001.

- [60] D. M. Fleetwood, "Effects of hydrogen transport and reactions on microelectronics radiation response and reliability," *Microelectron. Rel.*, vol. 42, nos. 4–5, pp. 523–541, Apr. 2002.

- [61] D. M. Fleetwood, "Effects of bias and temperature on interface-trap annealing in MOS and linear bipolar devices," *IEEE Trans. Nucl. Sci.*, vol. 69, no. 3, pp. 587–608, Mar. 2022.

- [62] F. Faccio et al., "Total ionizing dose effects in shallow trench isolation oxides," *Microelectron. Rel.*, vol. 48, no. 7, pp. 1000–1007, Jul. 2008.

- [63] L.-Å. Ragnarsson and P. Lundgren, "Electrical characterization of P<sub>b</sub> centers in (100)Si–SiO<sub>2</sub> structures: The influence of surface potential on passivation during post metallization anneal," *J. Appl. Phys.*, vol. 88, no. 2, pp. 938–942, Jul. 2000.

- [64] I. S. Esqueda, H. J. Barnaby, and M. L. Alles, "Two-dimensional methodology for modeling radiation-induced off-state leakage in CMOS technologies," *IEEE Trans. Nucl. Sci.*, vol. 52, no. 6, pp. 2259–2264, Dec. 2005.

- [65] P. M. Lenahan and P. V. Dressendorfer, "Hole traps and trivalent silicon centers in MOS devices," J. Appl. Phys., vol. 55, no. 10, pp. 3495–3499, May 1984.

- [66] D. M. Fleetwood, "Long-term annealing study of midgap interface-trap charge neutrality," *Appl. Phys. Lett.*, vol. 60, no. 23, pp. 2883–2885, Jun. 1992.