# Multilevel 3-D Device Simulation Approach Applied to Deeply Scaled Nanowire Field Effect Transistors

Natalia Seoane<sup>®</sup>, *Member, IEEE*, Karol Kalna<sup>®</sup>, *Senior Member, IEEE*, Xavier Cartoixà<sup>®</sup>, *Member, IEEE*, and Antonio García-Loureiro<sup>®</sup>, *Member, IEEE*

Abstract—Three silicon nanowire (SiNW) field effect transistors (FETs) with 15-, 12.5- and 10.6-nm gate lengths are simulated using hierarchical multilevel quantum and semiclassical models verified against experimental  $I_D-V_G$  characteristics. The tight-binding (TB) formalism is employed to obtain the band structure in k-space of ellipsoidal NWs to extract electron effective masses. The masses are transferred into quantum-corrected 3-D finite element (FE) drift-diffusion (DD) and ensemble Monte Carlo (MC) simulations, which accurately capture the quantum-mechanical confinement of the ellipsoidal NW cross sections. We demonstrate that the accurate parameterization of the bandstructure and the quantum-mechanical confinement has a profound impact on the computed  $I_D - V_G$ characteristics of nanoscaled devices. Finally, we devise a step-by-step technology computer-aided design (TCAD) methodology of simple parameterization for efficient DD device simulations.

Index Terms— Drift-diffusion (DD), Monte Carlo (MC), nanowire (NW), semiconductor device simulation, tight-binding (TB).

#### I. INTRODUCTION

THE 3-D multigate architectures are ruling industry lines since fin-like field-effect transistors (FinFETs) were adopted as the new standard architecture. The faster and less power-hungry FinFETs facilitate continuous scaling of semiconductor transistors [1] by increasing transistor density on a chip and reducing costs [2]. However, this architecture

Manuscript received 4 April 2022; revised 31 May 2022 and 24 June 2022; accepted 30 June 2022. Date of publication 15 July 2022; date of current version 23 August 2022. The work of Natalia Seoane and Antonio García-Loureiro was supported by the Spain's Ministerio de Ciencia e Innovación/Xunta de Galicia/ European Regional Development Fund, under Grant RYC-2017-23312, Grant PID2019-104834GB-I00, and Grant ED431F-2020/008. The work of Xavier Cartoixà was supported by the Spain's Ministerio de Ciencia, Innovación y Universidades under Grant RTI2018-097876-B-C21 (MCIU/AEI/FEDER). The review of this article was arranged by Editor S.-M. Hong. (Corresponding author: Natalia Seoane.)

Natalia Seoane and Antonio García-Loureiro are with the Centro Singular de Investigación en Tecnoloxías Intelixentes (CITIUS), Universidade de Santiago de Compostela, 15705 Santiago de Compostela, Spain (e-mail: natalia.seoane@usc.es).

Karol Kalna is with the Nanoelectronic Devices Computational Group, Faculty of Science and Engineering, Swansea University, Wales SA2 8PP, U.K.

Xavier Cartoixà is with the Departament d'Enginyeria Electrònica, Universitat Autònoma de Barcelona, 08193 Barcelona, Spain.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2022.3188945.

Digital Object Identifier 10.1109/TED.2022.3188945

cannot provide the required electrostatic integrity when scaled to future sub-5-nm technology nodes [3]. Hence, gate-all-around nanowire (NW) FETs are considered as a replacement [4] thanks to their superior electrostatic integrity against FinFETs [5] and nanosheet FETs [6].

Modeling of semiconductor devices via technology computer-aided design (TCAD) undoubtedly plays an essential role in the scaling of transistors [7]. TCAD tools based on quantum-mechanical corrected classical and semiclassical transport methods can provide a good tradeoff between the simulation precision and computational cost. The quantum corrections can be included via the density gradient (DG) approach, limited by the fitting of DG effective masses [8], or through the solution of the Schrödinger (SCH) equation, which is calibration-free [9]. However, when studying devices with channel cross section dimensions below 10 nm, geometry starts to play a substantial role in the band-structure [10]. The quest for an accurate band-structure leads to a couple of approaches to use. The effective mass approximation [11] is relatively simple and accurate near the conduction band (CB) minima [12] but will struggle to correctly estimate the quantization levels in nanostructures [10]. On the other hand, the  $sp^3d^5s^*$  nearest-neighbor empirical tight-binding (TB) model [13] gives a full Brillouin zone description of the bandstructure, allowing to atomistically discretize a realistic device at nanometer scale [14]. The effects of the quantum confinement band-structure in silicon NWs (SiNWs) were studied before [15]–[17], however, previous works: 1) calculated only a low-field mobility and/or 2) did not compare the results against experimental data obtained from a SiNW FET.

In this work, we use multilevel 3-D material and device simulations to obtain the  $I_D$ – $V_G$  characteristics for three ellipsoidal  $\langle 110 \rangle$  SiNW FETs with 15-, 12.5-, and 10.6-nm gate lengths, using bulk and quantum-mechanically confined electron effective masses of silicon. These gate lengths were chosen following the International Roadmap for Devices and Systems (IRDS) predictions for sub-5-nm industry nodes [18]. The 15-nm gate length simulated results are initially compared to experimental data [19]. Then, we analyze the role of quantum-mechanical confinement on the silicon band-structure for the three SiNW FETs. Finally, we present a step-by-step methodology of a relatively simple parameterization for speedy drift-diffusion (DD) quantum-corrected simulations.

# II. SIMULATION METHODOLOGY

To model the SiNW FETs, we use a multiscale simulation approach. Initially, we perform empirical TB band-structure calculations for the SiNWs to provide bandstructure parameters for electron transport simulations. These parameters are introduced into an in-house-built Variability Enabled Nanometric Device Simulator (VENDES) [20] that include 3-D finite-element (FE) self-consistent classical and semiclassical transport models. The classical transport approach is the DD method, which is a workhorse of many commercial TCAD tools [21]. The semiclassical transport model is the ensemble Monte Carlo (MC) technique, which is widely recognized as an accurate predictive simulation technique for semiconductor devices operating in a highly nonequilibrium transport regime [22]. Note that transport simulations are selfconsistently run with solutions of the Poisson equation, using the linear scheme, accounting for long-range electron-electron interactions [7].

Since quantum-mechanical confinement will play a role in the carrier transport in the SiNW FETs, both transport approaches incorporate quantum confinement corrections via the solution of 2-D FE SCH equation. The quantum corrected DD model of carrier transport is used when the diffusion transport dominates, in the subthreshold/OFF-region of device operation. The ensemble MC transport technique is used when a highly nonequilibrium carrier transport dominates, in the ON-region of device operation. This quantumcorrected ensemble MC technique was proven to reproduce the highly nonequilibrium carrier transport in weakly quantummechanically confined systems in [23] and [24]. The advantages of the quantum corrected 3-D FE MC simulations are: 1) the solutions of 2-D FE SCH equation accurately determine the carrier density distribution along the channel [25]; 2) the device domain described by the 3-D FE mesh precisely reproduces nonequilibrium electron transport in the device active region including interface roughness (IR); and 3) the accurate injection of electrons into the channel from a heavily doped source/drain (S/D) thanks to self-consistent Fermi-Dirac statistics used for the electron scattering with ionized impurities.

# A. Tight-Binding Model

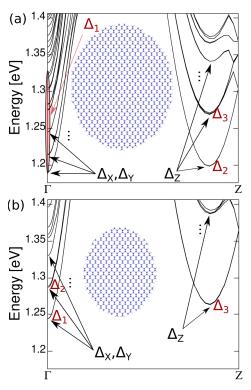

A 20-band  $sp^3d^5s^*$  nearest-neighbor TB model [13] is selected in order to obtain realistic dispersion relations of the SiNWs. The parameterization by Niquet *et al.* [26] was chosen because of its accurate reproduction of both the experimental electron and hole effective masses along all directions in **k**-space, crucial for accurate determination of the confinement energies. This parameterization yields a fundamental bandgap energy of 1.17 eV for bulk Si. Thus, all the CB levels obtained from the TB calculation were downshifted by 0.05 eV to account for finite temperature, and the gap values we report hereafter reflect this correction. In the calculation, surface dangling bonds were passivated by H atoms, with the Si–H bonds parameterized according to the values provided in [27]. Fig. 1 shows the bands for two SiNWs with ellipsoidal cross

Fig. 1. CB dispersion between Γ and the edge of the Brillouin zone (Z) along the transport direction (z-axis in Fig. 2) for (a)  $7.15 \times 8.99 \, \text{nm}^2$  and (b)  $5.06 \times 6.36 \, \text{nm}^2$  cross section SiNWs. The energy levels have been downshifted 0.05 eV to set the bulk CB edge at 1.12 eV. Blue (light gray) circles represent Si (H) atoms. The levels originating from the bulk  $\Delta_Z$  pocket and the folding of the bulk  $\Delta_X$ ,  $\Delta_Y$  pockets are labeled. Also,  $\Delta_1$ ,  $\Delta_2$  and  $\Delta_3$  indicate the bands that will be treated explicitly by the MC simulator. In particular,  $\Delta_1$  for the large SiNW captures the behavior of many Γ subbands.

sections, indicating the minima originating from the  $\Delta_Z$  pocket and the folding of the  $\Delta_X$ ,  $\Delta_Y$  pockets.

### B. Ensemble Monte Carlo Simulations

The MC engine simulating kinetics of electrons in the semiconductor device utilizes a nonparabolic anisotropic model within the effective mass approximation [11], [28] and it includes electron scattering mechanisms assuming first-order perturbation theory (Fermi Golden Rule). It considers electron scattering with acoustic and nonpolar optical phonons (intravalley and intervalley) [22], [29], ionized impurity scattering using the third body exclusion [30], and IR scattering using Ando's model [31]. The electron screening in ionized impurity scattering incorporates a self-consistent calculation of Fermi energy and electron temperature from the electron density and the average electron energy [32] at every real position of the electron in a 3-D simulation domain. More details on the 3-D FE MC engine can be found in [9] and [24].

# C. Schrödinger Equation Quantum Corrections

The quantum corrections are incorporated by solving the 2-D FE SCH equation repeatedly across 2-D slices perpendicular to the transport direction, equidistantly placed along the device. The SCH equation is solved in a minimum of

the conduction valley of Si assuming longitudinal and transverse electron effective masses while still considering the penetration of wave-functions into a surrounding dielectric layer [9], [23]. The SCH equation quantum corrections assume Boltzmann statistics but are anisotropic since the longitudinal and the transverse electron effective masses depend on the valley orientation with a degeneracy factor of 2. Quantum electron density,  $n_{\rm Sch}(y,z)$ , is thus obtained separately for each of the three  $\Delta$  valleys in Si [33]. For each valley, this 2-D electron density is interpolated into a 3-D FE domain to calculate  $n_{\rm Sch}({\bf r})$ . This electron density  $n_{\rm Sch}({\bf r})$  is then used to calculate the quantum-corrected electrostatic potential  $V_{QC}({\bf r})$  [34].

# D. Parameter Extraction for Drift-Diffusion

For fast turnaround in performance screening, the DD transport model is often desirable, despite assuming a near-equilibrium carrier transport in nanoscale transistors for all biases. We generate a workflow to turn the dispersion relations from the TB model in Section II-A into parameters suited for DD simulations as follows.

- 1) Conduction subband minima,  $E_{ci}$ , and effective masses,  $m_i^*$ , are computed by diagonalization of the TB Hamiltonian and extraction from the subband curvatures.

- 2) The density-of-states (DOS) effective mass in 1-D is obtained by a proper weighting of the individual subband DOS effective masses as

$$(m_{\text{DD},\text{DOS},1-D}^*)^{1/2} = \sum_{i \in \text{CB}} g_i (m_i^*)^{1/2} e^{-\frac{E_{ci} - E_{c0}}{k_B T}}$$

(1)

where  $k_B$  is Boltzmann's constant, T is the temperature, i runs over the CB subbands,  $g_i$  is the degeneracy of a subband excluding spin ( $g_i = 1$  for a spin-degenerate 1-D subband), and  $E_{ci} - E_{c0}$  is the energy distance between the ith subband and the lowest CB energy.

3) The DOS effective mass in 1-D is adapted to be used in 3-D simulators by

$$(m_{\text{DD},\text{DOS},3-D}^*)^{3/2} = \frac{2\pi \hbar^2}{Ak_B T} (m_{\text{DD},\text{DOS},1-D}^*)^{1/2}$$

(2)

where A is the NW cross section.

4) The average scattering time  $\tau$  and the transport effective mass  $m^*_{DD,t,1-D}$  are calculated from an experimental or computed diffusive mobility,  $\mu_{diff}$ , which is the long channel mobility, obtained when  $L \gg \langle \langle \lambda \rangle \rangle$ , being L the effective channel length and  $\langle \langle \lambda \rangle \rangle$  the average mean free path [35], by solving the equation

$$\tau = \frac{\mu_{\text{diff}} m_{\text{DD},t,1-D}^*}{q}$$

$$\frac{1/m_{\text{DD},t,1-D}^*}{\pi \tau \sqrt{\frac{2k_B T}{\pi m_{\text{DD},t,1-D}^*}} + L} = \left(m_{\text{DD},\text{DOS},1-D}^*\right)^{-1/2}$$

$$\times \sum_{i} g_i \frac{\left(m_i^*\right)^{-1/2}}{\pi \tau \sqrt{\frac{2k_B T}{\pi m_i^*}} + L} e^{-\frac{E_{ci} - E_{c0}}{k_B T}}$$

$$(4)$$

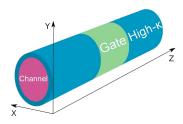

Fig. 2. Schematic of the SiNW FETs used as benchmark devices.

which allows for a regime between diffusive and ballistic transport.

5) The unidirectional thermal velocity [35] is calculated as

$$v_{\text{th},+x,1-D} = \sqrt{\frac{2k_B T}{\pi \, m_{\text{DD},t,1-D}^*}}.$$

(5)

6)  $\langle \langle \lambda \rangle \rangle$  is then obtained from the relation

$$\langle \langle \lambda \rangle \rangle = \pi \, \tau \, v_{\text{th}, +x, 1-D}. \tag{6}$$

7) The apparent mobility,  $\mu_{app}$ , combines the diffusive and ballistic mobilities [35] as

$$\mu_{\rm app} = \frac{\langle \langle \lambda \rangle \rangle L}{\langle \langle \lambda \rangle \rangle + L} \frac{v_{\rm th, +x, 1-D}}{2 k_B T/q}.$$

(7)

8) The critical length [36],  $L_{\text{crit}}$ , in the saturation regime is given by

$$L_{\text{crit,sat}} = \xi L = 6.029 \times 10^{-2} L$$

(8)

where the prefactor is obtained by fitting the data in [36, Fig. 8(a)]. This prefactor shows a very little dependence on the SiNW diameter or the type of carrier.

9) The transmission coefficient in the saturation regime is

$$T_{\text{sat}} = \frac{\langle \langle \lambda \rangle \rangle}{\langle \langle \lambda \rangle \rangle + L_{\text{crit, sat}}}.$$

(9)

10) The saturation velocity is finally computed as [36]

$$v_{\text{sat}} = v_{\text{th},+x,1-D} \frac{T_{\text{sat}}}{2 - T_{\text{sat}}}.$$

(10)

# III. CHARACTERISTICS OF THE NANOWIRE TRANSISTORS

#### A. Benchmark Devices

The theoretical models and numerical methods included in VENDES are initially validated against experimental  $I_D$ – $V_G$  characteristics for a 15-nm gate length SiNW FET that has an elliptical cross section of  $7.15 \times 8.99 \text{ nm}^2$  [19]. A scheme of the device structure is illustrated in Fig. 2, with the dimensions and doping profiles summarized in Table I. The 15-nm gate FET doping profile is extracted by a reverse-engineering process by simulating the device characteristics in the subthreshold [23]. The SiNW FETs are assumed to have a uniformly p-type doped channel and a Gaussian n-type doping in the S/D regions. The doping profile including a maximum doping and a lateral straggle of the Gaussian S/D doping is adjusted until the subthreshold slope of the simulated  $I_D$ – $V_G$

TABLE I

DEVICE DIMENSIONS AND DOPING PROFILES

| Physical gate length, L <sub>G</sub> [nm]                                            | 15.0  | 12.5 | 10.6 |

|--------------------------------------------------------------------------------------|-------|------|------|

| Physical source/drain length, L <sub>S/D</sub> [nm]                                  | 80    | 67   | 57   |

| Channel width, W <sub>CH</sub> [nm]                                                  | 7.15  | 6.20 | 5.06 |

| Channel height, H <sub>CH</sub> [nm]                                                 | 8.99  | 7.80 | 6.36 |

| Effective oxide thickness, EOT [nm]                                                  | 1.2   | 1.0  | 0.85 |

| Channel uniform p-type doping, N <sub>CH</sub> [×10 <sup>15</sup> cm <sup>-3</sup> ] | 1.0   | 1.0  | 1.0  |

| S/D Gaussian n-type doping, $N_{S/D}$ [×10 <sup>19</sup> cm <sup>-3</sup> ]          | 7.0   | 8.4  | 9.9  |

| Lateral straggle for S/D doping, σ [nm]                                              | 4.84  | 4.03 | 3.42 |

| Effective perimeter [nm]                                                             | 25.44 | 22.0 | 18.0 |

characteristics for the 15-nm gate length device matched that of the experimental data. The dimensions of the 12.5- and 10.6-nm gate length SiNW FETs and S/D doping profile parameters are scaled down according to [18] following the same methodology as in [23].

#### B. DD and MC Parameters for the Benchmark Devices

The application of the procedure in Section II-D to extract the relevant DD simulation parameters for the benchmark devices produces the DD DOS electron effective mass, electron saturation velocity, apparent electron mobility, perpendicular critical electric field, and the critical length in saturation collected in Table II. VENDES uses the Caughey–Thomas doping and temperature-dependent low-field carrier mobility model [37] that defines the low-field electron mobility,  $\mu_{\rm low}$ , as

$$\mu_{\text{low}} = \mu_{\text{min}} + \frac{\mu_{\text{max}} - \mu_{\text{min}}}{1 + \left(\frac{N_D + N_A}{N^{\text{ref}}}\right)^{\alpha}}$$

(11)

where  $N_D$  and  $N_A$  are the donor and the acceptor doping concentrations.  $\mu_{\rm min}$  and  $\mu_{\rm max}$  indicate the mobility for high or low doped materials, respectively. In our simulations, for a temperature of 300 K, we take  $\mu_{\rm diff}$  from [36], and we consider that  $\mu_{\rm min} = \mu_{\rm app}$  (see values in Table II) and  $\mu_{\rm max} = 1429$  [cm²/Vs].  $N^{\rm ref}$  (1.07 × 10<sup>17</sup>cm<sup>-3</sup>) and  $\alpha$  (0.76) are fitting parameters [38]. To describe the carrier transport between low-field and high-field transport conditions, the electron mobility dependence on the electric field (E) [37], [39] is included as

$$\mu(E) = \frac{\mu_{\text{low}}}{\left[1 + \left(\frac{\mu_{\text{low}}E_{\parallel}}{v_{\text{sat}}}\right)^{\beta}\right]^{1/\beta} \left[1 + \left(\frac{E_{\perp}}{E_{c}}\right)\right]^{1/2}}$$

(12)

being  $E_{\parallel}$  and  $E_{\perp}$  the parallel and perpendicular electric fields, respectively,  $\beta$  a fitting parameter equal to 2 and,  $E_c$  the perpendicular critical electric field (see Table II).

The results from the TB calculations inform the MC simulator and the SCH equation solver of energy gaps and electron effective masses (see Table III). Since the VENDES explicitly treats three bands, the following assumptions are made to incorporate many TB bands into VENDES. The 15- and 12.5-nm gate length NW FETs have many bands originating from the  $\Gamma$  point which fall inside the energy window relevant for the electron transport [see Fig. 1(a)]. Since a large density of subbands indicates energy spectrum close to the bulk, the longitudinal effective masses in the transport direction are set to the bulk values ( $\Delta_1$  in Table III), and the effects of

TABLE II

PARAMETERS USED IN THE DD SIMULATIONS

| L <sub>G</sub> [nm]                                                  | 15.0  | 12.5  | 10.6  |

|----------------------------------------------------------------------|-------|-------|-------|

| Band-gap energy, E <sub>G</sub> [eV]                                 | 1.190 | 1.208 | 1.243 |

| DD DOS $e^-$ effective mass, $m_{DD,DOS,3D}^*$ [m <sub>0</sub> ]     | 1.259 | 1.338 | 1.483 |

| $e^-$ saturation velocity, $v_{\rm sat}$ [×10 <sup>6</sup> cm/s]     | 7.96  | 8.18  | 3.75  |

| Apparent $e^-$ mobility, $\mu_{\rm app}$ [cm <sup>2</sup> /Vs]       | 114   | 103   | 46    |

| Perpendicular critical electric field, $E_c$ [×10 <sup>5</sup> V/cm] | 9.95  | 9.95  | 9.95  |

| Critical length in saturation, $L_{\rm crit,sat}$ [nm]               | 0.904 | 0.754 | 0.639 |

level quantization are accounted for by using a 3-D DOS effective mass with a value reduced with respect to bulk, calculated from the individual band curvatures and including the occupation probability, given by (1) and (2). On the other hand, the two lowest bands with minima close to the Brillouin zone edge Z are treated explicitly ( $\Delta_2$  and  $\Delta_3$ ), with the 3-D DOS effective mass considering a possible near-degeneracy. To prevent the electron movement in the transverse-to-transport direction, both transverse  $(m_t)$  effective masses are set to a value of  $1.9m_0$  for all three valleys. This large transverse mass will: 1) prevent the electron motion along the transverse directions due to quantum confinement and 2) assure that the occupation in phase space does not artificially alter the scattering rate. Note that, the chosen  $1.9m_0$  reproduces the experimental drain current for the 15-nm gate length device. Indeed, the drain current is sensitive to  $m_t$ , observing a 22/38% reduction/increase in the ON-current when  $m_t$  is increased/reduced by 26%.

The 10.6-nm gate length device is qualitatively different. The quantization of the energy levels at the  $\Gamma$  point is so strong that only a few bands are within the energy window available to electron transport [see Fig. 1(b)]. In this case, we treat the two bottom bands at  $\Gamma$  ( $\Delta_1$  and  $\Delta_2$ ) and the bottom band close to Z explicitly ( $\Delta_3$ ) using longitudinal effective masses obtained from the band curvatures, and the DOS masses reflecting a possible near-degeneracy. The transverse effective masses for the 10.6-nm gate length device are also set to a value of 1.9 $m_0$  as in the larger cross section devices.

# IV. SINW FETS I-V CHARACTERISTICS

In this section, we present the  $I_D$ – $V_G$  characteristics obtained using the quantum-corrected MC and DD simulations, compare them against experimental data, and analyze the impact of the TB extracted parameters on the results.

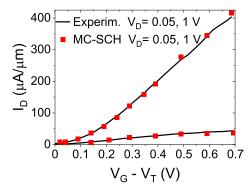

# A. Simulated Versus Experimental Results

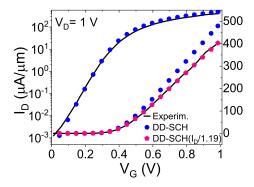

$I_D$ –( $V_G$  –  $V_T$ ) characteristics comparing experimental data against the results from the 3-D SCH equation quantum-corrected MC simulations (MC-SCH) that consider the TB generated parameters presented in Table III are plotted in Fig. 3 for the 15.0-nm gate length SiNW FET. There is an excellent agreement between the experiment and the simulations at both low and high drain biases. The external series resistance has been accounted for by increasing the length of the S/D regions up to 80 nm (see Table I). Fig. 4 shows, on both linear and logarithmic scales, a comparison of the experimental  $I_D$ – $V_G$  characteristics against the 3-D

TABLE III

TB-EXTRACTED MC PARAMETERS FOR A  $\langle 110 \rangle$  Channel Crystallographic Orientation.  $m_l =$  Longitudinal  $e^-$  Effective Mass,  $m_{\text{DOS }3-\text{D}}^* = 3\text{-D DOS }e^-$  Effective Mass,  $E_G =$  Band-Gap Energy

| $L_{\rm G}$ | 15.0 [nm]         |                |       | 12.5 [nm] |                |       | 10.6 [nm] |                |       |

|-------------|-------------------|----------------|-------|-----------|----------------|-------|-----------|----------------|-------|

|             | $m_l$             | $m^*_{DOS,3D}$ | $E_G$ | $m_l$     | $m^*_{DOS,3D}$ | $E_G$ | $m_l$     | $m^*_{DOS,3D}$ | $E_G$ |

| Valley      | [m <sub>0</sub> ] | $[m_0]$        | [eV]  | $[m_0]$   | $[m_0]$        | [eV]  | $[m_0]$   | $[m_0]$        | [eV]  |

| $\Delta_1$  | 0.18              | 0.40           | 1.19  | 0.18      | 0.43           | 1.21  | 0.17      | 0.45           | 1.24  |

| $\Delta_2$  | 0.56              | 0.67           | 1.2   | 0.56      | 0.81           | 1.22  | 0.16      | 0.44           | 1.29  |

| $\Delta_3$  | 0.59              | 1.08           | 1.27  | 0.61      | 1.32           | 1.31  | 0.57      | 1.07           | 1.26  |

Fig. 3.  $I_D$ –( $V_G$ – $V_T$ ) characteristics comparing experimental data against 3-D MC-SCH simulations for the 15.0-nm gate length SiNW FET at both low (0.05 V) and high (1.0 V) drain biases.

Fig. 4.  $I_D$ – $V_G$  characteristics comparing experimental data against 3-D DD-SCH simulations for the 15.0-nm gate length SiNW FET, on both linear and logarithmic scales.  $I_D$  from the DD-SCH corrected by a factor 1.19 is also included (pink pentagons).

SCH equation quantum-corrected DD simulations (DD-SCH) (see blue circles) that incorporate the TB-generated parameters presented in Table II. The DD simulations are able to precisely capture the experimentally observed subthreshold region (note the good match in the subthreshold slope and in the vicinity of the threshold voltage) thanks to the inclusion of SCH equation quantum corrections. However, in the ON-region, the DD simulations predict a 1.19 times larger ON-current than the experimentally seen. This failure to properly capture the nonequilibrium effects happening in the ON-region of the device is a well-known limitation of the DD transport model [40]. However, this difference can be used as a fitting parameter to fully calibrate the I-V curve, as done in Fig. 4 (pink hexagons), if the SCH equation quantumcorrected DD simulations were to be used in an ON-region study.

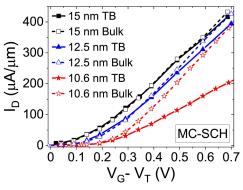

Fig. 5.  $I_D$  versus ( $V_G - V_T$ ) comparing 3-D MC-SCH simulations using either the TB-extracted or the bulk effective parameters at  $V_D$  of 1.0, 0.8, and 0.7 V for 15.0-, 12.5-, and 10.6-nm gate length devices, respectively.

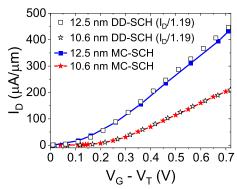

Fig. 6.  $I_D$  versus ( $V_G - V_T$ ) comparing 3-D SCH equation quantum-corrected DD and MC simulations using TB-extracted parameters for the 12.5- and 10.6-nm gate length SiNW FETs.  $I_D$  obtained from DD-SCH has been corrected by a factor of 1.19, the same value as in the 15.0-nm gate length device (see Fig. 4).

# B. Bulk Versus TB Parameters

Fig. 5 presents, for the three studied devices, a comparison of the MC-SCH simulated  $I_D$ –( $V_G$  –  $V_T$ ) characteristics when using either the TB-generated or the bulk parameters. For the bulk Si bandstructure parameters, in a  $\langle 110 \rangle$  channel crystallographic orientation, we consider a longitudinal electron effective mass of  $0.916m_0$ , transverse electron effective masses of  $0.190m_0$ , a 3-D DOS electron effective mass of  $0.553m_0$ , and a band-gap energy of 1.12 eV. As expected, the use of bulk parameters provides an accurate characterization of the I–V curve in the subthreshold region and only a minor overestimation (around 4%) of the current in the ON-region for the device with a 15.0-nm gate length. The SiNW FET scaled to a 12.5-nm gate length has very similar I–V characteristics in the subthreshold region when using TB or bulk parameters.

The current starts to differ only from  $(V_G - V_T) > 0.4 \text{ V}$  with a difference up to 8%. When scaled to the 10.6-nm gate length, the differences in current appears at lower gate biases of  $(V_G - V_T) > 0.25 \text{ V}$  with a 87% overestimation in the ON-current when the bulk parameters are used instead of the TB generated ones.

# C. DD-SCH for Strongly Confined SiNW FETs

The MC simulation results serve as the reference to validate the DD-SCH simulations, since no experimental data are available for the smaller SiNW FETs. The MC simulations were previously verified against experimental data for different architectures: a 25-nm gate length SOI FinFET [24], a 22-nm gate length gate-all-around NW FET [23], and a 12-nm gate length nanosheet FET [6] with an exceptional agreement. Fig. 6 shows  $I_D$  versus  $(V_G - V_T)$  characteristics for the 12.5- and 10.6-nm gate length SiNW FETs comparing results from the DD-SCH and the MC-SCH simulations using the TB-extracted parameters. The DD-SCH simulations overestimate the ON-current when compared to the results from the MC-SCH. When using the TB-generated parameters, this overestimation is by a factor 1.19 (as previously seen in Fig. 4 for the 15-nm gate length device) indicating a systematic error. This overestimation can be mitigated by calibrating simulations of a large gate length device against available experimental data and extracting a correction factor that can be applied for smaller gate length dimensions with no experimental measurements. The introduction of the TB-extracted parameters into the quantum-corrected DD and MC simulations will thus allow us to perform accurate analyses of performance and variability for advanced architectures at an affordable computational cost.

#### V. CONCLUSION

We have presented a multilevel physics-based methodology to simulate semiconductor devices in the nanometer regime, where quantum-mechanical confinement effects play an essential role at equilibrium and in highly nonequilibrium carrier transport. This methodology couples TB calculations (to accurately capture the impact of device cross section on band-structure) with quantum-corrected DD and MC techniques. The bulk Si parameters and band-gap energy values are perfectly adequate to reproduce the experimental  $I_D$ - $V_G$  characteristics for a 7.15  $\times$  8.99 nm<sup>2</sup> cross section SiNW FET. However, for smaller cross section devices of  $6.20 \times 7.80 \text{ nm}^2$  and  $5.06 \times 6.36 \text{ nm}^2$ , the results obtained from the quantum-corrected MC using bulk parameters overestimate the ON-current by 8% and 87%, respectively, when compared to the results obtained from the MC-SCH simulations using the TB-extracted electron effective parameters. In addition, the quantum-corrected DD simulations can still provide accurate results by using a very small number of fitting parameters obtained from our multilevel physics-based methodology to extract them.

#### REFERENCES

D. Bhattacharya and N. K. Jha, "FinFETs: From devices to architectures," Adv. Electron., vol. 2014, p. 21, Sep. 2014, doi: 10.1155/2014/365689.

- [2] G. E. Moore, "Cramming more components onto integrated circuits," IEEE Solid-State Circuits Soc. Newslett., vol. 11, no. 3, pp. 33–35, Ian 2006

- [3] M. T. Bohr and I. A. Young, "CMOS scaling trends and beyond," *IEEE Micro*, vol. 37, no. 6, pp. 20–29, Dec. 2017, doi: 10.1109/MM.2017.4241347.

- [4] O. Badami et al., "Performance comparison for FinFETs, nanowire and stacked nanowires FETs: Focus on the influence of surface roughness and thermal effects," in *IEDM Tech. Dig.*, Dec. 2017, p. 13, doi: 10.1109/IEDM.2017.8268382.

- [5] J.-S. Yoon, T. Rim, J. Kim, M. Meyyappan, C.-K. Baek, and Y.-H. Jeong, "Vertical gate-all-around junctionless nanowire transistors with asymmetric diameters and underlap lengths," *Appl. Phys. Lett.*, vol. 105, no. 10, Sep. 2014, Art. no. 102105, doi: 10.1063/1.4895030.

- [6] D. Nagy, G. Espineira, G. Indalecio, A. J. Garcia-Loureiro, K. Kalna, and N. Seoane, "Benchmarking of FinFET, nanosheet, and nanowire FET architectures for future technology nodes," *IEEE Access*, vol. 8, pp. 53196–53202, 2020, doi: 10.1109/ACCESS.2020.2980925.

- [7] D. Vasileska, S. M. Goodnick, and G. Klimeck, Computational Electronics: Semiclassical and Quantum Device Modeling and Simulation. Boca Raton, FL, USA: CRC Press, 2010.

- [8] A. J. García-Loureiro et al., "Implementation of the density gradient quantum corrections for 3-D simulations of multigate nanoscaled transistors," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 30, no. 6, pp. 841–851, Jun. 2011, doi: 10.1109/TCAD.2011.2107990.

- [9] J. Lindberg et al., "Quantum corrections based on the 2-D Schrödinger equation for 3-D finite element Monte Carlo simulations of nanoscaled FinFETs," *IEEE Trans. Electron Devices*, vol. 61, no. 2, pp. 423–429, Feb. 2014, doi: 10.1109/TED.2013.2296209.

- [10] M. Luisier, A. Schenk, W. Fichtner, and G. Klimeck, "Atomistic simulation of nanowires in the sp<sup>3</sup>d<sup>5</sup>s\* tight-binding formalism: From boundary conditions to strain calculations," *Phys. Rev. B, Condens. Matter*, vol. 74, Nov. 2006, Art. no. 205323, doi: 10.1103/PhysRevB.74.205323.

- [11] G. Bastard, Wave Mechanics Applied to Semiconductor Heterostucture. Les Ulis, France: Les Edition de Physique, 1988.

- [12] S. Horiguchi, "Validity of effective mass theory for energy levels in Si quantum wires," *Phys. B, Condens. Matter*, vol. 227, nos. 1–4, pp. 336–338, 1996, doi: 10.1016/0921-4526(96)00435-8.

- [13] J. M. Jancu, R. Scholz, F. Beltram, and F. Bassani, "Empirical spds\* tight-binding calculation for cubic semiconductors: General method and material parameters," *Phys. Rev. B, Condens. Matter*, vol. 57, no. 11, pp. 6493–6507, 1998.

- [14] G. Klimeck, R. C. Bowen, T. B. Boykin, C. Salazar-Lazaro, T. A. Cwik, and A. Stoica, "Si tight-binding parameters from genetic algorithm fitting," *Superlattices Microstruct.*, vol. 27, nos. 2–3, pp. 77–88, Feb. 2000, doi: 10.1006/spmi.1999.0797.

- [15] N. Neophytou and H. Kosina, "Atomistic simulations of low-field mobility in Si nanowires: Influence of confinement and orientation," *Phys. Rev. B, Condens. Matter*, vol. 84, no. 8, Aug. 2011, Art. no. 085313, doi: 10.1103/PhysRevB.84.085313.

- [16] Y.-M. Niquet, C. Delerue, D. Rideau, and B. Videau, "Fully atomistic simulations of phonon-limited mobility of electrons and holes in (001)-, (110)-, and (111)-oriented Si nanowires," *IEEE Trans. Electron Devices*, vol. 59, no. 5, pp. 1480–1487, May 2012, doi: 10.1109/TED.2012.2187788.

- [17] J. Kim and M. V. Fischetti, "Empirical pseudopotential calculations of the band structure and ballistic conductance of strained [001], [110], and [111] silicon nanowires," *J. Appl. Phys.*, vol. 110, no. 3, Aug. 2011, Art. no. 033716, doi: 10.1063/1.3615942.

- [18] IEEE. (2020). International Roadmap for Devices and Systems 2020 Edition. [Online]. Available: https://irds.ieee.org/editions/2020

- [19] S. Bangsaruntip *et al.*, "Density scaling with gate-all-around silicon nanowire MOSFETs for the 10 nm node and beyond," in *IEDM Tech. Dig.*, Dec. 2013, p. 20, doi: 10.1109/IEDM.2013.6724667.

- [20] N. Seoane et al., "A multi-method simulation toolbox to study performance and variability of nanowire FETs," *Materials*, vol. 12, no. 15, pp. 2391–2406, 2019, doi: 10.3390/ma12152391.

- [21] G. Carey, A. Pardhanani, and S. Bova, "Advanced numerical methods and software approaches for semiconductor device simulation," *VLSI Des.*, vol. 10, p. 43903, Jan. 2000, doi: 10.1155/2000/43903.

- [22] K. Tomizawa, Numerical Simulation of Submicron Semiconductor Devices (Artech House Materials Science Library). Norwood, MA, USA: Artech House, 1993.

- [23] M. A. Elmessary et al., "Scaling/LER study of Si GAA nanowire FET using 3D finite element Monte Carlo simulations," Solid-State Electron., vol. 128, pp. 17–24, Feb. 2017, doi: 10.1016/j.sse.2016.10.018.

- [24] M. Aldegunde, A. J. García-Loureiro, and K. Kalna, "3D finite element Monte Carlo simulations of multigate nanoscale transistors," *IEEE Trans. Electron Devices*, vol. 60, no. 5, pp. 1561–1567, May 2013, doi: 10.1109/TED.2013.2253465.

- [25] D. Nagy et al., "3-D finite element Monte Carlo simulations of scaled Si SOI FinFET with different cross sections," *IEEE Trans. Nanotechnol.*, vol. 14, no. 1, pp. 93–100, Jan. 2015, doi: 10.1109/TNANO.2014.2367095.

- [26] Y. M. Niquet, D. Rideau, C. Tavernier, H. Jaouen, and X. Blase, "Onsite matrix elements of the tight-binding Hamiltonian of a strained crystal: Application to silicon, germanium, and their alloys," *Phys. Rev. B, Condens. Matter*, vol. 79, Jun. 2009, Art. no. 245201, doi: 10.1103/PhysRevB.79.245201.

- [27] Y. P. Tan, M. Povolotskyi, T. Kubis, T. B. Boykin, and G. Klimeck, "Tight-binding analysis of Si and GaAs ultrathin bodies with subatomic wave-function resolution," *Phys. Rev. B, Condens. Matter*, vol. 92, no. 9, 2015, Art. no. 085301, doi: 10.1103/PhysRevB.92.085301.

- [28] A. Islam, B. Benbakhti, and K. Kalna, "Monte Carlo study of ultimate channel scaling in Si and In<sub>0.3</sub>Ga<sub>0.7</sub>As bulk MOSFETs," *IEEE Trans. Nanotechnol.*, vol. 10, no. 6, pp. 1424–1432, Nov. 2011, doi: 10.1109/TNANO.2011.2165555.

- [29] C. Jacoboni and P. Lugli, The Monte Carlo Method for Semiconductor Device Simulation (Computational Microelectronics). Vienna, Austria: Springer, 2012.

- [30] B. K. Ridley, "Reconciliation of the conwell-weisskopf and brooksherring formulae for charged-impurity scattering in semiconductors: Third-body interference," *J. Phys. C, Solid State Phys.*, vol. 10, no. 10, pp. 1589–1593, May 1977, doi: 10.1088/0022-3719/10/10/003.

- [31] D. K. Ferry, Semiconductor Transport. London, U.K.: CRC Press, 2000.

- [32] A. Islam and K. Kalna, "Monte Carlo simulations of mobility in doped GaAs using self-consistent Fermi–Dirac statistics," *Semicond. Sci. Technol.*, vol. 26, no. 5, Mar. 2011, Art. no. 055007, doi: 10.1088/0268-1242/26/5/055007.

- [33] M. A. Elmessary et al., "Anisotropic quantum corrections for 3-D finiteelement Monte Carlo simulations of nanoscale multigate transistors," *IEEE Trans. Electron Devices*, vol. 63, no. 3, pp. 933–939, Mar. 2016, doi: 10.1109/TED.2016.2519822.

- [34] B. Winstead and U. Ravaioli, "A quantum correction based on Schrödinger equation applied to Monte Carlo device simulation," *IEEE Trans. Electron Devices*, vol. 50, no. 2, pp. 440–446, Feb. 2003, doi: 10.1109/TED.2003.809431.

- [35] M. Lundstrom and C. Jeong, Near-Equilibrium Transport: Fundamentals and Applications, 1st ed. Singapore: World Scientific, 2013.

- [36] A. Majumdar et al., "Room-temperature carrier transport in high-performance short-channel silicon nanowire MOSFETs," in *IEDM Tech. Dig.*, Dec. 2012, p. 3, doi: 10.1109/IEDM.2012.6479003.

- [37] R. E. Thomas, "Carrier mobilities in silicon empirically related to doping and field," *Proc. IEEE*, vol. 55, no. 12, pp. 2192–2193, Dec. 1967, doi: 10.1109/PROC.1967.6123.

- [38] S. Selberherr, "Process and device modeling for VISI," *Microelectron. Rel.*, vol. 25, no. 2, p. 396, 1985, doi: 10.1016/0026-2714(85)90148-9.

- [39] K. Yamaguchi, "Field-dependent mobility model for two-dimensional numerical analysis of MOSFET's," *IEEE Trans. Electron Devices*, vol. 26, no. 7, pp. 1068–1074, Jul. 1979, doi: 10.1109/T-ED.1979.19547.

- [40] A. Asenov, A. R. Brown, J. H. Davies, S. Kaya, and G. Slavcheva, "Simulation of intrinsic parameter fluctuations in decananometer and nanometer-scale MOSFETs," *IEEE Trans. Electron Devices*, vol. 50, no. 9, pp. 1837–1852, Sep. 2003, doi: 10.1109/TED.2003.815862.