#### 5547

# Technology of GaN-Based Large Area CAVETs With Co-Integrated HEMTs

Philipp Döring<sup>®</sup>, Rachid Driad, Richard Reiner<sup>®</sup>, Patrick Waltereit, Stefano Leone<sup>®</sup>, Michael Mikulla, and Oliver Ambacher

Abstract—In this work, multi-finger current aperture vertical electron transistors (CAVETs) are fabricated with co-integrated high electron mobility transistors (HEMTs). The devices are realized by Mg-ion implantation and metalorganic chemical vapor deposition (MOCVD) regrowth. The intrinsic CAVET design is optimized for robust device performance and applied on multi-finger devices having a total gate periphery of  $W_{\rm G} = 13.5$  mm and  $W_{\rm G} = 77$  mm. Mappings of the transfer characteristics revealed reliable turn-off behavior demonstrating the suitability of the intrinsic device layout. The largest CAVETs revealed a total oN-state resistance of  $R_{ON} = 1.67 \Omega$  and a maximum drain current of  $I_{D,MAX} = 20.3$  A at  $V_{GS} = 3$  V. A pulse robustness of  $P_{PULS} = 976$  W at  $V_{DS} = 50$  V and a pulsewidth of 500  $\mu$ s is shown without thermal destruction. Additionally, HEMTs are co-integrated on-chip. This combination of HEMTs and reliable large area CAVETs enables the design of highperformance, monolithically integrated GaN power circuits (GaN power ICs) based on the CAVET technology.

*Index Terms*— Current aperture vertical electron transistor (CAVET), GaN, power electronics, vertical transistor.

# I. INTRODUCTION

G aN-BASED devices offer great potential for high power switching applications due to their superior physical properties, compared to Si and SiC [1], [2]. The most investigated AlGaN/GaN high electron mobility transistor (HEMT) has already entered the high-power and high-frequency electronics market [3], [4]. However, for high power applications, the lateral technology suffers from high gate-to-drain spacing to sustain high voltage operation. In contrast, vertical

Manuscript received May 3, 2021; revised June 22, 2021 and August 18, 2021; accepted August 31, 2021. Date of publication September 9, 2021; date of current version October 22, 2021. This work was supported in part by the Deutsche Forschungsgemeinschaft (DFG) under Grant AM 105/47-1 and in part by Fraunhofer Society under VERTIGO Grant. The review of this article was arranged by Editor S. Chowdhury. (*Corresponding author: Philipp Döring.*)

Philipp Döring is with the Department of Power Electronics, Albert-Ludwigs-Universität Freiburg, 79108 Freiburg im Breisgau, Germany (e-mail: philipp.doering@inatech.uni-freiburg.de).

Rachid Driad, Richard Reiner, Patrick Waltereit, Stefano Leone, and Michael Mikulla are with Fraunhofer Institute for Applied Solid State Physics (Fraunhofer IAF), 79108 Freiburg im Breisgau, Germany.

Oliver Ambacher is with the Department of Power Electronics, Albert-Ludwigs-Universität Freiburg, 79108 Freiburg im Breisgau, Germany, and also with Fraunhofer Institute for Applied Solid State Physics (Fraunhofer IAF), 79108 Freiburg im Breisgau, Germany.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2021.3109840.

Digital Object Identifier 10.1109/TED.2021.3109840

devices offer better area efficiency in the high voltage region, as the drift region can be scaled independently of the chip area. In contrast to other reported vertical GaN transistor designs [5]–[9], the current aperture vertical electron transistor (CAVET) combines the advantage of the vertical depletionand drift-region with the proven gate-source module of the lateral HEMT. This combination opens the possibility for monolithic integration of gate drivers as well as protection and sensor systems [10] of the low-voltage HEMT-technology and simultaneously avoids the requirement of an intricate field-plate design since the high electric field is moved into the bulk material. In addition, the current blocking layer (CBL), which serves as a potential barrier between the source and drain in CAVET technology, can be used to shield the low-voltage logic of the HEMT-technology from the high drain/substrate potential of the vertical transistor, when connected to the source contact. Even though CAVETs were demonstrated by various fabrication strategies, the intrinsic device design, the challenges in the fabrication process, and their impact on the performance of the fabricated devices are rarely explored [11]-[20]. The use of Mg-implantation to form the CBL seems to be an advantageous process to allow for the direct implementation of the HEMT surface process technology. In contrast to CAVETs demonstrated by Shibata et al. [11] or Nie et al. [12], trench etching in the active area can be avoided and a planar regrowth can be used to finalize the CAVET structure, as the Mg-implantation process leaves the surface morphology unaffected. Promising results of CAVETs were presented [17] with Mg-implanted CBL's fabricated by molecular beam epitaxy (MBE) regrowth to prevent Mg-diffusion from the CBL, which compensates the 2-D electron gas (2DEG) at the AlGaN/GaN interface [14]. However, these demonstrated devices were limited to the mA-range and large periphery devices could not be demonstrated. We have recently presented the first results on large area CAVETs completely grown by metalorganic chemical vapor deposition (MOCVD) [21], which circumvents the need for an industrially unsuitable and expensive MBE regrowth step [17]. In this work, recent progress on the technology of large area CAVETs is presented with lateral HEMTs co-integrated on-chip fabricated by Mg-implantation and MOCVD regrowth under standard growth conditions. An analysis of the intrinsic CAVET design and its impact on the ON-state and transfer characteristics of the fabricated devices is given. An optimized

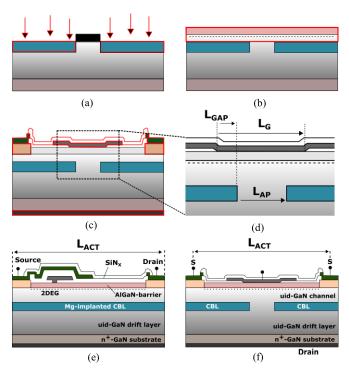

Fig. 1. Schematic overview of the CAVET fabrication process and the final device layout. (a) CBL-formation by Mg-ion implantation. (b) MOCVD AlGaN/GaN regrowth. (c) Metallization and passivation. (d) Definition of intrinsic design parameters. (e) On-chip HEMTs with CBL in vicinity to the AlGaN-barrier. (f) CAVET schematic.

device layout is derived and applied on large area multi-finger CAVETs with a chip size of  $1 \times 1 \text{ mm}^2$  and  $2 \times 2 \text{ mm}^2$ , and their ON-state, transfer, OFF-state characteristics are analyzed as well as their pulse power stability. Vertical and lateral transistors are realized on-chip to compare the vertical device performance directly as a function of the total gate width and to demonstrate the possibility of a direct integration of the AlGaN/GaN-HEMT. The combination of CAVETs and on-chip integrated HEMTs enables the introduction of several new design opportunities in the AlGaN/GaN-technology for high-functional, monolithic integrated GaN power ICs.

### **II. EXPERIMENTAL SECTION**

The fabrication of the devices started with the growth of a 2  $\mu$ m n<sup>-</sup>-GaN layer by MOCVD on 2-in bulk n<sup>+</sup>-GaN substrates. The HVPE grown substrate has a resistivity of  $ho~<~0.5~\Omega\cdot {

m cm}$  and a dislocation density of DD <~5~ imes10<sup>6</sup> cm<sup>-2</sup>. The CBL was formed by Mg-ion implantation [Fig. 1(a)] with an energy of 100 keV and a dose of 2  $\times$  $10^{14}$  cm<sup>-2</sup>, which gives a peak Mg-concentration of 1  $\times$  $10^{19}$  cm<sup>-3</sup>. This Mg-concentration allows for the regrowth of the following epitaxial layers under standard MOCVD growth conditions [22]. The aperture region was protected by a  $\sim$ 3- $\mu$ m-thick photoresist during implantation. After the photoresist was removed, the CAVET was finalized by MOCVD regrowth of a 250 nm uid-GaN channel, a 24 nm Al<sub>0.24</sub>Ga<sub>0.76</sub>N barrier, and a 4 nm GaN-cap layer [Fig. 1(b)]. The regrowth surface temperature of about 1050 °C also served as in situ annealing for the Mg-implanted CBL without the requirement of a capping layer. Atomic force microscopy (AFM)

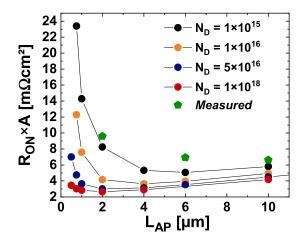

Fig. 2. TCAD simulations of the area-specific ON-state resistance  $R_{\rm ON} \times A$  versus the aperture length  $L_{\rm AP}$  in dependence of the donor concentration in the aperture region. A free donor concentration of  $N_{\rm D} = 2 \times 10^{16}$  cm<sup>-3</sup> is assumed in the drift region. Measured data of three single transistors ( $W_{\rm G} = 100 \ \mu$ m) are given in green.

revealed a root mean square of rms = 0.19 nm (10  $\times$ 10  $\mu$ m<sup>2</sup> scan). The device processing [Fig. 1(c)] is based on standard III-V technology [3]. Alignment markers were etched and protected by SiO<sub>X</sub> prior to regrowth to orientate the surface processing with respect to the aperture region. A Ti/Al/Ni/Au metal stack is deposited and alloyed at around 825 °C in N2 ambient to form the ohmic contacts. Afterward, the devices are passivated with a  $Si_XN_Y$  dielectric deposited by plasma-enhanced chemical vapor deposition (PECVD) and then isolated by Ar-implantation. Afterward, the passivation layers are opened by inductively coupled plasma etching (ICP-RIE) and Ni-Au-based Schottky gate contacts are deposited. The surface process is finalized by an additional Si<sub>X</sub>N<sub>Y</sub> passivation layer and a TiPtAu-based interconnection metallization. The drain contact in the vertical devices is realized on the backside of the GaN substrate by the previously mentioned alloyed ohmic and interconnection metallization.

### **III. RESULTS AND DISCUSSION**

The initial testing of the fabricated CAVETs comprises the characterization of standard Hall- and transfer length method (TLM)-structures. Hall measurements on isolated areas reveal sheet carrier density of  $n_{\rm S} = 8.7 \times 10^{12} {\rm cm}^{-2}$ , electron mobility of  $\mu = 1320 \text{ cm}^2/\text{V} \cdot \text{s}$ , and sheet resistance of  $R_{\text{S}} =$ 538  $\Omega/\Box$ . Contact resistance mapping by TLM reveals an  $R_{\rm C} = 0.3 - 0.35 \ \Omega \cdot \rm mm$  over the complete wafer, which is slightly above literature values [20]. One of the critical design parameters of the CAVET is the aperture length  $L_{AP}$ [Fig. 1(d)] [15], [21], [22]. To avoid current choking, the aperture resistivity should be low, which can be achieved either by intentional n-type doping of the aperture region or by increasing the aperture length. In order to investigate the impact of the aperture resistivity on the total area-specific ON-state resistance  $R_{ON} \times A$ , TCAD simulations are carried out using a self-consistent Poisson-solver (Silvaco Atlas) (Fig. 2). It is visible, that for small  $L_{AP}$ , the  $R_{ON} \times A$  is significantly increasing because of the dominating  $R_{AP}$ , particularly for low donor concentrations in the aperture. However, the impact

of  $R_{AP}$  successively vanishes with increasing  $L_{AP}$ , almost independent of the free donor concentration in the aperture. Furthermore, the lowest minimum  $R_{ON} \times A$  is shifting to higher  $L_{AP}$  with decreasing  $N_D$ . Thus, even though low  $R_{ON} \times A$  is achievable with small  $L_{AP}$ , higher aperture length (>4  $\mu$ m) still seems beneficial when addressing high voltage stability due to the higher critical fields at low donor concentrations. However, for high aperture length (>10  $\mu$ m), the lateral spreading of the transistor increases the total  $R_{ON} \times A$  which makes very large apertures unsuitable. Small gate width transistors ( $W_G = 100 \ \mu$ m) are fabricated on-chip to measure  $R_{ON} \times A$  empirically. The length of the active area  $L_{ACT}$  is defined between the centers of the two source contacts of each transistor (gate–source distance of  $L_{GS} = 4 \ \mu$ m and length of the ohmic contacts of  $L_{OHM} = 5 \ \mu$ m).

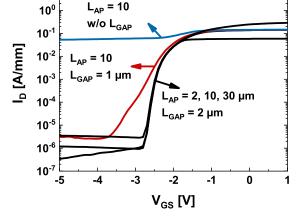

The measured data reveal higher resistances as expected from the TCAD simulations. It is assumed that the effective donor concentration in the aperture and drift layer is lower due to slight carrier compensation by carbon, which causes a slightly higher resistance. Carbon is a deep acceptor that may be introduced by auto-doping during the epitaxial growth, because of the carbon atoms present in the MOCVD precursors. Another potential contributor could be related to surface contamination during the aperture definition process. Nevertheless, the measured  $R_{\rm ON} \times A$  for CAVETs with an aperture length of  $L_{AP} = 10 \ \mu m$  is close to the expected values as the active device area becomes larger and the impact of the low carrier concentration is decreasing. A second critical parameter in the design of the CAVETs is the gate aperture overlap  $L_{\text{GAP}}$  [13], [17] shown in Fig. 1(d). The gate aperture overlap can be defined as the difference between the length of the gate  $L_{\rm G}$  and the aperture length  $L_{\rm AP}$ .  $L_{\rm GAP}$  determines the gate control by suppressing source-drain leakage through the GaN-channel below the gate. The required overlap needs to be adjusted with respect to the channel thickness between the CBL and source contact in the fabricated device structure. To determine the required dimension of the gate-aperture overlap, small gate width CAVETs were fabricated with  $L_{GAP}$ ranging between 0 and 2  $\mu$ m and a gate width of  $W_{\rm G}$  = 100  $\mu$ m. The corresponding transfer characteristics at  $V_{\rm DS}$  = 10 V and varying  $V_{GS} = -5$  to 1 V are shown in Fig. 3. The device with an aperture length of  $L_{AP} = 10 \ \mu m$  and  $L_{GAP} =$ 2  $\mu$ m presented a threshold voltage of  $V_{\rm TH} = -2.82$  V. Similar  $V_{\rm TH}$  is obtained for on-chip lateral HEMTs test structures. The device with an aperture length of  $L_{AP} = 10 \ \mu m$  and  $L_{GAP} =$ 2  $\mu$ m presented a threshold voltage of  $V_{\rm TH} = -2.82$  V. Similar  $V_{\rm TH}$  is obtained for on-chip lateral HEMTs test structures. Thus, the turn-off behavior is determined by the depletion of the 2DEG and unmodulated electrons in the GaN-channel seem to play a minor role in the OFF-state at  $V_{\rm DS} = 10$  V.

Besides, a sub-threshold slope of  $S_{\text{S-TH}} = 87.6 \text{ mV/decade}$ and an  $I_{\text{ON}}/I_{\text{OFF}}$  ratio of  $1.18 \times 10^5$  are derived from the transfer characteristics. A significant change is not observable for CAVETs with the same gate aperture overlap but different aperture lengths between 2 and 30  $\mu$ m. Thus, the ratio of the gate aperture overlap and the aperture was found to be not relevant. However, when decreasing the gate-aperture overlap to 1  $\mu$ m, a significant reduction of the gate control

10<sup>1</sup>

Fig. 3. Transfer characteristics at  $V_{\rm DS} = 10$  V of small gate width CAVETs ( $W_{\rm G} = 100 \,\mu$ m) with a gate aperture overlap of  $L_{\rm GAP} = 2 \,\mu$ m and varying aperture length (black). In addition, the gate aperture overlap of CAVETs with  $L_{\rm AP} = 10 \,\mu$ m is reduced to  $L_{\rm GAP} = 1 \,\mu$ m (red) and  $L_{\rm GAP} = 0 \,\mu$ m (blue), showing increasing loss of the gate control.

is visible, as the sub-threshold swing increases drastically to  $S_{\text{S-TH}} = 404.1 \text{ mV/decade}$  and the threshold voltage shifts to  $V_{\text{TH}} = -3.79 \text{ V}.$

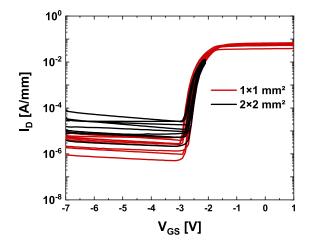

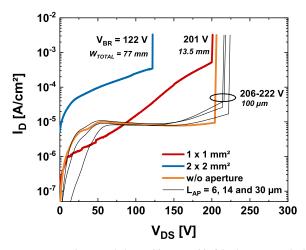

Devices without any  $L_{GAP}$  did not reveal any turn-off behavior and the gate control is completely lost. To investigate the suitability of the intrinsic device layout on the large area cell topology, two different dimensioned comb structures are fabricated with a chip size of  $1 \times 1 \text{ mm}^2$  and  $2 \times 2 \text{ mm}^2$ . The two different multi-finger transistors feature an aperture length of  $L_{AP} = 10 \ \mu m$ , a gate-finger length of  $L_G = 14 \ \mu m$ , and a gate-aperture overlap of  $L_{\text{GAP}} = 2 \ \mu \text{m}$ . The  $1 \times 1 \ \text{mm}^2$ -chip device has a total gate width of  $W_{\text{TOTAL}} = 26 \times 0.53 \text{ mm} =$ 13.78 mm (number of fingers  $\times$  finger width =  $N \times W_{\rm G}$ ) and an active finger area of  $A_{ACT} = 0.53 \text{ mm} \times 0.85 \text{ mm}$  $(W_{\rm G} \times L_{\rm ACT})$ . The 2  $\times$  2 mm<sup>2</sup>-chip device features a total gate periphery of  $W_{\text{TOTAL}} = 58 \times 1.32 \text{ mm} = 77 \text{ mm}$  and an active finger area of  $A_{ACT} = 1.32 \text{ mm} \times 1.85 \text{ mm}$ . Both comb structures are realized on the same chip with the previously shown small transistors ( $W_{\rm G} = 100 \ \mu {\rm m}$ ) to allow a direct comparison. Transfer characteristics of both large-area devices are mapped over the complete wafer (Fig. 4). A threshold voltage shift due to Mg-diffusion, observed for MOCVD-regrown CAVETs [14], is not observable, demonstrating the suitability of our MOCVD-based regrowth process even for much larger devices. In order to analyze the OFF-state behavior of the large area CAVETs, IV-characteristics at  $V_{GS} = -5$  V are measured until device breakdown (Fig. 5). The small gate width transistors reveal OFF-state drain currents in the range of  $I_{D,OFF} = 8 \times 10^{-6} \text{ A/cm}^2$  below  $V_{DS} = 200 \text{ V}$ . Breakdown is measured in the range of  $V_{\rm BR} = 206 - 222$  V (at room temperature) independent of the aperture length and also for the transistor without an aperture. Thus, it is assumed that breakdown is caused by electrons punch through the CBL.

Further improvement is expected by connecting the CBL with the source contact. In this case, the formation of a body diode improves reverse leakage behavior and self-biasing can be avoided by keeping the CBL at the source potential. The breakdown voltage of the  $1 \times 1 \text{ mm}^2$  device is found within

Fig. 4. Mapping of the transfer characteristics at  $V_{\text{DS}} = 10$  V of large area CAVETs. The devices feature an aperture length of  $L_{\text{AP}} = 2 \ \mu \text{m}$ , a gate aperture overlap of  $L_{\text{GAP}} = 2 \ \mu \text{m}$ . Transfer curves are shown for 1  $\times$  1 mm<sup>2</sup>-chip devices (red) and 2  $\times$  2 mm<sup>2</sup>-chip devices (black) having a total gate width of  $W_{\text{TOTAL}} = 13.5$  mm and  $W_{\text{TOTAL}} = 77$  mm, respectively. The current compliance was set to 1 A.

Fig. 5. OFF-state characteristics at  $V_{GS} = -5$  V of the large area devices with a chip size of 1 × 1 mm<sup>2</sup> (red), 2 × 2 mm<sup>2</sup> (blue). Small gate width CAVETs on the same chip with different aperture lengths are given in black. In addition, a CAVET without an aperture was measured (orange) to force the current through the CBL.

the same range at  $V_{\rm BR} = 201$  V. However, the drain leakage current is significantly increased, especially in the range of  $V_{\rm DS} > 100$  V. It is assumed that the higher leakage currents are the cause of a lower yield in the upscaled device but further data are needed to verify this assumption. A further increase in the drain leakage current of about two orders of magnitude is observable in the 2 × 2 mm<sup>2</sup> device, and the breakdown voltage is reduced to  $V_{\rm BR} = 122$  V, which is in agreement with the assumption of the loss in yield by further upscaling of the device area. Another reason for the higher leakage and reduced breakdown voltage could also result from dislocations/defects originating from the GaN-substrate.

The measured breakdown voltage of the 2  $\times$  2 mm<sup>2</sup> device corresponds to a critical field strength of  $E_{CRIT}$  = 1.4 MV/cm assuming depletion over the complete drift layer distance (according to [2]). It is also worth noting that the calculated field strength is still close to published values

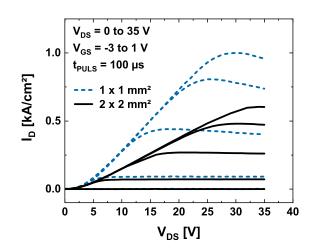

Fig. 6. Pulsed output characteristics of the multi-finger CAVETs with a chip size of 1  $\times$  1 (blue) and 2  $\times$  2 mm<sup>2</sup> (black). A pulsewidth of 100  $\mu s$  and a sample time after 50  $\mu s$  are used, with a duty cycle below 1%.

of small gate width CAVETs in [17] (1.72 MV/cm,  $W_G = 75 \ \mu$ m). The critical field strength of the 1 × 1 mm<sup>2</sup> ( $E_{CRIT} = 2.3 \text{ MV/cm}$ ) is even exceeding these values, which demonstrates the suitability of the present *in situ* annealing/regrowth process for large multi-finger CAVETs as reported in this work. However, a higher breakdown voltage can be expected by increasing the drift layer thickness, as demonstrated in other vertical GaN-designs [5]–[9], [11], [12], in view to increase the area-efficiency with respect to lateral GaN-based power transistors.

To demonstrate the behavior of the devices in terms of current handling capability and pulse power stability, pulsed output characteristics of the fabricated multi-finger CAVETs are measured (Fig. 6). A pulsewidth of 100  $\mu$ s and a sample time of 50  $\mu$ s is used with a duty cycle far below 1%. The CAVET with a chip size of  $1 \times 1 \text{ mm}^2$  revealed a maximum absolute drain current of  $I_{D,MAX} = 4.97$  A (normalized to the active area  $I_{D,MAX} = 1.08 \text{ kA/cm}^2$  and a total differential ON-state resistance of  $R_{\rm ON} = 3.56 \ \Omega \ (R_{\rm ON} \times A) =$ 16.2 m $\Omega$ /cm<sup>2</sup>) at V<sub>GS</sub> = 1 V. The knee-voltage is found at  $V_{\rm K} = 25$  V, which corresponds with a pulse power of  $P_{\text{PULS}} = 121 \text{ W}$  or a pulse power density of 26.86 kW/cm<sup>2</sup>. The larger multi-finger CAVET with a chip-size of  $2 \times 2 \text{ mm}^2$ revealed a maximum absolute drain current of  $I_{D,MAX}$  = 14.76 A and a total differential ON-state resistance of  $R_{\rm ON} =$ 1.81  $\Omega$  ( $R_{\rm ON} \times A = 40.9 \text{ m}\Omega/\text{cm}^2$ ) at  $V_{\rm GS} = 1$  V. The maximum drain current normalized to the active device area is reduced to  $I_{D,MAX} = 0.61 \text{ kA/cm}^2$ , when compared to the smaller multi-finger CAVET. The knee voltage is found at  $V_{\rm K} = 34$  V, corresponding to a total pulse power of  $P_{\rm PULS} =$ 501.8 W (20.4 kW/cm<sup>2</sup>). As Hall- and TLM-measurements revealed typical values, the high ON-state resistance and the high knee voltage  $V_{\rm K}$  in the fabricated devices are assumed to be the result of reduced effective carrier concentration in the nominally undoped aperture and drift region as mentioned previously. Additional testing of the aperture and drift region further indicated this assumption (not shown here).

To compare the pulse power stability with published data for lateral Schottky-gate HEMTs, a specific destruction energy

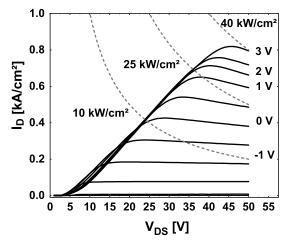

Fig. 7. Pulsed output characteristics of the multi-finger CAVETs with a chip size  $2 \times 2 \text{ mm}^2$ .  $V_{\text{DS}}$  is measured up to 50 V and  $V_{\text{GS}}$  is varied from -5 to 3 V. A pulsewidth of 500  $\mu$ s and a sample time after 50  $\mu$ s are used. A pulse power of  $P_{\text{PULS}} = 968$  W was measured at  $V_{\text{DS}} = 50$  V which is close to the predicted device failure of  $P_{\text{FAIL}} = 976$  W (using  $E_{\text{FAIL}} = 200 \text{ mJ/mm}^2$ ).

of  $E_{\text{FAIL}} = 200 \text{ mJ/mm}^2$  at  $V_{\text{DS}} = 50 \text{ V}$  is assumed, which was experimentally derived by Mocanu *et al.* [24]. Using a pulse power  $P_{\text{PULS}} = 500 \text{ W}$  and an active area of  $A_{\text{ACT}} =$ 2.16 mm<sup>2</sup>, a destruction power of  $P_{\text{FAIL}} = 976 \text{ W}$  is calculated. Pulsed output characteristics of the 2 × 2 mm<sup>2</sup>-chip CAVET are measured for  $V_{\text{DS}} = 0$  to 50 V and  $V_{\text{GS}} = -5$  to 3 V (Fig. 7). The multi-finger CAVET exhibited an absolute drain current of 20.3 A at  $V_{\text{GS}} = 3 \text{ V}$  and a total differential ON-state resistance of  $R_{\text{ON}} = 1.67 \Omega$ . A pulse power of  $P_{\text{PULS}} = 968 \text{ W}$ was measured at  $V_{\text{DS}} = 50 \text{ V}$ , close to the predicted destruction power of a lateral HEMT. Self-heating is visible but device failure in terms of sudden drain current increase or physical breakdown was not observed [24].

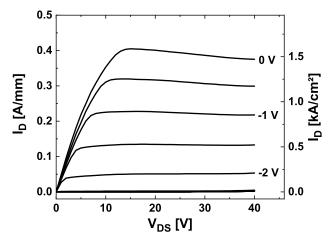

Finally, lateral transistors are processed on-chip, without an aperture below the gate. The fabricated HEMTs have a gate width of  $W_{\rm G} = 50 \ \mu \text{m}$  and an active area length of  $L_{\rm ACT} = 25.5 \ \mu \text{m}$  based on our 600 V HEMT-technology [23] but features the Mg-implanted CBL in the vicinity to the 2DEG [Fig. 1(e)]. Transfer characteristics (not shown here) at  $V_{\rm DS} = 10$  V and  $V_{\rm GS} = -6$  to 0 V revealed a sub-threshold swing of  $S_{\rm S-TH} = 93.4$  mV/decade and a threshold voltage of  $V_{\rm TH} = -2.81$  V. The measured gate leakage current was lower than 1 × 10<sup>-4</sup> A/mm<sup>2</sup>. Output characteristics are measured for  $V_{\rm DS} = 0$  to 40 V in 0.1 V steps (Fig. 8).

The lateral FET reveals a maximum drain current of  $I_{D,MAX} = 0.4$  A/mm or  $I_{D,MAX} = 1.59$  kA/cm<sup>2</sup> at  $V_{GS} = 0$  V and an area-specific ON-state resistance of  $R_{ON} \times A = 2.98$  m $\Omega \cdot \text{cm}^2$ . The resulting output characteristics of the lateral FETs demonstrate the suitability of the used fabrication process. However, in comparison to the vertical FETs, a significantly improved current density and ON-state conductivity can be observed. This is an additional indication that the aperture and drift region conductivity is reduced. The measurements of IV-characteristics of the on-chip integrated lateral transistors reveal the potential of future monolithic integration of the conventional HEMT-technology. On one hand, the CBL serves as a potential barrier to suppress source-drain leakage in the

Fig. 8. Output characteristic of the lateral on-chip HEMT with varying gate–source voltage of  $V_{GS} = -6$  to 0 V for  $V_{DS} = 0$  to 40 V. The device features a gate width of  $W_G = 50 \ \mu m$ , a length of the active area of  $L_{ACT} = 25.5 \ \mu m$  and a GaN-channel thickness of  $t_{CHA} = 250 \ nm$  between the Mg-implanted CBL and the AlGaN barrier.

vertical transistors. On the other hand, this potential barrier is expected to protect the low-voltage HEMT-logic from the high drain potential. However, connecting the CBL to the source contact of the CAVET will be beneficial to avoid any impact of the drain potential on the static and dynamic behavior of the lateral HEMTs.

# **IV. CONCLUSION**

In this article, recent progress in the CAVET technology is presented using low-dose Mg-implantation and MOCVD regrowth. The intrinsic CAVET design was optimized with respect to device performance and gate control. Larger aperture lengths were chosen to avoid current choking for low donor concentration. The fabricated multi-finger CAVETs presented in this work exhibit high absolute current capability and high pulse power stability. Lateral HEMTs were co-integrated onchip, with the 2DEG in the vicinity of the Mg-implanted CBL. This combination of a large area CAVET and an on-chip integrated HEMT demonstrates a pathway to allow monolithically integrated GaN power converters with power switches based on the CAVET technology. Future works will focus on the optimization of the aperture and drift region conductivity, as well as the increase in breakdown voltage to enable higher area efficiency in the vertical design with respect to its lateral counterpart.

# REFERENCES

- A. Q. Huang, "Power semiconductor devices for smart grid and renewable energy systems," *Proc. IEEE*, vol. 105, no. 11, pp. 2019–2047, Nov. 2017, doi: 10.1109/JPROC.2017.2687701.

- [2] B. J. Baliga, "Power semiconductor device figure of merit for high-frequency applications," *IEEE Electron Device Lett.*, vol. 10, no. 10, pp. 455–457, Oct. 1989, doi: 10.1109/55.43098.

- [3] P. Waltereit *et al.*, "GaN-based high voltage transistors for efficient power switching," *Phys. Status Solidi C*, vol. 10, no. 5, pp. 831–834, 2013, doi: 10.1002/pssc.201200563.

- [4] S. Krause, P. Bruckner, M. Dammann, and R. Quay, "High-powerdensity AlGaN/GaN technology for 100-V operation at L-band frequencies," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2019, pp. 1–17.

- [5] Y. Zhang *et al.*, "Large-area 1.2-kV GaN vertical power FinFETs with a record switching figure of merit," *IEEE Electron Device Lett.*, vol. 40, no. 1, pp. 75–78, Jan. 2019, doi: 10.1109/LED.2018. 2880306.

- [6] T. Oka, Y. Ueno, T. Ina, and K. Hasegawa, "Vertical GaN-based trench metal oxide semiconductor field-effect transistors on a free-standing GaN substrate with blocking voltage of 1.6 kV," *Appl. Phys. Exp.*, vol. 7, no. 2, p. 21002, 2014, doi: 10.7567/APEX.7.021002.

- [7] D. Ji *et al.*, "Large-area *in situ* oxide, GaN interlayer-based vertical trench MOSFET (OG-FET)," *IEEE Electron Device Lett.*, vol. 39, no. 5, pp. 711–714, May 2018, doi: 10.1109/LED.2018.2813312.

- [8] M. Sun, Y. Zhang, X. Gao, and T. Palacios, "High-performance GaN vertical fin power transistors on bulk GaN substrates," *IEEE Electron Device Lett.*, vol. 38, no. 4, pp. 509–512, Apr. 2016, doi: 10.1109/LED.2017.2670925.

- [9] T. Oka, T. Ina, Y. Ueno, and J. Nishii, "1.8 mΩ·cm<sup>2</sup> vertical GaN-based trench metal-oxide-semiconductor field-effect transistors on a freestanding GaN substrate for 1.2-kV-class operation," *Appl. Phys. Exp.*, vol. 8, no. 5, p. 54101, 2015, doi: 10.7567/APEX.8.054101.

- [10] S. Moench *et al.*, "Monolithic integrated AlGaN/GaN power converter topologies on high-voltage AlN/GaN superlattice buffer," *Phys. Status Solidi A*, vol. 218, no. 3, p. 2000404, 2021, doi: 10.1002/pssa.202000404.

- [11] D. Shibata *et al.*, "1.7 kV/1.0 mΩ·cm<sup>2</sup> normally-off vertical GaN transistor on GaN substrate with regrown p-GaN/AlGaN/GaN semipolar gate structure," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2016, pp. 10.1.1–10.1.4.

- [12] H. Nie *et al.*, "1.5-kV and 2.2-mΩ-cm<sup>2</sup> vertical GaN transistors on bulk GaN substrates," *IEEE Electron Device Lett.*, vol. 35, no. 9, pp. 939–941, Sep. 2014, doi: 10.1109/LED.2014.2339197.

- [13] I. Ben-Yaacov, Y.-K. Seck, U. K. Mishra, and S. P. DenBaars, "AlGaN/GaN current aperture vertical electron transistor with regrown channels," J. Appl. Phys., vol. 95, no. 4, p. 2073, 2004, doi: 10.1063/1.1641520.

- [14] S. Chowdhury, B. L. Swenson, and U. K. Mishra, "Enhancement and depletion mode AlGaN/GaN CAVET with Mg-ion-implanted GaN as current blocking layer," *IEEE Electron Device Lett.*, vol. 29, no. 6, pp. 543–545, Jun. 2008, doi: 10.1109/LED.2008.922982.

- [15] D. Ji, A. Agarwal, W. Li, S. Keller, and S. Chowdhury, "Demonstration of GaN current aperture vertical electron transistors with aperture region formed by ion implantation," *IEEE Trans. Electron Devices*, vol. 65, no. 2, pp. 483–487, Feb. 2018, doi: 10.1109/TED.2017.2786141.

- [16] R. Yeluri *et al.*, "Design, fabrication, and performance analysis of GaN vertical electron transistors with a buried p/n junction," *Appl. Phys. Lett.*, vol. 106, pp. 183502-1–183502-5, May 2015, doi: 10.1063/1.4919866.

- [17] S. Chowdhury, M. H. Wong, B. L. Swenson, and U. K. Mishra, "CAVET on bulk GaN substrates achieved with MBE-regrown AlGaN/GaN layers to suppress dispersion," *IEEE Electron Device Lett.*, vol. 33, no. 1, pp. 41–43, Jan. 2012, doi: 10.1109/LED.2011.2173456.

- [18] D. Ji, A. Agarwal, H. Li, W. Li, S. Keller, and S. Chowdhury, "880 V/2.7 mΩ·cm<sup>2</sup> MIS gate trench CAVET on bulk GaN substrates," *IEEE Electron Device Lett.*, vol. 39, no. 6, pp. 863–865, Jun. 2018, doi: 10.1109/LED.2018.2828844.

- [19] S. Mandal *et al.*, "Dispersion free 450-V p GaN-gated CAVETs with Mg-ion implanted blocking layer," *IEEE Electron Device Lett.*, vol. 38, no. 7, pp. 933–936, Jul. 2017, doi: 10.1109/LED.2017.2709940.

- [20] S. Rajabi et al., "A demonstration of nitrogen polar gallium nitride current aperture vertical electron transistor," *IEEE Electron Device Lett.*, vol. 40, no. 6, pp. 885–888, Jun. 2019, doi: 10.1109/LED.2019.2914026.

- [21] P. Doering, R. Driad, R. Reiner, P. Waltereit, M. Mikulla, and O. Ambacher, "Metal organic chemical vapour deposition regrown large area GaN-on-GaN current aperture vertical electron transistors with high current capability," *Electron. Lett.*, vol. 57, no. 3, pp. 145–147, Feb. 2021, doi: 10.1049/ell2.12068.

- [22] P. Doering *et al.*, "Growth and fabrication of quasivertical current aperture vertical electron transistor structures," *Phys. Status Solidi A*, vol. 218, no. 3, Feb. 2021, Art. no. 2000379, doi: 10.1002/pssa.202000379.

- [23] P. Waltereit *et al.*, "Impact of GaN cap thickness on optical, electrical, and device properties in AlGaN/GaN high electron mobility transistor structures," *J. Appl. Phys.*, vol. 106, no. 2, p. 23535, 2009, doi: 10.1063/1.3184348.

- [24] M. Mocanu, C. Unger, M. Pfost, P. Waltereit, and R. Reiner, "Thermal stability and failure mechanism of Schottky gate AlGaN/GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 64, no. 3, pp. 848–855, Mar. 2017, doi: 10.1109/TED.2016.2633725.