# All-Electrical Control of Scaled Spin Logic Devices Based on Domain Wall Motion

Eline Raymenants<sup>®</sup>, Student Member, IEEE, Danny Wan, Sebastien Couet<sup>®</sup>, Laurent Souriau, Arame Thiam, Diana Tsvetanova, Yann Canvel, Kévin Garello<sup>®</sup>, Member, IEEE, Gouri S. Kar, Marc Heyns, Inge Asselberghs<sup>®</sup>, Dmitri E. Nikonov<sup>®</sup>, Senior Member, IEEE, lan A. Young<sup>®</sup>, Fellow, IEEE, Stefania Pizzini, Iuliana Radu, Member, IEEE, and Van Dai Nguyen

Abstract—Spin logic devices based on domain wall (DW) motion offer flexible architectures to store and carry logic information in a circuit. In this device concept, information is encoded in the magnetic state of a magnetic track shared by multiple magnetic tunnel junctions (MTJs) and is processed by DW motion. Here, we demonstrate that all-electrical control of such nanoscale DW-based logic devices can be realized using a novel MTJ stack. In addition to field-driven motion, which is isotropic, we show the directional motion of DWs driven by current, a key requirement for logic operation. Full electrical control of an AND logic gate using DW motion is demonstrated. Our devices are fabricated in imec's 300-mm CMOS fab on full wafers, which clears the path for large-scale integration. This proof of concept, thus, offers potential solutions for high-performance and low-power DW-based devices for logic and neuromorphic applications.

Index Terms—Magnetic domain walls (DWs), magnetic logic devices, magnetic memory, spintronics, tunneling magnetoresistance (TMR).

#### I. INTRODUCTION

LTHOUGH magnetic phenomena for logic and memory were studied since the 1970s, they were surpassed by the success of industrial Si-based devices. The discovery of spintronics, due to the capabilities to fabricate magnetic multilayers where the individual thicknesses are on the order of the mean free path of electrons, was a breakthrough

Manuscript received November 17, 2020; revised December 22, 2020; accepted January 20, 2021. Date of publication March 15, 2021; date of current version March 24, 2021. This work was supported by imec's Industrial Affiliation Program. This article is an extended version of a paper presented at IEDM 2020. The review of this article was arranged by Editor D. Triyoso. (Corresponding author: Eline Raymenants.)

Eline Raymenants and Marc Heyns are with IMEC, 3001 Leuven, Belgium, and also with the Department of Materials Engineering, Katholieke Universiteit Leuven, 3001 Leuven, Belgium (e-mail: eline.raymenants@imec.be).

Danny Wan, Sebastien Couet, Laurent Souriau, Arame Thiam, Diana Tsvetanova, Yann Canvel, Gouri S. Kar, Inge Asselberghs, Iuliana Radu, and Van Dai Nguyen are with IMEC, 3001 Leuven, Belgium (e-mail: van.dai.nguyen@imec.be).

Kévin Garello was with IMEC, 3001 Leuven, Belgium. He is now with Spintec, 38000 Grenoble, France.

Dmitri E. Nikonov and Ian A. Young are with Intel Corporation, Hillsboro, OR 97124 USA.

Stefania Pizzini is with the Institut Néel, 38000 Grenoble, France.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2021.3061523.

Digital Object Identifier 10.1109/TED.2021.3061523

for the development of electronic devices. Researchers have proposed using magnetic phenomena for both memory and logic applications ever since [1], [2]. Read heads for hard disk drives based on giant magnetoresistance (GMR) and tunneling magnetoresistance (TMR) were introduced by IBM in 1997 and by Seagate in 2005, respectively [1]. The need for a magnetic field to perform write operations in hard-disk drives was replaced by spin-transfer torque (STT), a capability to electrically change the magnetic state of a nanomagnet. Thus, this effect allows all-electrical operation of spintronic devices at a very low dimension. Spin transfer torque magnetic random access memory (STT-MRAM) technology was developed, and the first commercial devices were made available by Everspin in 2012 [3], [4]. Spin-orbit torque (SOT)-MRAM has recently received a large interest in scientific communities. SOT-based devices offer a significant advantage compared to STT technology. Indeed, the writing current is applied through a separate current path, which avoids the degradation of the tunneling barrier and, thus, improves device reliability [5]. Interestingly, Parkin et al. proposed a magnetic storage device in 2008 based on the transport of magnetic domain walls (DWs) [6]. In this racetrack memory, information is densely packed in magnetic domains in a long magnetic track and is synchronously shifted by the application of an in-plane current (STT/SOT). An important feature of DW-based devices is that bit information can be transported in complex magnetic track geometries that enable logic operation. In 2005, Allwood et al. [7] showed the first demonstration of DW-based logic. Although the devices are not scalable and need a rotating magnetic field to perform logic functionality and a Kerr microscope to read out the magnetic state, they triggered further research in DW-based logic devices. Although not experimentally demonstrated yet, an interesting candidate is the spin-torque majority gate (STMG), proposed by Intel in 2011. The STMG has a simple structure, and it is reconfigurable and potentially allows fan-out and cascading functions [8]. In 2015, Incorvia et al. [9] demonstrated buffer, inverter, and fan-out operations based on DWs.

To foresee the potential application of DW logic devices, benchmarking to evaluate the energy consumption of these emerging devices has been extensively studied [10], [11]. Using a compact model to construct and benchmark a 32-bit adder based on DW devices, Xiao *et al.* [12] demonstrated that, at large-scale design, the devices based on SOT-driven

DW motion offer an improvement in the energy per operation by multiple orders of magnitude compared to their STT counterpart. As a result, this device concept can offer a competitive energy value to a comparable CMOS subprocessor component. Very recently, a promising concept for chiral magnetic DW logic was proposed, and a logic circuit diagram of the full adder was demonstrated by Luo *et al.* [13]. Based on experimental data, they could speculate the energy consumption per operation of an inverter if scaled down to  $10 \times 10 \text{ nm}^2$  is 25.5 aJ, which is comparable to the switching energy of advanced CMOS devices [14]. This study provides key features that make this DW logic device particularly interesting for practical application.

Interestingly, DW devices also hold particular interest for neuromorphic computing applications where DW bit information can be used in both logic and memory devices. The analysis of the energy consumption of such devices showed two orders of magnitude lower energy in comparison to CMOS-based analog circuit [15], [16]. Experimentally, Lequeux et al. proposed and demonstrated magnetic synapses in 2016 [17]. In 2019, Siddiqui et al. [18] showed that DW devices are capable of implementing linear, as well as programmable nonlinear functions. Therefore, these DW-based device concepts pave the way for a future beyond-CMOS devices. However, a single device allowing full-electrical and local control of magnetic domains, i.e., writing, transporting, and reading magnetic domains, to fulfill the requirement of device performance on-chip, has not been reported previously [19].

In this manuscript, we first optimize thin film materials for DW transport. Next, we measure single MTJ pillars to verify switching. Then, we demonstrate etch robustness and current-driven transport in simple hall-bar devices. Finally, we piece all these developments together in fully integrated DW devices on 300-mm wafers and demonstrate that all-electrical control of a DW is achieved. In addition, we prove directional control of DW motion and thus information transfer, which satisfies one of the key requirements for logic device functionality [10]. We overcome one of many hurdles to achieve the full technological realization of magnetic devices that hold great potential for future logic and memory devices.

#### II. RESULTS AND DISCUSSION

# A. Development of Novel MTJ Stack for Spin Logic Devices

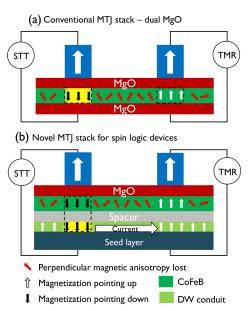

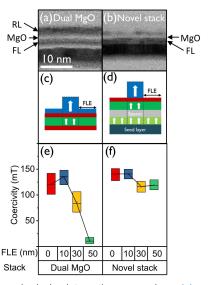

To overcome the challenges of applying the present STT-MRAM stack design [see Fig. 1(a)] for DW device integration (i.e., the magnetic properties of the DW conduit typically collapse during the etching process), we developed DW-based devices using a novel MTJ stack that incorporates the second FL into a conventional MTJ stack for DW transport [see Fig. 1(b)]. Carefully selected high PMA materials for the DW conduit are exploited for reliable DW transport and robustness against process-induced damage. High TMR and efficient STT are maintained by the CoFeB FL in contact with MgO. The role of the spacer is twofold: 1) it decouples the

Fig. 1. (a) Conventional dual MgO stack with etching damage in CoFeB FL track. (b) Novel stack where the second FL, DW conduit, is coupled to the standard CoFeB FL by a nonmagnetic spacer layer. DW conduit is undamaged from etching.

crystallization between CoFeB and the DW conduit and 2) it enables strong ferromagnetic coupling between CoFeB and the DW conduit to behave as a single ferromagnet. At run time, a DW is selectively written into the DW conduit by STT at the input pillar. Subsequently, the DW moves along the track by the magnetic field and/or by electrical control. The arrival of the DW at the output is detected by TMR read. This DW device concept benefits from the energy-efficient write and read processes of current MRAM technology and from fast DW motion in the separate DW conduit layer. Remarkably, this device concept also allows to independently optimize the DW conduit material for transport and reduce sensitivity to process-induced damage.

As described above, a fully integrated DW device requires three key components, i.e., efficient STT write, high TMR read, and efficient DW transport between the input and output. Therefore, in this section, we will address these three important challenges in terms of materials and etching for the integration of DW-based devices. First, we optimize the perpendicular magnetic anisotropy (PMA) of the DW conduit layer for enabling DW transport in a controlled manner. Secondly, we present the integration of the DW conduit layer in the magnetic tunnel junction (MTJ) stack aiming for full-electrical control of the DW conduit's magnetization via MTJs. We study the dependence of the DW conduit layer thickness on TMR reading and STT writing of a single MTJ device with a diameter of 100 nm. This result allows us to find the read/write operating window of our novel MTJ stack for realizing DW devices. Finally, we investigate the etching process window of the novel MTJ stack to ensure that the magnetic properties of the DW conduit layer are fully preserved after the integration process. Accordingly, we use different kinds of samples to evaluate the influence of the pillar patterning process by ion-beam etching (IBE) on DW

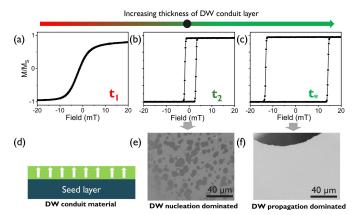

Fig. 2. Optimization of DW conduit thickness. (a)–(c) Hysteresis loops versus field for increasing thickness. (d) DW conduit layer to be optimized. (e) and (f)  $\mu$ MOKE images corresponding to (b) and (c), respectively. Thickness  $t_*$  is selected as target thickness with uniform PMA: high H\_C and DW propagation dominated reversal.

propagation behavior in the conduit layer. For that reason, we will go through several integration steps, including a thin film study by the magneto-optic Kerr effect microscopy ( $\mu$ MOKE) and scaled magnetic tracks where the magnetic state is electrically detected by the extraordinary Hall voltage of Hall bar devices.

1) Thickness Optimization of DW Conduit: Reliable DW motion is the key to device operation. Therefore, the magnetic properties of the DW conduit layer are first optimized, by varying its thickness. Fig. 2 illustrates that the magnetic state evolves from in-plane to out-of-plane with increasing DW conduit thickness. This experimental observation might be related to the interface roughness of the conduit. Indeed, a very thin conduit layer can become discontinuous leading to a reduced interfacial anisotropy [20]-[22]. Moreover, if the thickness is too large, the effective anisotropy becomes negative, and in-plane anisotropy is obtained due to dipolar fields [22]. Importantly,  $\mu$ MOKE images confirm that a higher PMA film can help to suppress random domain nucleation. This study allows us to find the critical thickness of the DW conduit layer that is required to ensure a controllable switching process, dominated by single domain nucleation and DW propagation. The process window is defined by the  $t_*$ thickness region.

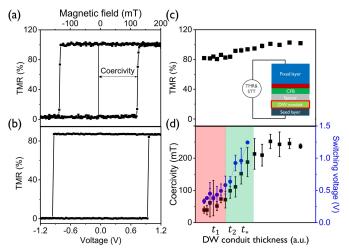

2) Electrical Reading/Writing of the DW Conduit's Magnetization: We now integrate the selected DW conduit material in an MTJ, aiming for electrical manipulation of the conduit's magnetization via MTJs, schematic Fig. 3. We experimentally demonstrate that the fundamental properties of an MTJ are not compromised. Fig. 3(a) and (b) display typical TMR loops of 100-nm-MTJ pillars driven by field and current pulses (50 ns), respectively. TMR values are plotted as a function of conduit thickness in Fig. 3(c). We observe only a slight change in TMR with increasing thickness. This indicates that TMR is primarily attributed to the CoFeB/MgO interface, as expected. The enhancement of magnetic coercivity  $H_C$  [left axis of Fig. 3(d)] and STT switching voltage  $V_{\rm SW}$  (right axis) with increasing conduit thickness is consistent with higher PMA observed in the thicker conduit layers (see Fig. 2).

Fig. 3. (a) and (b) MTJs with novel stack can be switched by magnetic field or by STT (50 ns pulses). (c) TMR as function of DW conduit thickness. (d) Coercivity and switching voltage increase with increasing thickness. Green shaded area is the region of interest. t1 is defined as the thickness region, where the magnetization of the DW conduit is in-plane,  $t_2$  as the region with PMA but random domain nucleation dominated switching, and  $t_*$  as the region with PMA and single domain nucleation and DW propagation dominated switching.

It importantly reveals that the magnetic state in the DW conduit layer can be electrically set and probed using an MTJ. The switching efficiency (defined as  $V_{\rm SW}/H_C$ ) is preserved even with the addition of the DW conduit in the MTJ. This experimental finding demonstrates that the characteristic properties of a standard MTJ device are not compromised by the integration of DW conduit materials. Note that STT switching is not achieved if the DW conduit is too thick  $(t > t^*)$ . This study defines the parameters of the DW conduit layer that can be electrically written/read via MTJs.

3) Impact of Etching on DW Conduit Layer Properties: In functional DW devices, the PMA of the DW conduit layer requires to be fully preserved during device integration. Thus, this is a significant challenge with the conventional MTJ stack based on the MgO/CoFeB free layer as the manufacturing process of DW-based devices includes a particularly damaging IBE step. During this step, pillars are patterned to define the inputs/outputs of the DW device. As a result, to prevent electrical shorting paths between input and output via the magnetic reference layer (RL), the MTJ stack requires to be etched down to the MgO tunneling barrier. However, during IBE, the highly energetic ions can penetrate a few nanometers deep into the material reaching the MgO/CoFeB interface. When this pristine interface is damaged, the interfacial PMA in the DW conduit is lost, which prevents DW propagation between pillars. This results in nonfunctional devices.

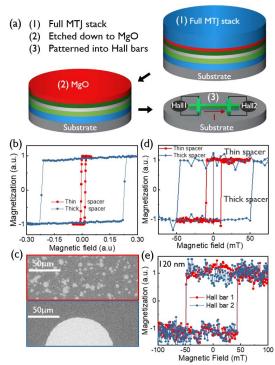

Therefore, we carried out three types of preliminary experiments to optimize the etching process of our novel MTJ stack prior to the fully integrated DW devices. Fig. 4(a) displays the studied samples. The full MTJ stack (step 1) is deposited on a full 300-mm wafer, after which it is etched down to the MgO barrier (step 2) and patterned into a magnetic track with a Hall bar on each side of the track (step 3). We first employ  $\mu$ MOKE measurements to visualize the magnetic domain state during magnetization switching of the etched thin film samples

Fig. 4. (a) MTJ stack deposited on the full wafer, followed by IBE with etch-stop on MgO and, finally, patterning into Hall bars. (b) and (c) Impact of spacer thickness on magnetic properties of DW conduit layer studied by  $\mu$ MOKE on etched blanket samples. Thin spacer shows nucleation-dominated reversal (small coercivity), while thick spacer displays proper DW propagation (large coercivity). (d) Comparison of the Hall bar coercivity for the thin and thick spacers. (e) PMA confirmed in Hall bars down to 120 nm. Overlapping coercivity suggests a magnetically connected track.

at step 2. We compare the effect of etching on our samples with thin and thick spacer materials. When a short etching condition is applied, i.e., etch-stop above the MgO layer, we observe controlled nucleation of a single domain and DW propagation for both spacer thicknesses (not shown). This result indicates that there is no impact of etching on the magnetic properties of the remaining free layer since the IBE has not reached the MgO/CoFeB interface. Therefore, it is certainly required to etch deeper to completely remove the remaining magnetic materials on MgO to avoid any unexpected behavior on the operation of DW devices, such as an electrical short between pillars.

We, now, apply an extreme etch condition, in which the etching process is stopped on the MgO barrier for both samples. In this case, we first observe, in Fig. 4(b), a significant reduction of the coercivity in the thinner spacer sample, meaning that there was a strong influence of the etching process on the magnetic properties of this sample. As a result, the magnetic image of the thinner spacer sample [see Fig. 4(c) (top)] shows that the magnetization switching is dominated by a random nucleation process. This behavior is not desired for the operation of DW-based devices. Interestingly, we obtain the DW-propagation-dominated switching regime for the thick spacer sample [see Fig. 4(c) (bottom)]. This behaves like an optimized stand-alone DW conduit layer as presented above [see Fig. 2(f)]. These results evidence that integration challenges related to etching can be solved by precisely tuning the novel stack.

After this thin film study, it is important to evaluate that the IBE etch-robustness of our novel stack can also be achieved in scaled devices. Therefore, we study the magnetic properties of scaled DW tracks measured electrically using Hall bar devices. For fabrication of these devices [see Fig. 4(a) (step 3)], we first etch the full MTJ stack down to the MgO barrier. Consequently, the devices are patterned and fully integrated on a 300-mm wafer. The width of the DW tracks is ranging from 5  $\mu$ m down to 120 nm, measured by Hall crosses on either end of the track separated by a pitch of 22.5  $\mu$ m. The square hysteresis loop of a 5- $\mu$ m-wide track versus magnetic field [see Fig. 4(d)] indicates PMA in the Hall bar devices. The higher coercivity in the thicker spacer devices confirms that spacer thickness indeed plays an important role in protecting the PMA of the remaining DW conduit layer against the etching process, as demonstrated in the thin film study.

In addition, we observe an almost identical hysteresis loop in both hall bars in the same device for all sizes, exemplified by the 120-nm track in Fig. 4(e). The overlapping switching fields in both hall bars suggest that a single domain nucleated and expanded along the track [23]. This demonstrates the capabilities of our uniform fabrication process, and our etch-robust stack is also validated in scaled devices.

# B. DW Motion in Fully Integrated Magnetic Tracks Using Hall Bar Devices

In this section, we prove that electrical control of DW motion can be achieved in the scaled Hall bar devices. We first study in a 5- $\mu$ m magnetic track that a domain, nucleated in one Hall bar, propagates through the track by both magnetic field and/or current. In this experiment, the device is saturated in the down (up) state by a negative (positive) external z-field. Sequentially, a domain is nucleated in one Hall bar by the application of a large current in the Hall bar transverse to the DW track, a similar approach as previous studies [24]. We confirm domain nucleation by a change in its Hall voltage. The domain then expands through the track driven by an external z-field. The arrival of the DW in the second hall bar is finally confirmed by a change in the Hall voltage at the second Hall bar. Moreover, we confirm in this device that in-plane current along the DW track can also drive the motion of a DW to the second Hall bar over a distance of 20  $\mu$ m. A small external assist field (<15% of coercivity) is still needed to assist DW transport in this experiment (not shown).

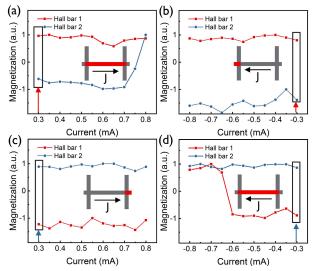

Note that, in low dimensional devices, DW pinning induced by the integration process is expected to play an important role in the dynamics of DW motion [25]. Therefore, we now show that DW motion along the track can also be reliably obtained in a nanoscale Hall bar device. In this experiment, the 200-nm track is saturated in the down-state (magnetization –1). Sequentially a domain is injected in Hall bar 1 (a,b) or Hall bar 2 (c,d). Fig. 5 then displays the magnetization in both hall bars measured as a function of in-plane current. If a positive (negative) current is applied, the DW will propagate from Hall bar 1 (2) to Hall bar 2 (1). Similar to the previous experiment, a small external assist field was applied in the z-direction. This result confirms that DW motion in our

Fig. 5. Current-driven DW motion in the 200-nm wide Hall bar device. If a domain is initially injected at Hall bar 1 (HB1), a DW moves from HB1 to Hall bar 2 (HB2) with positive current (a) and no DW transport is observed with negative current (b). If a domain is initially injected at HB2, no current-driven DW transport is observed from HB2 to HB1 with positive current (c), but DW transport is obtained with negative current (d), as expected. Rectangle and colored arrow highlight the initial state and hall bar from which transport occurs, respectively.

nanoscale Hall bar devices can be directionally controlled by the current polarity as expected. Importantly, this experiment evidences that our stack proposal offers robustness to etching challenges of DW devices while still enabling current-driven DW transport in scaled DW tracks over large distances.

It is worth noting that Hall bar devices are a very important approach to characterize the materials, but their applicability to full device operation is limited. Indeed, Hall bar devices do not offer large read-out signals, nor the possibility to efficiently write DWs. Therefore, MTJs are required as input/outputs, which certainly offers a more energy-efficient scheme to read/write in fully integrated DW devices.

# C. All-Electrical Control of DW-Based Devices With MTJs as Input—Output

1) Verification of Etch-Robustness in Integrated MTJ Pillars With Free Layer Extension Using Novel MTJ Stack: Prior to the demonstration of full device operation, we confirm the etch robustness of our stack in single MTJ pillars with free layer extension (FLE), fabricated on 300-mm wafers. In contrast to conventional STT-MRAM devices, the free layer of these studied devices is larger than the size of the MTJ, and they are considered as a basic building block for DW devices. In Fig. 6, we compare the magnetic properties of a dual MgO stack with the novel stack in MTJ pillars with FLE. As mentioned before, the dual MgO stack requires to etch-stop above the MgO barrier to protect the PMA of the DW conduit layer, suffering from remaining RL material [see Fig. 6(a) and (c)]. The novel stack allows an etch-stop on MgO since the PMA of the DW conduit layer originates from the bottom interface with the seed layer [see Fig. 6(b) and (d)]. Similar TMR values were obtained in both stacks as TMR is only sensitive to the CoFeB/MgO interface. Therefore, the TMR value does

Fig. 6. Large-scale device integration comparison. (a) and (b) TEM of FL track between pillars, (c) and (d) cartoons of devices under test with etching damage to CoFeB layer, (e) coercivity drops in dual MgO, and (f) remains constant in novel stack with increasing FL extension (FLE). Each experimental data point is collected from few tens of devices across 300-mm wafer.

not provide information on the magnetic state of the FLE. However, the coercivity clearly reduces with FLE in dual MgO devices indicating partial damage to the FLE [see Fig. 6(e)], while coercivity is independent of FLE in the novel stack [see Fig. 6(f)]. Therefore, we also prove that the novel stack is more robust against process-induced damage to the DW conduit in integrated devices, a necessity for manufacturability and reliability of DW-based devices.

In addition, the coercivity of single pillars with FLE processed with a thin or thick spacer layer is compared [19]. The TMR values remain constant with pillar size as expected. However, we observe a large dispersion in coercivity in thin spacer-based devices, indicating partial damage to the DW conduit (FLE). A narrow dispersion of coercivity in the thick spacer-based devices indicates that the PMA of the DW conduit layer is less sensitive to the damaging processing steps.

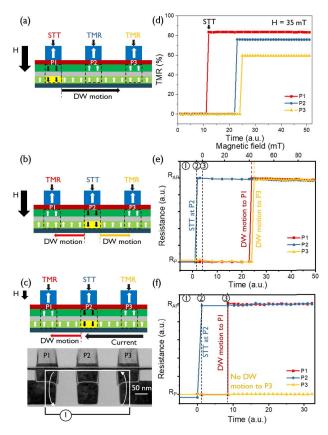

2) Electrical Control of Directional DW Motion With MTJs as Write/Read Components: With all parameters optimized, DW devices with the novel stack were integrated on 300-mm wafers. We first simultaneously measure TMR versus magnetic field loops of three pillars (CD: 100 nm and spacing: 500 nm) sharing the nanotrack (width 200 nm). We then observe overlapping switching fields in all pillars (coercivity: 62 mT), confirming a single domain nucleated and expanded along the track (not shown) [19]. In the following experiment [see Fig. 7(a) and (d)], STT is selectively applied at input pillar P1, seen as an increase in resistance (TMR). This shows that we locally write a domain at a chosen input pillar by STT without impacting the magnetic state of its neighboring pillars. Second, it shows that TMR can be applied to locally detect the magnetic state of the DW track under each pillar. After a domain is locally nucleated at P1, the domain expands along the track sequentially passing the next pillars (P2, then P3), under a constant external field (35 mT ≪ coercivity). High TMR values provide reliable device operation. Note that a

Fig. 7. (a) and (d) STT-driven reversal in P1, expansion by constant field to P2 and P3. (b) and (e) STT-driven reversal in P2, isotropic expansion by sweeping field to P1 and P3. (c) and (f) STT-driven reversal in P2, current-driven DW transport to P1 along current direction. TEM image in (c) presents how the current is applied in the track from via to via.

small variation of TMR in each individual pillar might be due to process variations.

The field-driven experiment in Fig. 7(b) and (e) starts from a uniformly magnetized FL  $\odot$ , a domain is nucleated by STT in the center pillar (P2)  $\odot$ , and we, finally, monitor TMR of all pillars while sweeping the field from 0 to 100 mT  $\odot$ . The domain initiated at P2 expands isotropically through the track to both sides of P2 at the propagation field ( $H_P \sim 42$  mT). This was observed as an increase in resistance from P to AP in both P1 and P3.

Although the manipulation of DWs by field is the first important step in the validation of our novel stack design, it poses challenges in practical applications, i.e., a magnetic field approach is not scalable. However, a transmission electron microscope (TEM) image of a selected device exemplifies that each pillar sits on top of an individual via allowing electrical contact (see Fig. 7). Therefore, in-plane current can flow through the track from via to via, enabling full electrical manipulation of DW transport in our devices. Accordingly, we demonstrate all-electrical control of DW motion, a critical requirement in practical applications. As in the previous experiment, we perform steps ① and ②. Now, a current is applied in the track [see Fig. 7(c) and (f)] from time 3 onward. In contrast to the field-driven case, the DW propagates instantly to P1 as its resistance state changes from P to AP, while it does not arrive at P3 (resistance remains in P state)

Fig. 8. Logic AND gate. (a) Device consists of a track shared by two MTJs. (b) AND truth table defining IN1, IN2, and OUT. (c) Experimental data of AND operation with IN1 = (no) STT, IN2 = 0/HP, and OUT = TMR.

in the measured time frame ( $\sim$ 20 s). The same experiment was performed with the reversed current polarity (not shown), where instant switching in P3 and no switching in P1 were observed, confirming directional DW motion (not shown). Note that an external field of about 25% of the coercivity,  $H_C$ , is used in our experiment. This small assist field helps to suppress process-induced defects, which lead to DW pinning in nanoscale devices and facilitates the current-induced DW motion. We believe that, by further optimization of the MTJ stack and the device integration process in the future, the device can be fully electrically controlled without external field assistance.

Finally, to verify that the switching is not due to random current-driven DW nucleation, the same measurement procedure was carried out, while no domain was initially nucleated by STT. Indeed, no magnetization reversal in any pillar was observed. This experiment proves that directional DW transport was achieved by electrical control.

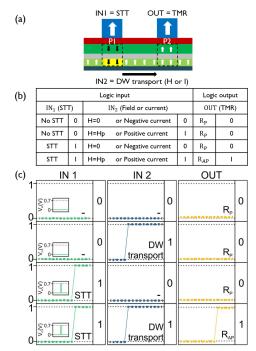

3) Operation of DW-Based Spin Logic Devices: As mentioned above, spin logic devices based on DW motion are currently explored to enable functional rather than dimensional scaling [5], [10], [11]. However, the lack of all-electrical control in previous studies [9], [13], [18], [23] impedes practical applications. In this section, we show that our device proposal indeed provides a significant step forward in the development of spin logic devices where the inputs/outputs can be electrically controlled using MTJs. As an example, we present the operation of a logic AND gate using DW motion in a device with two pillars [see Fig. 8(a)]. Input IN1 is the resistance state at the input pillar, set by STT. Input IN2 is the driving force to propagate the DW from input to output (field or current). Output OUT is defined by the resistance state of

the output pillar, read by TMR [see Fig. 8(b)]. OUT is only logic 1 if a DW was injected (IN1 = 1) and transported to the output (IN2 = 1). Fig. 8(c) displays the truth table of the AND gate where the field is used to propagate the DW to the output (IN2 = 0 corresponds to no field and IN2 = 1 to  $H_P$ ). Importantly, we also obtained the logic AND gate fully electrically, by choosing IN2 = 0 for negative current and IN2 = 1 for positive current (not shown). Note that the OR function was also obtained when IN2 was chosen as 0 at H =  $H_P$  and 1 at H =  $H_C$ .

We believe that this demonstration provides the basic ingredients to enable the implementation of other Boolean logic functionalities in more complex device architectures.

### III. CONCLUSION

We have experimentally demonstrated all-electrical control of a nanoscale logic device based on DW motion using MTJs as inputs and outputs. We employed a novel MTJ stack that not only offers efficient STT write and high TMR read but also provides the possibility for fast device operation through the introduction of high DW speed materials in the DW conduit layer. The demonstration of current-induced directional DW motion and robust large-scale device integration on 300-mm wafers paves the path toward ultrafast, energy-efficient spintronic devices for implementation in the beyond-CMOS logic, racetrack memory, and artificial neural networks.

#### **ACKNOWLEDGMENT**

This work was performed as part of the IMEC IIAP core CMOS and the Beyond CMOS Program of Intel Corporation. The authors gratefully acknowledge Jeroen Heijlen and the P-line for operational support. Eline Raymenants gratefully acknowledges FWO Flanders for a Strategic Basic Research Ph.D. Fellowship.

### REFERENCES

- C. Chappert, A. Fert, and F. N. Van Dau, "The emergence of spin electronics in data storage," in *Nanoscience And Technology: A Collection Rev. from Nature Journals*. Singapore: World Scientific, 2010, pp. 147–157, doi: 10.1142/9789814287005\_0015.

- [2] B. Dieny et al., "Opportunities and challenges for spintronics in the microelectronics industry," *Nature Electron.*, vol. 3, no. 8, pp. 446–459, Aug. 2020, doi: 10.1038/s41928-020-0461-5.

- [3] A. Hatfield, Everspin Debuts First Spin-Torque MRAM for High Performance Storage System. Chandler, AZ, USA: Everspin Technologies, 2012.

- [4] S. Bhatti, R. Sbiaa, A. Hirohata, H. Ohno, S. Fukami, and S. N. Piramanayagam, "Spintronics based random access memory: A review," *Mater. Today*, vol. 20, no. 9, pp. 530–548, Nov. 2017, doi: 10.1016/j.mattod.2017.07.007.

- [5] E. Y. Vedmedenko et al., "The 2020 magnetism roadmap," J. Phys. D, Appl. Phys., vol. 53, no. 45, 2020, Art. no. 453001, doi: 10.1088/1361-6463/ab9d98.

- [6] S. S. P. Parkin, M. Hayashi, and L. Thomas, "Magnetic domain-wall racetrack memory," *Science*, vol. 320, no. 5873, pp. 190–194, Apr. 2008, doi: 10.1126/science.1145799.

- [7] D. A. Allwood, "Magnetic domain-wall logic," *Science*, vol. 309, no. 5741, pp. 1688–1692, Sep. 2005, doi: 10.1126/science.1108813.

- [8] D. E. Nikonov, G. I. Bourianoff, and T. Ghani, "Proposal of a spin torque majority gate logic," *IEEE Electron Device Lett.*, vol. 32, no. 8, pp. 1128–1130, Aug. 2011, doi: 10.1109/LED.2011.2156379.

- [9] J. A. Currivan-Incorvia et al., "Logic circuit prototypes for three-terminal magnetic tunnel junctions with mobile domain walls," *Nature Commun.*, vol. 7, no. 1, pp. 1–7, Apr. 2016, doi: 10.1038/ncomms10275.

- [10] D. E. Nikonov and I. A. Young, "Overview of beyond-CMOS devices and a uniform methodology for their benchmarking," *Proc. IEEE*, vol. 101, no. 12, pp. 2498–2533, Dec. 2013, doi: 10.1109/JPROC.2013.2252317.

- [11] S. Manipatruni, D. E. Nikonov, and I. A. Young, "Beyond CMOS computing with spin and polarization," *Nature Phys.*, vol. 14, no. 4, pp. 338–343, Apr. 2018, doi: 10.1038/s41567-018-0101-4.

- [12] T. P. Xiao et al., "Energy and performance benchmarking of a domain wall-magnetic tunnel junction multibit adder," *IEEE J. Explor. Solid-State Comput. Devices Circuits*, vol. 5, no. 2, pp. 188–196, Dec. 2019, doi: 10.1109/JXCDC.2019.2955016.

- [13] Z. Luo et al., "Current-driven magnetic domain-wall logic," Nature, vol. 579, no. 7798, pp. 214–218, Mar. 2020, doi: 10.1038/s41586-020-2061-v.

- [14] S. Manipatruni et al., "Scalable energy-efficient magnetoelectric spinorbit logic," *Nature*, vol. 565, no. 7737, pp. 35–42, Jan. 2019, doi: 10.1038/s41586-018-0770-2.

- [15] M. Sharad, D. Fan, and K. Roy, "Spin-neurons: A possible path to energy-efficient neuromorphic computers," *J. Appl. Phys.*, vol. 114, no. 23, Dec. 2013, Art. no. 234906, doi: 10.1063/1.4838096.

- [16] X. Fong et al., "Spin-transfer torque devices for logic and memory: Prospects and perspectives," IEEE Trans. Comput. Aided Design Integr. Circuits Syst., vol. 35, no. 1, pp. 1–22, Jan. 2016, doi: 10.1109/TCAD.2015.2481793.

- [17] S. Lequeux et al., "A magnetic synapse: Multilevel spin-torque memristor with perpendicular anisotropy," Sci. Rep., vol. 6, no. 1, Nov. 2016, Art. no. 31510, doi: 10.1038/srep31510.

- [18] S. A. Siddiqui, S. Dutta, A. Tang, L. Liu, C. A. Ross, and M. A. Baldo, "Magnetic domain wall based synaptic and activation function generator for neuromorphic accelerators," *Nano Lett.*, vol. 20, no. 2, pp. 1033–1040, Feb. 2020, doi: 10.1021/acs.nanolett.9b04200.

- [19] E. Raymenants et al., "All-electrical control of scaled spin logic devices based on domain wall motion," in *IEDM Tech. Dig.*, Dec. 2020, p. 21.5.

- [20] W. B. Zeper, F. J. A. M. Greidanus, P. F. Carcia, and C. R. Fincher, "Perpendicular magnetic anisotropy and magneto-optical Kerr effect of vapor-deposited Co/Pt-layered structures," *J. Appl. Phys.*, vol. 65, no. 12, pp. 4971–4975, Jun. 1989, doi: 10.1063/1.343189.

- [21] S. Monso et al., "Crossover from in-plane to perpendicular anisotropy in Pt/CoFe/AlOx sandwiches as a function of al oxidation: A very accurate control of the oxidation of tunnel barriers," Appl. Phys. Lett., vol. 80, no. 22, pp. 4157–4159, Jun. 2002, doi: 10.1063/1.1483122.

- [22] B. Dieny and M. Chshiev, "Perpendicular magnetic anisotropy at transition metal/oxide interfaces and applications," *Rev. Modern Phys.*, vol. 89, no. 2, Jun. 2017, Art. no. 025008, doi: 10.1103/RevMod Phys.89.025008.

- [23] E. Raymenants et al., "Scaled spintronic logic device based on domain wall motion in magnetically interconnected tunnel junctions," in *IEDM Tech. Dig.*, Dec. 2018, pp. 4–36, doi: 10.1109/IEDM.2018.8614587.

- [24] S. Fukami, T. Iwabuchi, H. Sato, and H. Ohno, "Current-induced domain wall motion in magnetic nanowires with various widths down to less than 20 nm," *Jpn. J. Appl. Phys.*, vol. 55, no. 4S, 2016, Art. no. 04EN01, doi: 10.7567/JJAP.55.04EN01.

- [25] V. D. Nguyen et al., "Dimensionality effects on the magnetization reversal in narrow FePt nanowires," Appl. Phys. Lett., vol. 100, no. 25, Jun. 2012, Art. no. 252403, doi: 10.1063/1.4721672.