# Effects of Self-Heating on *f*<sub>T</sub> and *f*<sub>max</sub> Performance of Graphene Field-Effect Transistors

Marlene Bonmann<sup>®</sup>, Marijana Krivic, Xinxin Yang<sup>®</sup>, Andrei Vorobiev<sup>®</sup>, *Member, IEEE*, Luca Banszerus, Christoph Stampfer, Martin Otto<sup>®</sup>, Daniel Neumaier, and Jan Stake<sup>®</sup>, *Senior Member, IEEE*

Abstract—It has been shown that there can be a significant temperature increase in graphene field-effect transistors (GFETs) operating under high drain bias, which is required for power gain. However, the possible effects of self-heating on the high-frequency performance of GFETs have been weakly addressed so far. In this article, we report on an experimental and theoretical study of the effects of self-heating on dc and high-frequency performance of GFETs by introducing a method that allows accurate evaluation of the effective channel temperature of GFETs with a submicrometer gate length. In the method, theoretical expressions for the transit frequency  $(f_{T})$  and the maximum frequency of oscillation  $(f_{max})$  based on the small-signal equivalent circuit parameters are used in combination with the models of the field- and temperature-dependent charge carrier concentration, velocity, and saturation velocity of GFETs. The thermal resistances found by our method are in good agreement with those obtained by the solution of the Laplace equation and by the method of thermo-sensitive electrical parameters. Our experiments and modeling indicate that the self-heating can significantly degrade the  $f_{T}$ and  $f_{max}$  of GFETs at power densities above 1 mW/ $\mu$ m<sup>2</sup>, from approximately 25 to 20 GHz. This article provides valuable insights for further development of GFETs, taking into account the self-heating effects on the high-frequency performance.

*Index Terms*—Field-effect transistors, graphene, microwave amplifiers, self-heating, thermal resistances.

#### I. INTRODUCTION

THE implementation of the fairly new class of 2-D materials, such as graphene [1] and  $MoS_2$  [2], opens up opportunities for new device concepts within electronics and

Manuscript received August 26, 2019; revised October 23, 2019 and December 2, 2019; accepted January 3, 2020. Date of publication January 29, 2020; date of current version February 26, 2020. This work was supported in part by the EU Graphene Flagship Core 2 Project under Grant 785219, in part by the Swedish Foundation for Strategic Research (SSF) under Grant SE13-0061, and in part by the Swedish Research Council (VR) under Grant 2017-04504. The review of this article was arranged by Editor F. Schwierz. *(Corresponding author: Marlene Bonman.)*

Marlene Bonmann, Marijana Krivic, Xinxin Yang, Andrei Vorobiev, and Jan Stake are with the Terahertz and Millimetre Wave Laboratory, Department of Microtechnology and Nanoscience, Chalmers University of Technology, 412 96 Gothenburg, Sweden (e-mail: marbonm@chalmers.se).

Luca Banszerus and Christoph Stampfer are with the 2nd Institute of Physics, RWTH Aachen University, 52074 Aachen, Germany.

Martin Otto and Daniel Neumaier are with the Advanced Microelectronic Center Aachen, AMO GmbH, 52074 Aachen, Germany.

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2020.2965004

optoelectronics [3], [4]. Among the 2-D materials, graphene is considered as a promising new channel material for advanced high-frequency field-effect transistors due to its intrinsically high charge carrier mobility and saturation velocity [5] – [7]. Recently, graphene field-effect transistors (GFETs) with the state-of-the-art extrinsic transit frequency  $f_{\rm T} = 34$  GHz and a maximum frequency of oscillation  $f_{\text{max}} = 37$  GHz at a gate length  $L_g = 0.5 \ \mu m$  have been demonstrated [8]. These values of  $f_{\rm T}$  and  $f_{\rm max}$  are already comparable to those of the best reported Si MOSFETs, but still well below the III-V HEMTs [9]-[11]. It is well recognized that the development of GFETs, operating in the amplifying mode, i.e., with high  $f_{\text{max}}$ , is challenging due to relatively high drain conductance [12]. Additional degradation is possible due to Joule heating, i.e., self-heating, as it has been reported for other high-frequency devices, such as III-V HEMTs [13], [14], and Schottky and heterostructure-barriervaractor diodes [15], [16]. A considerable increase in temperature, up to several hundreds of Kelvin, in a graphene sheet on a SiO<sub>2</sub>/Si substrate has been shown via infrared microscopy and Raman spectroscopy at power densities above 0.1 mW/ $\mu$ m<sup>2</sup> [17], [18]. These power densities are typical for GFETs being developed for current and power amplification applications [8], [19]. This underlines the importance of taking into account the effects of self-heating in practical circuit applications such as GFET mixers and amplifiers [8], [20]–[22], device modeling [23], and optimization of the high-frequency performance, including the gain and noise performance [24]. The dc characteristics and the effect of self-heating on it have been studied theoretically and experimentally [17], [25]-[27]. However, to the best of authors' knowledge, there are no reported systematic theoretical or experimental studies addressing the effects of self-heating and/or external heating on the high-frequency performance, i.e.,  $f_{\rm T}$  and  $f_{\rm max}$ , of GFETs with a submicrometer gate length.

In this article, we provide a theoretical and experimental study of the effects of self-heating and external heating on dc and high-frequency performance of GFETs. In contrast to the test structures used in previous temperature studies, the GFETs considered in this article have the design and layout that are practical for advanced high-frequency amplifier applications, as presented in [8]. Theoretical models that have been developed for other device technologies are not applicable because they either require the knowledge of the thermal conductivities [13] which is in

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see http://creativecommons.org/licenses/by/4.0/

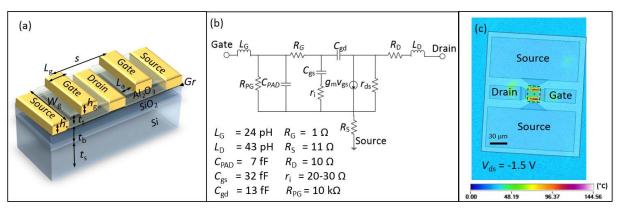

Fig. 1. (a) Device structure of the GFET. The GFET has two gate fingers with a gate length  $L_g = 0.5 \,\mu$ m and a total gate width of  $W_g = 2 \cdot 15 \,\mu$ m. *s* is the separation between the gates, and  $L_a = 0.1 \,\mu$ m is the ungated access length. The top oxide is  $t_t = 18$ -nm-thick Al<sub>2</sub>O<sub>3</sub>.  $h_s = 1$ -nm Ti + 15-nm Pd + 250-nm Au and  $h_g = 10$ -nm Ti + 290-nm Au are the source and gate metal heights, respectively. The substrate is  $t_s = 300 \cdot \mu$ m-thick Si with  $t_b = 1 \cdot \mu$ m-thick SiO<sub>2</sub> on top. (b) Small-signal equivalent circuit of the GFET with extracted parameter values. (c) Infrared image of a GFET at  $V_{gs} = 1.5$  V and  $V_{ds} = -1.5$  V. The gate, drain, and source pads of the transistor are labeled, and the dashed square indicates the GFET area shown in (a).

the case of graphene hard to access [28], or technologyspecific temperature-dependent current-voltage (I-V) dependencies [29]. Therefore, we develop a method for the evaluation of the effective GFET channel temperature using the measured dependencies of  $f_{\rm T}$  and  $f_{\rm max}$  on the drain voltage, i.e., dissipated power densities, and at different external temperatures. For this purpose, theoretical expressions for  $f_{\rm T}$  and  $f_{\rm max}$  based on small-signal equivalent circuit parameters are used in combination with the models of the field-dependent carrier velocity and the temperature-dependent and charge carrier concentration-dependent mobility and saturation velocity of GFETs. In contrast to pulsed I-V studies, which are usually employed to investigate thermal effects, all velocity saturation effects, such as optical phonon and remote optical phonon scattering, are included and can be studied under the real application conditions in this article [30].

We verify our method by comparing the values of the thermal resistance found by our method, by employing a thermal-resistance model based on the solution of the Laplace equation [14], and by thermo-sensitive electrical parameters (TSEP), i.e., the gate leakage current [31]. This article provides valuable insights for further device optimization by considering the heating effects, enabling the development of GFETs for high-frequency applications.

#### II. METHOD

In the following, we introduce a new method for evaluating the field-effect transistor effective channel temperature using the measured values of the drain-source current ( $I_{ds}$ ),  $f_T$ , and  $f_{max}$ . The method allows us to analyze the effects of self-heating and external heating on  $f_T$  and  $f_{max}$ , on the output conductance  $g_{ds}$ , on the effective charge carrier concentration *n*, on the effective velocity *v*, on the saturation velocity  $v_{sat}$ , and on the charge carrier mobility  $\mu$ . Measurements are based on two-finger top-gated GFETs presented in [8] with  $L_g = 0.5 \ \mu m$  and  $W_g = 2 \cdot 15 \ \mu m$ , and the ungated access length  $L_a = 0.1 \ \mu m$ . The top dielectric is a  $t_t = 18$ -nm-thick Al<sub>2</sub>O<sub>3</sub> layer with a relative permittivity  $\epsilon_t = 7.5$ , and the substrate is  $1-\mu m/300-\mu m \operatorname{SiO}_2/\text{high-resistive Si}$ . The device structure is shown in Fig. 1(a). The properties are assumed to be interchangeable for the gate fingers, i.e., not affected by possible variations during fabrication.

## A. Measurements

We used three different methods and corresponding setups for the measurements.

In the first setup, a Quantum Focus Instruments Corporation (QFI) InfraScope was used to demonstrate the self-heating of the GFET, while using a dual-channel Keithley Source Meter 2604B for biasing between the source–gate and source–drain contact. The connection to the GFET is made with ground-signal–ground dc probes. A reference measurement with an unpowered device at a QFI InfraScope stage temperature of 60 °C is conducted to attribute for a different emissivity of different materials on the device sample surface (gold and silicon oxide). Then, the temperature is measured under different bias conditions.

In the second setup, S-parameters were measured using an Agilent E8361A vector network analyzer (VNA) together with a Keithley Source Meter 2604B for biasing and a Temptronic ThermoChuck for controlling the temperature of the sample holder. The connection to the GFET is made with ground-signal-ground RF probes. Calibration at the RF probe tips is performed with a standard calibration substrate. The temperature was swept from room temperature (RT) up to 100 °C, and at each temperature, the bias between source and drain was swept from  $V_{ds} = 0$  to -1.4 V and the source–gate bias is kept at  $V_{gs} = -1$  V as optimal bias for highest measured  $f_T$  and  $f_{max}$ . For each bias point, the measurements are delayed for 30 s to ensure the measurement conditions that do not incur fast charging effects of traps in the gate oxide [32]–[34].

The S-parameters were measured in the frequency range of 1–50 GHz and were used to calculate the small-signal current gain  $(h_{21})$  and the unilateral power gain (U) [35], [36].  $f_{\rm T}$  and  $f_{\rm max}$  are defined as the frequencies at which the magnitudes of  $h_{21}$  and U, respectively, have decreased to 0 dB.

In the third setup, I-V measurements were conducted with a Cascade Summit 12000 probe station with a Temptronic ThermoChuck System and an Agilent B1500A semiconductor analyzer. For this measurement, dc probes were used and

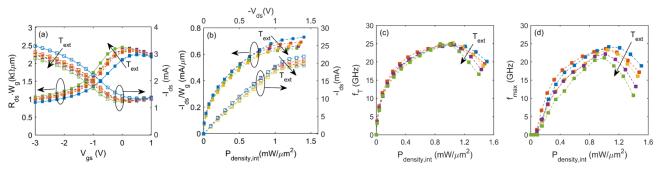

Fig. 2. (a) Normalized drain resistance curves  $(R_{ds} \cdot W_g)$  versus gate voltage  $V_{gs}$ , together with the corresponding transfer curves at  $V_{ds} = -0.1$  V. (b) Normalized drain current  $(I_{ds}/W_g)$  at  $V_{gs} = -1$  V versus intrinsic power density  $P_{density,int}$ , together with the corresponding output characteristics. (c) Transit frequency  $f_T$  and (d) maximum frequency of oscillation  $f_{max}$  versus  $P_{density,int}$ . The arrows indicate external temperatures from  $T_{ext} = 60$  °C, 70 °C, 80 °C, 90 °C, and 100 °C.

connected to one gate finger at a time. The external chuck temperature and the dc bias were swept in the same way as in the second setup.

#### B. Parameter Extraction

First, the output conductance  $g_{ds}$  is estimated by using the measured values of  $f_T$  and  $f_{max}$  and the equations for  $f_T$  and  $f_{max}$  based on the small-signal equivalent circuit parameters of the equivalent circuit shown in Fig. 1(b) [37], [38]

$$f_{\rm T} = \frac{g_m}{2\pi (C_{\rm gs} + C_{\rm gd})} \frac{1}{1 + g_{\rm ds} R_{\rm C} + \frac{C_{\rm gd} g_m R_{\rm C}}{C_{\rm gs} + C_{\rm gd}}} \quad (1)$$

$$f_{\rm max} = \frac{g_m}{4\pi C_{\rm gs}} \frac{1}{\sqrt{g_{\rm ds}(r_{\rm i} + R_{\rm S} + R_{\rm G}) + g_m R_{\rm G} \frac{C_{\rm gd}}{C_{\rm gs}}}}$$

(2)

where  $C_{gs}$  and  $C_{gd}$  are the gate-source and gate-drain capacitances,  $C_{\text{PAD}}$  is the parasitic pad capacitance and  $C_{\text{ox}} = \epsilon_t / t_t$ is the oxide capacitance per unit area,  $r_i$  is the charging resistance, and  $R_{\rm D} = R_{\rm S} = R_{\rm C}/2$  are the drain-source resistances, where  $R_{\rm S}$  and  $R_{\rm D}$  consist of the metal-graphene contact resistance and the resistance of the ungated channel access length  $L_a$  of the graphene channel. The contact resistance  $R_{\rm C}$  is found from fitting the drain-source resistance model to the measured drain-source resistance [39] and changes in the range of 20–23  $\Omega$  with a temperature varying in the range of 60 °C–100 °C. The other small-signal parameters are found from fitting the small-signal equivalent circuit model to the measured S-parameters and are summarized in Fig. 2(b). In contrast to semiconductor MOSFETs, the capacitances  $C_{gs}$ and  $C_{\rm gd}$  of GFETs are not significantly changing with  $V_{\rm ds}$ , due to the lack of a bandgap in graphene, which prevents the formation of a depletion region at the drain, and can be considered constant within the studied bias range. The capacitance values can be taken from [8] as  $C_{PAD} = 7$  fF, and  $C_{\rm gs} \approx 0.5 C_{\rm ox} L_g W_g$  and  $C_{\rm gd} \approx 0.2 C_{\rm ox} L_g W_g$ . The value  $r_i \approx 1/(3 \cdot g_m)$  is the charging resistance of the gate-source capacitance [37].

To obtain  $g_{ds}$ , (1) is rewritten to solve for  $g_m$  and substituted into (2), which is then solved for  $g_{ds}$ .

Second, the found  $g_{ds}$  is used to calculate  $g_m$ .

Third, the effective charge carrier velocity v is estimated using (3)

$$v = \frac{g_m \cdot L_g}{C_{\rm gs} + C_{\rm gd}}.$$

(3)

Equation (3) is derived from the expression for the intrinsic transit frequency  $f_{\text{T,int}} = g_m/(2\pi C_{\text{gs}}) = v/(2\pi L_g)$  [37], with the difference that  $C_{\text{gd}}$  needs to be included since GFETs exhibit no real depletion region in the channel [40]. Fourth, knowing the effective charge carrier velocity allows estimating the effective charge carrier concentration *n* using the measured drain current  $I_{\text{ds}}$  and the relation

$$n = \frac{I_{\rm ds}}{q \cdot W_g \cdot v}.\tag{4}$$

In the last step, the field-dependent velocity model [41]

$$v' = \frac{\mu \cdot E_{\rm ds,int}}{\left(1 + \left(\frac{\mu \cdot E_{\rm ds,int}}{v_{\rm sat}}\right)^{\gamma}\right)^{\frac{1}{\gamma}}}\tag{5}$$

is used together with the temperature- and charge carrier concentration-dependent saturation velocity  $v_{sat}$  [27]

$$v_{\text{sat}}(n,T) = \frac{2}{\pi} \frac{\omega_{\text{OP}}}{\sqrt{\pi \cdot n}} \sqrt{1 - \frac{\omega_{\text{OP}}^2}{4\pi \cdot nv_F^2} \frac{1}{N_{\text{OP}} + 1}}$$

(6)

and temperature- and charge carrier concentration-dependent low-field mobility  $\mu$  [27]

$$u(n,T) = \frac{\mu_0}{1 + (n/n_{\text{ref}})^{\alpha}} \cdot \frac{1}{1 + (T/T_{\text{ref}} - 1)^{\beta}}$$

(7)

to solve for the channel temperature T at v = v'.  $E_{ds, int} = (V_{ds} - R_{C} \cdot I_{ds})/L_g$  is the intrinsic electric field,  $\gamma = 3$  is a model parameter,  $N_{OP} = 1/[\exp(\hbar\omega_{OP}/k_{B}T) - 1]$  is the phonon occupation,  $\hbar\omega_{OP} \approx 81$  eV is the optical phonon energy,  $\mu_0 = 0.17 \text{ m}^2/\text{Vs}$  is the low-field mobility found from fitting the drain-source resistance model [39] to the measured drain-source resistance, and the parameters  $n_{ref} =$  $1.1 \cdot 10^{13} \text{ cm}^{-2}$ ,  $T_{ref} = 250 \text{ K}$ ,  $\alpha = 2.2$ , and  $\beta = 3$  [27]. The analysis of the results in the following focuses on the bias range  $V_{ds} = -0.5$  to -1.4 V since (7) is limited to  $n > 2 \cdot 10^{16} \text{ m}^{-2}$  [27].

The derivative of the found temperature T with respect to the intrinsic dissipated power  $P_{\text{int}} = P_{\text{density,int}} \cdot L_g \cdot W_g = (V_{\text{ds}} - R_{\text{C}}I_{\text{ds}}) \cdot I_{\text{ds}}$  is used to estimate the thermal resistance  $R_{\text{th}}$  of the GFETs.

In addition, the method of TSEP is used to estimate  $R_{\text{th}}$ . The TSEP method relies on the thermal dependence of electrical properties, such as the threshold voltage and saturation current, to estimate the temperature of semiconductor devices, where

the channel is not accessible by direct temperature measurement methods [31]. In this article, we employ the temperature dependence of the gate leakage current  $(I_g)$ . Fig. 2(c) shows that  $I_g$  increases exponentially with  $P_{\text{density,int}}$  and  $T_{\text{ext}}$  due to external heating and self-heating in agreement with the most probable conduction mechanisms, such as the Poole–Frenkel transport mechanism and the field-enhanced Schottky mechanism [42].  $R_{\text{th}}$  is found based on the differential of the gate leakage current  $I_g$  with respect to  $P_{\text{int}}$  and the temperature T as  $R_{\text{th}} = (\partial I_g / \partial P_{\text{int}}) \cdot (\partial T / \partial I_g)$ . For  $P_{\text{density,int}}$  below 0.4 mW/ $\mu$ m<sup>2</sup>, the leakage current is too small to observe a significant change in  $I_g$  with changing  $P_{\text{density,int}}$  or  $T_{\text{ext}}$ . The estimate of  $R_{\text{th}}$  analyzed below is evaluated for  $P_{\text{density,int}} >$ 0.4 mW/ $\mu$ m<sup>2</sup>.

Furthermore, we calculated  $R_{\text{th}}$  by an analytical thermal-resistance model [14].

Finally, we analyze the potential performance of GFETs assuming that there is no degrading due to self-heating by using the charge carrier concentration found from measurements and then estimating v' using (5)–(7) at different external temperatures. Knowing v and n allows us to calculate  $I_{ds}$  as follows:

$$I_{\rm ds} = q \cdot W_g \cdot v' \cdot n \tag{8}$$

and  $g_m$  using (3). Since, in this case,  $I_{ds}$  is not affected by self-heating at high fields, we can estimate  $g_{ds}$  as the derivative  $I_{ds}$  with respect to the intrinsic drain-source voltage  $V_{ds,int} = V_{ds} - R_C I_{ds}$  as follows:

$$g_{\rm ds} = \frac{\partial I_{\rm ds}}{\partial V_{\rm ds,int}}|_{V_{\rm gs} = \rm const.}$$

(9)

Then,  $f_{\rm T}$  and  $f_{\rm max}$  are calculated using (1) and (2), respectively.

#### **III. RESULTS AND DISCUSSION**

Investigation of the GFETs by *IR* microscopy clearly shows that the temperature in the channel region increases with the drain bias, as shown in Fig. 1(c). Since the top oxide layer and the metal layer are very thin, the temperature on the top of the gate metal can be assumed to be the same as in the channel. However, we can assume that the *IR* microscope underestimates the real channel temperature, due to the resolution limitations of approximately 1.6  $\mu$ m per pixel, which is larger than  $L_g = 0.5 \ \mu$ m.

Fig. 2 shows the measured drain-source resistance divided by the gate width and the drain current divided by the gate width as well as  $f_{\rm T}$  and  $f_{\rm max}$  versus the intrinsic dissipated power density at different external temperatures of  $T_{\rm ext} =$ 60 °C, 70 °C, 80 °C, 90 °C, and 100 °C. It can be seen from Fig. 2(a) that the voltage for minimal conductance, e.g., the Dirac voltage ( $V_{\rm Dir}$ ), shifts with the measurements, which can be explained by charge carrier detrapping [34]. Detrapping is a thermally activated process leading to the release of more electrons from traps with increasing temperature supported by the negative bias at the gate. This leads to the observed shift from the positive  $V_{\rm Dir}$  for the first few measurement sweeps to  $V_{\rm Dir} \approx 0$  V. The resistance is larger at higher external temperatures. This can be associated not only with a decrease of the low-field mobility with higher temperature (7) but also with the charge detrapping from the oxide, which leads to a reduction of the residual charge carrier concentration and originates from charge inhomogeneities in the channel. In addition, the contact resistance increases slightly from 20 to 23  $\Omega$ .

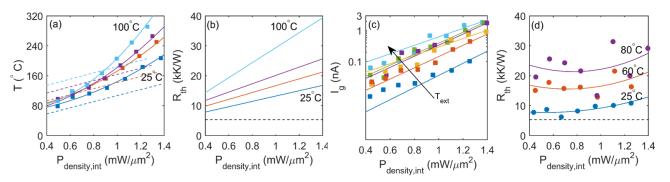

Fig. 2(b) shows that the drain-source current  $I_{ds}$  is saturating at intrinsic power densities  $P_{\text{density,int}} = (V_{\text{ds}} - R_{\text{C}} \cdot$  $I_{\rm ds}$ ) ·  $I_{\rm ds}/(L_g \cdot W_g)$  of approximately 1 mW/ $\mu$ m<sup>2</sup>, which corresponds to  $V_{ds} = -1$  V and an intrinsic lateral field of  $E_{\rm ds,int} \approx 1 \, {\rm V}/\mu{\rm m}$  consistent with previous publications [27], [32]. Depending on the bias condition, it is possible to observe a so-called "kink" in the output curve of GFETs. This is attributed to the lack of a bandgap of graphene, which leads to the change of the charge carrier type at the drain side of the GFET channel instead of the formation of a depletion region as in semiconductor counterparts. In our measurements, this condition can be reached at  $V_{\rm ds} \approx -1$ V (for  $T_{\rm ext} = 100$  °C) when  $V_{\rm ds} \approx V_{\rm gs} - V_{\rm Dir}$ . Taking into account the typical width of the kink of approximately 0.5 V [8], one can expect observing the kink at  $-V_{ds}$  above 1.5 V, which is out of the studied  $V_{ds}$  range [see Fig. 2(b)]. The weak decrease in the saturation current of 5% above  $V_{\rm ds} > 1$  V with a larger  $T_{\rm ext}$  can be explained by the decreasing saturation velocity and mobility with temperature. Fig. 2(c)and (d) shows that both the values of  $f_{\rm T}$  and  $f_{\rm max}$  decrease rapidly starting from  $P_{\text{density,int}} \approx 1 \text{ mW}/\mu\text{m}^2$ . The strong decrease of  $f_{\rm T}$  has been similarly observed in InGaP/GaAs heterojunction bipolar transistors [44]. As seen, the effect of the extrinsic temperature on  $f_{\text{max}}$  is more remarkable than that on  $f_{\rm T}$ . It will be shown below that the decrease in  $f_{\rm T}$ and  $f_{\text{max}}$  at higher  $P_{\text{density,int}}$  can be fully explained by selfheating. Fig. 3(a) shows the effective channel temperature found using (1)-(7) and calculated by the thermal-resistance model [14] for different  $T_{\text{ext}}$ . The temperatures extracted by the method presented in this article increase strongly for  $P_{\text{density.int}} > 1 \text{ mW}/\mu\text{m}^2$ , while the thermal-resistance model predicts lower temperatures. Fig. 3(b) shows the thermal resistance extracted as the derivative of the polynomial fit in Fig. 3(a) together with  $R_{\rm th}$  estimated by the thermal-resistance model. For low  $P_{\text{density,int}} \approx 0.6 \text{ mW}/\mu\text{m}^2$ , the thermal resistance estimated by the thermal-resistance model  $R_{\rm th} \approx$ 6 kK/W agrees well with the temperatures extracted by the method presented in this article. The disagreement at higher  $P_{\rm int}$  and external temperatures can be explained by an increase in the thermal resistances, which is not taken into account sufficiently by the thermal-resistance model for the GFET system. To evaluate  $R_{\rm th}$  by yet another method, we use the temperature and dissipated power dependence of  $I_g$  to extract  $R_{\text{th}}$  using the TSEP method [31], [45], as described in Section II. Fig. 3(c) shows the gate leakage current  $(I_g)$ versus  $P_{\text{density,int}}$ , which is used to estimate  $R_{\text{th}}$  estimated by the TSEP method shown in Fig. 3(d). The resolution ratio of the TSEP method is approximately 0.2. Fig. 3(d) shows the  $R_{\rm th}$ estimated by the TSEP method versus P<sub>density,int</sub>. It can be seen that  $R_{\rm th}$  evaluated by the TSEP method agrees fairly well with that calculated with our proposed method.  $R_{\rm th}$  increases with  $P_{\text{density,int}}$  and  $T_{\text{ext}}$ , explaining, as expected, the deviations of

Fig. 3. (a) Effective channel temperature *T* derived using (1) –(7) (symbols) versus intrinsic dissipated power density  $P_{density,int}$  (corresponds to  $V_{ds}$  in the range -0.3 to -1.4 V) at external temperatures  $T_{ext} = 25 \degree C$ , 60 °C, 80 °C, and 100 °C. The lines are polynomial fitting curves. The temperatures calculated by the thermal-resistance model (dashed lines) [14] are also shown. (b) Thermal resistance  $R_{th}$  versus intrinsic dissipated power density  $P_{density,int}$  estimated as the derivative of the polynomial fit in (a) and estimated by the thermal-resistance model (dashed line). (c) Gate leakage current  $I_g$  versus  $P_{density,int}$  and  $T_{ext}$  ranging from 25 °C to 100 °C. (d)  $R_{th}$  versus  $P_{density,int}$  estimated by the method of TSEPs (circles) with polynomial fitting curves (solid lines).

temperature evaluated by the method presented in this article and the thermal-resistance model at higher  $P_{\text{density,int}}$  and  $T_{\text{ext}}$ [see Fig. 3(a) and (b)]. The temperature dependence of  $R_{\text{th}}$  can be explained by the temperature dependence of the thermal conductivity of the involved materials that may decrease by half for an increase in the temperature by self-heating of approximately 300 K [46], [47]. This is associated with more intensive phonon scattering at higher temperatures since the thermal conductivity is related to the mean-free path and the phonon group velocity [46], [47]. Analysis of Figs. 2(c) and (d) and 3(a) allows us to conclude that the decrease in  $f_{\rm T}$  and  $f_{\rm max}$  and higher  $P_{\rm density,int}$ , respectively, can be fully explained by self-heating. Indeed,  $\Delta P_{\text{density,int}}$  of approximately 0.4 mW/ $\mu$ m<sup>2</sup> results in  $\Delta T$  of approximately 40 °C [see Fig. 3(a)]. On the other hand, the corresponding increase in  $P_{\text{density,int}}$  from 1.0 to 1.4 mW/ $\mu$ m<sup>2</sup> results in the decrease of  $f_{\text{max}}$  from approximately 20 to 10 GHz, which is similar to that caused by the increase in T<sub>ext</sub> from 60 °C to 100 °C in the same power region [see Fig. 2(d)]. Other mechanisms that are causing irreversible degradation, such as oxide breakdown or current breakdown, can be ruled out since the GFETs recovered after measurements and the gate leakage current is low, i.e., in the nA range, even at high fields and temperatures, and the breakdown current density of graphene has been shown to be three orders of magnitude larger than the maximum current density in this article [48].

Thus, self-heating clearly affects the high-frequency performance of GFETs limiting  $f_{\rm T}$  and  $f_{\rm max}$  at higher source–drain fields. However, the self-heating effect can be controlled and minimized by optimizing the transistor layouts and selecting substrate materials with higher thermal conductivity. Calculations, using the analytical thermal-resistance model, indicate that the GFET thermal resistance associated with the SiO<sub>2</sub> layer dominates and is approximately 80% of that of the total SiO<sub>2</sub>/Si substrate. For comparison, the thermal conductivity of sapphire, which, for example, can be used as the GFET substrate without the SiO<sub>2</sub> layer, is  $\approx 35$  W/mK [49], which is significantly higher than that of SiO<sub>2</sub> with 1.4 W/mK [50]. In the analysis below, we simulate the GFET high-frequency performance with and without the self-heating effect.

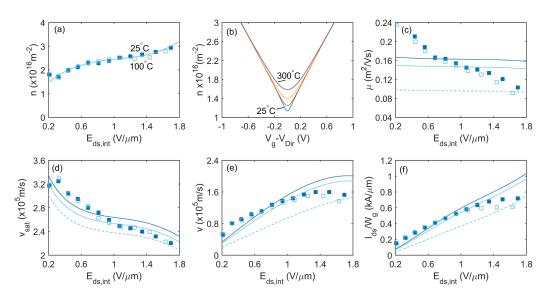

Applying the equations discussed in Section II, we estimated the mobility  $\mu$ , the saturation velocity  $v_{sat}$ , the effective channel velocity v, the drain-source current  $I_{ds}$ , the output conductance  $g_{ds}$ , and  $f_T$  and  $f_{max}$  assuming T = 27 °C, 100 °C, and 250 °C. Fig. 4(a) shows the charge carrier concentration *n* estimated from the measured  $f_{\rm T}$ ,  $f_{\rm max}$ , and  $I_{\rm ds}$ using (1)–(4). The increase of n with  $E_{ds,int}$  can be explained mainly by self-gating since there is no significant difference in *n* for different  $T_{\text{ext}}$ . Applying  $V_{\text{ds}}$  results in an effective gate bias at the drain side of the channel, which will alters the charge carrier concentration. For illustration, Fig. 4(b) shows the charge carrier concentration n versus the applied gate voltage overdrive,  $V_{gs} - V_{Dir}$ , at different temperatures. The charge carrier concentration constitutes the sum of thermally generated charge carriers  $n_{\rm th}$ , residual charge carriers  $n_0$  due to the charged impurity doping [51], and gate-induced charge carriers  $n_g$ . In our calculations,  $n_0 = 1 \cdot 10^{16} \text{ m}^{-2}$  and  $n_{\text{th}} + n_g$ dependent on the position of the Fermi level is calculated as in [43], and the relation between the gate bias  $V_{gs}$  and  $E_F$ is established as  $V_{gs} = (Q_g + Q_{ox})/C_{ox} + E_F$ , where  $Q_g$  is the charge in the graphene sheet and  $Q_{ox}$  is the charge in the oxide, which constitute the charge trapped in deep traps and interface states [43]. Fig. 4(b) shows that higher temperatures only affect *n* noticeably close to  $|V_{gs} - V_{Dir}| = 0$  V. Therefore, we use the average charge carrier concentration n, as shown in Fig. 4(a), in (4), (6), and (7) to estimate  $I_{ds}$ ,  $\mu$ , and  $v_{sat}$ without the effect of self-heating.

Fig. 4(c) and (d) shows the low-field mobility  $\mu$  and saturation velocity  $v_{sat}$  versus  $E_{ds,int}$ . Comparison of Fig. 4(c) and (d) and Fig. 4(a) indicates that both  $\mu$  and  $v_{sat}$  correlate with variations in the charge carrier concentration. When removing the effect of self-heating (lines), the mobility increases from  $\mu \approx 0.1$  to 0.16 m<sup>2</sup>/Vs and  $v_{sat}$  from  $\approx 2 \cdot 10^5$  to 2.3  $\cdot 10^5$ m/s, for external temperatures up to 100 °C. For  $T_{ext}$  above 100 °C,  $\mu$  and  $v_{sat}$  and, hence, v are strongly degraded. The low-field mobility below  $E_{ds,int} = 0.6$  V/ $\mu$ m increases sharply due to the limitation of (7) being only valid for  $n > 2 \cdot 10^{16}$  m<sup>-2</sup> [27]. Fig. 4(e) shows the effective drift velocity v in the channel versus  $E_{ds,int}$  calculated by (5). The velocity increases with increasing  $E_{ds,int}$  according to

Fig. 4. (a) Charge carrier concentration *n* derived from measurements at  $T_{ext} = 25 \degree C$  and 100 °C versus intrinsic electric field  $E_{ds,int}$  (solid and open squares, respectively) together with a polynomial fitting curve of the average of these two that is used for the calculations of the solid and dashed lines in (c)–(f). (b) Charge carrier concentration *n* versus applied gate voltage  $V_{gs} - V_{Dir}$  at  $T_{ext} = 25 \degree C$ , 100 °C, 200 °C, and 300 °C calculated as in [43]. (c) Low-field mobility  $\mu$  calculated using (7). (d) Velocity saturation  $v_{sat}$  calculated using (6). (e) Effective drift velocity *v* calculated using (5). (f) Drain current divided by gate width  $I_{ds}/W_g$  versus drain–source intrinsic electric field  $E_{ds,int}$ , where  $I_{ds}$  is measured or calculated using (8). In (c)–(e), the lines are dependencies simulated without self-heating for  $T_{ext} = 25 \degree C$ , 100 °C, and 250 °C (solid, dashed-dotted, and dashed lines, respectively).

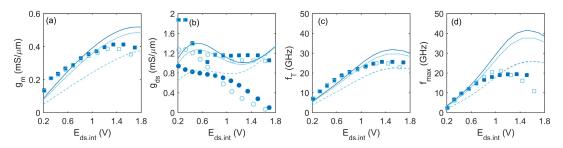

Fig. 5. (a) Transconductance divided by a gate width  $g_m/W_g$ . (b) Output conductance divided by a gate width  $g_{ds}/W_g$ , (c)  $t_T$ , and (d)  $t_{max}$  versus intrinsic drain–source electric field  $E_{ds,int}$  (corresponding to  $V_{ds}$  in the range from -0.2 to -1.4 V) derived from measurements using (1) and (2) for  $T_{ext} = 25$  °C and 100 °C (solid and open squares, respectively) and simulated without self-heating using (9) for  $T_{ext} = 25$  °C, 100 °C, and 250 °C (solid, dashed-dotted, and dashed lines). In (b),  $g_{ds}/W_g$  is also shown, calculated using (9) from the measured  $I_{ds}$  shown in Fig. 4(f) for  $T_{ext} = 25$  °C and 100 °C (solid and open circles, respectively).

the field-dependent velocity model. At  $E_{ds,int} \approx 1.2 \text{ V}/\mu\text{m}$ , the velocity drops rapidly due to self-heating. If self-heating is avoided, the velocity in the channel continues to increase by approximately 20% compared to the measurements with self-heating. The measured drain–source current divided by the gate width and  $I_{ds}/W_g$  calculated without self-heating using (8) is shown in Fig. 4(f). The  $I_{ds}$  without self-heating is larger at high fields due to the larger velocity for  $T_{ext} = 25 \text{ °C}$ and 100 °C and smaller for  $T_{ext} = 250 \text{ °C}$  due to a strong decrease in  $\mu$  and  $v_{sat}$ . The good agreement of the measured and modeled  $I_{ds}$  at  $E_{ds,int} = 1.8 \text{ V}/\mu\text{m}$  and  $T_{ext} = 250 \text{ °C}$ indicates that the temperature estimate shown in Fig. 3(a) of approximately 250 °C at  $P_{density,int} = 1.4 \text{ mW}/\mu\text{m}^2$  is reasonable.

Fig. 5 shows  $g_m/W_g$ ,  $g_{ds}/W_g$ ,  $f_T$ , and  $f_{max}$  versus  $E_{ds,int}$ , where  $g_m$  and  $g_{ds}$  are estimated from measurements using (1) and (2). The values of these parameters without self-heating calculated using (9) are also shown. Due to the relation

between v and  $g_m$  given by (3), the transconductance exhibits the same dependence as v on  $E_{ds,int}$  and  $T_{ext}$ . Fig. 5(b) shows that  $g_{ds}$  extracted from  $f_T$  and  $f_{max}$  is almost constant with  $E_{\rm ds,int}$ . In addition,  $g_{\rm ds}$  calculated using (9) and measured  $I_{\rm ds}$ from Fig. 4(f) are shown. Due to the self-heating effects,  $I_{ds}$ exhibits a slightly negative slope at high fields that results in the negative  $g_{ds}$  [out of bounds in Fig. 5(b)]. The negative  $g_{ds}$  is also observed in MOSFETs and HEMTs and is associated with trapping and heating effects that lead to the reduction of the effective applied gate voltage and a reduction of the saturation velocity and mobility [52], [53]. The  $g_{ds}$ calculated without self-heating first follows the slope of  $g_{ds}$ with self-heating and then increases again at higher fields due to larger current  $I_{ds}$  [see Fig. 4(f)]. Fig. 5 shows that  $f_T$ and  $f_{\text{max}}$  are not notably affected by self-heating for fields below 1 V/ $\mu$ m, which is not surprising since  $g_m$  and  $g_{ds}$ are not affected. Channel temperatures below  $T_{\rm ext} \approx 200$  °C do not significantly affect the temperature-dependent mobility

and saturation velocity [27], and, thus, the high-frequency performance. However, at high fields above  $E_{ds,int} = 1 \text{ V}/\mu\text{m}$ , self-heating leads to a significant increase of the channel temperature, which is additionally boosted by an increase of the thermal resistance. Therefore, there would be a clear improvement in  $f_T$  and  $f_{max}$  at  $E_{ds,int}$  above  $1 \text{ V}/\mu\text{m}$ , if the self-heating case is avoided, from approximately 18 GHz up to approximately 30 and 40 GHz, respectively.

# **IV. CONCLUSION**

In summary, we studied the effects of self-heating and external heating on the high-frequency performance of GFETs. We presented a new method that allows for the evaluation of the thermal resistance of GFETs with a submicrometer gate length. The method has the advantage that in addition to the temperature, it also allows for the evaluation of the output conductance, the effective channel velocity, the charge carrier concentration, the saturation velocity, and the mobility. Hence, it allows for studying the effect of self-heating and external heating on these parameters. Another advantage is that our method does not rely on the estimate of the charge carrier concentration derived from the applied gate voltage since there is typically some shift of the Dirac point during extensive measurements due to charge trapping and detrapping in the gate oxide, which is dependent on the measurement sweeping rate [33], [34]. Analysis of the experimental and theoretical dependencies of the transit frequency and maximum frequency of oscillation of GFETs on the drain-source voltage and different external temperatures indicates that at the power densities above approximately 1 mW/ $\mu$ m<sup>2</sup>, the highfrequency performance significantly degrades due to selfheating. For instance, the extrinsic  $f_{\rm T}$  and  $f_{\rm max}$  decrease from approximately 25 down to 20 GHz explained by a decrease in the low-field mobility and saturation velocity although the drain conductance decreases with temperature. This article provides valuable insights for further development of GFETs for high-frequency applications, taking into account the self-heating as well as the external heating effects on the high-frequency performance. The self-heating effect can be significant, particularly for GFETs on flexible polymer substrates [54], in which the thermal conductivity is typically lower than that of rigid substrates. In future work, a temperature-dependent nonlinear  $R_{\rm th}$  model for the GFET system is required for more accurate simulations of the GFET channel temperature and corresponding further optimization of the device design.

### REFERENCES

- K. S. Novoselov, "Electric field effect in atomically thin carbon films," *Science*, vol. 306, no. 5696, pp. 666–669, Oct. 2004, doi: 10.1126/ science.1102896.

- [2] K. F. Mak, C. Lee, J. Hone, J. Shan, and T. F. Heinz, "Atomically thin MoS<sub>2</sub>: A new direct-gap semiconductor," *Phys. Rev. Lett.*, vol. 105, Sep. 2010, Art. no. 136805, doi: 10.1103/PhysRevLett.105.136805.

- [3] F. Schwierz, J. Pezoldt, and R. Granzner, "Two-dimensional materials and their prospects in transistor electronics," *Nanoscale*, vol. 7, no. 18, pp. 8261–8283, Apr. 2015, doi: 10.1039/c5nr01052g.

- [4] X. Li et al., "Graphene and related two-dimensional materials: Structure-property relationships for electronics and optoelectronics," *Appl. Phys. Rev.*, vol. 4, no. 2, Jun. 2017, Art. no. 021306, doi: 10. 1063/1.4983646.

- [5] M. A. Yamoah, W. Yang, E. Pop, and D. Goldhaber-Gordon, "High-velocity saturation in graphene encapsulated by hexagonal boron nitride," *ACS Nano*, vol. 11, no. 10, pp. 9914–9919, Oct. 2017, doi: 10. 1021/acsnano.7b03878.

- [6] F. Schwierz, "Graphene transistors: Status, prospects, and problems," *Proc. IEEE*, vol. 101, no. 7, pp. 1567–1584, Jul. 2013, doi: 10. 1109/jproc.2013.2257633.

- [7] G. Fiori et al., "Electronics based on two-dimensional materials," *Nature Nanotechnol.*, vol. 9, no. 10, pp. 768–779, Oct. 2014, doi: 10. 1038/nnano.2014.207.

- [8] M. Bonmann *et al.*, "Graphene field-effect transistors with high extrinsic f<sub>T</sub> and f<sub>max</sub>," *IEEE Electron Device Lett.*, vol. 40, no. 1, pp. 131–134, Jan. 2019, doi: 10.1109/LED.2018.2884054.

- [9] A. Leuther *et al.*, "20 nm metamorphic hemt technology for terahertz monolithic integrated circuits," in *Proc. 9th Eur. Microw. Integr. Circuit Conf.*, Oct. 2014, pp. 84–87, doi: 10.1109/EuMIC.2014. 6997797.

- [10] D.-H. Kim, B. Brar, and J. A. del Alamo, "fT=688 GHz and fmax=800 GHz in Lg=40 nm In0.7Ga0.3As MHEMTs with gm\_max>2.7 mS/μm," in *IEDM Tech. Dig.*, Dec. 2011, pp. 13.6.1–13.6.4, doi: 10.1109/IEDM.2011.6131548.

- [11] M. Micovic *et al.*, "High frequency GaN HEMTs for RF MMIC applications," in *IEDM Tech. Dig.*, Dec. 2016, doi: 10.1109/iedm. 2016.7838337.

- [12] F. Schwierz, "Industry-compatible graphene transistors," *Nature*, vol. 472, no. 7341, pp. 41–42, Apr. 2011, doi: 10.1038/472041a.

- [13] J. C. Freeman, "Channel temperature model for microwave AlGaN/GaN power HEMTs on SiC and sapphire," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Oct. 2004, pp. 2031–2034, doi: 10.1109/ mwsym.2004.1339012.

- [14] A. Darwish, A. J. Bayba, and H. A. Hung, "Channel temperature analysis of GaN HEMTs with nonlinear thermal conductivity," *IEEE Trans. Electron Devices*, vol. 62, no. 3, pp. 840–846, Mar. 2015, doi: 10.1109/ted.2015.2396035.

- [15] A. Y. Tang *et al.*, "Electro-thermal model for multi-anode Schottky diode multipliers," *IEEE Trans. THz Sci. Technol.*, vol. 2, no. 3, pp. 290–298, May 2012, doi: 10.1109/tthz.2012.2189913.

- [16] J. Stake, A. Malko, T. Bryllert, and J. Vukusic, "Status and prospects of high-power heterostructure barrier varactor frequency multipliers," *Proc. IEEE*, vol. 105, no. 6, pp. 1008–1019, Jun. 2017, doi: 10. 1109/jproc.2016.2646761.

- [17] M.-H. Bae, S. Islam, V. E. Dorgan, and E. Pop, "Scaling of high-field transport and localized heating in graphene transistors," ACS Nano, vol. 5, no. 10, pp. 7936–7944, Oct. 2011, doi: 10.1021/nn202239y.

- [18] S.-K. Son *et al.*, "Graphene hot-electron light bulb: Incandescence from hBN-encapsulated graphene in air," *2D Mater.*, vol. 5, no. 1, 2017, Art. no. 011006, doi: 10.1088/2053-1583/aa97b5.

- [19] I. Meric *et al.*, "High-frequency performance of graphene field effect transistors with saturating IV-characteristics," in *IEDM Tech. Dig.*, Dec. 2011, pp. 2.1.1–2.1.4, doi: 10.1109/iedm.2011.6131472.

- [20] H. Lyu *et al.*, "Graphene distributed amplifiers: Generating desirable gain for graphene field-effect transistors," *Sci. Rep.*, vol. 5, Dec. 2015, Art. no. 17649, doi: 10.1038/srep17649.

- [21] O. Habibpour, S. Cherednichenko, J. Vukusic, K. Yhland, and J. Stake, "A subharmonic graphene FET mixer," *IEEE Electron Device Lett.*, vol. 33, no. 1, pp. 71–73, Jan. 2012, doi: 10.1109/led.2011.2170655.

- [22] M. Saeed, A. Hamed, Z. Wang, M. Shaygan, D. Neumaier, and R. Negra, "Metal-insulator-graphene diode mixer based on CVD grapheneon-glass," *IEEE Electron Device Lett.*, vol. 39, no. 7, pp. 1104–1107, Jul. 2018, doi: 10.1109/LED.2018.2838451.

- [23] O. Habibpour, J. Vukusic, and J. Stake, "A large-signal graphene FET model," *IEEE Trans. Electron Devices*, vol. 59, no. 4, pp. 968–975, Apr. 2012, doi: 10.1109/ted.2012.2182675.

- [24] M. Tanzid, M. A. Andersson, J. Sun, and J. Stake, "Microwave noise characterization of graphene field effect transistors," *Appl. Phys. Lett.*, vol. 104, no. 1, Jan. 2014, Art. no. 013502, doi: 10.1063/ 1.4861115.

- [25] I. Meric *et al.*, "Channel length scaling in graphene field-effect transistors studied with pulsed current-voltage measurements," *Nano Lett.*, vol. 11, no. 3, pp. 1093–1097, 2011, doi: 10.1021/nl103993z.

- [26] S. Islam, Z. Li, V. E. Dorgan, M.-H. Bae, and E. Pop, "Role of joule heating on current saturation and transient behavior of graphene transistors," *IEEE Electron Device Lett.*, vol. 34, no. 2, pp. 166–168, Feb. 2013, doi: 10.1109/led.2012.2230393.

- [27] V. E. Dorgan, M.-H. Bae, and E. Pop, "Mobility and saturation velocity in graphene on SiO<sub>2</sub>," *Appl. Phys. Lett.*, vol. 97, no. 8, Aug. 2010, Art. no. 082112, doi: 10.1063/1.3483130.

- [28] A. A. Balandin, "Thermal properties of graphene and nanostructured carbon materials," *Nature Mater.*, vol. 10, no. 8, pp. 569–581, Aug. 2011, doi: 10.1038/nmat3064.

- [29] T. Kiuru, J. Mallat, A. V. Raisanen, and T. Narhi, "Schottky diode series resistance and thermal resistance extraction from S-parameter and temperature controlled I–V measurements," *IEEE Trans. Microw. Theory Techn.*, vol. 59, no. 8, pp. 2108–2116, Aug. 2011, doi: 10. 1109/TMTT.2011.2146268.

- [30] H. Ramamoorthy, R. Somphonsane, J. Radice, G. He, C.-P. Kwan, and J. P. Bird, "Freeing' graphene from its substrate: Observing intrinsic velocity saturation with rapid electrical pulsing," *Nano Lett.*, vol. 16, no. 1, pp. 399–403, 2015, doi: 10.1021/acs.nanolett.5b04003.

- [31] Y. Avenas, L. Dupont, and Z. Khatir, "Temperature measurement of power semiconductor devices by thermo-sensitive electrical parameters—A review," *IEEE Trans. Power Electron.*, vol. 27, no. 6, pp. 3081–3092, Jun. 2012, doi: 10.1109/TPEL.2011.2178433.

- [32] M. Bonmann, A. Vorobiev, M. A. Andersson, and J. Stake, "Charge carrier velocity in graphene field-effect transistors," *Appl. Phys. Lett.*, vol. 111, no. 23, Dec. 2017, Art. no. 233505, doi: 10.1063/1.5003684.

- [33] H. Wang, Y. Wu, C. Cong, J. Shang, and T. Yu, "Hysteresis of electronic transport in graphene transistors," ACS Nano, vol. 4, no. 12, pp. 7221– 7228, Dec. 2010, doi: 10.1021/nn101950n.

- [34] H. Ramamoorthy *et al.*, "Probing charge trapping and joule heating in graphene field-effect transistors by transient pulsing," *Semicond. Sci. Technol.*, vol. 32, no. 8, Aug. 2017, Art. no. 084005, doi: 10. 1088/1361-6641/aa7ba3.

- [35] S. Mason, "Power gain in feedback amplifier," *Trans. IRE Prof. Group Circuit Theory*, vols. CT–1, no. 2, pp. 20–25, Jun. 1954, doi: 10. 1109/tct.1954.1083579.

- [36] M. Gupta, "Power gain in feedback amplifiers, a classic revisited," *IEEE Trans. Microw. Theory Techn.*, vol. 40, no. 5, pp. 864–879, May 1992, doi: 10.1109/22.137392.

- [37] F. Schwierz and J. J. Liou, Modern Microwave Transistors: Theory, Design, and Performance. Hoboken, NJ, USA: Wiley, 2002.

- [38] S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices*. Hoboken, NJ, USA: Wiley, 2007.

- [39] S. Kim *et al.*, "Realization of a high mobility dual-gated graphene fieldeffect transistor with Al<sub>2</sub>O<sub>3</sub> dielectric," *Appl. Phys. Lett.*, vol. 94, no. 6, Feb. 2009, Art. no. 062107, doi: 10.1063/1.3077021.

- [40] I. Meric, M. Y. Han, A. F. Young, B. Ozyilmaz, P. Kim, and K. L. Shepard, "Current saturation in zero-bandgap, top-gated graphene field-effect transistors," *Nature Nanotech*, vol. 3, no. 11, pp. 654–659, Nov. 2008, doi: 10.1038/nnano.2008.268.

- [41] D. Caughey and R. Thomas, "Carrier mobilities in silicon empirically related to doping and field," *Proc. IEEE*, vol. 55, no. 12, pp. 2192–2193, 1967, doi: 10.1109/proc.1967.6123.

- [42] P. Li and T.-M. Lu, "Conduction mechanisms in BaTiO<sub>3</sub> thin films," *Phys. Rev. B, Condens. Matter*, vol. 43, pp. 14261–14264, Jun. 1991, doi: 10.1103/PhysRevB.43.14261.

- [43] M. Bonmann, A. Vorobiev, J. Stake, and O. Engström, "Effect of oxide traps on channel transport characteristics in graphene field effect transistors," J. Vac. Sci. Technol.B, Nanotechnol. Microelectron., Mater., Process., Meas., Phenomena, vol. 35, no. 1, Jan. 2017, Art. no. 01A115, doi: 10.1116/1.4973904.

- [44] Y. Hsin, W. Tang, and H. Hsu, "Temperature dependence of electron saturation velocity in GaAs measured in InGaP/GaAs HBT using DC and AC approaches," *Solid-State Electron.*, vol. 49, no. 3, pp. 295–300, Mar. 2005, doi: 10.1016/j.sse.2004.10.006.

- [45] L. Dupont, Y. Avenas, and P.-O. Jeannin, "Comparison of junction temperature evaluations in a power IGBT module using an IR camera and three thermosensitive electrical parameters," *IEEE Trans. Ind. Appl.*, vol. 49, no. 4, pp. 1599–1608, Jul. 2013, doi: 10.1109/ tia.2013.2255852.

- [46] M. Asheghi, M. N. Touzelbaev, K. E. Goodson, Y. K. Leung, and S. S. Wong, "Temperature-dependent thermal conductivity of single-crystal silicon layers in SOI substrates," *J. Heat Transf.*, vol. 120, no. 1, pp. 30–36, Feb. 1998, doi: 10.1115/1.2830059.

- [47] A. Balandin, "Thermal properties of graphene, carbon nanotubes and nanostructured carbon materials," *Nature Mater.*, vol. 10, pp. 569–581, Jul. 2011, doi: 10.1038/nmat3064.

- [48] R. Murali, Y. Yang, K. Brenner, T. Beck, and J. D. Meindl, "Breakdown current density of graphene nanoribbons," *Appl. Phys. Lett.*, vol. 94, no. 24, Jun. 2009, Art. no. 243114, doi: 10.1063/1.3147183.

- [49] W. J. Knapp, "Thermal conductivity of nonmetallic single crystals," J. Amer. Ceram. Soc., vol. 26, no. 2, pp. 48–55, 1943, doi: 10.1111/ j.1151-2916.1943.tb15185.x.

- [50] T. Yamane, N. Nagai, S.-I. Katayama, and M. Todoki, "Measurement of thermal conductivity of silicon dioxide thin films using a 3ω method," *J. Appl. Phys.*, vol. 91, no. 12, pp. 9772–9776, 2002, doi: 10. 1063/1.1481958.

- [51] S. Adam, E. H. Hwang, V. M. Galitski, and S. Das Sarma, "A self-consistent theory for graphene transport," *Proc. Nat. Acad. Sci. USA*, vol. 104, no. 47, pp. 18392–18397, 2007, doi: 10.1073/pnas.0704772104.

- [52] P. Barlow, R. Davis, and M. Lazarus, "Negative differential output conductance of self heated power MOSFETs," *IEE Proc. I Solid-State Electron. Devices*, vol. 133, no. 5, pp. 177–179, Oct. 1986, doi: 10. 1049/ip-i-1.1986.0036.

- [53] A. E. Parker and D. A. Root, "Pulse measurements quantify dispersion in PHEMTs," in *Proc. IEEE Conf. URSI Int. Symp. Signals Syst. Electron.*, New York, NY, USA, Oct. 1998, pp. 444–449, doi: 10. 1109/ISSSE.1998.738113.

- [54] W. Wei *et al.*, "Mechanically robust 39 GHz cut-off frequency graphene field effect transistors on flexible substrates," *Nanoscale*, vol. 8, no. 29, pp. 14097–14103, Jul. 2016, doi: 10.1039/c6nr01521b.