IEEE TRANSACTIONS ON ELECTRON DEVICES

# Demonstration of >8-kV GaN HEMTs With CMOS-Compatible Manufacturing on 6-in Sapphire Substrates for Medium-Voltage Applications

Xiangdong Li<sup>®</sup>, *Member, IEEE*, Jie Zhang, Jian Ji, Zhibo Cheng, Junbo Wang, Long Chen<sup>®</sup>, Lezhi Wang<sup>®</sup>, Shuzhen You<sup>®</sup>, Lili Zhai, Qiushuang Li, Yuanhang Zhang, Tong Liu<sup>®</sup>, Zilan Li, Yue Hao<sup>®</sup>, *Senior Member, IEEE*, and Jincheng Zhang<sup>®</sup>, *Member, IEEE*

Abstract - Traditional GaN HEMTs on silicon suffer relatively low lateral and vertical blocking voltages and thick buffers, which impede their use in ≥1.2-kV applications. In this work, the prototypes of 8-kV GaN HEMTs on 6-in sapphire are successfully fabricated using CMOS-compatible processing. An etch-stop nitride layer AIN in the in situ SiN cap precisely defines the gate dielectric thickness. Au-free low-temperature ohmic contact and metal I are achieved by Ti/AlCu/Ti/TiN, and gate metal is achieved by TiN/Ti/AlCu/Ti/TiN, which significantly reduces the material cost. The high mechanical strength of sapphire results in low nonuniformity and well-controlled warpage, enabling the use of a 1.5- $\mu$ m buffer. The fabricated HEMTs with an  $L_{\rm GD}$  of 100  $\mu$ m exhibit a low  $R_{\rm ON}$  of 52  $\Omega$  mm and a stable  $V_{\rm TH}$  of -20 V. Benefiting from high-quality in situ SiN passivation, the dynamic  $R_{ON}$  and  $V_{TH}$  shift are maintained within 2.5% and 10%, respectively. The OFF-state breakdown voltage (BV) is increased beyond 8 kV using a simple device structure with only two field plates. The proposed low-cost and CMOS-compatible 8-kV GaN HEMTs fabricated on 6-in sapphire highlight an extremely simple epitaxy process, lateral device structure, and processing flow. Therefore, they offer great potential for serving future medium-voltage applications.

Manuscript received 7 February 2024; revised 17 March 2024; accepted 17 April 2024. This work was supported by the National Key Research and Development Program of China under Grant 2021YFB3600900. The review of this article was arranged by Editor K. Sheng. (Corresponding authors: Xiangdong Li; Jincheng Zhang.)

Xiangdong Li, Jie Zhang, Jian Ji, Zhibo Cheng, Junbo Wang, Shuzhen You, Lili Zhai, Qiushuang Li, Yuanhang Zhang, Tong Liu, Yue Hao, and Jincheng Zhang are with Guangzhou Wide Bandgap Semiconductor Innovation Center, Guangzhou Institute of Technology, Xidian University, Guangzhou 510555, China, and also with the State Key Laboratory of Wide Bandgap Semiconductor Devices and Integrated Technology and the Key Laboratory of Wide Bandgap Semiconductor Materials and Devices, School of Microelectronics, Xidian University, Xi'an 710071, China (e-mail: xdli@xidian.edu.cn; jchzhang@xidian.edu.cn).

Long Chen, Lezhi Wang, and Zilan Li are with Guangdong Ziener Technology Company Ltd., Guangzhou 510670, China.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2024.3392175.

Digital Object Identifier 10.1109/TED.2024.3392175

Index Terms—6-in sapphire, 8 kV, GaN HEMTs, medium voltage.

# I. INTRODUCTION

▶ AN HEMTs have achieved great success in commercial electronics [1], [2], [3], and their applications have focused mainly on mobile and laptop fast chargers [4], [5]. Since 2023, GaN HEMTs have also been adopted for other consumer applications, such as Class D-Audio devices, e-tools, and home appliances [6]. Interest in GaN for dc-dc converters and on-board chargers (OBCs) is growing, and vendors, such as Transphorm and Texas Instruments, have been qualified for electric vehicles use of such devices. Industrial applications are also expected to accelerate after 2024, as the price is expected to continue to fall. In fact, the medium-voltage power electronics market has an enormous demand for ≥1.2-kV power devices for data centers, electric vehicles, renewable energies, industrial automations, smart grids, and even rail traffic. However, emerging 1.2-kV GaN HEMTs have just been reported [7], [8], and 1.7-, 3.3-, 4.5-, and 6.5-kV products remain in development. In contrast, 1.7-kV SiC MOSFETs [9] have been widely commercialized, and 10-kV prototype SiC MOSFETs [10] have been demonstrated; 10-kV Ga<sub>2</sub>O<sub>3</sub> charge-balance Schottky rectifiers have been realized by a reduced surface field (RESURF) structure based on p-type NiO [11].

To increase the GaN breakdown voltage (BV), GaN vertical devices, mainly including current aperture vertical electron transistors (CAVETs) [12], vertical GaN trench MOSFETs [13], [14], and GaN vertical FinFETs [15], have been widely explored. Regardless of the complex processing flow, the reliability issue persists in the threshold voltage  $V_{\rm TH}$  shift of vertical GaN devices employing gate dielectrics, impeding their application potential [16]. To overcome this gate dielectric problem, Liu et al. [17] successfully fabricated a 1.2-kV-class, 4-A normally off vertical

GaN fin-channel JFET on a GaN substrate with avalanche capability.

GaN superjunction MOSFETs/HEMTs have also been proposed for 5–20-kV utility applications, but related research has been conducted mainly by simulation [18]. Alternatively, polarization superjunction (PSJ) HEMTs were proposed to promote a BV greater than 3 kV by achieving charge balance by engineering the positive and negative polarization charges inherent in the GaN material [19]. A similar p-GaN RESURF structure was adopted to fabricate a 10-kV monolithic-cascode HEMT with an  $L_{\rm GD}$  of 103  $\mu$ m [20]. Furthermore, 10 400-V BV was obtained on HEMTs with an  $L_{\rm GD}$  of 125  $\mu$ m by means of a thick poly-AlN passivation layer [21]. Furthermore, pioneering multidimensional device architectures were proposed to balance  $V_{\rm BD}$  and  $R_{\rm ON}$  [22].

Overall, certain solutions are unsuitable for mass production because of requiring complex epitaxy and processing flows. Additionally, devices on large-scale wafers produced by CMOS-compatible processing have seldom been reported. The nonuniformity, reliability, and manufacturability also require detailed elaboration. GaN-on-sapphire is a feasible solution that has attracted great attention recently for >1200-V applications [7], [20]. Benefiting from the insulating substrate, the buffer vertical leakage path is cut off, and the lateral parasitic leakage channel at the substrate/(Al)GaN interface is also significantly suppressed [23], making GaN-on-sapphire suitable for higher blocking voltages. Although the thermal conductivity of sapphire is only a quarter that of silicon, the total thermal resistance of GaN-on-sapphire, which offers a higher mechanical strength than Si, can be limited by thinning of the sapphire substrate [24].

In this work, the epitaxy and fabrication of 8-kV HEMTs on 6-in sapphire substrates using CMOS-compatible processing are first introduced. Then, the wafer-level nonuniformity is inspected by recording the contactless sheet resistance  $R_{\square}$ , warpage testing, and mapping of the current and  $V_{\rm TH}$ . Then, OFF-state blocking measurements are recorded on devices with various structures. Finally, dynamic performance is explored further.

## II. EPITAXY AND FABRICATION

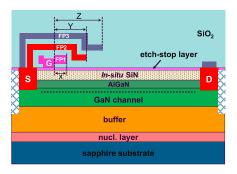

The HEMT structure was epitaxially grown by a metal–organic chemical vapor deposition (MOCVD) system on 6-in sapphire substrates, as shown in Fig. 1. The epitaxy stack consists of a 1-mm sapphire substrate, a 35-nm AlGaN nucleation layer, a 1.5- $\mu$ m GaN buffer layer, a 200-nm GaN channel layer, a 1-nm AlN spacer, a 20-nm Al<sub>0.26</sub>GaN barrier layer, a 50-nm in situ SiN passivation layer, and a 5-nm etch-stop poly-AlN layer, as depicted in Fig. 2. Notably, the 1.5- $\mu$ m GaN buffer layer contains a 0.3- $\mu$ m AlGaN transition layer and a 1.2- $\mu$ m blocking layer to ensure high crystal quality.

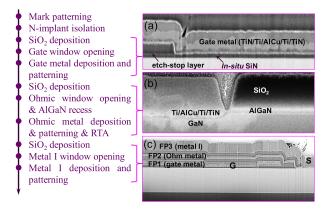

As shown in Fig. 3, CMOS-compatible gate-first manufacturing was initiated by first patterning lithography marks and isolation. The device was isolated through multiple N ion implantation procedures [25].

Then, gate contact was achieved by 150-nm SiO<sub>2</sub> deposition via plasma-enhanced chemical vapor deposition (PECVD),

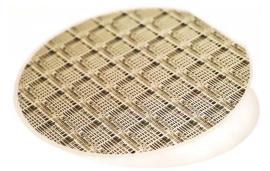

Fig. 1. Photograph of the fabricated 6-in GaN-on-sapphire wafer fabricated by CMOS-compatible processing.

Fig. 2. Cross-sectional schematic of the fabricated GaN HEMTs on a 6-in sapphire.

Fig. 3. Processing flow of the GaN HEMTs on 6-in sapphire, in which the SEM images show the areas of (a) gate, (b) low-temperature ohmic contact, and (c) field plates.

gate window opening via reactive ion etching (RIE), gate metal deposition via physical vapor deposition (PVD), and gate metal patterning via chlorine-based inductively coupled plasma etching (ICP). As shown in Fig. 3(a), the gate metal stack comprises TiN/Ti/AlCu/Ti/TiN (40/20/250/5/30 nm), under which are the 2-nm etch-stop nitride layer and 50-nm in situ SiN dielectric. The etch-stop poly-AlN layer works to terminate RIE etching during gate window opening to guarantee the uniformity of the dielectric thickness and  $V_{\rm TH}$  across the whole 6-in wafer. The etching selectivity between poly-AlN and the dielectric material reaches 15, and the etching gases are CF<sub>4</sub> and CHF<sub>3</sub> with flow rates of 10 and 30 sccm, respectively.

Next, a low-temperature Au-free ohmic contact was fabricated by 260-nm SiO<sub>2</sub> deposition, ohmic contact

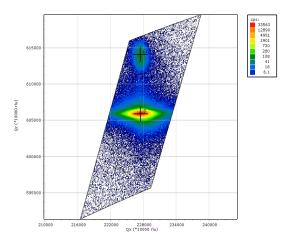

Fig. 4. Measured asymmetric RSM across the (105) plane of the Al<sub>0.25</sub>GaN/GaN heterostructure on sapphire.

window opening, AlGaN recession by ICP, Ti/AlCu/Ti/TiN (5/100/20/60 nm) ohmic metal stack deposition, and rapid thermal annealing at 565 °C for 90 s in the ambient of N<sub>2</sub>. The AlGaN recessing is conducted by etching through the AlGaN barrier layer to the GaN channel, with a recession thickness of 40 nm, as shown in Fig. 3(b), to eliminate the injected fluorine introduced by RIE etching [26].

Finally, metal I was processed by 300-nm SiO<sub>2</sub> deposition, Ti/AlCu/Ti/TiN (8/650/5/30 nm) metal stack deposition, and patterning by ICP etching. As shown in Fig. 3(c), metal I works as the 3rd field plate FP3.

The fabricated HEMTs have a gate width  $W_{\rm G}$  of 100  $\mu$ m, a gate length  $L_{\rm G}$  of 6  $\mu$ m, a gate–source distance  $L_{\rm GS}$  of 1.5  $\mu$ m, and various gate–drain distances  $L_{\rm GD}$  from 22 to 100  $\mu$ m. The dimensions of the field plates by gate metal, ohmic metal, and metal I are denoted as [X, Y, Z]. The electrical characterization was performed by using Keysight B1500A and B1505A.

### III. RESULTS AND DISCUSSION

Fig. 4 shows the reciprocal space mapping (RSM) of the  $Al_{0.25}GaN/GaN$  heterostructure on a 6-in sapphire wafer on which GaN and  $Al_{0.25}GaN$  have been distinguished separately. The aligned x coordinate indicates that the  $Al_{0.25}GaN$  barrier layer is fully strained. Moreover, the clear mapping image also corroborates the simple epitaxy structure in our work.

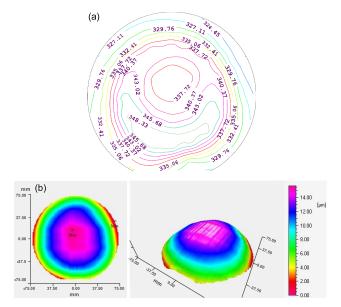

The fabricated 6-in wafer exhibited a well-controlled wafer-level nonuniformity of 2%, as verified by the mapping of the contactless sheet resistance  $R_{\square}$  in Fig. 5(a). Moreover, Fig. 5(b) shows that the warpage of the 6-in GaN-on-sapphire wafer is only 16  $\mu$ m due to the high mechanical strength of the sapphire substrate as well as the dedicated buffer design and processing flow.

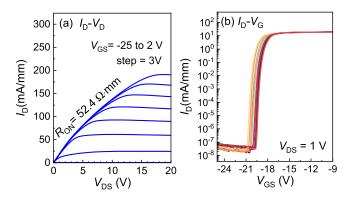

Fig. 6(a) shows the output characteristics of the fabricated GaN HEMTs, for which  $R_{\rm ON}$  reaches 52  $\Omega \cdot$  mm due to the large  $L_{\rm GD}$  of 100  $\mu$ m. It is noticed that  $R_{\rm ON}$  reaches 31.5  $\Omega \cdot$  mm in [20] when using a complex five-channel wafer. Fig. 6(b) shows the transfer characteristics of 18 HEMTs across the wafer. The relatively tight distribution indicates the low nonuniformity of the epitaxy and the in situ SiN under

Fig. 5. (a) Mapping of the contactless sheet resistance  $R_{\square}$  and (b) warpage of the fabricated 6-in GaN-on-sapphire wafer.

Fig. 6. (a) Output and (b) transfer characteristics of GaN HEMTs with an  $L_{\rm GD}$  of 100  $\mu{\rm m}$  on 6-in GaN-on-sapphire.

the gate. The  $V_{\rm TH}$  of -20 V is determined by the dielectric thickness, which can be easily tuned.

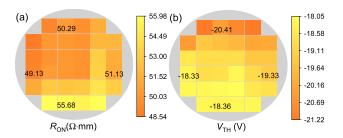

The electrical mapping of  $R_{\rm ON}$  and  $V_{\rm TH}$  was then conducted to verify the uniformity of the 6-in wafer. As shown in Fig. 7, the  $R_{\rm ON}$  values are concentrated in the range of 48.5–56.0  $\Omega \cdot$  mm, and the  $V_{\rm TH}$  values are concentrated in the range from -21.5 to -18.0 V. The existing nonuniformity is attributed to variations in the SiN thickness and the low-temperature Au-free ohmic contact. Overall, the relatively high uniformity of the GaN-on-sapphire wafer ensures the high productivity of devices fabricated using this technique.

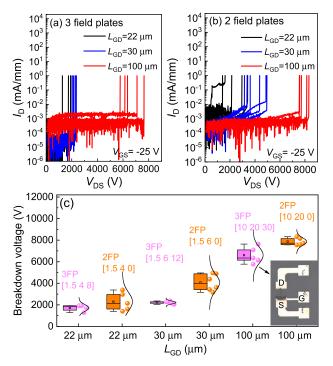

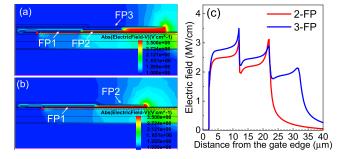

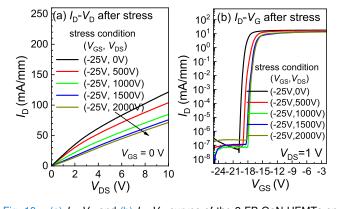

The devices with various structures were then subjected to OFF-state breakdown characterization. Fig. 8(a) and (b) demonstrates the OFF-state breakdown characteristics of the 3-FP and 2-FP HEMTs, respectively. As shown in Fig. 8(c), generally, 2-FP HEMTs with an extremely simplified structure feature a greater blocking capability, for which  $V_{\rm BD}$  reaches 8 kV with an  $L_{\rm GD}$  of 100  $\mu$ m. Fig. 9 shows the simulated electric field contours of the 3-FP and 2-FP HEMTs. The electric field crowding effect takes place at the field plate edges. It is demonstrated in Fig. 9(c) that the peak electric field occurs

Fig. 7. Electrical mapping of (a)  $R_{\rm ON}$  and (b)  $V_{\rm TH}$  of the fabricated 6-in GaN-on-sapphire wafer.

Fig. 8. (a) OFF-state breakdown characteristics of (a) 3-FP and (b) 2-FP HEMTs and (c) statistics of the OFF-state breakdown voltages of the HEMTs with various structures on the 6-in GaN-on-sapphire wafer. The inset of (c) shows a microscopy image of the 3-FP HEMTs with an  $L_{\rm GD}$  of 100  $\mu$ m after OFF-state breakdown.

at the gate field plate edge and the 3-FP HEMT inversely suffers a higher electric field under the same drain bias of 8 kV. This effect is attributed to the presence of field plates that extend outward to approach the drain terminal, which jeopardizes the effective  $L_{\rm GD}$ . Therefore, breakdown occurs on the field plates rather than at the gate. This phenomenon has also been observed by Saito et al. [27], [28]. This indicates that for kV-HEMTs, the length of their field plates should be limited to avoid any early failure. If not so, the dielectric under field plates should be thick enough. This hypothesis is verified by the microscopy image of the failed 3-FP HEMTs in the inset of Fig. 8(c), where we can clearly see that failure occurs between the field plate and the drain terminal.

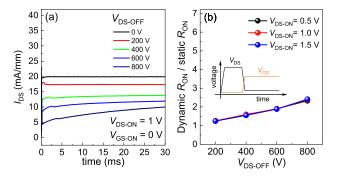

High-voltage OFF-state stress was subsequently applied on the HEMTs with an  $L_{\rm GD}$  of 100  $\mu{\rm m}$  to probe the dynamic stability. During the measurements, the device was first stressed for 1 s in the OFF-state and then quickly subjected to  $I_{\rm D}-V_{\rm D}$  and  $I_{\rm D}-V_{\rm G}$  measurements. Fig. 10(a) shows that the current collapse worsens as the stress voltage increases but gradually saturates after 1500-V stress. Saturation can also be observed

Fig. 9. Simulated electric field contours of (a) 3-FP HEMT and (b) 2-FP HEMT, and the electric field distribution of the two devices along the cutline in (a) and (b).

Fig. 10. (a)  $I_D$ – $V_D$  and (b)  $I_D$ – $V_G$  curves of the 2-FP GaN HEMTs on sapphire with an  $L_{GD}$  of 100  $\mu$ m after various OFF-state stresses.

Fig. 11. (a) Transient current and (b) dynamic  $R_{\rm ON}$  after high-voltage pulse stress by Keysight N1267A.

in Fig. 10(b), where the  $V_{\rm TH}$  shift saturates after the 1000-V stress. The stabilities of the high-quality GaN epitaxy and the in situ SiN dielectric are thereby confirmed. Other passivation strategies, such as LPCVD SiN [29] and Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> [30], are also widely adopted in commercial devices. Recently, Wu et al. [31], [32] presented a promising structure of actively passivated p-GaN gate HEMTs to further reduce the dynamic  $R_{\rm ON}$ .

Dynamic  $R_{\rm ON}$  of the HEMTs was then subjected to high-voltage pulse stress by Keysight N1267A. As shown in the inset of Fig. 11(b), this is actually a hard-switching setup that can strictly assess the dynamic performance, and the relaxation time between the stress and current recording is 200  $\mu$ s. The dynamic  $R_{\rm ON}$  is kept within 2.5 till 800-V stress.

# IV. CONCLUSION

An 8-kV 6-in GaN-on-sapphire wafer, which has the potential to be a breakthrough solution for the medium-voltage

power electronics market, was successfully demonstrated using our pilot line. The CMOS-compatible processing in this work verifies the feasibility of mass production of these wafers using the existing chip fabs. Moreover, the etch-stop nitride layer and in situ SiN dielectric guarantee high uniformity across the whole wafer. The remarkably simple epitaxy process and device structures, together with the use of large-scale and low-cost GaN-on-sapphire wafers, are potential to facilitate the realization of broader GaN applications in the market.

### REFERENCES

- K. Hoo Teo et al., "Emerging GaN technologies for power, RF, digital, and quantum computing applications: Recent advances and prospects," J. Appl. Phys., vol. 130, no. 16, Oct. 2021, Art. no. 160902, doi: 10.1063/5.0061555.

- [2] J. P. Kozak et al., "Stability, reliability, and robustness of GaN power devices: A review," *IEEE Trans. Power Electron.*, vol. 38, no. 7, pp. 1–31, Jul. 2023, doi: 10.1109/TPEL.2023.3266365.

- [3] K. J. Chen et al., "GaN-on-Si power technology: Devices and applications," *IEEE Trans. Electron Devices*, vol. 64, no. 3, pp. 779–795, Mar. 2017, doi: 10.1109/TED.2017.2657579.

- [4] Infineon. (2018). IGO60R070D1 Datasheet. [Online]. Available: https://www.infineon.com

- [5] GaN Systems. (2017). GS66502B Datasheet. [Online]. Available: http://www.gansystems.com

- [6] Efficient Power Conversion. (2019). EPC2019 Datasheet. [Online]. Available: https://epc-co.com/epc

- [7] G. Gupta et al., "1200 V GaN switches on sapphire substrate," in *Proc. Int. Symp. Power Semiconductor Devices ICs*, Vancouver, BC, Canada, May 2022, pp. 349–352, doi: 10.1109/ISPSD49238.2022.9813640.

- [8] Power Integrations. (2023). InnoSwitch3-AQ Family Datasheet. [Online]. Available: https://www.powerint.cn/company?langcode=en

- [9] Wolfspeed. (2022). C2M0045170D Datasheet. [Online]. Available: https://www.wolfspeed.com

- [10] J. Wang et al., "Characterization, modeling, and application of 10-kV SiC MOSFET," *IEEE Trans. Electron Devices*, vol. 55, no. 8, pp. 1798–1806, Aug. 2008, doi: 10.1109/TED.2008. 926650.

- [11] Y. Qin et al., "10 kV Ga<sub>2</sub>O<sub>3</sub> charge-balance Schottky rectifier operational at 200 °C," *IEEE Electron Device Lett.*, vol. 4, no. 8, pp. 1268–1271, Aug. 2023, doi: 10.1109/LED.2023.3287887.

- [12] D. Ji et al., "Normally OFF trench CAVET with active Mg-doped GaN as current blocking layer," *IEEE Trans. Electron Devices*, vol. 64, no. 3, pp. 805–808, Mar. 2017, doi: 10.1109/TED.2016.2632150.

- [13] H. Otake, K. Chikamatsu, A. Yamaguchi, T. Fujishima, and H. Ohta, "Vertical GaN-based trench gate metal oxide semiconductor fieldeffect transistors on GaN bulk substrates," *Appl. Phys. Exp.*, vol. 1, no. 1, Jan. 2008, Art. no. 011105, doi: 10.1143/apex.1. 011105.

- [14] R. A. Khadar, C. Liu, R. Soleimanzadeh, and E. Matioli, "Fully vertical GaN-on-Si power MOSFETs," *IEEE Electron Device Lett.*, vol. 40, no. 3, pp. 443–446, Mar. 2019, doi: 10.1109/LED.2019. 2894177.

- [15] Y. Zhang et al., "Large-area 1.2-kV GaN vertical power FinFETs with a record switching figure of merit," *IEEE Electron Device Lett.*, vol. 40, no. 1, pp. 75–78, Jan. 2019, doi: 10.1109/LED.2018.2880306.

- [16] K. Mukherjee et al., "Analysis of threshold voltage instabilities in semi-vertical GaN-on-Si FETs," Appl. Phys. Exp., vol. 13, no. 2, Jan. 2020, Art. no. 024004, doi: 10.35848/1882-0786/ab6ddd.

- [17] J. Liu et al., "1.2 kV vertical GaN fin JFETs with robust avalanche and fast switching capabilities," in *IEDM Tech. Dig.*, Dec. 2020, pp. 23.2.1–23.2.4, doi: 10.1109/IEDM13553.2020.9372048.

- [18] Z. Li and T. P. Chow, "Design and simulation of 5–20-kV GaN enhancement-mode vertical superjunction HEMT," *IEEE Trans. Electron Devices*, vol. 60, no. 10, pp. 3230–3237, Oct. 2013, doi: 10.1109/TED.2013.2266544.

- [19] H. Kawai et al., "Low cost high voltage GaN polarization superjunction field effect transistors," *Phys. Status Solidi A*, vol. 214, no. 8, Aug. 2017, Art. no. 1600834, doi: 10.1002/pssa.201600834.

- [20] M. Xiao et al., "Multi-channel monolithic-cascode HEMT (MC2-HEMT): A new GaN power switch up to 10 kV," in *IEDM Tech. Dig.*, Dec. 2021, pp. 5.5.1–5.5.4, doi: 10.1109/IEDM19574.2021.9720714.

- [21] M. Yanagihara, Y. Uemoto, T. Ueda, T. Tanaka, and D. Ueda, "Recent advances in GaN transistors for future emerging applications," *Phys. Status Solidi A*, vol. 206, no. 6, pp. 1221–1227, Jun. 2009, doi: 10.1002/pssa.200880968.

- [22] Y. Zhang, F. Udrea, and H. Wang, "Multidimensional device architectures for efficient power electronics," *Nature Electron.*, vol. 5, no. 11, pp. 723–734, Nov. 2022, doi: 10.1038/s41928-022-00860-5.

- [23] X. Li et al., "1700 V high-performance GaN HEMTs on 6-inch sapphire with 1.5  $\mu$ m thin buffer," *IEEE Electron Device Lett.*, vol. 45, no. 1, pp. 84–87, Jan. 2024, doi: 10.1109/LED.2023.3335393.

- [24] Power Integrations. (2022). *InnoSwitch3-CE Family Datasheet*. [Online]. Available: http://www.innoswitch3-ce\_family\_data

- [25] C. F. Lo et al., "Isolation blocking voltage of nitrogen ionimplanted AlGaN/GaN high electron mobility transistor structure," *Appl. Phys. Lett.*, vol. 97, no. 26, Dec. 2010, Art. no. 262116, doi: 10.1063/1.3533381.

- [26] Y. Wang et al., "Effects of fluorine plasma treatment on Au-free ohmic contacts to ultrathin-barrier AlGaN/GaN heterostructure," *IEEE Trans. Electron Devices*, vol. 66, no. 7, pp. 2932–2936, Jul. 2019, doi: 10.1109/TED.2019.2916997.

- [27] W. Saito et al., "High breakdown voltage AlGaN-GaN power-HEMT design and high current density switching behavior," *IEEE Trans. Electron Devices*, vol. 50, no. 12, pp. 2528–2531, Dec. 2003, doi: 10.1109/TED.2003.819248.

- [28] W. Saito, M. Kuraguchi, Y. Takada, K. Tsuda, I. Omura, and T. Ogura, "Design optimization of high breakdown voltage AlGaN/GaN power HEMT on an insulating substrate for R<sub>ON</sub>A-V<sub>B</sub> tradeoff characteristics," *IEEE Trans. Electron Devices*, vol. 52, no. 2, pp. 106–111, Feb. 2005, doi: 10.1109/TED.2004.841338.

- [29] Y. Shi et al., "Normally OFF GaN-on-Si MIS-HEMTs fabricated with LPCVD-SiN<sub>x</sub> passivation and high-temperature gate recess," *IEEE Trans. Electron Devices*, vol. 63, no. 2, pp. 614–619, Feb. 2016, doi: 10.1109/TED.2015.2510630.

- [30] N. E. Posthuma et al., "An industry-ready 200 mm p-GaN E-mode GaN-on-Si power technology," in *Proc. IEEE 30th Int. Symp. Power Semiconductor Devices ICs (ISPSD)*, Chicago, IL, USA, May 2018, pp. 284–287, doi: 10.1109/ISPSD.2018.8393658.

- [31] Y. Wu et al., "An actively-passivated p-GaN gate HEMT with screening effect against surface traps," *IEEE Electron Device Lett.*, vol. 44, no. 1, pp. 25–28, Jan. 2023, doi: 10.1109/LED.2022. 3222170.

- [32] J. Cui et al., "Demonstration of 1200-V E-mode GaN-on-sapphire power transistor with low dynamic ON-resistance based on active passivation technique," *IEEE Electron Device Lett.*, vol. 45, no. 2, pp. 220–223, Feb. 2024, doi: 10.1109/LED.2023.3341413.