# Effects of Electron Quantum Confinement on Velocity Overshoot in Si Nanosheet Gate-All-Around FETs

Junichi Hattori<sup>®</sup>, Koichi Fukuda<sup>®</sup>, *Member, IEEE*, Tsutomu Ikegami<sup>®</sup>, and Yoshihiro Hayashi<sup>®</sup>, *Member, IEEE*

Abstract—We study the relationship between velocity overshoot (VO) and guantum confinement (QC) in electron transport in Si nanosheet (NS) gate-all-around (GAA) fieldeffect transistors (FETs) through device simulation. VO is incorporated into the simulation with an energy transport (ET) model, and QC with a density-gradient (DG) model. We measure the effects of VO on the NS FETs by comparing their static characteristics obtained with the ET model and with a drift-diffusion (DD) model, which essentially cannot consider VO, and then examine the differences in the VO effects between the cases with and without QC. VO increases the drain current, and QC enhances this increase by gathering electrons inside the NS. This enhancement increases as the gate length decreases, although it eventually begins to decrease. It also generally increases as the gate voltage decreases. However, it shows a more complex behavior for a change in NS thickness, depending on the gate length and gate voltage. These behaviors of the VO effect enhancement by QC can be well explained from the effective potential acting on electrons in the NS.

Index Terms—Device simulation, gate-all-around (GAA), nanosheet (NS) field-effect transistor (FET), quantum confinement, technology computer-aided design (TCAD), velocity overshoot.

#### I. INTRODUCTION

**T**ECHNOLOGICAL and industrial development of artificial intelligence is gaining momentum, with chatbot software based on large language models becoming popular in a significantly short period, and the demand for computational resources is expected to continue to grow. Processors and memories, representatives of physical computational resources, have continuously achieved a higher performance by miniaturizing components, such as transistors, and integrating them in larger numbers on a chip. Si nanosheet (NS) gate-all-around (GAA) field-effect transistor (FET), in

Manuscript received 8 March 2024; accepted 9 April 2024. Date of publication 29 April 2024; date of current version 23 May 2024. This work was supported by the New Energy and Industrial Technology Development Organization (NEDO) under Grant JPNP20017 for the Research and Development Project of the Enhanced Infrastructures for Post-5G Information and Communication Systems. The review of this article was arranged by Editor J. Mateos. *(Corresponding author: Junichi Hattori.)*

The authors are with the National Institute of Advanced Industrial Science and Technology (AIST), Tsukuba 305-8568, Japan (e-mail: j.hattori@aist.go.jp).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2024.3389633.

Digital Object Identifier 10.1109/TED.2024.3389633

which Si NSs are used as channels with their sides covered with gate metal, is expected to be fabricated with scaled dimensions compared with Si fin FET, the current mainstream transistor for logic ICs, owing to its higher gate controllability over the potential in channels [2], [3], [4]. If this miniaturization can be achieved, NS FET-based ICs are expected to be superior to fin FET-based ICs in terms of not only area but also speed and power consumption [5], [6]. The NS FET also offers more flexibility in terms of effective gate width, which is advantageous in the design of ICs [7], [8]. For these reasons, it has been chosen as the successor to the fin FET and its research and development is being vigorously pursued to bring its products to market [9], [10], [11]. To this end, a detailed understanding of carrier transport in the NS FET is essential, which can be achieved with device simulation.

Carriers accelerated by a strong electric field can temporarily exceed their saturation velocity [12], [13], [14]. This phenomenon is known as velocity overshoot (VO) and is considered to affect the performance of FETs when the gate length is short. In this situation, ballistic transport is also considered to occur, in which carriers pass through a channel without experiencing scattering. As scattering sources such as phonons are always present, in reality, most of the carriers would be scattered even if only a few times, and the carrier transport would not be purely ballistic but quasi-ballistic. The carrier transport we assume in this study is such that carriers are not scattered frequently enough for their overshot velocity to settle down to the saturation velocity, which situation is similar to that in the quasi-ballistic transport. In fact, the previous study [15] has pointed out that VO can occur in quasiballistic transport. In addition, when carriers are confined to a narrow space, their quantum-mechanical behavior becomes pronounced. A typical example observed in FETs is that, at high gate voltages, the carrier density peak is slightly away from the semiconductor-insulator interface where the peak should be located according to classical mechanics [16]. This phenomenon is known as a quantum confinement (QC) effect. Both VO and QC will definitely affect the performance of NS FETs. Most device simulators can incorporate VO into the simulations with an energy transport (ET) model, commonly referred to as a hydrodynamic model, and QC with a quantum correction model such as a density-gradient (DG) model. Such simulations have been widely performed for various types of FETs, including NS FETs [17], [18], [19]. However, the interaction between VO and QC is not yet fully understood.

© 2024 The Authors. This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 License. For more information, see https://creativecommons.org/licenses/by-nc-nd/4.0/

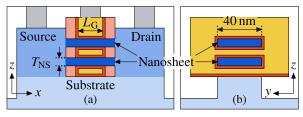

Fig. 1. Sectional views of Si NS GAA FETs along (a) the *x*-axis and (b) the *y*-axis, parallel to the gate length and width directions, respectively.

In this study, we investigate the effects of QC on VO in electron transport in Si NS GAA FETs using device simulation. To this end, we measure the effects of VO on device performance by comparing the static characteristics of the NS FETs obtained with and without the consideration of VO, and then examine how much the VO effects change depending on the presence or absence of QC. Although we have already demonstrated such changes in our previous work [20], here, we discuss them in detail along with their causes. The findings of this study will improve our understanding of electron transport not only in NS FETs but also in other ultrascaled FETs.

## **II. SIMULATION FRAMEWORK**

We employed the ET and DG models to incorporate VO and QC into the simulation, respectively. Although the two models are well known, their forms differ among device simulators. To clarify the forms and facilitate the discussion of the simulation results, we describe the two models below, as well as the device structure considered and the simulator used in this study.

#### A. Device Structure

Fig. 1 illustrates the structure of Si NS GAA FETs with a gate length of  $L_{\rm G}$ . Each FET comprises two Si NSs with a thickness of  $T_{\rm NS}$  and width of 40 nm, gate insulating films with a thickness of 2 nm and relative permittivity  $\varepsilon_{\rm OX}$  of 7.8, and gate sidewalls with a thickness of 5 nm and relative permittivity of 5.0. Thus, the NS length is 14 nm longer than  $L_{\rm G}$ . Moreover, the spacing between the two NSs and that between the lower NS and the substrate are 10 nm. In this study, the NS FETs were assumed to be of n-type. The donor concentration was  $N_{\rm SD}$  in the source/drain and decreased away from there according to a Gaussian distribution with a standard deviation of 3 nm. The substrate was doped with acceptors at a concentration of  $1 \times 10^{18}$  cm<sup>-3</sup> to weaken parasitic transistors. In addition, we set  $N_{\rm SD}$  to  $1 \times 10^{20}$  cm<sup>-3</sup>, the gate metal work function to 4.6 eV, and the supply voltage to 0.65 V.

#### B. Velocity Overshoot

The overshoot of carrier velocity in Si involves the energy dependence of carrier scattering [15]. In device simulation, carrier transport in semiconductors is usually described by a drift–diffusion (DD) model consisting of Poisson and current continuity equations. The DD model provides information on the number of carriers but not the energy. We therefore solved the following energy balance equation for electrons [21]:

$$\partial nw/\partial t + \nabla \cdot \mathbf{S} - \mathbf{J} \cdot \mathbf{\mathcal{E}} - H + n(w - w_0)/\tau_w = 0$$

(1)

where *n* is the electron density, J the current density, *w* the average energy,  $w_0$  its value in thermal equilibrium, *H* the net energy gain rate,  $\tau_w$  the energy relaxation time, and  $\mathcal{E}$  the electric field. When only the thermal energy is considered, *w* and  $w_0$  are approximated with  $(3/2)k_BT$  and  $(3/2)k_BT_{dev}$ , where *T* and  $T_{dev}$  are the electron and device temperatures, respectively. Moreover, the energy flux density *S* is given by

$$\boldsymbol{S} = -(5/2)(\mu_{\boldsymbol{S}}/\mu)(k_{\mathrm{B}}T/q)(\boldsymbol{J} + \mu nk_{\mathrm{B}}\nabla T)$$

(2)

where  $\mu$  and  $\mu_S$  are the electron mobility and its *S*'s counterpart, respectively. The DD model in combination with the energy balance equation is called the ET model. In our simulation, it was applied to electron transport in the NSs and source/drain along with *H* given by [22]

$$H = (3/2)k_{\rm B}TG_{\rm SRH} + [(3/2)k_{\rm B}(T - T_{\rm dev}) - E_{\rm g}]G_{\rm Aug} \quad (3)$$

and  $\tau_w$  given by [23]

$$\tau_w(\omega) = (0.27 + 0.62\omega - 0.63\omega^2 + 0.13\omega^3 + 0.01\omega^4)\tau_{w0}.$$

(4)

Here,  $G_{\text{SRH}}$  and  $G_{\text{Aug}}$  are the net generation rates of electron-hole pairs due to Shockley-Read-Hall and Auger recombinations, respectively;  $E_{\text{g}}$  is the bandgap energy;  $\omega$  is w divided by 1 eV; and  $\tau_{w0}$  is 1 ps. In addition, the mobility ratio  $\mu_S/\mu$  was set to 0.8 [21] and  $T_{\text{dev}}$  to 300 K. In the substrate, by contrast, the DD model was applied to electron transport and T was assumed to be equal to  $T_{\text{dev}}$ . Regarding hole transport, the DD model was used for all regions.

The energy dependence of electron scattering was represented by an energy-dependent mobility model. In the DD model, as a lateral field–dependent mobility model that determines the final value of carrier mobility, the following Caughey–Thomas model [24] was used:

$$\mu = \mu_{\text{low}} \left[ 1 + (\mu_{\text{low}} | \boldsymbol{\mathcal{E}}_{\text{drv}} | / v_{\text{sat}})^b \right]^{-1/b}$$

(5)

where  $\mathcal{E}_{drv}$  is the driving field,  $v_{sat}$  is the carrier saturation velocity,  $\mu_{low}$  is the low-field mobility considering the effects up to the transverse field, and *b* is a fitting parameter. From this driving-field dependence of the carrier mobility, the energy dependence can be derived with the method described in [25]. Solving (1) with assumptions that the system is homogeneous and stationary and H = 0 yields the average energy that an electron will eventually have under a given  $\mathcal{E}_{drv}$  as

$$w(\boldsymbol{\mathcal{E}}_{\rm drv}) = q\,\mu |\boldsymbol{\mathcal{E}}_{\rm drv}|^2 \tau_w + w_0. \tag{6}$$

By eliminating  $\mathcal{E}_{drv}$  from (5) with this equation, we obtained the energy-dependent mobility model for electrons. Note that, if *T* was lower than  $T_{dev}$ ,  $\mu$  was fixed at  $\mu_{low}$ . When an electron under an  $\mathcal{E}_{drv}$  has an energy lower than that given by (6), its velocity can exceed  $v_{sat}$ , that is, VO can occur.

In the DD model, as J can be written as  $J = n\mu\nabla E_{qF}$ with the electron quasi-Fermi level  $E_{qF}$  if T is uniform, for electrons,  $\mathcal{E}_{drv}$  was assumed to be given by  $\mathcal{E}_{drv} = \nabla E_{qF}/q$ . Moreover,  $v_{sat}$  was set to 1.07 × 10<sup>7</sup> cm/s and b to 1.109. Other settings of the DD model have been described in [26]; however, band-to-band tunneling was ignored in this study.

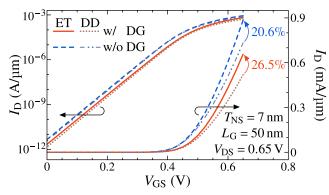

Fig. 2.  $I_D-V_{GS}$  characteristics of NS FETs with an  $L_G$  of 50 nm and  $T_{NS}$  of 7 nm at a  $V_{DS}$  of 0.65 V. The characteristics obtained with both ET and DG models are shown by the solid lines, those obtained with the DD model instead of the ET model by the lines containing dots, and those obtained without the DG model by the lines containing dashes. The values of  $I_D$  are normalized by the NS width, which is 40 nm.

## C. Quantum Confinement

We incorporated electron QC into the simulation with the DG model [27], which introduces the quantum potential

$$U_{\rm QC} = -\left(\hbar^2/6m_{\rm QC}\right)\nabla^2\sqrt{n} / \sqrt{n} \tag{7}$$

for electrons, where  $m_{QC}$  is the electron effective mass related to QC. The quantity  $U_{QC}$  represents the influence of potentials at distant locations and, in practice, acts as a modifier of the conduction band edge  $E_{C}$ . For example, *n* is modified as

$$n = N_{\rm C} \exp\left\{\left[E_{\rm qF} - \left(E_{\rm C} + U_{\rm QC}\right)\right]/k_{\rm B}T\right\}$$

(8)

where  $N_{\rm C}$  is the conduction-band effective density of states.

As with the ET model, the DG model was applied to electrons in the NSs and source/drain. At the Si-insulator interface, the same boundary condition as described in [28] was used and the insulator was assumed to be made of SiO<sub>2</sub>. The boundary condition parameters and  $m_{\rm QC}$  were adjusted so that, for an NS with a  $T_{\rm NS}$  of 7 nm, the profile of *n* along the central axis in the  $T_{\rm NS}$ -direction is close to that obtained from a one-dimensional Schrödinger–Poisson equation. Then,  $m_{\rm QC}$  was determined to be  $0.14m_0$  for Si and  $0.08m_0$  for SiO<sub>2</sub>. The latter value is required for the boundary condition. At the interface of the source/drain with the substrate and electrodes,  $U_{\rm QC}$  was assumed to be zero.

## D. Device Simulator

We used our homemade device simulator, Impulse TCAD [29], to simulate NS FETs. Although Impulse TCAD solves equations with the Newton method, it automatically calculates the Jacobians of the equations at run time. Thanks to this feature, users can easily incorporate their own models into simulations without providing the models' Jacobians, and besides through simulation control scripts without hard coding the models. In this way, we incorporated the ET and DG models into the simulation. Both models are widely used; however, they have limitations [21], [30]. To verify our simulation framework, including the models' validity, we simulated the three-layer NS FET with an  $L_G$  of 12 nm and  $T_{NS}$  of 5 nm [9]. The simulation results were found to be in reasonable agreement with the experimental data on drain

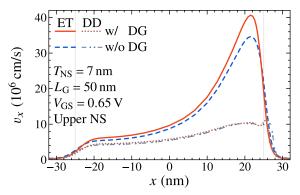

Fig. 3. Electron velocity in the *x*-direction  $v_x$  in the upper NS at a  $V_{GS}$  of 0.65 V. It is plotted along the *x*-axis after being averaged over each section with a weight of *n*.

current  $I_{\rm D}$  versus gate-to-source voltage  $V_{\rm GS}$  characteristics under assumptions that  $\varepsilon_{\rm OX}$  is 9.0 and  $N_{\rm SD}$  is  $6 \times 10^{19} \,{\rm cm}^{-3}$ . Furthermore, no serious problems were observed that could be attributed to the models' limitations. Note that the unit of the experimental  $I_{\rm D}$  was assumed to be  $10^{-2} \,{\rm A}/\mu{\rm m}$  [19] because it is not specified.

### III. RESULTS AND DISCUSSION

We simulated the Si NS GAA FETs shown in Fig. 1 and measured the effects of VO on them by comparing their static characteristics obtained with the ET model and with the DD model, and then examined how much the VO effects change depending on the application or non-application of the DG model, that is, the presence or absence of QC.

# A. VO and QC Effects on Device Performance

Fig. 2 shows the  $I_{\rm D}-V_{\rm GS}$  characteristics of NS FETs with an  $L_{\rm G}$  of 50 nm and  $T_{\rm NS}$  of 7 nm at a drain-to-source voltage  $V_{\rm DS}$ of 0.65 V. The characteristics obtained when the ET and DG models were applied to electrons in the NSs and source/drain are shown by the solid lines, those obtained with the DD model instead of the ET model by the lines containing dots, and those obtained without the DG model by the lines containing dashes. Comparing the characteristics obtained with the ET model and with the DD model, we see that the ET model produces a larger  $I_{\rm D}$ . This is because the ET model reproduces VO as shown in Fig. 3, where the electron velocity v in the upper NS is plotted in the  $L_{G}$ -direction. The velocity is limited to  $v_{sat}$  in the DD model, whereas it exceeds  $v_{sat}$  in the ET model. This VO leads to an increase in  $I_{\rm D}$ . Note that, in the ET model, a diffusion current due to the gradient of T flows, which is not considered in the DD model. This current was found to contribute much less to  $I_{\rm D}$  than the drift current and the diffusion current due to the gradient of n. Furthermore, it carried electrons from the hot drain to the cold source and decreased  $I_{\rm D}$ . Therefore, the larger  $I_{\rm D}$  in the ET model than in the DD model is entirely due to VO.

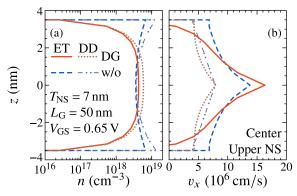

Comparing the  $I_D-V_{GS}$  characteristics obtained with and without the DG model, we see that QC decreases  $I_D$ . As shown in Fig. 4(a), QC moves electrons away from the surface in an NS, which degrades the effective capacitance of the gate insulating film. Consequently, the number of electrons induced by a given  $V_{GS}$  decreases, and  $I_D$  also decreases.

Fig. 4. (a) n and (b)  $v_x$  on the center section of the upper NS. Both quantities are averaged over the width and plotted in the  $T_{NS}$ -direction. In the averaging of  $v_x$ , n is used as a weight.

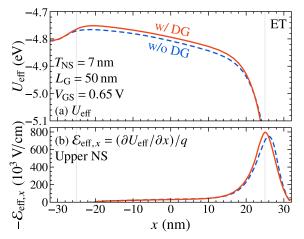

Fig. 5. (a)  $U_{\text{eff}}$  (b)  $\partial U_{\text{eff}}/\partial x$  in terms of the electric field. Both quantities are obtained for the upper NS with the ET model and plotted along the *x*-axis after being averaged over each section with a weight of *n*.

#### B. VO Effect Enhancement by QC

As VO is expected to mitigate the decrease in  $I_D$  due to device miniaturization [12], we focused on the ON-state current  $I_{on}$  and measured the VO effect on it in terms of the difference between the  $I_{on}$ 's obtained with the ET model and with the DD model. As shown in Fig. 2, VO increases  $I_{on}$  by 26.5% with QC while by 20.6% without it, which indicates that QC enhances the VO effect. This enhancement is intuitively explained as follows: first, electrons are more accelerated when they are located more inside an NS, as shown in Fig. 4(b), because the lateral field is stronger owing to a weaker influence of the gate, and furthermore the mobility is higher owing to a weaker effect of the surface; second, QC gathers electrons inside the NS. The more precise reason is discussed below.

Fig. 5 shows the  $L_{\rm G}$ -direction profiles of the effective potential  $U_{\rm eff}$  and lateral field acting on electrons as obtained for the upper NS with the ET model, where  $U_{\rm eff}$  considers  $U_{\rm QC}$  and is given by  $U_{\rm eff} = E_{\rm C} + U_{\rm QC}$ . In an NS, when electrons are farther away from the surface,  $U_{\rm eff}$  is higher and its drop between the NS and the drain is larger, which is of course the case when  $V_{\rm GS}$  is higher than the flat-band voltage. In addition, as the gate influence on  $U_{\rm eff}$  is weaker, the drain influence extends deeper into the NS. As a result, the lateral field near the drain is stronger in the case with QC than in the case without it.

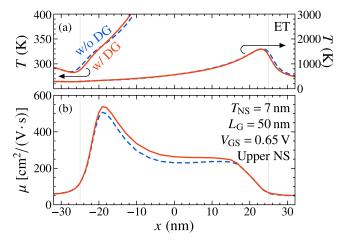

Fig. 6. x-axis profiles of (a) T and (b)  $\mu$ . Both quantities are obtained for the upper NS with the ET model and averaged over each section with a weight of *n*.

Furthermore, as electrons move away from the surface, the surface scattering becomes less effective and  $\mu_{low}$  increases. The final mobility,  $\mu$ , decreases from  $\mu_{\text{low}}$  with w in the ET model. Overall, there is little difference in w, and hence  $\mu$  is higher in the case with QC, as shown in Fig. 6. In the figure, w is converted to T according to the relation,  $w = (3/2)k_{\rm B}T$ . Before reaching the potential barrier top, in the case with QC, electrons clime a higher barrier and lose more energy, resulting in a lower w. This lowering contributes to the higher  $\mu$  and to the fact that the v in the case with QC exceeds that in the case without it. Then, as the electrons approach the drain, they are more accelerated by the higher  $\mu$  and stronger lateral field. As a result, the difference in v between the two cases increases. In the DD model, however, there is no such difference because  $\mu$  decreases with increasing  $\mu_{low}$  and  $\mathcal{E}_{drv}$ , as seen from (5), and besides v is eventually limited to  $v_{sat}$ . Therefore, the difference in v observed in the ET model directly related to the difference in the VO effects on device performance, and the relative increase in  $I_{on}$  due to VO is higher in the case with QC than in the case without it. A simple explanation for these two points is provided below. First, let us represent the VO effect on  $I_D$  by the ratio  $\alpha$  of the  $I_D$  density obtained with the ET model,  $J^{ET} = -qn^{ET}v^{ET}$ , to that obtained with the DD model,  $J^{DD} = -qn^{DD}v^{DD}$ , and next, the  $\alpha$  in the case with QC by  $\alpha_{QC} = J_{QC}^{ET}/J_{QC}^{DD} = n_{QC}^{ET}v_{QC}^{ET}/n_{QC}^{DD}v_{QC}^{DD}$  and that in the case without QC by  $\alpha_0 = J_0^{ET}/J_0^{DD} = n_0^{ET}v_0^{ET}/n_0^{DD}v_0^{DD}$ . Then, the ratio of the two  $\alpha$ 's,  $\beta = \alpha_{\rm QC}/\alpha_0$ , indicates how much QC affects the VO effect. As  $v_{\rm QC}^{\rm DD} \approx v_0^{\rm DD}$ , and also  $n_{\rm QC}^{\rm ET}/n_{\rm QC}^{\rm DD} \approx n_0^{\rm ET}/n_0^{\rm DD}$  from Fig. 4(a),  $\beta$  can be approximated as  $\beta \approx v_{\rm QC}^{\rm ET}/v_0^{\rm ET}$ . As discussed above,  $v_{\rm QC}^{\rm ET}/v_0^{\rm ET} > 1$ ; therefore,  $\beta > 1$ , that is, QC enhances the VO effect on  $I_{\rm D}$ .

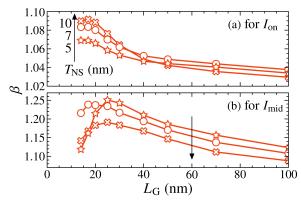

# C. L<sub>G</sub>, T<sub>NS</sub>, and V<sub>GS</sub> Dependences of the Enhancement

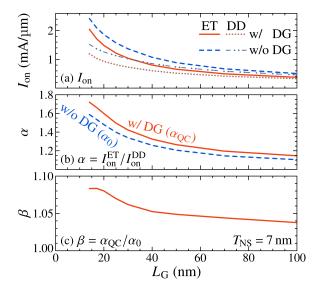

As described in Section III-B, QC enhances the VO effects on device performance through the extension of the drain influence on  $U_{\text{eff}}$  deep into an NS. As  $L_{\text{G}}$  becomes shorter, the proportion of the region influenced by the drain in the NS increases, and therefore the enhancement is expected to become larger. Fig. 7 shows  $I_{\text{on}}$  and its  $\alpha$  and  $\beta$  as functions of  $L_{\text{G}}$ . As expected,  $\beta$  increases with shortening  $L_{\text{G}}$ . However,

Fig. 7. (a)  $I_{on}$  and [(b) and (c)] its  $\alpha$  and  $\beta$  as functions of  $L_{G}$ .

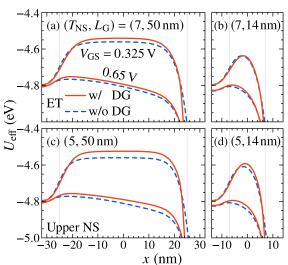

Fig. 8. x-axis profiles of  $U_{\rm eff}$  in the upper NS at  $V_{\rm GS}$ 's of 0.65 and 0.325 V. The values of  $U_{\rm eff}$  are obtained for  $(T_{\rm NS}, L_{\rm G})$ -pairs of (a) (7, 50 nm), (b) (7, 14 nm), (c) (5, 50 nm), and (d) (5, 14 nm) with the ET model and averaged over each section with a weight of *n*.

when  $L_{\rm G}$  becomes significantly short, less than 17 nm,  $\beta$  begins to decrease. This is because a rise in  $U_{\rm eff}$ , another factor enhancing the VO effects, is suppressed by the extended drain influence, as shown in Fig. 8(b). Fig. 8 shows the  $L_{\rm G}$ -direction profiles of  $U_{\rm eff}$  in the upper NS for  $L_{\rm G}$ 's of 50 and 14 nm,  $T_{\rm NS}$ 's of 7 and 5 nm, and  $V_{\rm GS}$ 's of 0.65 and 0.325 V.

We also examined the VO effect enhancement by QC for its dependence on  $T_{\rm NS}$ . Fig. 9(a) shows  $\beta$  as a function of  $L_{\rm G}$  for  $T_{\rm NS}$ 's of 5 and 10 nm as well as 7 nm. Although QC becomes stronger with thinning  $T_{\rm NS}$ ,  $\beta$  is lower when  $T_{\rm NS}$ is 5 nm than 7 nm. As electrons approach the drain in an NS, their velocity increases, while their number decreases to maintain current continuity. Accordingly, the electrons gather more inside the NS in the case with QC. This is because, if they are close to equilibrium, their population in the ground subband relatively increases, which can be reproduced by the DG model. In reality, however, they would be in nonequilibrium near the drain. It is therefore necessary to verify whether the scattering of them to the ground subband is

Fig. 9.  $\beta$ 's for (a)  $l_{on}$  and (b)  $l_{mid}$  and for different  $T_{NS}$ 's of 5, 7, and 10 nm, plotted as functions of  $L_{G}$ .

sufficient, although optical phonon scattering becomes more frequent as their energy increases. This verification is beyond the scope of this study. For now, let us consider the simulation result that electrons gather more inside an NS as they approach the drain, which acts to raise  $U_{eff}$  gradually and weaken the lateral field as opposed to the drain influence extension. When  $T_{NS}$  is 5 nm,  $\beta$  is not at its highest because, as shown in Fig. 8(c), this negative contribution is large. When  $T_{NS}$  is 10 nm,  $\beta$  is expected to be at its lowest because of the weakest QC. However, the opposite occurs when  $L_G$  is short, approximately 30 nm or lower. This is because, as the gate can no longer sufficiently control  $U_{eff}$ , the drain influence extended by QC significantly impacts  $I_{on}$ .

Finally, we discuss the  $V_{GS}$  dependence of the VO effect enhancement by QC. As  $V_{GS}$  becomes lower, the electrons in an NS decrease in number, and in the case with QC, they gather more inside the NS. As a result,  $U_{\rm eff}$  rises more and its drop near the drain increases more, as seen in Fig. 8(a) and (c). In addition, the extension of the drain influence and the improvement in  $\mu$  also increase more. Thus, the VO effect enhancement becomes larger. Fig. 9(b) shows the  $\beta$  for the  $I_{\rm D}$ at a  $V_{\rm DS}$  of 0.65 V and  $V_{\rm GS}$  of 0.325 V,  $I_{\rm mid}$ . Comparing this  $\beta$ with the  $\beta$  for  $I_{on}$  shown in Fig. 9(a), respectively denoted by  $\beta_{\rm mid}$  and  $\beta_{\rm on}$ , we see that  $\beta_{\rm mid}$  is higher than  $\beta_{\rm on}$ , as expected. Unlike  $\beta_{on}$ , the  $\beta_{mid}$  for a  $T_{NS}$  of 5 nm is the highest among the three  $\beta_{\text{mid}}$ 's for different  $T_{\text{NS}}$ 's when  $L_{\text{G}}$  is long. This is because, at a  $V_{GS}$  of 0.375 V, significantly fewer electrons are present under the gate than at a  $V_{GS}$  of 0.65 V. They are gathered sufficiently inside an NS even on the source side, so that a decrease in their number toward the drain does not weaken the lateral field, as shown in Fig. 8(c). However, as  $L_{\rm G}$  shortens from 25 nm, the  $\beta_{\rm mid}$  for a  $T_{\rm NS}$  of 5 nm decreases sharply. QC extends not only the drain influence but also the source influence on  $U_{\rm eff}$  deep into an NS. The extended source influence moves the potential barrier top toward the drain and shortens the distance over which electrons are accelerated by the lateral field, thereby contributing to a decrease in  $\beta$  at short  $L_{G}$ 's. As can be seen from Fig. 8(b) and (d), in the case where  $T_{\rm NS}$  is 5 nm and  $V_{\rm GS}$  is 0.325 V, as QC basically raises  $U_{\rm eff}$ more, the shortening ratio of the acceleration distance is also higher compared with the cases where  $T_{\rm NS}$  or  $V_{\rm GS}$  is varied. This is the cause of the sharp decrease in the  $\beta_{mid}$  for a  $T_{NS}$ of 5 nm. When  $T_{\rm NS}$  is 10 nm,  $\beta_{\rm mid}$  does not increase rapidly

at short  $L_{\rm G}$ 's, unlike  $\beta_{\rm on}$ . As a lower  $V_{\rm GS}$  raises the potential barrier, the enhancement of the electron diffusion flow toward the barrier top by QC, or an increase in  $\mu$ , is more reflected in  $\beta$ . However, at short  $L_{\rm G}$ 's, the extended source and drain influences degrade the QC-induced barrier rise and hence this increase in  $\mu$ , which slows an increase in  $\beta_{\rm mid}$ . Furthermore, when  $V_{\rm GS}$  is low enough for electrons to gather inside an NS even in the case without QC, the trend for  $\beta$  to increase with lowering  $V_{\rm GS}$  may change; however, such a change was not observed in the  $V_{\rm GS}$  range down to 0 V.

#### **IV. CONCLUSION**

In this study, we performed the device simulation of n-type Si NS GAA FETs while considering VO and QC and investigated how much QC changes the effects of VO on their static characteristics. VO increases the drain current, and QC enhances this increase. This enhancement increases as the gate length becomes shorter, although it eventually begins to decrease. It also generally increases as the gate voltage becomes lower. However, its dependence on the NS thickness is more complex and varies with the gate length and gate voltage. These behaviors of the VO effect enhancement by QC can be fully explained from the effective potential acting on electrons and their mobility in the NS. Furthermore, the gathering of electrons toward the inside of the NS, the most fundamental result of QC, plays a pivotal role in the determination of both these quantities. The findings of this study will be helpful in understanding electron transport in ultrascaled devices, including those other than the NS FETs, and in predicting their performance.

#### REFERENCES

- IEEE (2020). International Roadmap for Devices and Systems 2020 Edition. [Online]. Available: https://irds.ieee.org/topics/semiconductorsandartificial-intelligence

- [2] S.-D. Kim, M. Guillorn, I. Lauer, P. Oldiges, T. Hook, and M.-H. Na, "Performance trade-offs in FinFET and gate-all-around device architectures for 7 nm-node and beyond," in *Proc. IEEE SOI-3D-Subthreshold Microelectron. Technol. Unified Conf. (S3S)*, Oct. 2015, pp. 1–3, doi: 10.1109/S3S.2015.7333521.

- [3] D. Jang et al., "Device exploration of NanoSheet transistors for sub-7-nm technology node," *IEEE Trans. Electron Devices*, vol. 64, no. 6, pp. 2707–2713, Jun. 2017, doi: 10.1109/TED.2017.2695455.

- [4] D. Nagy, G. Espineira, G. Indalecio, A. J. Garcia-Loureiro, K. Kalna, and N. Seoane, "Benchmarking of FinFET, nanosheet, and nanowire FET architectures for future technology nodes," *IEEE Access*, vol. 8, pp. 53196–53202, 2020, doi: 10.1109/ACCESS.2020.2980925.

- [5] A. Veloso et al., "(Invited) innovations in transistor architecture and device connectivity options for advanced logic scaling," *ECS Trans.*, vol. 108, no. 2, pp. 31–42, May 2022, doi: 10.1149/10802.0031ecst.

- [6] L. Wu, "The next generation of gate-all-around transistors," *Nature Electron.*, vol. 6, no. 7, p. 469, Jul. 2023, doi: 10.1038/s41928-023-01006-x.

- [7] J.-S. Yoon, J. Jeong, S. Lee, and R.-H. Baek, "Optimization of nanosheet number and width of multi-stacked nanosheet FETs for sub-7-nm node system on chip applications," *Jpn. J. Appl. Phys.*, vol. 58, Mar. 2019, Art. no. SBBA12, doi: 10.7567/1347-4065/ab0277.

- [8] A. Pal, E. M. Bazizi, B. Colombeau, B. Alexander, and B. Ayyagari-Sangamalli, "Nanosheet width investigation for gateall-around devices targeting SRAM application," in *Proc. Int. Conf. Simul. Semiconductor Processes Devices (SISPAD)*, Sep. 2021, pp. 19–22, doi: 10.1109/SISPAD54002.2021.9592579.

- [9] N. Loubet et al., "Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET," in *Proc. Symp. VLSI Technol.*, Jun. 2017, pp. T230–T231, doi: 10.23919/VLSIT.2017.7998183.

- [10] S. Barraud et al., "Tunability of parasitic channel in gate-all-around stacked nanosheets," in *IEDM Tech. Dig.*, Dec. 2018, pp. 21.3.1–21.3.4, doi: 10.1109/IEDM.2018.8614507.

- [11] C. W. Yeung et al., "Channel geometry impact and narrow sheet effect of stacked nanosheet," in *IEDM Tech. Dig.*, Dec. 2018, pp. 28.6.1–28.6.4, doi: 10.1109/IEDM.2018.8614608.

- [12] G. A. Sai-Halasz, M. R. Wordeman, D. P. Kern, S. Rishton, and E. Ganin, "High transconductance and velocity overshoot in NMOS devices at the 0.1-μm gate-length level," *IEEE Electron Device Lett.*, vol. 9, no. 9, pp. 464–466, Sep. 1988, doi: 10.1109/55.6946.

- [13] G. G. Shahidi, D. A. Antoniadis, and H. I. Smith, "Electron velocity overshoot at room and liquid nitrogen temperatures in silicon inversion layers," *IEEE Electron Device Lett.*, vol. 9, no. 2, pp. 94–96, Feb. 1988, doi: 10.1109/55.2051.

- [14] T. Mizuno and R. Ohba, "Experimental study of nonstationary electron transport in sub-0.1 μm metal–oxide–silicon devices: Velocity overshoot and its degradation mechanism," J. Appl. Phys., vol. 82, no. 10, pp. 5235–5240, Nov. 1997, doi: 10.1063/1.366389.

- [15] S. L. Teitel and J. W. Wilkins, "Ballistic transport and velocity overshoot in semiconductors: Part I—Uniform field effects," *IEEE Trans. Electron Devices*, vol. ED-30, no. 2, pp. 150–153, Feb. 1983, doi: 10.1109/T-ED.1983.21088.

- [16] F. Stern, "Quantum properties of surface space-charge layers," CRC Crit. Rev. Solid State Sci., vol. 4, nos. 1–4, pp. 499–514, Dec. 1973, doi: 10.1080/10408437308245840.

- [17] L. Cai, W. Chen, G. Du, X. Zhang, and X. Liu, "Layout design correlated with self-heating effect in stacked nanosheet transistors," *IEEE Trans. Electron Devices*, vol. 65, no. 6, pp. 2647–2653, Jun. 2018, doi: 10.1109/TED.2018.2825498.

- [18] Y. Lee et al., "Design study of the gate-all-around silicon nanosheet MOSFETs," *Semicond. Sci. Technol.*, vol. 35, no. 3, Feb. 2020, Art. no. 03LT01, doi: 10.1088/1361-6641/ab6bab.

- [19] D. Ryu et al., "Design and optimization of triple-k spacer structure in two-stack nanosheet FET from off-state leakage perspective," *IEEE Trans. Electron Devices*, vol. 67, no. 3, pp. 1317–1322, Mar. 2020, doi: 10.1109/TED.2020.2969445.

- [20] J. Hattori, K. Fukuda, T. Ikegami, and Y. Hayashi, "Relationship between electron velocity overshoot and quantum confinement in Si nanosheet gate-all-around field-effect transistors," in *Proc. Extended Abstr. Int. Conf. Solid State Devices Mater.*, Sep. 2023, pp. 497–498, doi: 10.7567/ssdm.2023.f-1-07.

- [21] T. Grasser, T.-W. Tang, H. Kosina, and S. Selberherr, "A review of hydrodynamic and energy-transport models for semiconductor device simulation," *Proc. IEEE*, vol. 91, no. 2, pp. 251–274, Feb. 2003, doi: 10.1109/JPROC.2002.808150.

- [22] D. Chen, Z. Yu, K.-C. Wu, R. Goossens, and R. W. Dutton, "Dual energy transport model with coupled lattice and carrier temperatures," in *Proc. Int. Conf. Simul. Semiconductor Devices Processes (SISDEP)*, 1993, pp. 157–160, doi: 10.1007/978-3-7091-6657-4\_38.

- [23] K. Hasnat et al., "Thermionic emission model of electron gate current in submicron NMOSFETs," *IEEE Trans. Electron Devices*, vol. 44, no. 1, pp. 129–138, Jan. 1997, doi: 10.1109/16.554802.

- [24] D. M. Caughey and R. E. Thomas, "Carrier mobilities in silicon empirically related to doping and field," *Proc. IEEE*, vol. 55, no. 12, pp. 2192–2193, 1967, doi: 10.1109/PROC.1967.6123.

- [25] Y. Apanovich et al., "Numerical simulation of submicrometer devices including coupled nonlocal transport and nonisothermal effects," *IEEE Trans. Electron Devices*, vol. 42, no. 5, pp. 890–898, May 1995, doi: 10.1109/16.381985.

- [26] J. Hattori, K. Fukuda, T. Ikegami, and W. H. Chang, "Temperature rise effects on static characteristics of complementary FETs with Si and Ge nanosheets," *Jpn. J. Appl. Phys.*, vol. 62, Jan. 2023, Art. no. SC1025, doi: 10.35848/1347-4065/acae61.

- [27] M. G. Ancona and H. F. Tiersten, "Macroscopic physics of the silicon inversion layer," *Phys. Rev. B, Condens. Matter*, vol. 35, no. 15, pp. 7959–7965, May 1987, doi: 10.1103/physrevb.35.7959.

- [28] S. Jin, Y. J. Park, and H. S. Min, "Simulation of quantum effects in the nano-scale semiconductor device," *J. Semicond. Technol. Sci.*, vol. 4, no. 1, pp. 32–40, Mar. 2004.

- [29] T. Ikegami, K. Fukuda, J. Hattori, H. Asai, and H. Ota, "A TCAD device simulator for exotic materials and its application to a negativecapacitance FET," *J. Comput. Electron.*, vol. 18, no. 2, pp. 534–542, Feb. 2019, doi: 10.1007/s10825-019-01313-7.

- [30] D. Nagy et al., "Drift-diffusion versus Monte Carlo simulated ON-current variability in nanowire FETs," *IEEE Access*, vol. 7, pp. 12790–12797, 2019, doi: 10.1109/ACCESS.2019.2892592.