Dhanu Chettri<sup>®</sup>, *Graduate Student Member, IEEE*, Ganesh Mainali<sup>®</sup>, *Graduate Student Member, IEEE*, Amruth C<sup>®</sup>, Vishal Khandelwal<sup>®</sup>, Saravanan Yuvaraja<sup>®</sup>, Na Xiao, Xiao Tang, Derya Baran, and Xiaohang Li<sup>®</sup>, *Member, IEEE*

Abstract—In this article, we report on the fabrication of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> pseudo-CMOS inverters using enhancementmode (E-mode)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> single-finger (S<sub>F</sub>) and multifinger (M<sub>F</sub>) thin-film transistors (TFTs). Initially, single-stage monolithic inverter ICs were fabricated using TFTs having threshold voltages  $V_{th}^{SF} = 0.6$  V and  $V_{th}^{MF} = 0.1$  V. However, the single-stage inverter yielded poorer gain (4.50 at  $V_{DD}$ , supply voltage = 3 V). Alternatively, a pseudo-CMOS (double-stage) inverter was designed and fabricated, yielding a maximum gain of 6.45 but with a poor noise margin (NM). To improve the NM, the pseudo-CMOS circuit was tested using TFTs having higher threshold voltages ( $V_{th}^{SF} = 1.85$  V and  $V_{th}^{MF} = 1.75$  V). Notably, the optimized pseudo-CMOS circuit exhibited the least peak power consumption (0.2 nW) and the maximum gain of 8 at  $V_{DD} = 3$  V. The monolithically integrated devices' performance and IC highlight this technology's remarkable potential for application in the emerging sector of power electronics and extreme-environment electronics.

Index Terms— $\beta$ -Ga<sub>2</sub>O<sub>3</sub> heteroepitaxy,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin-film transistors (TFTs), inverter logic circuits, pseudo-CMOS.

### I. INTRODUCTION

**B**-Ga<sub>2</sub>O<sub>3</sub>, an emerging ultrawide-bandgap (UWBG) material with a bandgap of 4.8 eV and a large breakdown field of 8 MV/cm, is a promising candidate for high-power electronics [1]. Furthermore, the availability of high-quality  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrates promoted the entry of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> electronics into the market [2]. In addition to power electronics, UWBG CMOS circuits are highly desirable for extreme-environment

Manuscript received 26 June 2023; revised 4 August 2023; accepted 7 August 2023. Date of publication 28 August 2023; date of current version 22 September 2023. This work was supported in part by the King Abdullah University of Science and Technology (KAUST) Baseline Fund under Grant BAS/1/1664-01-01, in part by the Impact Acceleration Fund under Grant REI/1/5124-01-01, in part by the Near-Term Grand Challenge Grant under Grant REI/1/4999-01-01, and in part by the Semiconductor Initiative Grant under Grant REP/1/5314-01-01. The review of this article was arranged by Editor Y. Zhao. (*Corresponding author: Dhanu Chettri.*)

Dhanu Chettri, Ganesh Mainali, Vishal Khandelwal, Saravanan Yuvaraja, Na Xiao, Xiao Tang, and Xiaohang Li are with the Advanced Semiconductor Laboratory, Electrical and Computer Engineering Program, CEMSE Division, King Abdullah University of Science and Technology (KAUST), Thuwal 23955-6900, Saudi Arabia (e-mail: dhanu.chettri@kaust.edu.sa; Xiaohang.li@kaust.edu.sa).

Amruth C and Derya Baran are with the Physical Sciences and Engineering Division, KAUST Solar Center (KSC), King Abdullah University of Science and Technology (KAUST), Thuwal 23955-6900, Saudi Arabia.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2023.3305338.

Digital Object Identifier 10.1109/TED.2023.3305338

applications [3]. Integrating a high-power  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> module and an efficient  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> logic circuit is desirable for the miniaturization of power electronics modules. So far, highpower MOSFETs have been extensively researched [4], [5].  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> metal–semiconductor field-effect transistors [6] and vertical and lateral MOSFETs have also been reported [7], [8].

It is possible to obtain n-type  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> by doping Si and Sn impurities; however, producing p-type  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is difficult due to the large activation energy (>1 eV) of p-dopants, such as Mg and Fe in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> [9]. First-principles calculations show that the activation energy of p-dopants can be reduced via codoping; however, efficient p-type  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> has not yet been demonstrated experimentally [10]. Thus, the unavailability of efficient p-type doping in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> hampers the development of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> CMOS circuits. Nevertheless, it is possible to design logic circuits, e.g., an inverter with a unipolar n-MOS circuit. Various topologies are available for building unipolar inverters, and each design has certain advantages and limitations. The commonly used unipolar inverters include the diode-load type implementing two enhancement-mode (E-mode) thin-film transistors (TFTs) [11]. The other design includes the enhancement-depletion mode TFTs, which have higher gain and better power dissipation than the E-mode TFTs but increases the fabrication cost and complexity as both E-mode and D-mode TFTs are needed [11], [12]. Furthermore, pseudo-CMOS was first introduced by Huang et al. [13] demonstrating pseudo-CMOS inverters having comparable performances with CMOS counterparts. In addition, compared to conventional n-MOS logic, pseudo-CMOS gives better noise immunity, and its circuit could be implemented using either just E-mode or only D-mode TFTs [14], [15].

Demonstration of a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> inverter circuit using a combination of D-mode and E-mode  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistors is previously reported [16], [17]. Furthermore, based on first-principles analysis, Ma et al. [18] reported that a monolayer Ga<sub>2</sub>O<sub>3</sub> MOSFET exhibited superior characteristics compared with most other reported 2-D materials. However, we would like to emphasize that many challenges remain with respect to the development, integration, and device application of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> logic circuits. Furthermore, notably, research on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> logic/driver circuits is limited. Hence, this study focuses on the fabrication and characterization of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> pseudo-CMOS inverters. Different topologies of single- and dual-stage inverters are fabricated, utilizing

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 License. For more information, see https://creativecommons.org/licenses/by-nc-nd/4.0/

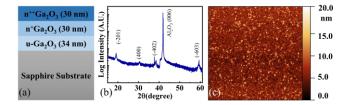

Fig. 1.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layers grown on a sapphire substrate via PLD. (a) Schematic, (b) X-ray diffraction spectrum, and (c) atomic force microscopy image (5 × 5  $\mu$ m) of the as-grown  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>.

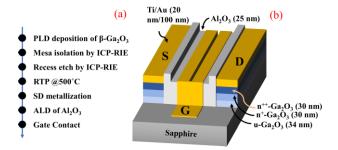

Fig. 2. (a) Process flow and (b) schematic of the standard  $S_F$  device.

$\beta$ -Ga<sub>2</sub>O<sub>3</sub> TFTs with different threshold voltages. The performance parameters, including gain, voltage transfer characteristics (VTCs), noise margin (NM), and power consumption, are thoroughly examined.

# II. MATERIAL GROWTH AND DEVICE FABRICATION A. Material Growth and Characterizations

$\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin films were grown on a single-side polished, c-plane sapphire substrate using the pulsed laser deposition (PLD) technique. Before PLD, the sapphire substrate was diced into  $1 \times 1$  cm and cleaned in an ultrasonication bath of acetone followed by immersion in isopropyl alcohol for 5 min; the squares were rinsed with deionized (DI) water and dried with N<sub>2</sub> gun and finally loaded into the PLD chamber. Three PLD targets were used: target 1 was undoped  $Ga_2O_3$ , target 2 was Si-doped (SiO<sub>2</sub> 0.1 wt%) Ga<sub>2</sub>O<sub>3</sub>, and target 3 was Si-doped (SiO<sub>2</sub> 0.001 wt%) Ga<sub>2</sub>O<sub>3</sub>. Each target was irradiated using a KrF excimer laser ( $\lambda = 248$  nm) at 100 mJ (on the target) for 1000 pulses at a frequency of 5 Hz and O<sub>2</sub> pressure of 4 mTorr at different temperatures of 600 °C for unintentionally doped, u-Ga<sub>2</sub>O<sub>3</sub> and 700 °C for n-Ga<sub>2</sub>O<sub>3</sub>. Through this process,  $\sim$ 34-nm u-Ga<sub>2</sub>O<sub>3</sub> and two types of  $\sim$ 30-nm Si-doped Ga<sub>2</sub>O<sub>3</sub> with carrier concentrations of  $4 \times 10^{18}$  and  $6 \times 10^{19}$ /cm<sup>3</sup>, respectively, were obtained as a stack of films [Fig. 1(a)]. The thickness of the film was determined by filmetrics. The X-ray diffraction spectrum depicted in Fig. 1(b) shows a low-intensity (400) peak of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> along with a prominent (-201) peak. The atomic force microscopy surface morphology shows a root-meansquared roughness value of 2.36 nm, as shown in Fig. 1(c).

## B. Device Fabrication

Fig. 2(a) and (b) shows the fabrication flow of the device and the 3-D view of the single-finger TFT device (device  $S_F$ ). For the purpose of device isolation, the sample was patterned using a photoresist and mesa etched via inductively

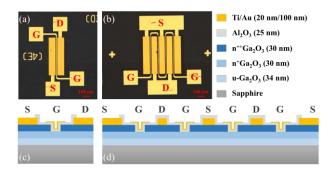

Fig. 3. Microscopy images of (a)  $S_F$  device and (b)  $M_F$  device. Schematics of the cross sections of (c) device  $S_F$  and (d) device  $M_F$ .

coupled plasma reactive ion etching (ICP-RIE); this process was performed using BCl<sub>3</sub> and Ar plasmas. After isolation, using ICP-RIE for the gate recess depth of 30 nm was etched to engineer the threshold voltage ( $V_{\text{th}}$ ) of the TFT close to zero. ICP-RIE is known to damage the surface of the target [19]. Hence, the sample was annealed in a N<sub>2</sub> environment at 500 °C for 5 min to heal the damage caused by the plasma [20].

Ti/Au (20/100 nm) was deposited as the source-drain (SD) ohmic contact via dc magnetron sputtering. Furthermore, a 25-nm-thick Al<sub>2</sub>O<sub>3</sub> layer was grown via atomic layer deposition (ALD) at 300 °C using (CH<sub>3</sub>)<sub>3</sub>Al and O<sub>2</sub> plasmas as the Al and O precursors, respectively; this layer functioned as a gate dielectric. After ALD, Al<sub>2</sub>O<sub>3</sub> was patterned and etched via ICP-RIE. Finally, Ti/Au (20/100 nm) layer was deposited via dc magnetron sputtering as a gate electrode. In addition to the standard design (device  $S_F$ ) shown in Fig. 3(a), we also fabricated a multifinger  $(M_F)$  device [Fig. 3(b)]. Both devices have an identical source-to-drain distance ( $L_{sd}$ ) of 25  $\mu$ m and a gate length  $(L_g)$  of 7  $\mu$ m. Along with the recess depths of 30 nm and Al<sub>2</sub>O<sub>3</sub> gate dielectric thickness of 25 nm. The  $S_F$  and  $M_F$  devices only differed in their channel widths: the channel width  $W_S$  (device  $S_F$ ) and  $W_M$  (device  $M_F$ ) were 400 and 1600  $\mu$ m (i.e.,  $W_{\rm M} = 4 \times W_{\rm S}$ ), respectively. The cross-sectional schematic of device S<sub>F</sub> and M<sub>F</sub> is given in Fig. 3(c) and (d), respectively.

### **III. RESULTS AND DISCUSSION**

In this section, the characteristics of transistors and the performances of the single- and dual-stage logic inverters are discussed. The devices were characterized for dc performance using a Keithley 4200 SCS parameter analyzer.

#### A. Transistor Characteristics

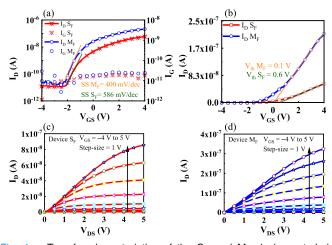

The top-gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> shows the typical transistor characteristics (Fig. 4). The transfer characteristics of S<sub>F</sub> and M<sub>F</sub> devices are shown in Fig. 4(a) and (b) respectively. The ON-current of M<sub>F</sub> devices is higher than that of the S<sub>F</sub> device because the M<sub>F</sub> devices have a larger channel width-to-length ratio (W/L) and the drain current is directly proportional to the gate width ( $I_D \propto W$ ). The V<sub>th</sub> values for S<sub>F</sub> and M<sub>F</sub> devices are 0.6 and 0.1 V, respectively. The  $I_{on}$  and  $I_{off}$  ratios for S<sub>F</sub> and M<sub>F</sub> devices are 7.1 × 10<sup>3</sup> and 1.5 × 10<sup>4</sup>, respectively. Furthermore, the S<sub>F</sub> device has a higher subthreshold slope (SS) of 586 mV/dec compared with that of the M<sub>F</sub> device (400 mV/dec), which is ~32% less than the former.

Fig. 4. Transfer characteristics of the  $S_F$  and  $M_F$  devices at drain voltage = 3 V in (a) log scale and (b) linear scale. Output characteristics of (c)  $S_F$  device and (d)  $M_F$  device.

The higher SS in the fabricated devices may result from the potential degradation of the channel–gate dielectric interface. Despite annealing to recover from plasma damage during recess formation, the gate interface quality might remain poor, contributing to the higher SS. The SS is given as follows [21]:

$$SS = \ln(10) \left(\frac{kT}{q}\right) \left(1 + \frac{C_{\rm d} + qD_{\rm it}}{C_{\rm ox}}\right) \tag{1}$$

where  $C_d$ ,  $D_{it}$ , and  $C_{ox}$  are the depletion capacitance, interface trap density, and oxide capacitance, respectively. In the  $M_F$ device, SS decreases due to decreased  $C_d$  as a result of charge sharing. Similar SS improvements are observed in nano transistors with an  $M_F$  structure [21]. Plasma-free wet chemical etching, such as metal-assisted chemical etching (MacEtch), could further enhance SS [22].

Fig. 4(c) and (d) shows the output characteristics of  $S_F$ and  $M_F$  devices, respectively. The drain current of the  $M_F$ device is approximately four times that of the  $S_F$  device as the channel width of the former is four times that of the latter. The ON-resistance ( $R_{on}$ ) is very large for both devices: 43.3 M $\Omega$ ·m for the  $S_F$  device and 14 M $\Omega$ ·m for the  $M_F$  device. The effective mobility is calculated using the following equation [23]:

$$\mu_{\rm eff} = \frac{L_{\rm ch}}{W.C_{\rm ox}.(V_{\rm GS} - V_{\rm th})} \frac{d(I_{\rm D,lin})}{d(V_{\rm DS})} \tag{2}$$

where  $L_{ch}$  denotes the channel length (source-to-drain distance), W denotes the channel width, and  $V_{GS}$  denotes the gate-to-source voltage.  $C_{ox}$  is the oxide capacitance per unit area, given by the following equation:

$$C_{\rm ox} = \frac{\varepsilon_0 \varepsilon_{\rm r}}{t_{\rm ox}} \tag{3}$$

where  $\varepsilon_0$  and  $\varepsilon_r$  denote the absolute permittivity of air and relative permittivity of the gate dielectric (Al<sub>2</sub>O<sub>3</sub>), respectively, and  $t_{ox}$  denotes the dielectric thickness. The effective mobilities of the S<sub>F</sub> and M<sub>F</sub> devices were calculated to be  $1.02 \times 10^{-3}$  and  $7.35 \times 10^{-3}$  cm<sup>2</sup>/Vs, respectively, which are considerably lower than the values reported in [5] and [24]. The low mobility is mainly caused by the relatively poor film quality of heteroepitaxially grown  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> on the

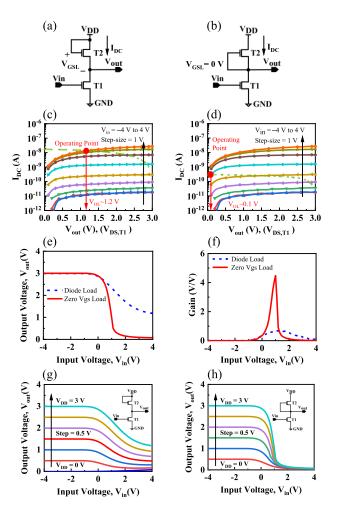

Fig. 5. Schematic of single-stage inverters (using S<sub>F</sub> load and driver TFT). (a) Diode-load inverter. (b) Zero- $V_{\rm GS}$  load inverter. Output characteristics of driver TFT (T1) with load curves (dotted line) imposed by load TFT (T2) for (c) diode-load inverter and (d) zero- $V_{\rm GS}$  load inverter. (e) VTC and (f) gain versus input voltage of diode-load and zero- $V_{\rm GS}$  load inverters at  $V_{\rm DD} = 3$  V. VTC of (g) diode-load inverter and (h) zero- $V_{\rm GS}$  load inverter at different  $V_{\rm DD}$ 's.

sapphire substrate because of the lattice mismatch between the sapphire substrate and the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin film [25].

## B. Single-Stage Inverter Characteristics

The schematic of the diode-load inverter and zero- $V_{\rm GS}$  load [13] inverter is shown in Fig. 5(a) and (b). Fig. 5(c) shows the output characteristics of the driver TFT (T1) of the diode-load inverter with load curve imposed by the load TFT (T2) to show the operating point and achieved output voltage low ( $V_{\rm OL}$ ) of ~1.2 V. Similarly, Fig. 5(d) shows the output characteristics of the driver TFT (T1) of zero- $V_{\rm GS}$  load inverter with load curve imposed by load TFT (T2) to show the operating point, which shows that it can achieve the  $V_{\rm OL}$  of ~0.1 V. Fig. 5(e) and (f) shows VTCs and gains curves of the diode-load inverter and zero- $V_{\rm GS}$  load inverter.

The K ratio (KR) [26], estimated using (4), determines the transfer characteristics of the inverter. The inverter gain improves with increasing KR, but it also contributes to increase the power consumption as a higher KR implies a larger driver transistor, which in turn indicates a higher ON-current of the device

$$KR = \frac{\mu_{n \, driver \, TFT} \times C_{ox} \left(\frac{W}{L}\right)_{driver}}{\mu_{n \, load \, TFT} \times C_{ox} \left(\frac{W}{L}\right)_{load}}.$$

(4)

The gain of the inverter module can be approximated by the product of the transconductance  $(g_m)$  of the driver transistor and a parallel combination of the driver transistor resistance  $(R_D)$  and load resistance  $(R_L)$ , as shown in (5). From this expression, we can infer that for the inverter to have a higher gain,  $g_m$  of the driver TFT should be high. In addition, the resistance offered by the driver and load TFT should be high

$$gain = g_{\rm m} \times \left(\frac{R_{\rm D}R_{\rm L}}{R_{\rm D} + R_{\rm L}}\right).$$

(5)

In the subthreshold region, the transconductance is given as [27]

$$g_{\rm m} = \frac{\ln 10}{\rm SS} I_{\rm DS} \tag{6}$$

where  $I_{DS}$  is the subthreshold drain-to-source current. From (6), we can infer that the lower the SS, the higher are  $g_m$  and gain; however, a lower SS indicates sensitivity to bias variation [27]. Both S<sub>F</sub> and M<sub>F</sub> TFTs have high SS (an SS of 586 mV/dec for S<sub>F</sub> and 400 mV/dec for M<sub>F</sub>). As pointed out by (6), higher SS decreases  $g_m$  but as discussed in [27], the high SS gives stability over the bias variation. This stability for bias variation for diode-load inverter and zero- $V_{GS}$  load inverter is evident by the VTC curves shown in Fig. 5(g) and (h), respectively.

The gain of the zero- $V_{GS}$  load inverter is 4.5, which is four times that of the diode-load inverter, as shown in Fig. 5(f). The reason for the higher gain can be understood from the load line plot shown in Fig. 5(c) and (d). For the diodeload inverter load curve, we observe that the load TFT and driver TFT are not saturated at the same instant of time. To realize the maximum inverter gain, the load and driver TFTs should provide the maximum small-signal resistance, which is possible when the current is saturated. In other words, because the gain depends on the parallel resistance offered by the driver and load TFTs, if either the driver TFT or load TFT has low resistance, the effective resistance is close to the lower resistance (i.e., a parallel combination). This results in a decrease in the gain of the diode-load inverter.

Furthermore, Fig. 5(d) shows that although the load and driver TFTs [refer to Fig. 5(b)] operate in the subthreshold region, the current passing through devices in the zero- $V_{GS}$  load inverter saturates when  $V_{DS}$  across driver TFT (T1) approaches 1 V and load TFT (T2) is close to 2 V ( $V_{DD}-V_{out}$ ). This implies that both load and driver TFTs offer a huge resistance; hence, the gain is greater than that of the diode-load inverter.

The power consumption  $(P_{\rm DC})$  in this study is calculated as the product of the total current  $(I_{\rm DC})$  drawn by the inverter module from the supply rail and the supply voltage  $(V_{\rm DD})$  (i.e.,  $P_{\rm DC} = I_{\rm DC} \times V_{\rm DD}$ ). The maximum power consumption of the zero- $V_{\rm GS}$  load inverter was 7.5 nW (at  $V_{\rm DD} = 3$  V), which is 9.5 times less than that of the diode-load inverter as the zero- $V_{\rm GS}$  inverter's load transistor operates in a subthreshold region where the current flowing through the circuit is in the order of nanoamperes. Such low power consumption is the major advantage of using a subthreshold-load TFT (zero- $V_{GS}$  TFT). Ideally, the static power consumption must be zero, but a small current is present in the subthreshold region of the Ga<sub>2</sub>O<sub>3</sub> TFT used in the circuit as the channel is not fully depleted at 0 V. In addition, as the threshold is close to zero, the subthreshold current is of the order of a few nanoamperes. Thus, power dissipation occurs when the driver TFT operates above the threshold voltage.

The transfer characteristics curve shows that the output voltage high ( $V_{OH}$ ) values of both inverters are equal to  $V_{DD}$ , but  $V_{OL}$  of the diode-load inverter is 1.2 V and that of the zero- $V_{GS}$  inverter is 0.3 V. This is because the load curve intersects the output characteristics of the driver at a higher voltage for the diode-load inverter than that for the zero- $V_{GS}$  load inverter, as shown in Fig. 5(c) and (d). The transfer characteristics and gain were further improved by developing a pseudo-CMOS inverter as described in Section III-C.

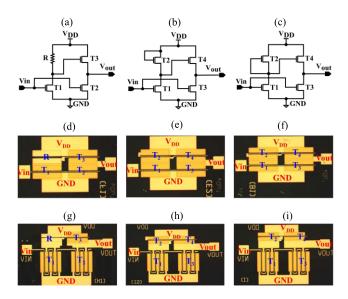

#### C. Dual-Stage Inverter Characteristics

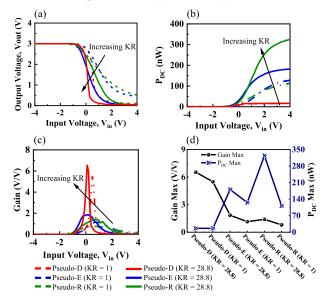

The performance of the CMOS inverter is well reported [14], and ideally, this type of inverter does not dissipate any static power [13]. The single-stage inverters in Section III-B lack full CMOS-like behavior due to incomplete turn-off of the load TFT when the driver TFT is on. Hence, to ensure proper turn-off of the load TFT during pull-down and the driver TFT during pull-up, pseudo-CMOS topologies were fabricated using n-type Ga<sub>2</sub>O<sub>3</sub> TFT. The most common inverter topologies are pseudo-R (resistor-load inverter first stage), pseudo-E (diode-load inverter first stage) [13], [15], and pseudo-D (zero- $V_{\rm GS}$  load inverter first stage) inverters [13], as shown in Fig. 6(a)-(c), respectively. The load resistance in the first stage of pseudo-R circuit was realized monolithically using n-type  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> itself giving a resistance of about 666 M $\Omega$ . The optical images of all the fabricated inverters, namely, pseudo-R, pseudo-D, and pseudo-E with KR = 1, are shown in Fig. 6(d)-(f), respectively. Furthermore, Fig. 6(g)-(i) shows the optical images of inverters with KR = 28.8.

The VTC, dc power consumption, and gain are shown in Fig. 7(a)–(c), respectively. With an increase in KR, the gain increases and the transfer characteristics improve. However, power consumption also increases as the size of the driver transistor increases. This can be clearly observed in Fig. 7(b). The power consumption of pseudo-R and pseudo-E inverters increases by 3 and 1.5 times, respectively, with a fourfold increase in the drive transistor channel width. However, there is almost no significant increase in the power consumption  $(\sim 16 \text{ nW})$  of the pseudo-D inverter [Fig. 7(d)] because all the transistors work in the subthreshold region.

In integrated logic circuits, the inverters should be cascaded and should be able to drive consecutive stages. Therefore, each inverter should have a gain higher than unity. Thus, logic inverters with high gain are desirable. The zero- $V_{\rm GS}$  load inverter and pseudo-D inverter with KR = 28.8 have high gains of 5.5 and 6.5 compared with other inverter topologies,

Fig. 6. Dual-stage inverter circuits and fabricated devices. (a) Pseudo-R, (b) pseudo-E, and (c) pseudo-D schematics. Fabricated devices with KR = 1. (d) Pseudo-R. (e) Pseudo-E. (f) Pseudo-D. Fabricated devices with KR = 28.8. (g) Pseudo-R. (h) Pseudo-E. (i) Pseudo-D.

Fig. 7. Comparison of the dual-stage inverters with KR = 1 and 28.8. (a) VTC. (b) Power consumption. (c) Gain. (d) Gain and peak power consumption. Note that legends are common for (a)-(c).

respectively. This occurs because the threshold voltage of the transistor used in the zero- $V_{GS}$  load inverter and the first stage of pseudo-D inverter is close to 0 V (0.1 V for S<sub>F</sub> and 0.6 V for M<sub>F</sub>), which will ensure that the load TFT is in the saturation region offering the highest load impedance resulting in an increase in the gain.

Although zero- $V_{\rm GS}$  and pseudo-D inverters have considerable gain, the NM offered by these topologies near zero  $V_{\rm th}$  is poor. In the pseudo-R and pseudo-E configurations as shown in Fig. 6(a) and (b), respectively, the output of the first stage connects to the gate of the pull-up TFT in the second stage. Considering the higher  $V_{\rm OL}$  exhibited by resistive and diode-load topologies, careful consideration of  $V_{\rm th}$  is crucial. Choosing a very large  $V_{\rm th}$  (much greater than the output high of the first stage) will result in the pull-up

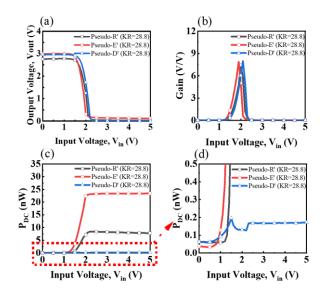

Fig. 8. For topologies pseudo-R', pseudo-E', and pseudo-D'. (a) VTC, (b) gain, (c) dc power consumption, and (d) scaled version of (c) to illustrate the dc power consumption of the pseudo-D' inverter.

TABLE I COMPARISON OF FABRICATED PSEUDO-CMOS INVERTERS WITH THE REPORTED LOGIC INVERTER

| Logic<br>Inverters      | Mater-<br>ial                  | V <sub>DD</sub><br>(V) | NMH<br>(V)/NML<br>(V) | Gain<br>Max<br>(V/V) | P <sub>DC</sub><br>Max<br>(nW) |

|-------------------------|--------------------------------|------------------------|-----------------------|----------------------|--------------------------------|

| <b>Pseudo-D</b><br>[14] | ZnO                            | 5                      | 3.57/1.37             | 230                  | ~ 25                           |

| E-D [28]                | IGZO                           | 3                      | -                     | 40                   | -                              |

| E-D [16]                | Ga <sub>2</sub> O <sub>3</sub> | 1.4                    | -                     | 2.6                  | -                              |

| <b>E-D</b> [17]         | Ga <sub>2</sub> O <sub>3</sub> | 3.0                    | -                     | < 0.5                | -                              |

| *Pseudo-D'              | Ga <sub>2</sub> O <sub>3</sub> | 3.0                    | 0.66/1.63             | 8.0                  | 0.19                           |

| *Pseudo-E'              | Ga <sub>2</sub> O <sub>3</sub> | 3.0                    | 0.91/1.32             | 7.9                  | 23.10                          |

| *Pseudo-R'              | Ga <sub>2</sub> O <sub>3</sub> | 3.0                    | 0.55/1.53             | 7.5                  | 8.38                           |

E-D= Enhancement-Depletion n-MOS inverter, \*This work,  $V_{DD}$  = Supply Voltage, NMH/NML = Noise Margin High/Noise Margin Low, Gain Max = Maximum Gain,  $P_{DC}$  Max = dc peak power consumption.

TFT being OFF. Similarly, in the pseudo-D circuit, increasing  $V_{\text{th}}$  shifts the load TFT (T2) toward the deep subthreshold region, eventually turning it OFF. Hence, the driver and load TFTs with optimal  $V_{\text{th}}$  (S<sub>F</sub> ~1.85 V and M<sub>F</sub> ~1.75 V) were fabricated to improve the inverter's NM. The threshold voltage was increased by deepening the recess etch to ~35 nm. The pseudo-topologies with increased  $V_{\text{th}}$  are referred to as pseudo-R', pseudo-E', and pseudo-D', which are implemented with KR = 28.8. Fig. 8 shows their VTC, gain, and dc power consumptions.

Moreover, because the gate voltage of the load TFT in the second stage is derived from the output of the first stage, the source terminal of the second-stage load switches like  $V_{out}$  of the first stage. Hence,  $V_{GS}$  of the load TFT in the second stage is less than its  $V_{th}$  in all three pseudo-topologies. Consequently, the load TFT is in a subthreshold region, and it limits the current through it. Thus, the second stage of pseudo-topologies is in the subthreshold region. Hence, the gain of all pseudo-topologies improved and is almost equal, as shown in Fig. 8(b). Alternatively, the power consumption is <0.2 nW

for the pseudo-D' design, as shown in Fig. 8(c) and (d), because of the subthreshold region of operation in both stages.

Table I lists  $V_{\text{DD}}$ , NM high (NMH), NM low (NML), gain, and dc peak power consumption of the reported ZnO, IGZO, and Ga<sub>2</sub>O<sub>3</sub> inverters along with our reported Ga<sub>2</sub>O<sub>3</sub> pseudo inverters for comparison. The fabricated topologies can be considered robust with NMH of >0.5 V and NML of ~1.5 V. The slight variations in the NM values among the pseudo-CMOS topologies originate from the small variations in  $V_{\text{OH}}$ and  $V_{\text{OL}}$  among the inverters, as seen from the VTCs in Fig. 8(a). To the best of our knowledge, this is the first pseudo inverter with a unipolar Ga<sub>2</sub>O<sub>3</sub> TFT on a sapphire substrate with substantially low power consumption resulting from operation in the subthreshold region.

## **IV. CONCLUSION**

In this study, we demonstrated a single-stage inverter and dual-stage pseudo-CMOS inverters using heteroepitaxial grown  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> TFTs. Various  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> logic inverters topologies were demonstrated, and their performance, including gain, VTCs, NM, and power consumption, was examined to highlight their merits and demerits. All the TFTs in the inverters were monolithically integrated on the same wafer. The threshold voltage of the TFT was tuned by tuning the recess depths of the gate during fabrication. TFTs of different sizes should be used to improve the gain; this can be achieved by using an M<sub>F</sub> design. An ultralow power consumption inverter was realized by operating the TFTs in the subthreshold regions. Power consumption as low as 0.2 nW was achieved in the case of the pseudo-D' inverter. A gain of  $\sim 8$  V/V for  $V_{\rm DD}$  of 3 V was achieved in the case of the pseudo-D' inverter. The NML and NMH values for all pseudo-CMOS inverters at higher threshold voltages were  $\sim 1.5$  and  $\sim 0.5$  V, respectively, demonstrating their robust design.

#### REFERENCES

- E. Farzana and J. S. Speck, Ultrawide Bandgap β-Ga<sub>2</sub>O<sub>3</sub> Semiconductor. New York, NY, USA: AIP Publishing, 2023, doi: 10.1063/9780735425033.

- [2] Z. Zuo and Y. Li, "Emerging electrochemical energy applications of graphdyne," *Joule*, vol. 3, no. 4, pp. 899–903, Apr. 2019, doi: 10.1016/j.joule.2019.01.016.

- [3] M. A. Mastro, A. Kuramata, J. Calkins, J. Kim, F. Ren, and S. J. Pearton, "Perspective—Opportunities and future directions for Ga<sub>2</sub>O<sub>3</sub>," *ECS J. Solid State Sci. Technol.*, vol. 6, no. 5, pp. P356–P359, 2017, doi: 10.1149/2.0031707jss.

- [4] O. Hilt et al., "Lateral and vertical power transistors in GaN and Ga<sub>2</sub>O<sub>3</sub>," *IET Power Electron.*, vol. 12, no. 15, pp. 3919–3927, Dec. 2019, doi: 10.1049/iet-pel.2019.0059.

- [5] J. Bae, H. W. Kim, I. H. Kang, G. Yang, and J. Kim, "High breakdown voltage quasi-two-dimensional β-Ga<sub>2</sub>O<sub>3</sub> field-effect transistors with a boron nitride field plate," *Appl. Phys. Lett.*, vol. 112, no. 12, pp. 1–10, Mar. 2018, doi: 10.1063/1.5018238.

- [6] A. Bhattacharyya, S. Roy, P. Ranga, C. Peterson, and S. Krishnamoorthy, "High-mobility tri-gate β-Ga<sub>2</sub>O<sub>3</sub> MESFETs with a power figure of merit over 0.9 GW/cm<sup>2</sup>," *IEEE Electron Device Lett.*, vol. 43, no. 10, pp. 1637–1640, Oct. 2022, doi: 10.1109/LED.2022.3196305.

- [7] Z. Hu et al., "Enhancement-mode Ga<sub>2</sub>O<sub>3</sub> vertical transistors with breakdown voltage >1 kV," *IEEE Electron Device Lett.*, vol. 39, no. 6, pp. 869–872, Jun. 2018, doi: 10.1109/LED.2018.2830184.

- [8] M. H. Wong, K. Sasaki, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, "Field-plated Ga<sub>2</sub>O<sub>3</sub> MOSFETs with a breakdown voltage of over 750 V," *IEEE Electron Device Lett.*, vol. 37, no. 2, pp. 212–215, Feb. 2016, doi: 10.1109/LED.2015.2512279.

- [9] R. Sharma, M. E. Law, F. Ren, A. Y. Polyakov, and S. J. Pearton, "Diffusion of dopants and impurities in β-Ga<sub>2</sub>O<sub>3</sub>," J. Vac. Sci. Technol. A, Vac., Surf., Films, vol. 39, no. 6, Dec. 2021, Art. no. 060801, doi: 10.1116/6.0001307.

- [10] A. Kyrtsos, M. Matsubara, and E. Bellotti, "On the feasibility of p-type Ga<sub>2</sub>O<sub>3</sub>," *Appl. Phys. Lett.*, vol. 112, no. 3, pp. 1–12, Jan. 2018, doi: 10.1063/1.5009423.

- [11] L.-J. Chi, M.-J. Yu, Y.-H. Chang, and T.-H. Hou, "1-V full-swing depletion-load a-In–Ga–Zn–O inverters for back-end-of-line compatible 3D integration," *IEEE Electron Device Lett.*, vol. 37, no. 4, pp. 441–444, Apr. 2016, doi: 10.1109/LED.2016.2535124.

- [12] Z. Feng et al., "Fluorination-enabled monolithic integration of enhancement- and depletion-mode indium-gallium-zinc oxide TFTs," *IEEE Electron Device Lett.*, vol. 39, no. 5, pp. 692–695, May 2018, doi: 10.1109/LED.2018.2818949.

- [13] T.-C. Huang et al., "Pseudo-CMOS: A design style for low-cost and robust flexible electronics," *IEEE Trans. Electron Devices*, vol. 58, no. 1, pp. 141–150, Jan. 2011, doi: 10.1109/TED.2010.2088127.

- [14] W. Zhao et al., "High-gain transparent inverters based on deuterated ZnO TFTs fabricated by atomic layer deposition," *IEEE Electron Device Lett.*, vol. 41, no. 10, pp. 1508–1511, Oct. 2020, doi: 10.1109/LED.2020.3018443.

- [15] J.-S. Kim et al., "Dynamic logic circuits using a-IGZO TFTs," *IEEE Trans. Electron Devices*, vol. 64, no. 10, pp. 4123–4130, Oct. 2017, doi: 10.1109/TED.2017.2738665.

- [16] J. Kim and J. Kim, "Monolithically integrated enhancement-mode and depletion-mode β-Ga<sub>2</sub>O<sub>3</sub> MESFETs with graphene-gate architectures and their logic applications," ACS Appl. Mater. Interface, vol. 12, no. 6, pp. 7310–7316, Feb. 2020, doi: 10.1021/acsami.9b19667.

- [17] V. Khandelwal et al., "Monolithic β-Ga<sub>2</sub>O<sub>3</sub> NMOS IC based on heteroepitaxial E-mode MOSFETs," *Appl. Phys. Lett.*, vol. 122, no. 14, Apr. 2023, Art. no. 143502, doi: 10.1063/5.0143315/2882382.

- [18] Y. Ma et al., "First-principles-based quantum transport simulations of high-performance and low-power MOSFETs based on monolayer Ga<sub>2</sub>O<sub>3</sub>," ACS Appl. Mater. Interface, vol. 14, no. 42, pp. 48220–48228, Oct. 2022, doi: 10.1021/acsami.2c12266.

- [19] C. Joishi et al., "Deep-recessed β-Ga<sub>2</sub>O<sub>3</sub> delta-doped field-effect transistors with in situ epitaxial passivation," *IEEE Trans. Electron Devices*, vol. 67, no. 11, pp. 4813–4819, Nov. 2020, doi: 10.1109/TED.2020.3023679.

- [20] Y. Lv et al., "Influence of gate recess on the electronic characteristics of β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs," *Superlattices Microstruct.*, vol. 117, pp. 132–136, May 2018, doi: 10.1016/j.spmi.2018.03.013.

- [21] S.-L. Siu, W.-S. Tam, H. Wong, C.-W. Kok, K. Kakusima, and H. Iwai, "Influence of multi-finger layout on the subthreshold behavior of nanometer MOS transistors," *Microelectron. Rel.*, vol. 52, no. 8, pp. 1606–1609, Aug. 2012, doi: 10.1016/J.MICROREL.2011.09.011.

- [22] H. C. Huang et al., "β-Ga<sub>2</sub>O<sub>3</sub> FinFETs with ultra-low hysteresis by plasma-free metal-assisted chemical etching," *Appl. Phys. Lett.*, vol. 121, no. 5, p. 52102, Aug. 2022.

- [23] Y. Xu et al., "Precise extraction of charge carrier mobility for organic transistors," Adv. Funct. Mater., vol. 30, no. 20, May 2020, Art. no. 1904508, doi: 10.1002/ADFM.201904508.

- [24] Z. Xia et al., "β-Ga<sub>2</sub>O<sub>3</sub> delta-doped field-effect transistors with current gain cutoff frequency of 27 GHz," *IEEE Electron Device Lett.*, vol. 40, no. 7, pp. 1052–1055, Jul. 2019, doi: 10.1109/LED.2019.2920366.

- [25] L. Dimitrocenko, G. Strikis, B. Polyakov, L. Bikse, S. Oras, and E. Butanovs, "The effect of a nucleation layer on morphology and grain size in MOCVD-grown β-Ga<sub>2</sub>O<sub>3</sub> thin films on C-plane sapphire," *Materials*, vol. 15, no. 23, p. 8362, Nov. 2022, doi: 10.3390/ma15238362.

- [26] S.-M. Ang and Y. Leblebgi, CMOS Digital Integrated Circuits: Analysis and Deisgn. NY, USA: McGraw-Hill, 2003.

- [27] X. Cheng, S. Lee, and A. Nathan, "Deep subthreshold TFT operation and design window for analog gain stages," *IEEE J. Electron Devices Soc.*, vol. 6, pp. 195–200, 2018, doi: 10.1109/JEDS.2018.2789579.

- [28] R.-J. Lyu, Y.-H. Chiu, H.-C. Lin, P.-W. Li, and T.-Y. Huang, "High-gain, low-voltage BEOL logic gate inverter built with film profile engineered IGZO transistors," in *Proc. Int. Symp. VLSI Technol., Syst. Appl.*, Apr. 2016, pp. 1–2, doi: 10.1109/VLSI-TSA.2016.7480534.