**An IEEE Photonics Society Publication**

Volume 3, Number 4, August 2011

Amir Jafari Andrew G. Kirk

DOI: 10.1109/JPHOT.2011.2159582 1943-0655/\$26.00 ©2011 IEEE

# Demonstration of Distributed Etched Diffraction Grating Demultiplexer

#### Amir Jafari and Andrew G. Kirk

Department of Electrical and Computer Engineering, McGill University, Montreal, QC H3A 2A7, Canada

DOI: 10.1109/JPHOT.2011.2159582 1943-0655/\$26.00 © 2011 IEEE

Manuscript received April 26, 2011; revised June 2, 2011; accepted June 4, 2011. Date of publication June 16, 2011; date of current version July 5, 2011. This work was supported by the Natural Sciences and Engineering Research Council. The device was fabricated in the frame of ePIXfab operated by IMEC VZW and CEA-LETI. Corresponding author: A. Jafari (e-mail: amir.jafari@mail.mcgill.ca).

Abstract: The design principles and measurement results for a compact shallow etched distributed diffraction grating waveguide demultiplexer are presented. The deeply etched diffraction grating facets are replaced with a shallow etched odd-order quarter wavelength Bragg reflector to increase the Fresnel reflection coefficient. A prototype device was designed for coarse wavelength demultiplexing applications and was fabricated in nanophotonic silicon-on-insulator platform using deep ultraviolet (DUV) optical lithography. The demultiplexer, which supports four channels with 20-nm channel spacing, shows a crosstalk of -25 dB.

Index Terms: Distributed Bragg reflector (DBR), etched diffraction grating demultiplexer, waveguide devices.

#### 1. Introduction

Optical demultiplexers are essential components of wavelength division multiplexing (WDM) systems. To implement multiplexing/demultiplexing functionality, many technologies, such as thin film interference filters, fiber Bragg gratings, microoptic techniques, and planar integrated devices [i.e., arrayed waveguide grating (AWG) and etched diffraction grating (EDG)] have been considered. However, during the last two decades, there has been much interest in the AWG-based and EDGbased technologies.

Both AWG and EDG have been demonstrated in different material systems, including silica-onsilicon [1], [2], III–V [3], [4], and a nanophotonic silicon-on-insulator (SOI) platform [5], [6]. AWGs have been more popular particularly in low refractive index contrast materials. This popularity is due to their more relaxed fabrication requirements where arrayed waveguides can be realized with conventional waveguide fabrication techniques. In contrast, fabrication of vertical deep etched walls in EDG in order to provide a high Fresnel reflection coefficient is a challenge. Different techniques such as coating the grating walls with a thin metallic film and changing the shape of the diffraction grating facets to take advantage of the total internal reflection (TIR) phenomenon have been used in order to increase the reflectivity at the facets and, therefore, eliminate the requirement of deep etched walls.

Recently, nanophotonic SOI has attracted a great deal of attention as a high refractive index contrast material system for the implementation of EDG-based demultiplexers. The high refractive index contrast of this material system allows for a significantly higher Fresnel reflection coefficient with a much shallower etch depth. Additionally, the ability to apply the nanofabrication techniques that have already been extensively developed by the microelectronics industry, the desire to

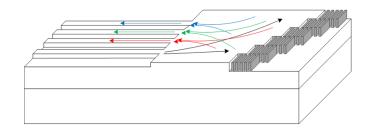

Fig. 1. (a) Schematic of distributed etched diffraction grating. (b) Design parameters of QW Bragg reflector.

integrate photonics with electronics integrated circuits, the possibility of mass producing silicon chips, and the ever-growing demand for decreasing photonic devices dimensions in order to increase integration density are among other factors contributing to increasing interest in nanophotonic SOI platform.

The EDG-based demultiplexer has already been demonstrated in nanophotonics SOI platform for both coarse [6] and dense [7] WDM applications. Despite the high refractive index contrast (and therefore the high reflection coefficient) of this platform, the main source of loss in EDG-based demultiplexers remains Fresnel reflection at the facets. A recently introduced approach to improve facet reflection is to incorporate a distributed Bragg reflector (DBR) at the EDG facets [8], [9]. Brouckaert *et al.* in [10] have achieved an experimentally measured insertion loss of 2.4 dB in the silicon-on-insulator material system, using a second-order Bragg reflector. The DBR grating in that work was implemented using deep etching, which meant that only a few layers of deep etched high reflective Bragg reflectors were implemented.

In this paper, we propose an alternative approach whereby the deeply EDG facets are replaced with shallow etched facets, followed by an odd-order quarter wavelength (QW) dielectric reflector [see Fig. 1(a)]. This approach, which we refer to as a distributed etched diffraction grating (DEDG) demultiplexer, requires an etch depth that is typically less than 100 nm. This approach is much simpler when compared to previous conventional techniques for improving the performance of EDGs such as metallic coating of the facets. Although shallow etched facets do result in a tradeoff between reflection bandwidth and efficiency (as we discuss in more detail below), the most significant advantage of this design, as compared with the previously reported approaches, is that the low effective index contrast of the shallow etched Bragg structure allows the spectral response of the demultiplexer to be optimized. We have previously numerically shown that by modifying the reflectivity spectrum of the shallow etched DBR, the overall spectral response of the demultiplexer can be engineered [11]. However, the possibility of tailoring the overall spectral response of the demultiplexer is essentially lost upon using a deep etched DBR due to availability of only a few DBR periods. Here, we report on a proof-of-concept device that makes use of shallow etching, and we will demonstrate spectral response engineered devices in future publications. The remainder of this paper is organized as follows. In Section 2, the design principles of the DEDG are described. In Section 3 we discuss the measurement results, and we conclude in Section 4.

# 2. Design Principles

The design procedure of the DEDG commences with the design of the QW Bragg reflector. The width of each layer must be one quarter of the wavelength of light propagating in that layer. This

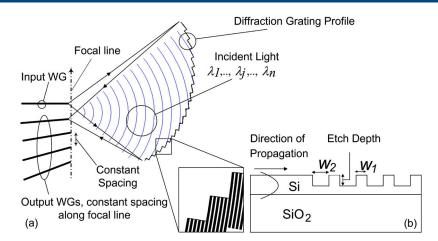

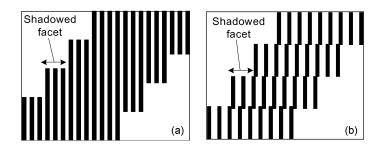

Fig. 2. Interaction of different design parameters (i.e., number of layers and refractive index contrast) of a DBR calculated at 1550 nm. For a given order, a larger number of layers result in a higher reflectivity (color map) while reducing the reflectivity bandwidth (white contours). The circle on the map shows the location of the realized device.

width is given by

$$w_i = \frac{m\lambda_0}{4n_{eff,i}} \tag{1}$$

where  $w_i$  and  $n_{eff,i}$  represent the width and the effective refractive index of the unetched (i = 1) and etched (i = 2) layers, respectively.  $\lambda_0$  is the design vacuum wavelength and *m* is the order of the Bragg grating [see Fig. 1(b)]. Equation (1) assumes a normal incidence. The properties of a QW Bragg reflector such as reflectivity and bandwidth can be calculated using transfer matrix method (TMM) [12]. These properties depend on several parameters including refractive index contrast between low and high index layers, total number of periods, and order of the Bragg reflector. The design of a QW Bragg reflector involves choosing the order of the QW stack (m) and the etch depth (or refractive index contrast between high and low index layers). This choice should be made by taking into account the fabrication process limitations such as minimum feature size. For a given order, a larger number of layers result in a higher reflectivity while reducing the reflectivity bandwidth.

The interplay between the dielectric stack parameters is shown in Fig. 2. This graph which is calculated using TMM shows the reflectivity and bandwidth of a third-order QW Bragg reflector to be fabricated on an SOI platform with an Si top layer of 220 nm thickness and a buried oxide layer of 2000 nm. Once the Bragg reflector is designed, the diffraction grating profile must be determined. To do so, we have adopted the approach in [13].

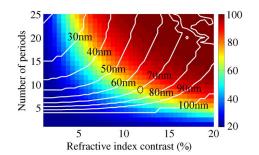

In this scheme, the grating facets are considered to be reflective arcs of concentric circles centered at the input point. The difference between the radii of successive arcs is chosen to be an integer (diffraction grating order) multiple of half wavelengths. The coordinates of the facet centers can thus be calculated since each facet subtends an equal angle at the input. Another characteristic of this approach is that it assumes the output waveguides are placed equidistantly along a line through the input point, that is, the centers of the output waveguides are placed along a vertical straight (focal) line that passes through the input point. The spacing between the output waveguides centers is constant along this line (see Fig. 1). This approach exhibits less aberration than the conventional Rowland approach [14]. In addition, and more importantly, upon using a shallow etched DBR structure to improve the reflectivity at facets of the grating, a relatively large number of DBR periods is required to achieve a reasonably high reflectivity. In such a case, the total length of the DBR structure is usually longer than the length of the facet comprising it, and therefore, the DBR layers from a higher facet overlap with the ones from a lower facet. The conventional Rowland approach does not allow for a continuity of Bragg layers between successive facets (see Fig. 3). This drawback, which is due to the fact that in a Rowland configuration, the grating facets maintain a constant angle along a chord rather than along the grating curve, will lead to additional scattering loss when fabricated unless either the grating is designed to work at very large orders (to achieve a sufficiently long facet length), or only a few Bragg cycles are considered so that all the DBR layers are contained in one period of the grating. The former results in a small free spectral range while the

Fig. 3. Flat-field design (a) versus conventional Roland design (b). The flat-field design allows for a continuity of DBR layers of successive facets.

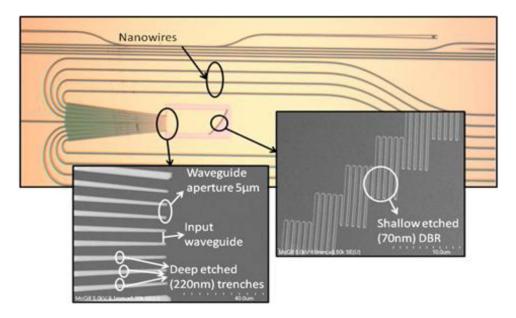

Fig. 4. Layout of the tested DEDG.

latter, requiring deeply etched trenches to provide high reflectivity with only a few layers, leads to losing the possibility of optimizing the reflectivity of Bragg structure in order to manipulate the overall spectral response of the EDG demultiplexer. We believe that the flat-field configuration used in this work is more suitable for the EDG demultiplexers incorporating shallow etched Bragg structure at the facets.

In the approach introduced in [13], the input waveguide is placed in the middle of the output waveguides leading to creation of a hole in the spectrum. For example, if the design wavelength is to be 1550 nm, then one half of the spectrum ( $\lambda < 1550$  nm) will be directed to one side of the input waveguide, and the other half ( $\lambda > 1550$  nm) will be focused on the other side of the input waveguide. In that configuration, the center wavelength ( $\lambda = 1550$  nm) is reflected back on the input waveguide, resulting in a gap in the middle of the output spectrum. To avoid such a gap, we employ a slightly different approach. The design wavelength ( $\lambda = 1600$  nm) was chosen to be at the edge of the wavelength range of interest. As a result, the entire wavelength band of interest (the C band in this case) lies below the design wavelength and, thus, is focused to one side of the input waveguide, avoiding a gap in the output spectrum. In the prototype device (see Fig. 4), only the four lower output waveguides are employed, making the upper group redundant and only included for test purposes.

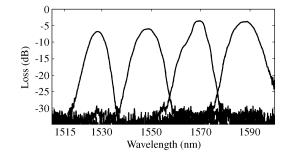

Fig. 5. Measured spectrum of the DEDG.

## 3. Experiments

The layout of the proof-of-concept DEDG discussed in this paper is shown in Fig. 4. This structure, which was designed for coarse WDM applications, demultiplexes four output channels with 20 nm channel spacing. The dielectric stack in this structure was designed to be a third-order Bragg reflector with 10 DBR periods (see Fig. 4).

The shadowed facet of the diffraction grating comprises five DBR periods, which results in a diffraction grating order of 15 at the design wavelength of 1600 nm. The illuminated facets were designed with a curvature that perfectly matches that of the focusing diffraction grating and the incident wavefronts.

The diffraction grating contains 25 periods with a period of 6.07  $\mu$ m. The input/output waveguides are tapered to a width of 5  $\mu$ m (at the edge of the free propagation region), and vertical grating couplers were used in order to couple light in/out of the waveguides. The distance from the input waveguide to the central period (i.e., the pole) of the diffraction grating is 310  $\mu$ m. The cross section of waveguides is 220 × 500 nm<sup>2</sup> to maintain single mode operation, and the smallest waveguide curvature radius is 50  $\mu$ m. The device and the vertical grating couplers are designed for transverse electric (TE)-polarization. The device was fabricated at ePIXfab via the IMEC process on an SOI wafer with a 220-nm-thick Si top layer using 193-nm deep-ultraviolet (DUV) lithography. Input/ output waveguides were formed by etching deep trenches through the silicon layer (220 nm). For the shallow etched structures (i.e., DBR structure and the input/output vertical grating couplers) the etch depth was 70 nm.

In order to measure the spectrum of the demultiplexer, light from a cleaved single mode fiber was coupled into the input waveguide through a shallow etched fiber grating coupler, and the output light was collected at the output waveguides using another single mode cleaved fiber. Grating couplers were employed in this case due to their relative ease of fabrication and coupling; however, they do suffer from greater insertion loss, bandwidth limitation, and polarization dependence more than alternative methods such as inverse tapers [15]. As such, they are less likely to be employed in an ultimate commercial implementation. The coupling loss in our experiment was –10 dB/coupler. However, better coupling losses (–5 dB) have been reported in the literature for these gratings [16].

Fig. 5 shows the measured spectrum of the device normalized to the spectrum of a reference waveguide. The device shows a crosstalk of -25 dB and an insertion loss of -3.8 dB for the best channel and -7 dB for the worst channel. The insertion loss nonuniformity is due to the fact that the DBR is designed to have a higher reflectivity at 1590 than at 1530. This nonuniformity, however, can be mitigated via spectral response engineering [11]. The insertion loss of the device is mainly due to the scattering loss of the third-order DBR incorporated at the facets. Two-dimensional-finite-difference time-domain (FDTD) calculations show a DBR scattering loss of -2.7 dB for the best channel and -6 dB for the worst channel. Replacing the third-order DBR with a first-order design would significantly improve the insertion loss. However, since a first-order design requires smaller feature sizes it would not be possible to fabricate the devices using optical lithography techniques. FDTD calculations also predict a diffraction loss (i.e., diffracting light into diffraction orders other than the desired one) of -0.5 dB. The additional -0.6 dB loss can be attributed to the DBR

fabrication imperfections such as roughness and trench width nonuniformity. FDTD simulations show that the insertion loss in theory could be reduced to -0.55 dB if first-order DBR is considered instead of a higher order one. From Fig. 5, one also observes that the passband of the demultiplexer increases with wavelength. The main reason behind the passband nonuniformity is that the outermost channels are not optimally focused on the flat output focal line assumed in the grating design. The approximation used in [13] no longer holds as perfectly for the outer channel at 1530 nm as it does for the channel at 1590 nm. To overcome this problem, the focal position for each channel can be optimized by displacing it slightly from the flat-field condition

### 4. Conclusion

Measurement results for a proof-of-concept four channel DEDG demultiplexer were presented. The device, which was fabricated on an SOI nanophotonic platform using DUV optical lithography, achieved an insertion loss of -3.8 dB for the best channel and -7 dB for the worst channel. The main contributing factor to the insertion loss of the device is scattering loss due to using a higher order DBR (third order). Numerical simulations indicated that a first order implementation would reduce insertion loss by more than 2 dB. Due to the long interaction length of the distributed diffraction grating, the conventional Rowland design is not suitable, since it results in misalignments between adjacent grating periods. As a result, we have adopted an alternative design approach, in which the grating facets are placed along arcs of concentric circles centered at the input point. The distributed shallow EDG provides the possibility of spectral response engineering [11] of the DEDG demultiplexer, although it does result in the need to tradeoff reflection bandwidth with insertion loss. While the shallow etching required for the diffraction grating does require an additional etch step beyond that required for SOI waveguides alone, in practice, this is the same etch depth that is necessary for the etched input and output grating couplers that are employed in this device. As a result, it does not increase the fabrication complexity of the device.

## Acknowledgment

The authors thank D. Deptuk of CMC Microsystems Canada for his kind help with device layout creation.

#### References

- A. Sugita, A. Kaneko, K. Okamoto, M. Itoh, A. Himeno, and Y. Ohmori, "Very low insertion loss arrayed waveguide grating with vertically tapered waveguides," *IEEE Photon. Technol. Lett.*, vol. 12, no. 9, pp. 1180–1182, Sep. 2000.

- [2] S. Janz, A. Balakrishnan, S. Charbonneau, P. Cheben, M. Cloutier, A. Delage, K. Dossou, L. Érickson, M. Gao, P. A. Krug, B. Lamontagne, M. Packirisamy, M. Pearson, and D.-X. Xu, "Planar waveguide echelle gratings in silica-on-silicon," *IEEE Photon. Technol. Lett.*, vol. 16, no. 2, pp. 503–505, Feb. 2004.

- [3] Y. Yoshikuni, "Semiconductor arrayed waveguide gratings for photonic integrated devices," *IEEE J. Sel. Topics Quantum Electron.*, vol. 8, no. 6, pp. 1102–1114, Nov./Dec. 2002.

- [4] J. J. He, B. Lamontagne, A. Delage, L. Erickson, M. Davies, and E. S. Koteles, "Monolithic integrated wavelength demultiplexer based on a waveguide Rowland circle grating in InGaAsP/InP," *J. Lightw. Technol.*, vol. 16, no. 4, pp. 631–638, Apr. 1998.

- [5] P. D. Trinh, S. Yegnanarayanan, F. Coppinger, and B. Jalali, "Silicon-on-insulator (SOI) phased-array wavelength multi/demultiplexer with extremely low-polarization sensitivity," *IEEE Photon. Technol. Lett.*, vol. 9, no. 7, pp. 940–942, Jul. 1997.

- [6] J. Brouckaert, W. Bogaerts, P. Dumon, D. Van Thourhout, and R. Baets, "Planar concave grating demultiplexer fabricated on a nanophotonic silicon-on-insulator platform," J. Lightw. Technol., vol. 25, no. 5, pp. 1269–1275, May 2007.

- [7] B. B. C. Kyotoku, C. Long, and M. Lipson, "Broad band 1 nm channel spacing silicon-on-insulator wavelength division multiplexer," in *Proc. CLEO/QELS*, 2009, pp. 1–2, 2–4.

- [8] E. Bisaillon, D. T. H. Tan, M.-C. Nadeau, L. Chrostowski, and A. G. Kirk, "Distributed-grating wavelength demultiplexer in SOI," in *Proc. 19th Annu. Meeting IEEE LEOS*, 2006, pp. 462–463.

- [9] C. T. Lin, Y. T. Huang, and J. W. Huang, "A planar waveguide concave grating employing dielectric mirrors," Opt. Commun., vol. 281, no. 5, pp. 1072–1076, Mar. 2008.

- [10] J. Brouckaert, W. Bogaerts, S. Selvaraja, P. Dumon, R. Baets, and D. Van Thourhout, "Planar concave grating demultiplexer with high reflective Bragg reflector facets," *IEEE Photon. Technol. Lett.*, vol. 20, no. 4, pp. 309–311, Feb. 15, 2008.

- [11] A. Jafari and A. G. Kirk, "Distributed etched diffraction grating demultiplexer with engineered response," in *Proc. 21st Annu. Meeting IEEE LEOS*, Nov. 9–13, 2008, pp. 59–60.

- [12] H. A. MacLeod, Thin-Film Optical Filters, 3rd ed. Philadelphia, PA: Inst. Phys., 2001.

- [13] J. N. McMullin, R. G. DeCorby, and C. J. Haugen, "Theory and simulation of a concave diffraction grating demultiplexer for coarse WDM systems," J. Lightw. Technol., vol. 20, no. 4, pp. 758–765, Apr. 2002.

- [14] S. Ho and S. Chang, "Curved grating spectrometer with very high wavelength resolution," U.S. Patent 7 283 233, Oct. 16, 2007.

- [15] I. E. Day, I. Evans, A. Knights, F. Hopper, S. Roberts, J. Johnston, S. Day, J. Luff, H. K. Tsang, and M. Asghari, "Tapered silicon waveguides for low insertion loss highly-efficient high-speed electronic variable optical attenuators," in *Opt. Fiber Commun. Conf., Tech. Dig.*, 2003, pp. 249–251.

- [16] W. Bogaerts, S. K. Selvaraja, P. Dumon, J. Brouckaert, K. De Vos, D. Van Thourhout, and R. Baets, "Silicon-oninsulator spectral filters fabricated with CMOS technology," *IEEE J. Sel. Topics Quantum Electron.*, vol. 16, no. 1, pp. 33–44, Jan./Feb. 2010.